Characteristics of Offset Corbino Thin Film Transistor: A Physical Model

Abstract

1. Introduction

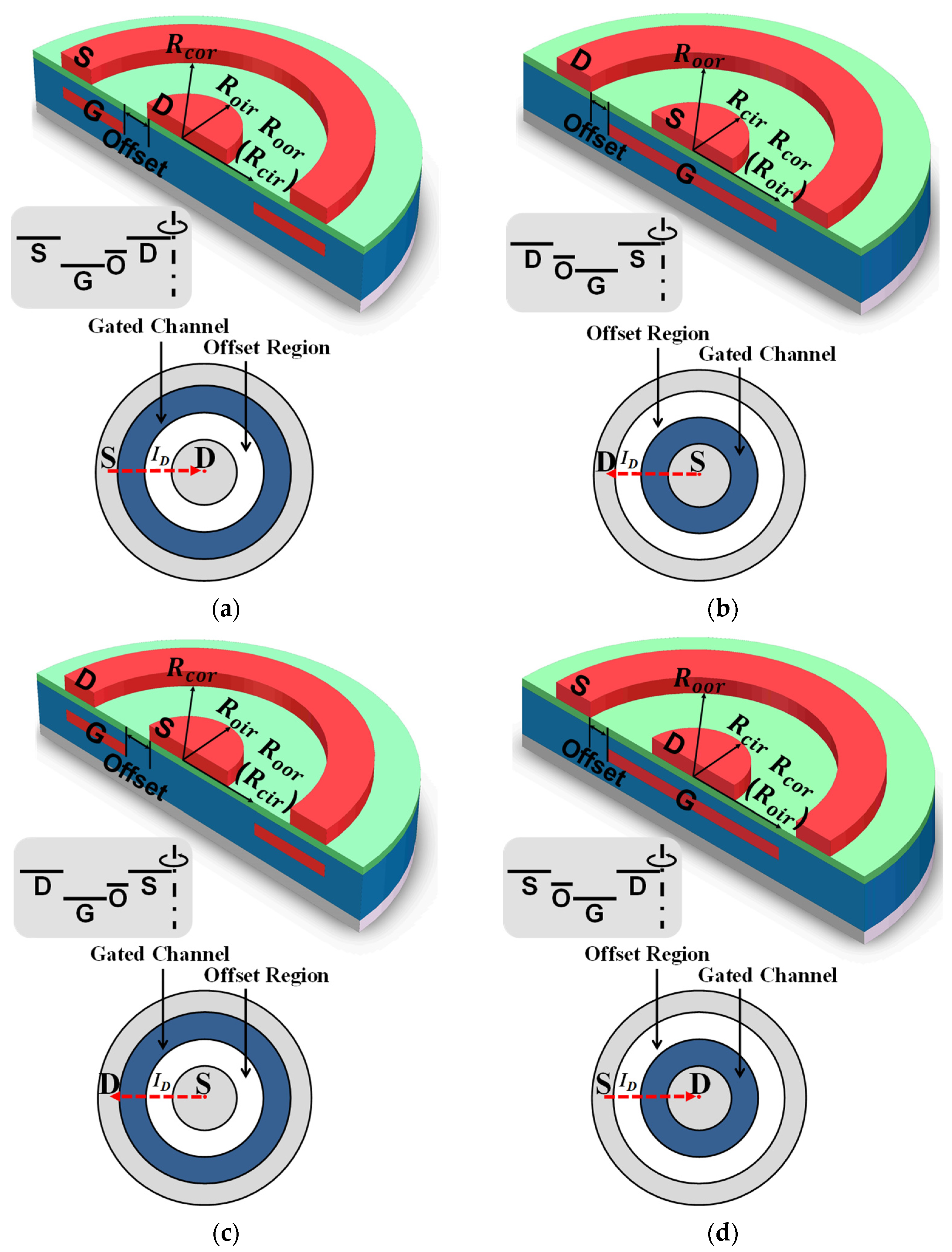

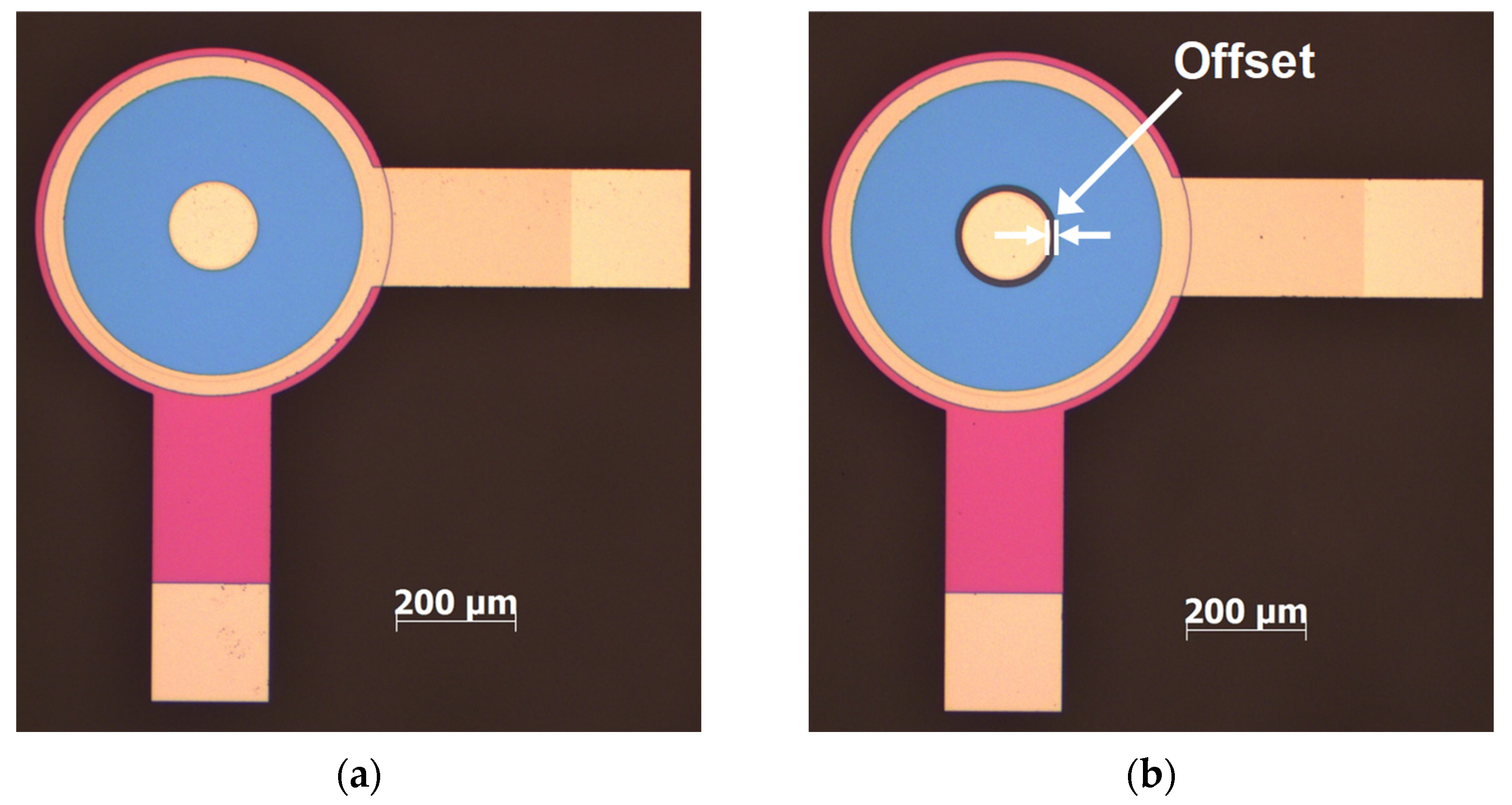

2. Device Structure of Model

3. Results and Discussion

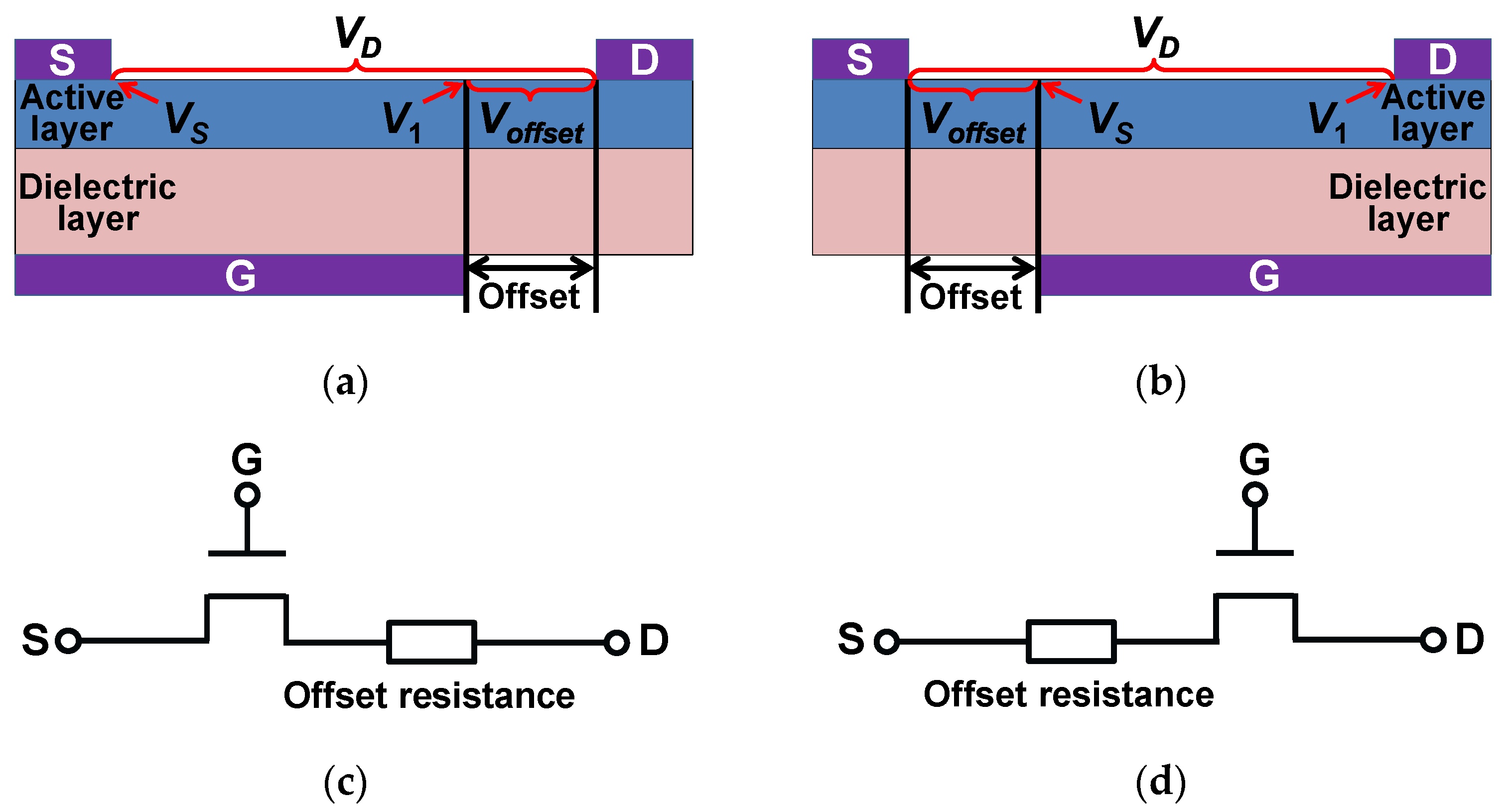

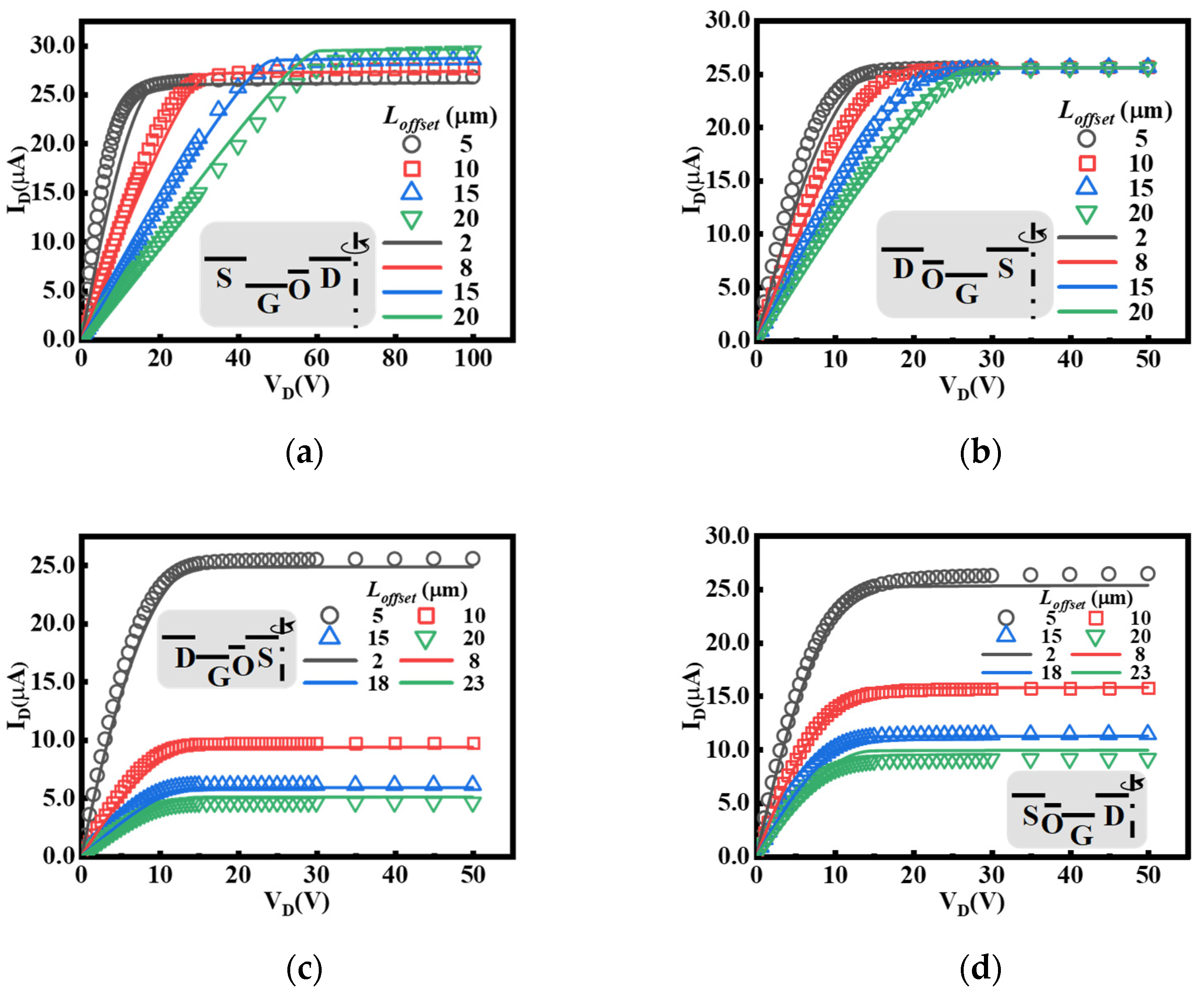

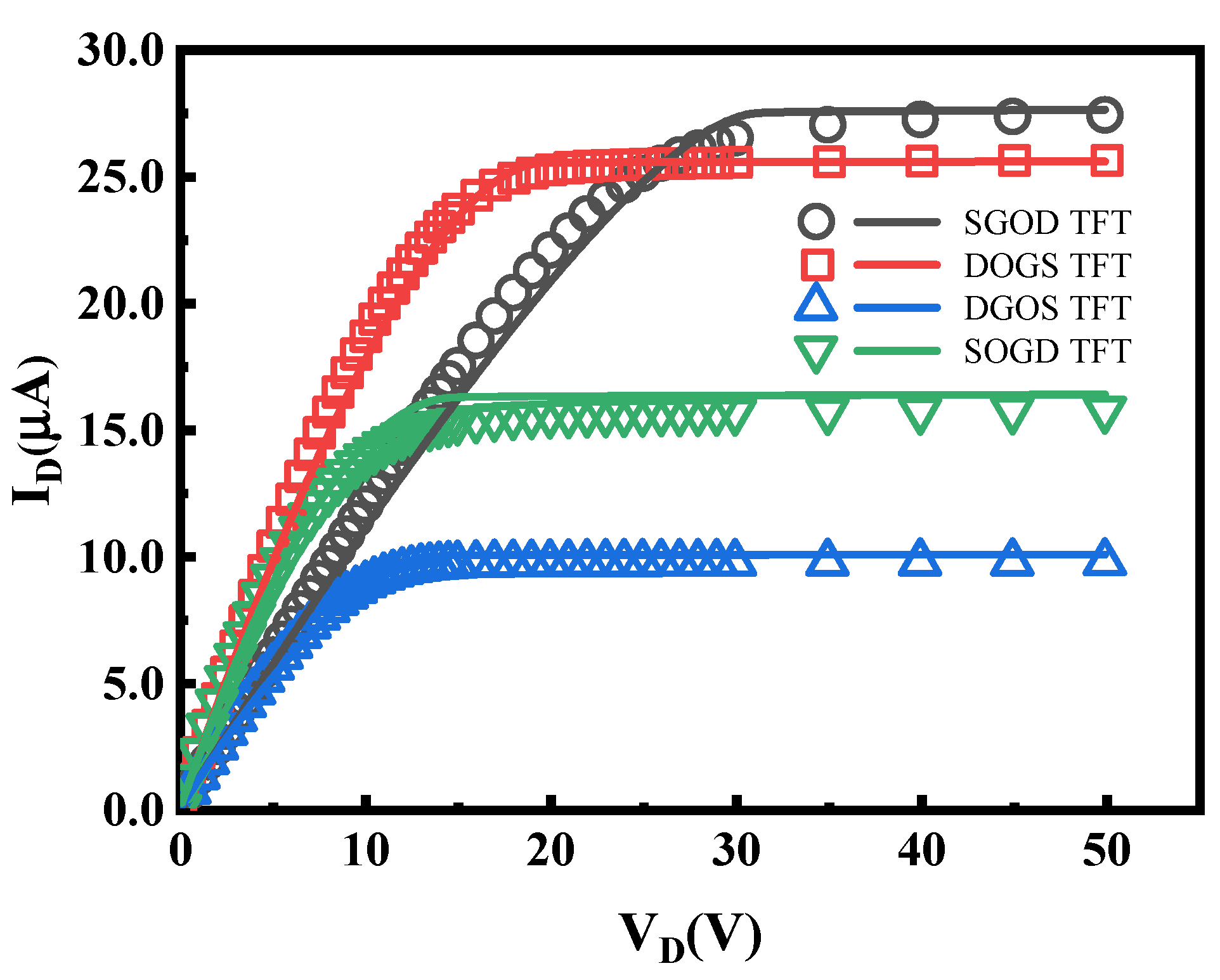

3.1. Formula

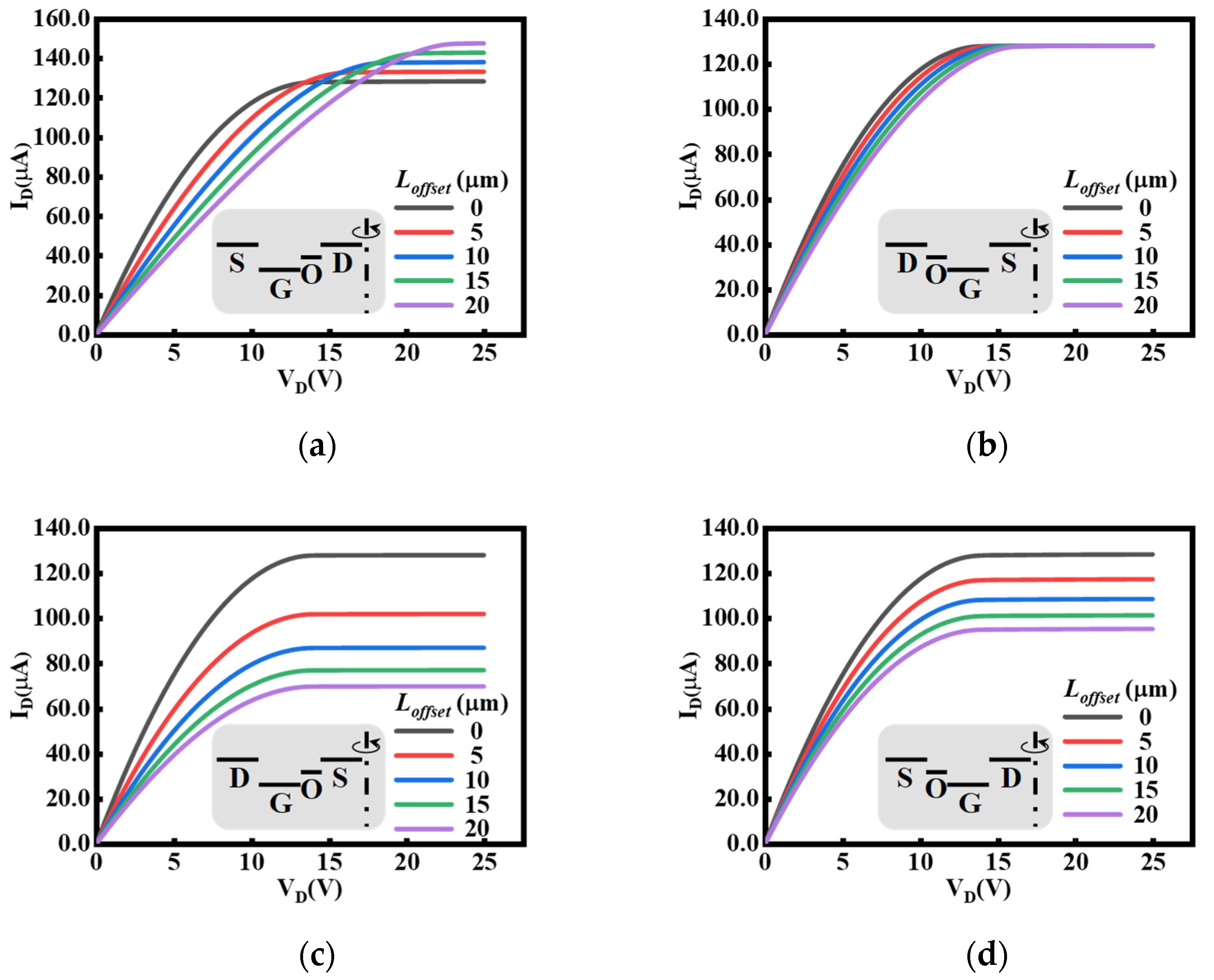

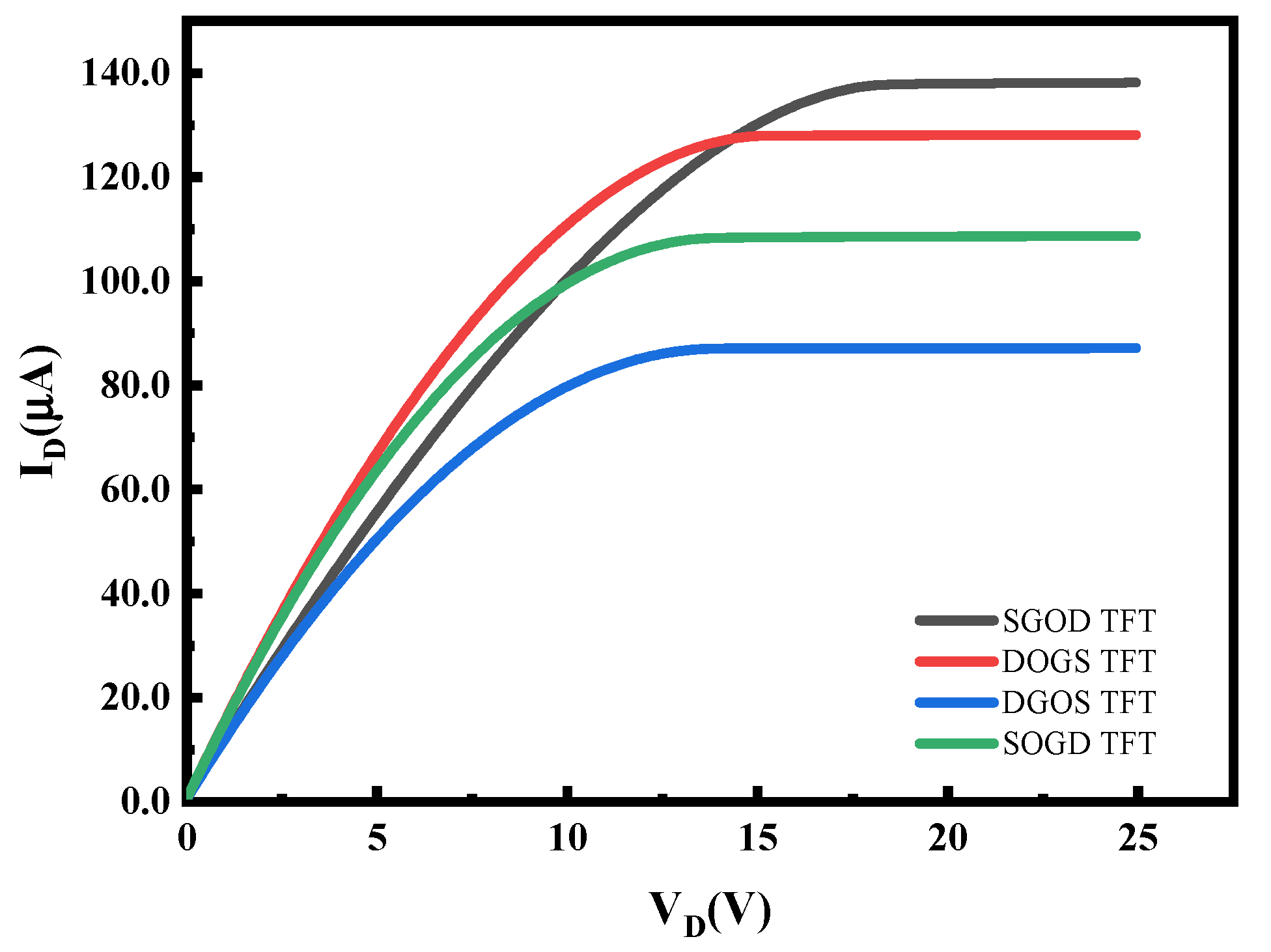

3.2. Simulation

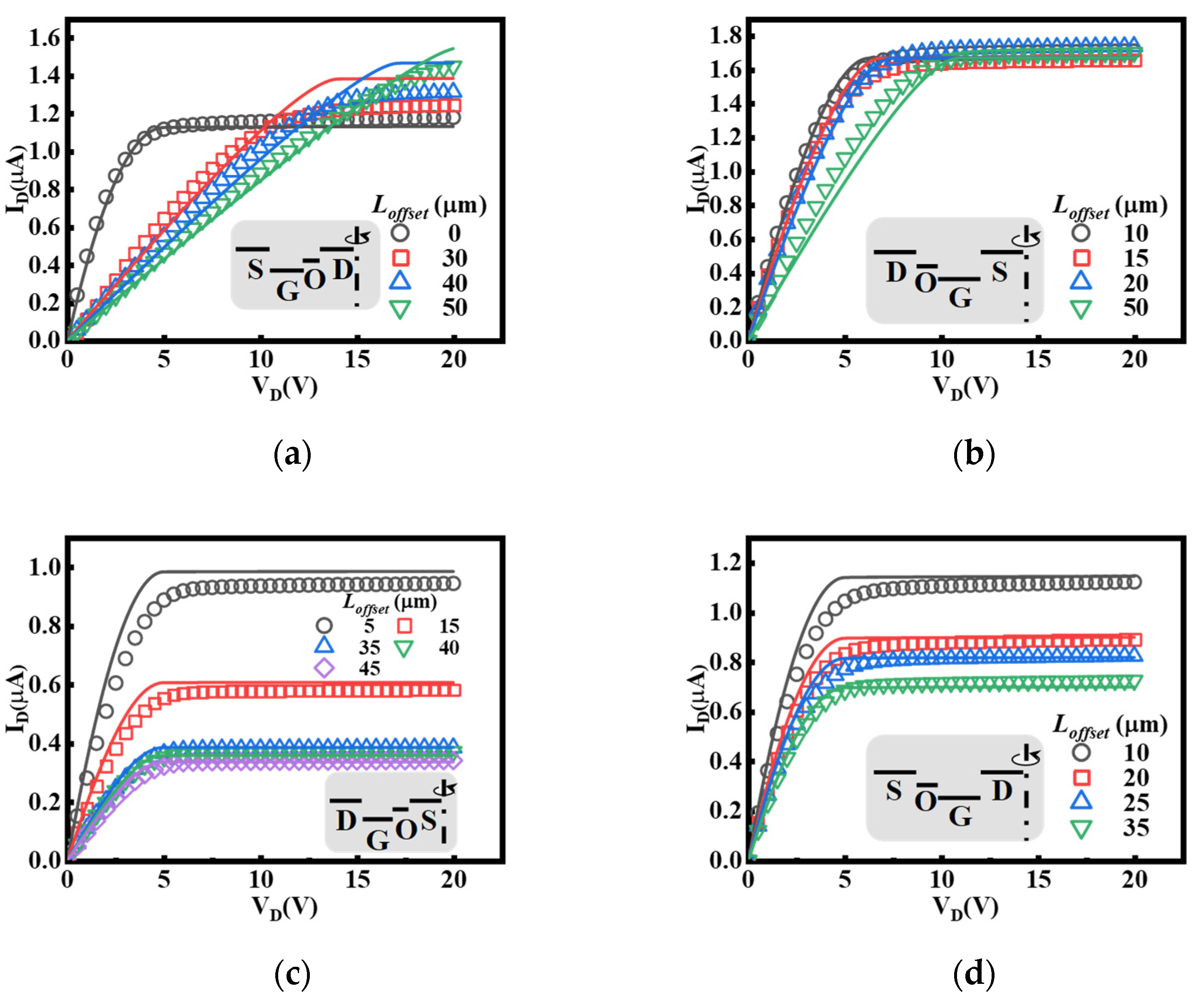

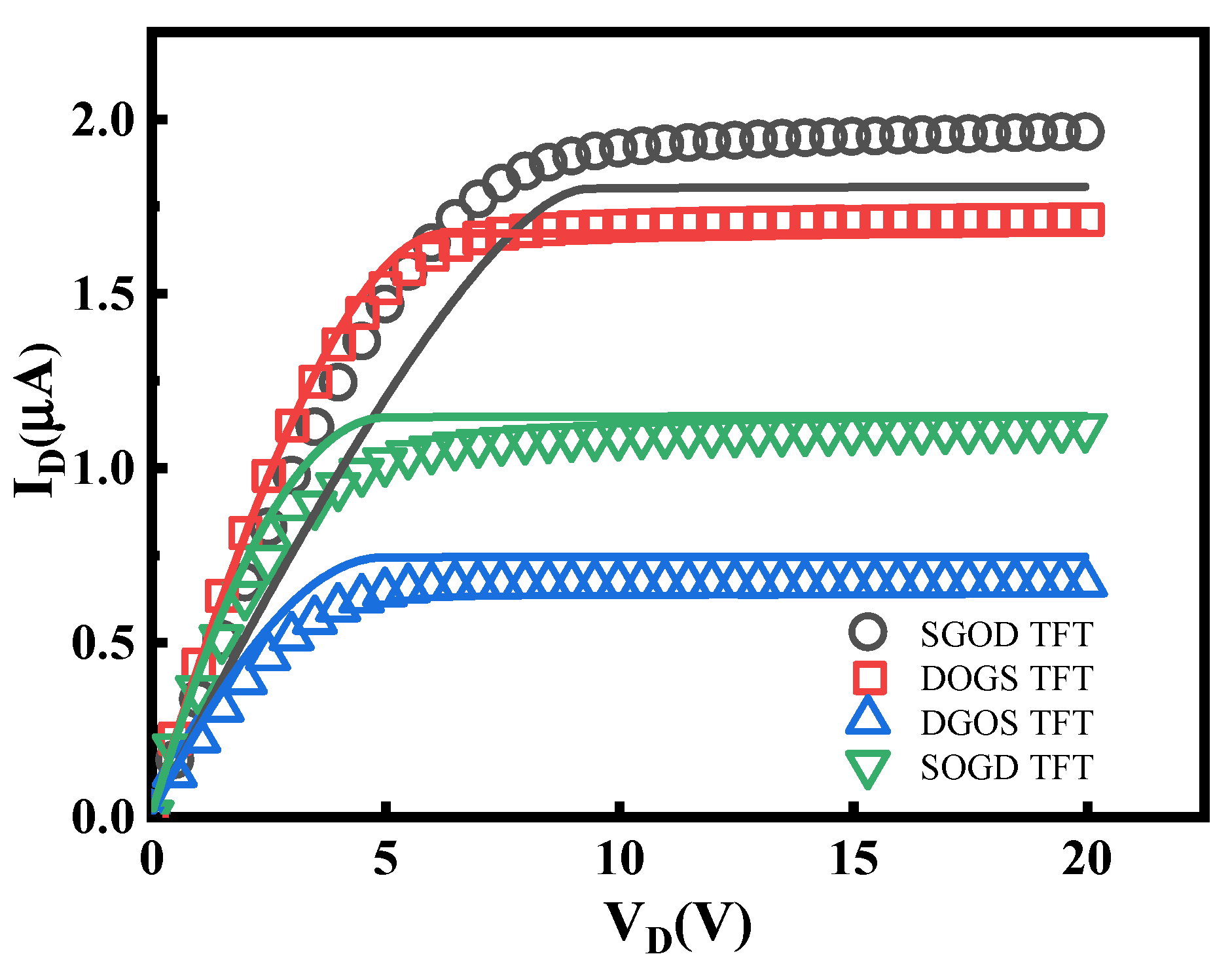

3.3. Experimental Verification

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Song, Y.H.; Kim, K.B.; Hwang, C.S.; Park, D.J.; Lee, J.H.; Kang, K.Y.; Hur, J.H.; Jang, J. Active-matrix field-emission display based on a CNT emitter and a-Si TFTs. J. Soc. Inf. Disp. 2005, 13, 241–244. [Google Scholar] [CrossRef]

- Marette, A.; Poulin, A.; Besse, N.; Rosset, S.; Briand, D.; Shea, H. Flexible zinc–tin oxide thin film transistors operating at 1 kV for integrated switching of dielectric elastomer actuators arrays. Adv. Mater. 2017, 29, 1700880. [Google Scholar] [CrossRef] [PubMed]

- Karpelson, M.; Wei, G.-Y.; Wood, R.J. Driving high voltage piezoelectric actuators in microrobotic applications. Sens. Actuators A 2012, 176, 78–89. [Google Scholar] [CrossRef]

- Zhang, Y.; Mei, Z.; Wang, T.; Huo, W.; Cui, S.; Liang, H.; Du, X. Flexible transparent high-voltage diodes for energy management in wearable electronics. Nano Energy 2017, 40, 289–299. [Google Scholar] [CrossRef]

- Galazka, Z.; Uecker, R.; Irmscher, K.; Albrecht, M.; Klimm, D.; Pietsch, M.; Brützam, M.; Bertram, R.; Ganschow, S.; Fornari, R. Czochralski growth and characterization of β-Ga2O3 single crystals. Cryst. Res. Technol. 2010, 45, 1229–1236. [Google Scholar] [CrossRef]

- Hasegawa, H.; Kawabe, U.; Aita, T.; Ishiba, T. Single crystal growth of layered perovskite metal oxides. Jpn. J. Appl. Phys. 1987, 26, L673. [Google Scholar] [CrossRef]

- Seki, S.; Kogure, O.; Tsujiyama, B. Leakage current characteristics of offset-gate-structure polycrystalline-silicon MOSFET’s. IEEE Electron Device Lett. 1987, 8, 434–436. [Google Scholar] [CrossRef]

- Unagami, T. High-voltage poly-Si TFTs with multichannel structure. IEEE Trans. Electron Devices 1988, 35, 2363–2367. [Google Scholar] [CrossRef]

- Huang, T.-Y.; Lewis, A.; Wu, I.-W.; Chiang, A.; Bruce, R. New intra-gate-offset high-voltage thin-film transistor with misalignment immunity. Electron. Lett. 1989, 25, 544–545. [Google Scholar] [CrossRef]

- Huang, T.-Y.; Wu, I.-W.; Lewis, A.G.; Chiang, A.; Bruce, R.H. A simpler 100-V polysilicon TFT with improved turn-on characteristics. IEEE Electron Device Lett. 1990, 11, 244–246. [Google Scholar] [CrossRef]

- Huang, T.-Y.; Wu, I.-W.; Lewis, A.; Chiang, A.; Bruce, R. Device sensitivity of field-plated polysilicon high-voltage TFTs and their application to low-voltage operation. IEEE Electron Device Lett. 1990, 11, 541–543. [Google Scholar] [CrossRef]

- Park, C.; Billah, M.M.; Siddik, A.B.; Lee, S.; Han, B.; Jang, J. High Voltage Amorphous InGaZnO TFT with F Doped Drain Offset Structure. IEEE Electron Device Lett. 2021, 42, 1476–1479. [Google Scholar] [CrossRef]

- Wu, M.-H.; Lin, H.-C.; Li, P.-W. Film-profile-engineered ZnO thin-film transistor with gate/drain offset for high-voltage operation. Jpn. J. Appl. Phys. 2019, 58, 066502. [Google Scholar] [CrossRef]

- Saito, W.; Kakiuchi, Y.; Nitta, T.; Saito, Y.; Noda, T.; Fujimoto, H.; Yoshioka, A.; Ohno, T.; Yamaguchi, M. Field-plate structure dependence of current collapse phenomena in high-voltage GaN-HEMTs. IEEE Electron Device Lett. 2010, 31, 659–661. [Google Scholar] [CrossRef]

- Saito, W.; Nitta, T.; Kakiuchi, Y.; Saito, Y.; Tsuda, K.; Omura, I.; Yamaguchi, M. On-resistance modulation of high voltage GaN HEMT on sapphire substrate under high applied voltage. IEEE Electron Device Lett. 2007, 28, 676–678. [Google Scholar] [CrossRef]

- Zhang, P.; Zhao, S.-L.; Hou, B.; Wang, C.; Zheng, X.-F.; Ma, X.-H.; Zhang, J.-C.; Hao, Y. Improvement of the off-state breakdown voltage with field plate and low-density drain in AlGaN/GaN high-electron mobility transistors. Chin. Phys. B 2015, 24, 037304. [Google Scholar] [CrossRef]

- Saito, W.; Nitta, T.; Kakiuchi, Y.; Saito, Y.; Tsuda, K.; Omura, I.; Yamaguchi, M. Suppression of dynamic on-resistance increase and gate charge measurements in high-voltage GaN-HEMTs with optimized field-plate structure. IEEE Trans. Electron Devices 2007, 54, 1825–1830. [Google Scholar] [CrossRef]

- Dora, Y.; Chakraborty, A.; Mccarthy, L.; Keller, S.; DenBaars, S.; Mishra, U. High breakdown voltage achieved on AlGaN/GaN HEMTs with integrated slant field plates. IEEE Electron Device Lett. 2006, 27, 713–715. [Google Scholar] [CrossRef]

- Huo, W.; Liang, H.; Lu, Y.; Han, Z.; Zhu, R.; Sui, Y.; Wang, T.; Mei, Z. Dual-active-layer InGaZnO high-voltage thin-film transistors. Semicond. Sci. Technol. 2021, 36, 065021. [Google Scholar] [CrossRef]

- Yang, G.; Li, M.; Yu, Z.; Xu, Y.; Sun, H.; Liu, S.; Sun, W.; Wu, W. High-Voltage a-IGZO TFTs With the Stair Gate-Dielectric Structure. IEEE Trans. Electron Devices 2021, 68, 4462–4466. [Google Scholar] [CrossRef]

- Karim, K.S.; Servati, P.; Nathan, A. High voltage amorphous silicon TFT for use in large area applications. Microelectron. J. 2004, 35, 311–315. [Google Scholar] [CrossRef]

- Martin, R.A.; Da Costa, V.M.; Hack, M.; Shaw, J.G. High-voltage amorphous silicon thin-film transistors. IEEE Trans. Electron Devices 1993, 40, 634–644. [Google Scholar] [CrossRef]

- Unagami, T.; Kogure, O. High-voltage TFT fabricated in recrystallized polycrystalline silicon. IEEE Trans. Electron Devices 1988, 35, 314–319. [Google Scholar] [CrossRef]

- Yu, M.-J.; Lin, R.-P.; Chang, Y.-H.; Hou, T.-H. High-Voltage Amorphous InGaZnO TFT With Al2O3 High-k Dielectric for Low-Temperature Monolithic 3-D Integration. IEEE Trans. Electron Devices 2016, 63, 3944–3949. [Google Scholar] [CrossRef]

- Chow, E.M.; Lu, J.P.; Ho, J.; Shih, C.; De Bruyker, D.; Rosa, M.; Peeters, E. High voltage thin film transistors integrated with MEMS. Sens. Actuators A 2006, 130, 297–301. [Google Scholar] [CrossRef]

- Li, X.; Liu, C.; Liu, C.; Ou, H.; She, J.; Deng, S.; Chen, J. Kilo-voltage thin-film transistors for driving nanowire field emitters. IEEE Electron Device Lett. 2020, 41, 405–408. [Google Scholar] [CrossRef]

- Li, X.; Liu, C.; Kong, J.; Ou, H.; She, J.; Deng, S.; Chen, J. Widely Adjusting the Breakdown Voltages of Kilo-voltage Thin Film Transistors. IEEE Electron Device Lett. 2022, 43, 240–243. [Google Scholar] [CrossRef]

- Hong, W.-C.; Ku, C.-J.; Li, R.; Abbaslou, S.; Reyes, P.; Wang, S.-Y.; Li, G.; Lu, M.; Sheng, K.; Lu, Y. MgZnO high voltage thin film transistors on glass for inverters in building integrated photovoltaics. Sci. Rep. 2016, 6, 34169. [Google Scholar] [CrossRef]

- Hong, W.-C.; Zhang, Y.; Wang, S.-Y.; Li, Y.; Alim, N.; Du, X.; Mei, Z.; Lu, Y. ZnO flexible high voltage thin film transistors for power management in wearable electronics. J. Vac. Sci. Technol. B Nanotechnol. Microelectron. Mater. Process. Meas. Phenom. 2018, 36, 050601. [Google Scholar] [CrossRef]

- Mativenga, M.; Jun, H.; Choe, Y.; Um, J.G.; Jang, J. Circular structure for high mechanical bending stability of a-IGZO TFTs. IEEE J. Electron Devices Soc. 2017, 5, 453–457. [Google Scholar] [CrossRef]

- Huo, W.; Mei, Z.; Sui, Y.; Han, Z.; Wang, T.; Liang, H.; Du, X. Flexible transparent InGaZnO thin-film transistors on muscovite mica. IEEE Trans. Electron Devices 2019, 66, 2198–2201. [Google Scholar] [CrossRef]

- Mativenga, M.; Ha, S.H.; Geng, D.; Kang, D.H.; Mruthyunjaya, R.K.; Heiler, G.N.; Tredwell, T.J.; Jang, J. Infinite output resistance of Corbino thin-film transistors with an amorphous-InGaZnO active layer for large-area AMOLED displays. IEEE Trans. Electron Devices 2014, 61, 3199–3205. [Google Scholar] [CrossRef]

- Joo, H.-J.; Shin, M.-G.; Kwon, S.-H.; Jeong, H.-Y.; Jeong, H.-S.; Kim, D.-H.; Jin, X.; Song, S.-H.; Kwon, H.-I. High-gain complementary inverter based on Corbino p-type tin monoxide and n-type indium-gallium-zinc oxide thin-film transistors. IEEE Electron Device Lett. 2019, 40, 1642–1645. [Google Scholar] [CrossRef]

- Geng, R.; Gong, Y. High performance active image sensor pixel design with circular structure oxide TFT. J. Semicond. 2019, 40, 022402. [Google Scholar] [CrossRef]

- Deegan, R.D.; Bakajin, O.; Dupont, T.F.; Huber, G.; Nagel, S.R.; Witten, T.A. Capillary flow as the cause of ring stains from dried liquid drops. Nature 1997, 389, 827–829. [Google Scholar] [CrossRef]

- Zhang, L.; Liu, H.; Zhao, Y.; Sun, X.; Wen, Y.; Guo, Y.; Gao, X.; Di, C.a.; Yu, G.; Liu, Y. Inkjet printing high-resolution, large-area graphene patterns by coffee-ring lithography. Adv. Mater. 2012, 24, 436–440. [Google Scholar] [CrossRef]

- Liu, C.; Li, X.; Luo, Y.; Wang, Y.; Hu, S.; Liu, C.; Liang, X.; Zhou, H.; Chen, J.; She, J. How Materials and Device Factors Determine the Performance: A Unified Solution for Transistors with Nontrivial Gates and Transistor–Diode Hybrid Integration. Adv. Sci. 2021, 9, 2104896. [Google Scholar] [CrossRef]

- Qiang, L.; Yao, R. A new definition of the threshold voltage for amorphous InGaZnO thin-film transistors. IEEE Trans. Electron Devices 2014, 61, 2394–2397. [Google Scholar] [CrossRef]

- Byun, Y.H.; Den Boer, W.; Yang, M.; Gu, T. An amorphous silicon TFT with annular-shaped channel and reduced gate-source capacitance. IEEE Trans. Electron Devices 1996, 43, 839–841. [Google Scholar] [CrossRef]

- Neamen, D.A. Semiconductor Physics and Devices: Basic Principles, 4th ed.; McGraw-Hill: New York, NY, USA, 2003; pp. 446–447. [Google Scholar]

| Drain-Offset Corbino TFT | ||

| SGOD TFT | DOGS TFT | |

| V1 | ||

| VS | 0 | |

| ID in the linear region | ||

| ID in the saturation region | ||

| VDsat | ||

| IDsat | ||

| Source-Offset Corbino TFT | ||

| DGOS TFT | SOGD TFT | |

| V1 | VD | |

| VS | ||

| ID in the linear region | ||

| ID in the saturation region | ||

| VDsat | ||

| IDsat | ||

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| 1.0 | 1.5 × 1017 | ||

| 5.0 | 5.0 | ||

| 5.0 × 10−8 | 0.05 × 10−4 | ||

| 8.5 × 10−13 | 1.0 × 1017 | ||

| 0, 5, 10, 15, 20 | () | 175 | |

| Inner electrode radius () | 75 |

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| 5.5 × | 1.85 × | ||

| 0.015 | 0.3 | ||

| 5.5 × | 1.225 × | ||

| 0.22 | 0.13 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kong, J.; Liu, C.; Li, X.; Ou, H.; She, J.; Deng, S.; Chen, J. Characteristics of Offset Corbino Thin Film Transistor: A Physical Model. Electronics 2023, 12, 2195. https://doi.org/10.3390/electronics12102195

Kong J, Liu C, Li X, Ou H, She J, Deng S, Chen J. Characteristics of Offset Corbino Thin Film Transistor: A Physical Model. Electronics. 2023; 12(10):2195. https://doi.org/10.3390/electronics12102195

Chicago/Turabian StyleKong, Jiaquan, Chuan Liu, Xiaojie Li, Hai Ou, Juncong She, Shaozhi Deng, and Jun Chen. 2023. "Characteristics of Offset Corbino Thin Film Transistor: A Physical Model" Electronics 12, no. 10: 2195. https://doi.org/10.3390/electronics12102195

APA StyleKong, J., Liu, C., Li, X., Ou, H., She, J., Deng, S., & Chen, J. (2023). Characteristics of Offset Corbino Thin Film Transistor: A Physical Model. Electronics, 12(10), 2195. https://doi.org/10.3390/electronics12102195