Prospective Submodule Topologies for MMC-BESS and Its Control Analysis with HBSM

Abstract

1. Introduction

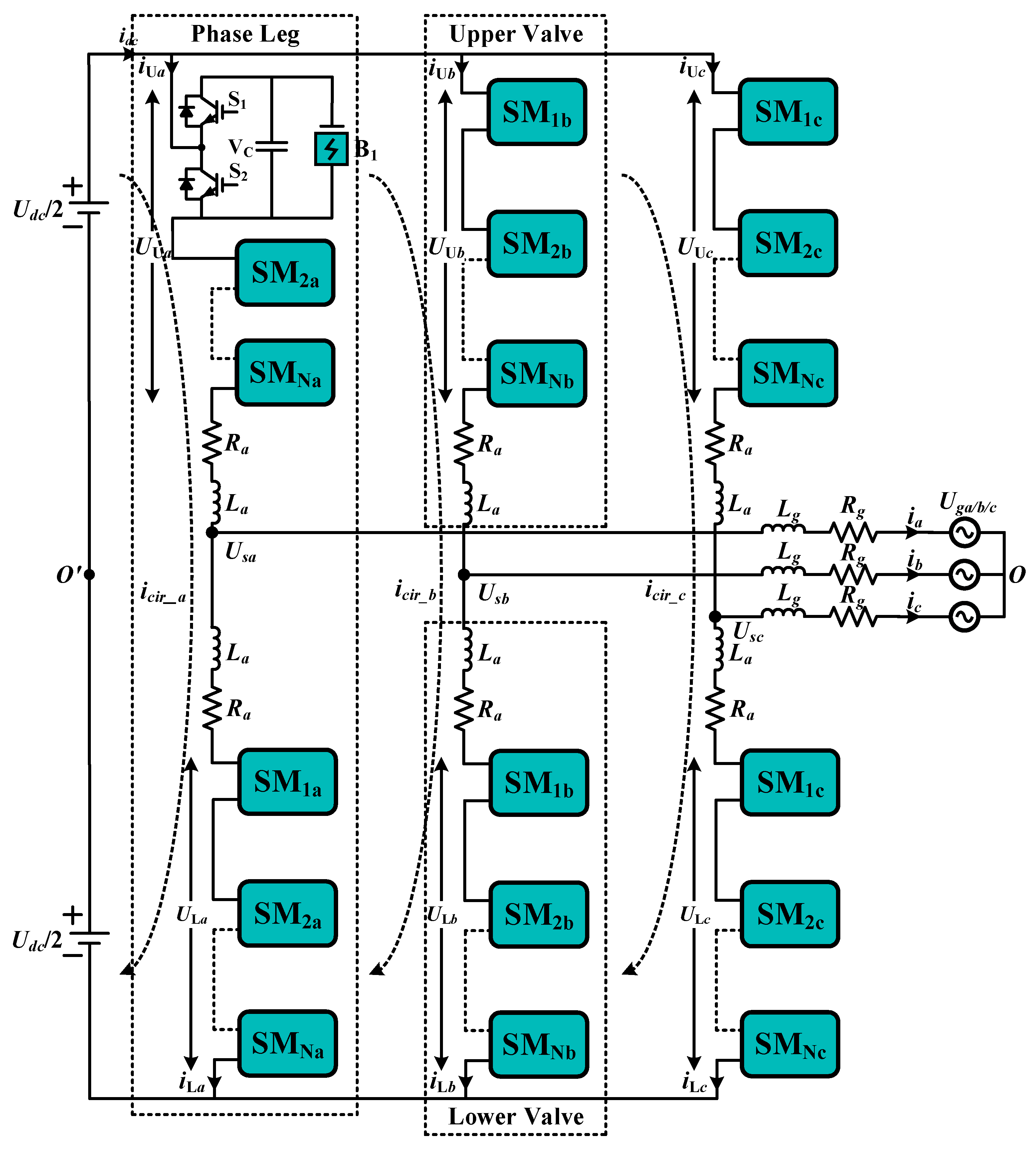

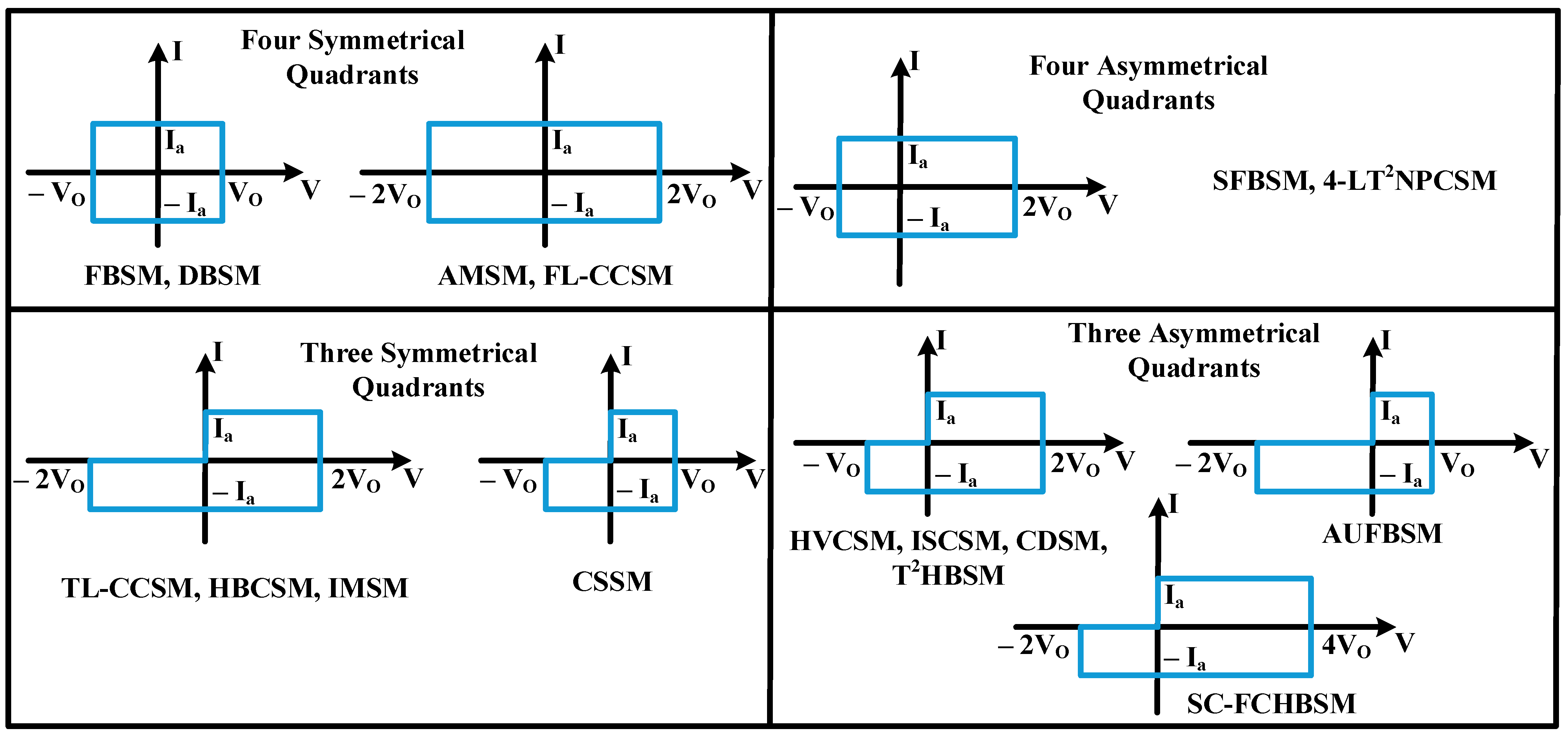

2. Submodule Topologies

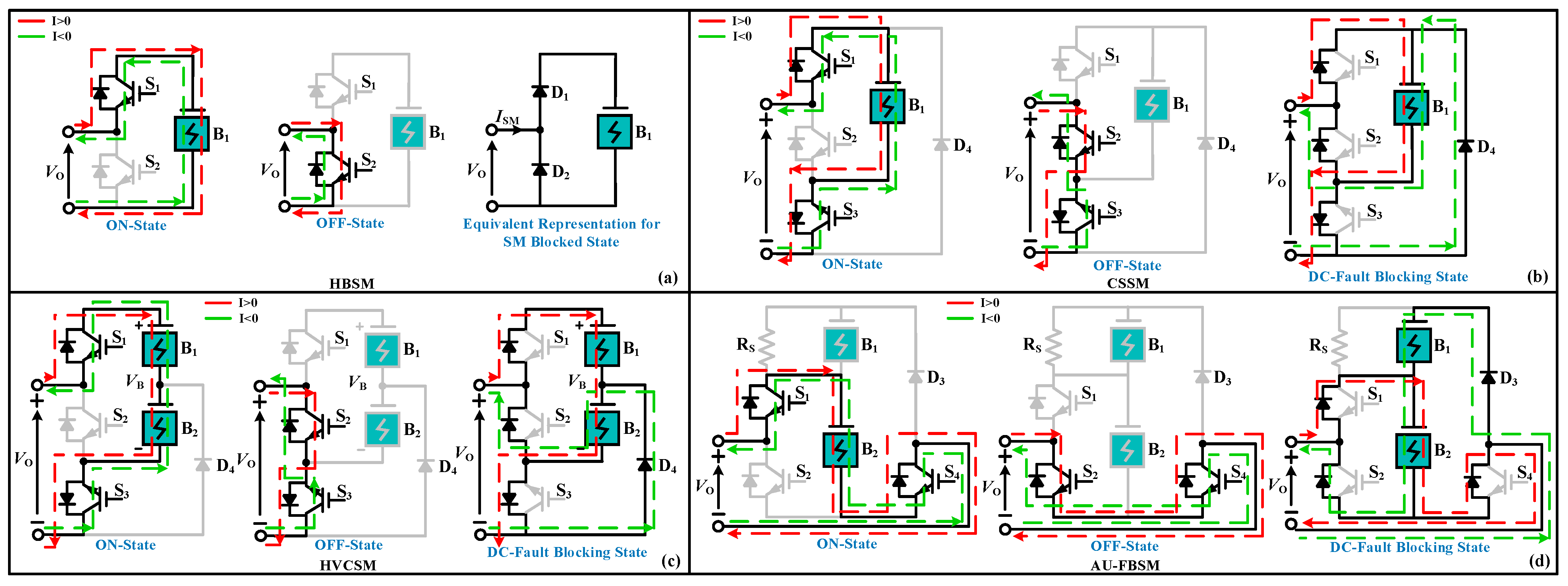

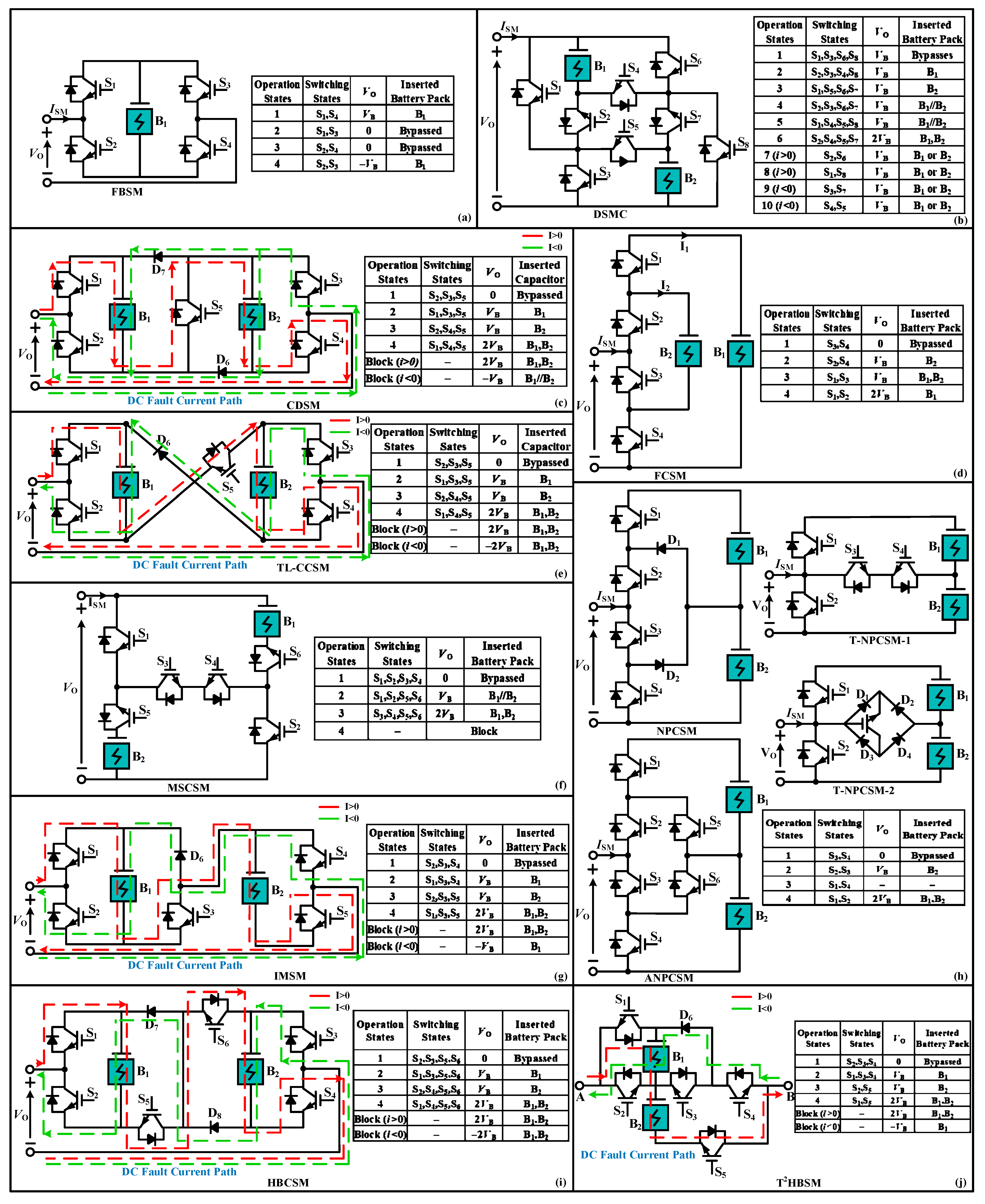

2.1. Two Level SMs

2.2. Three Level SMs

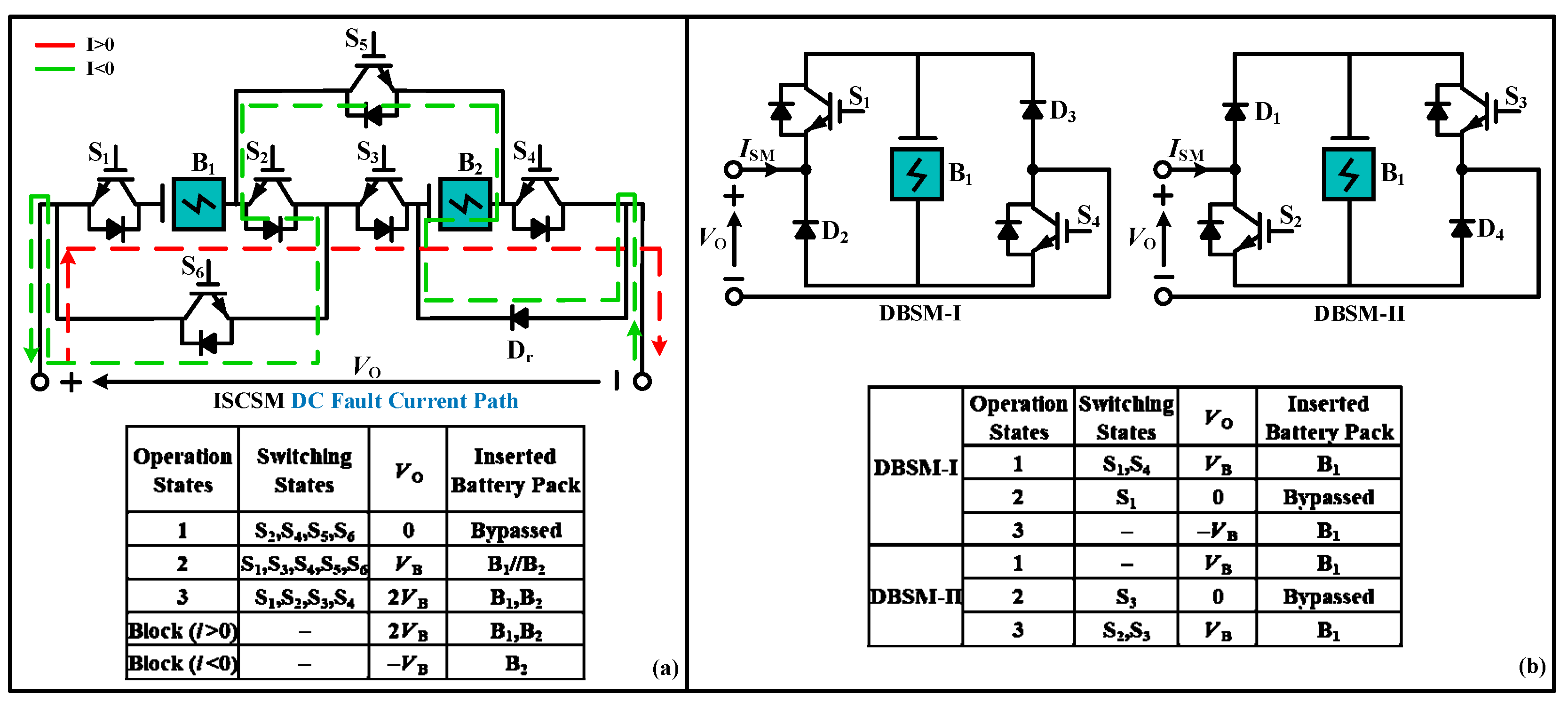

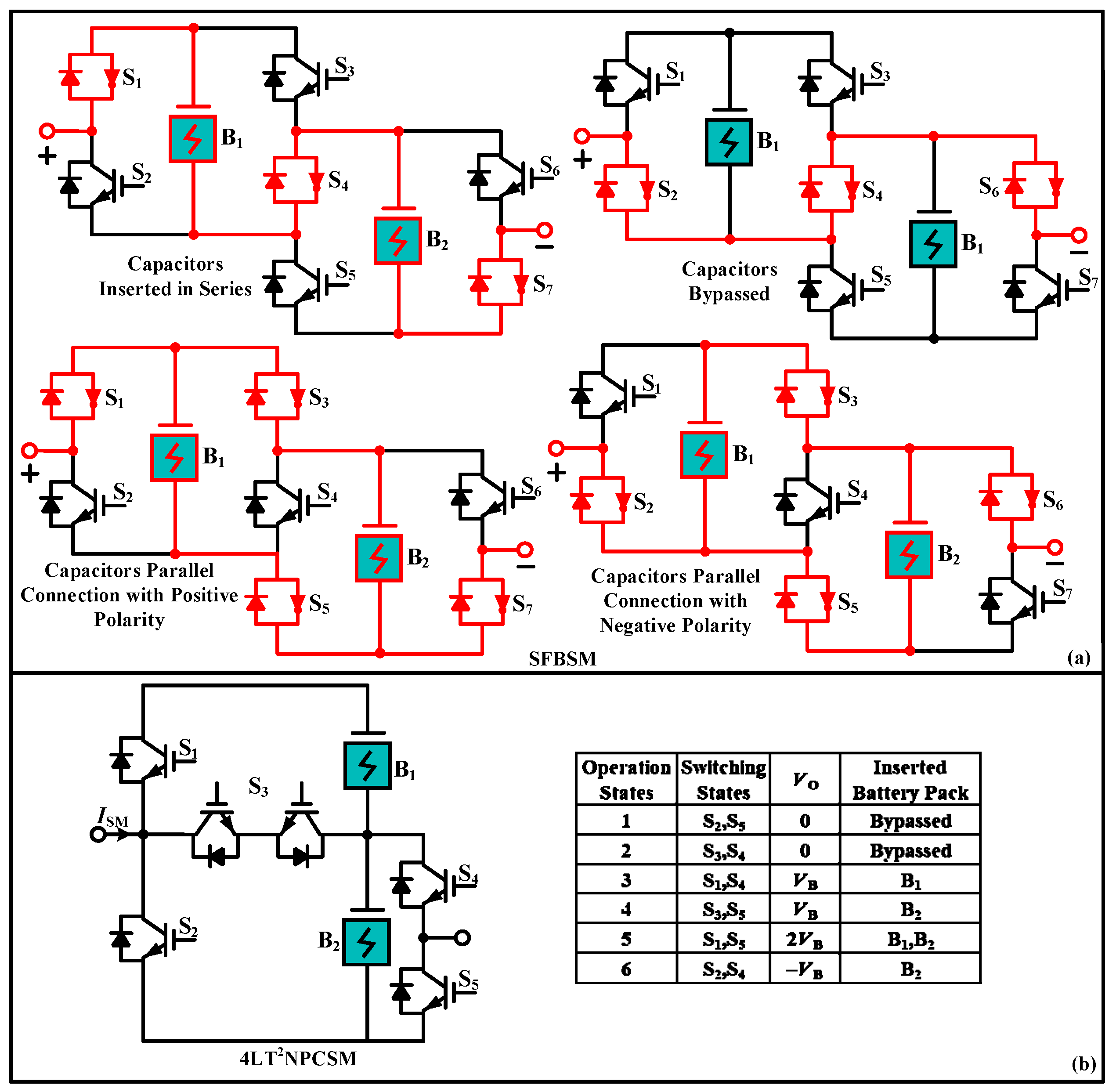

2.3. Four Level SMs

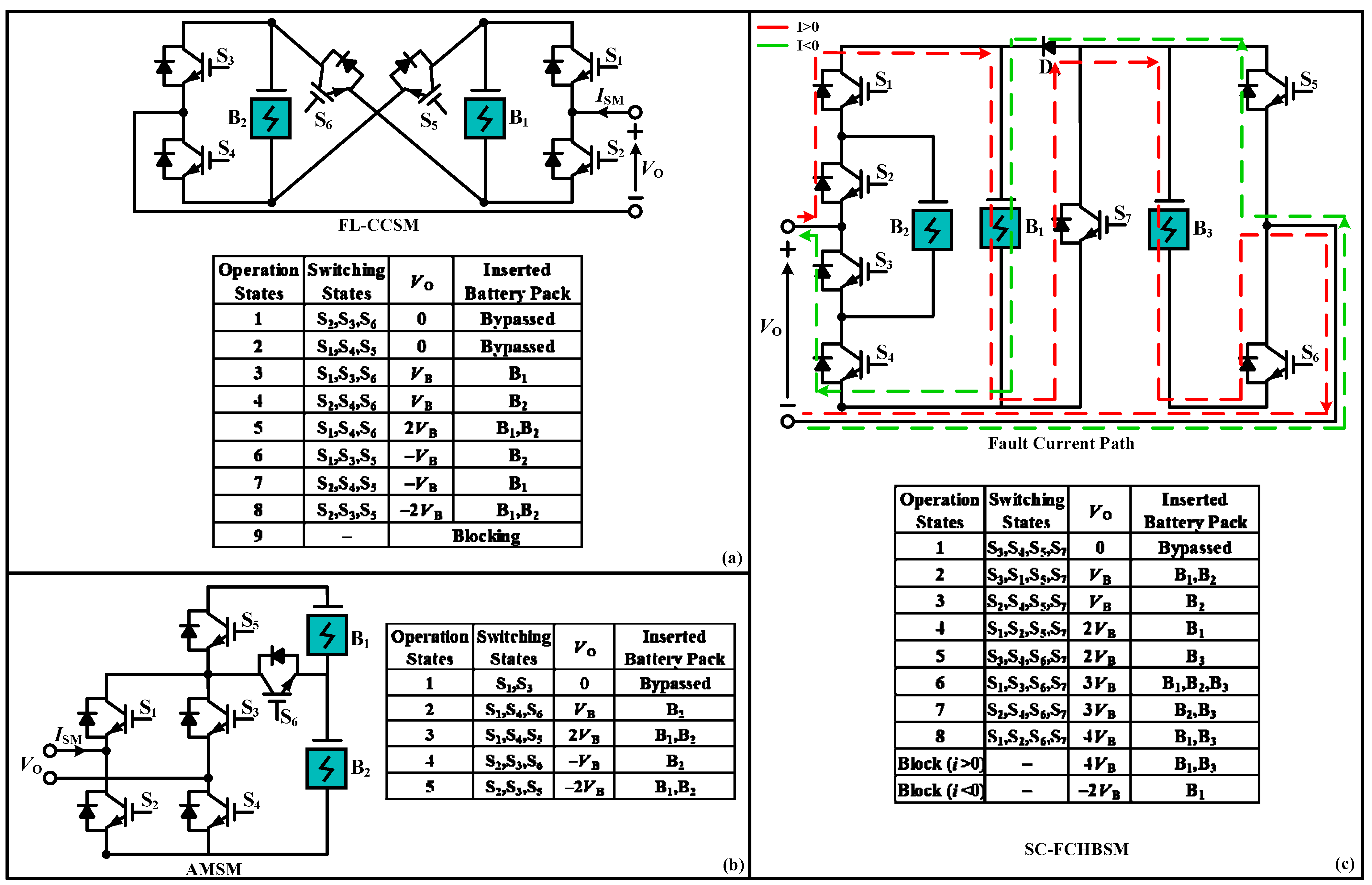

2.4. Five Level SMs

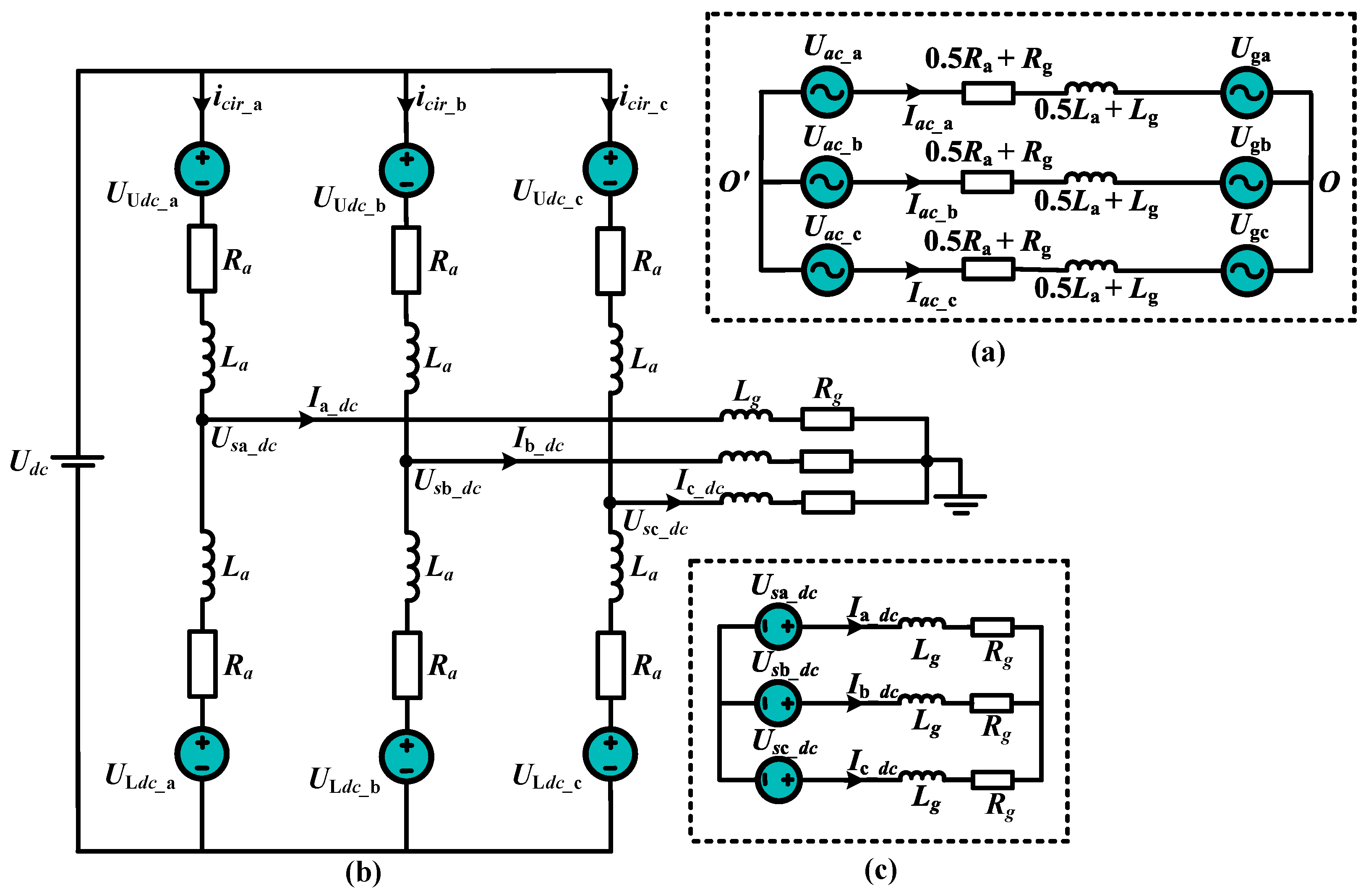

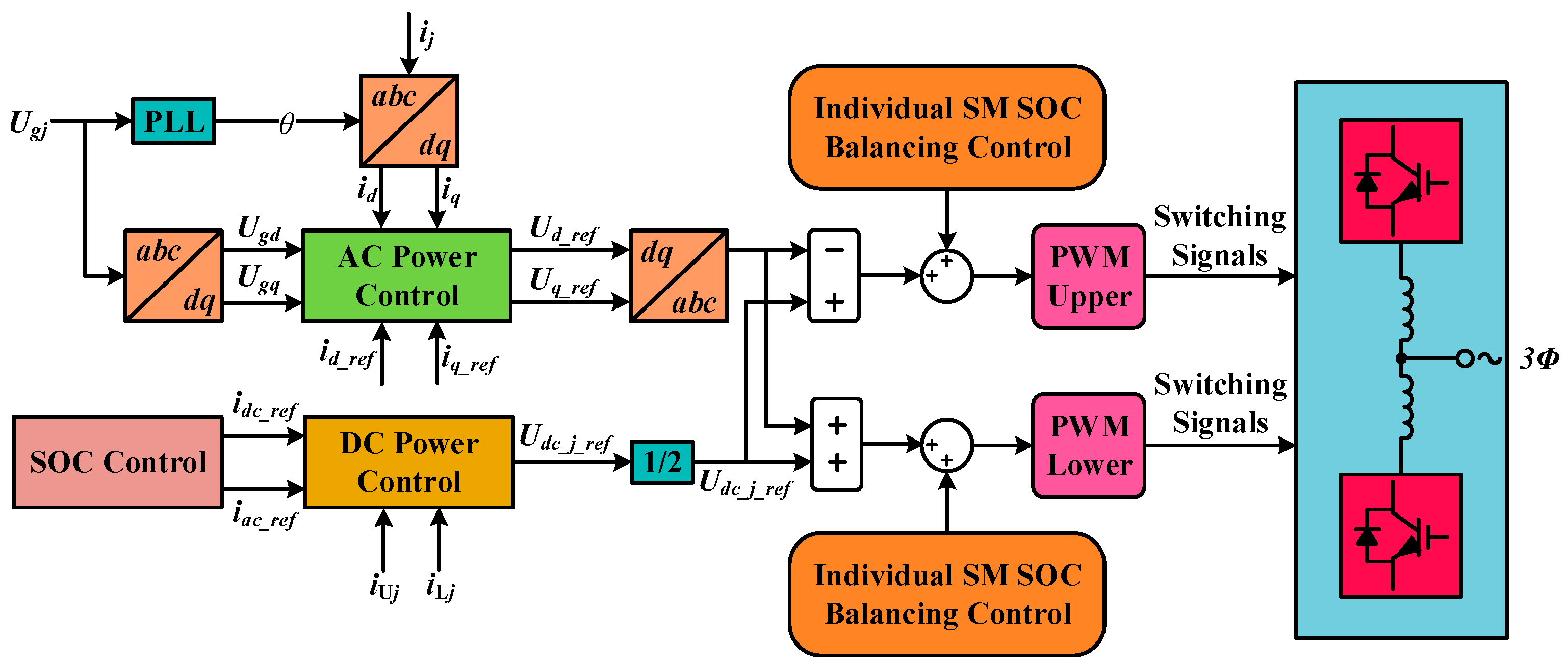

3. Power Flow and SOC Control Analysis of MMC-BESS with HBSM

3.1. AC and DC System Analysis

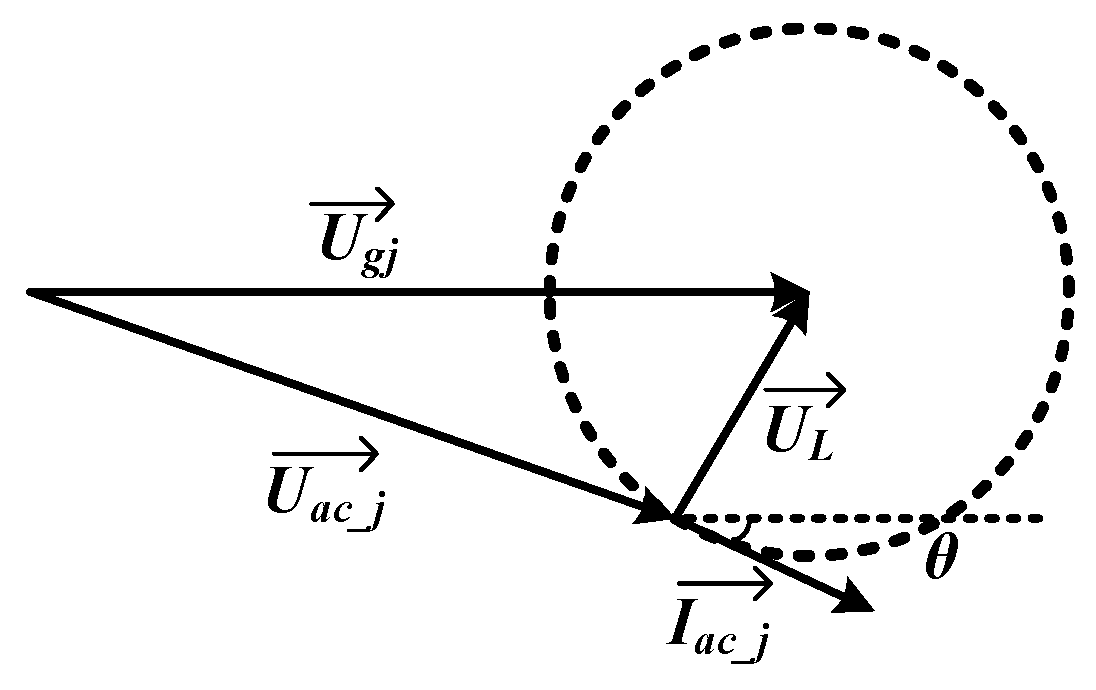

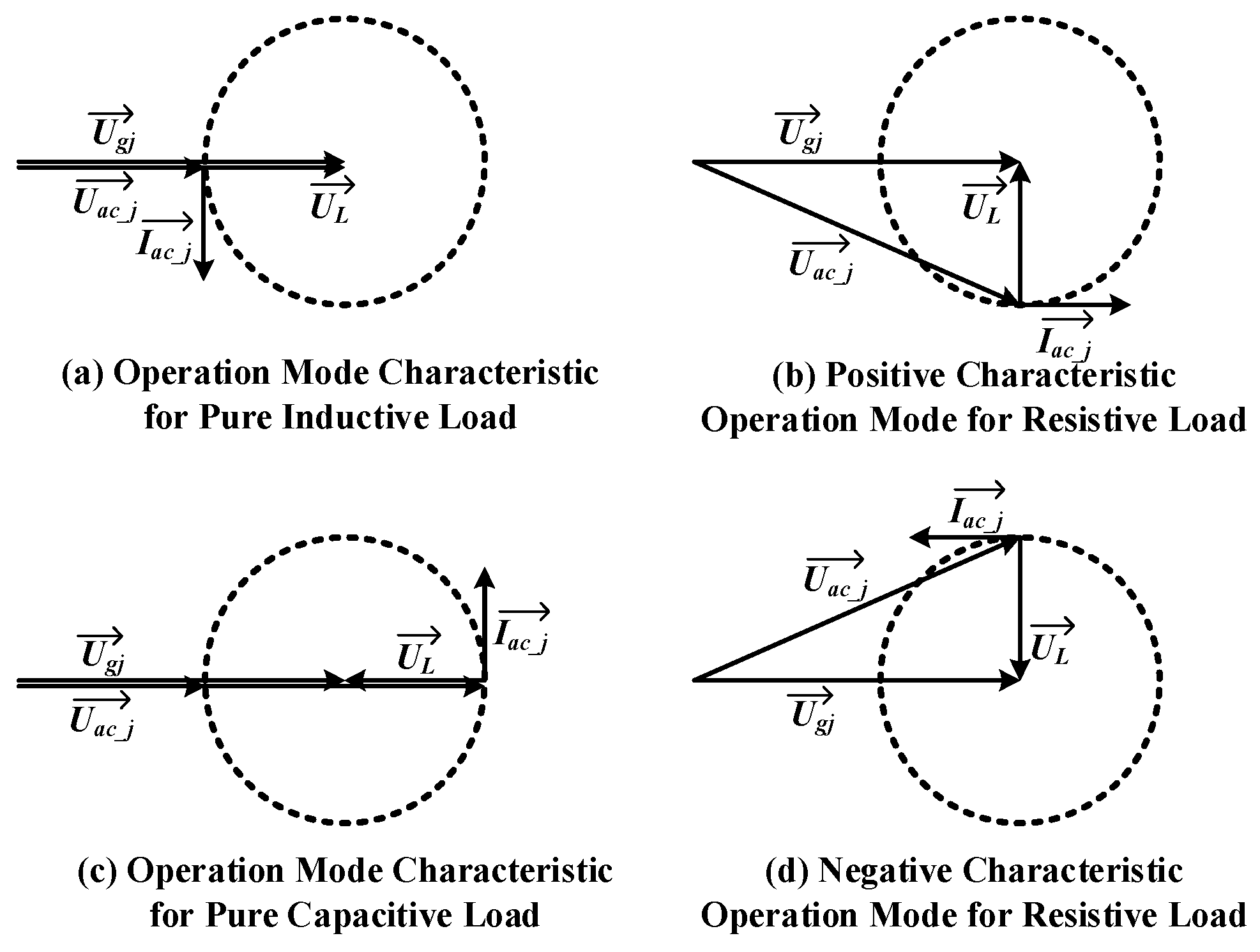

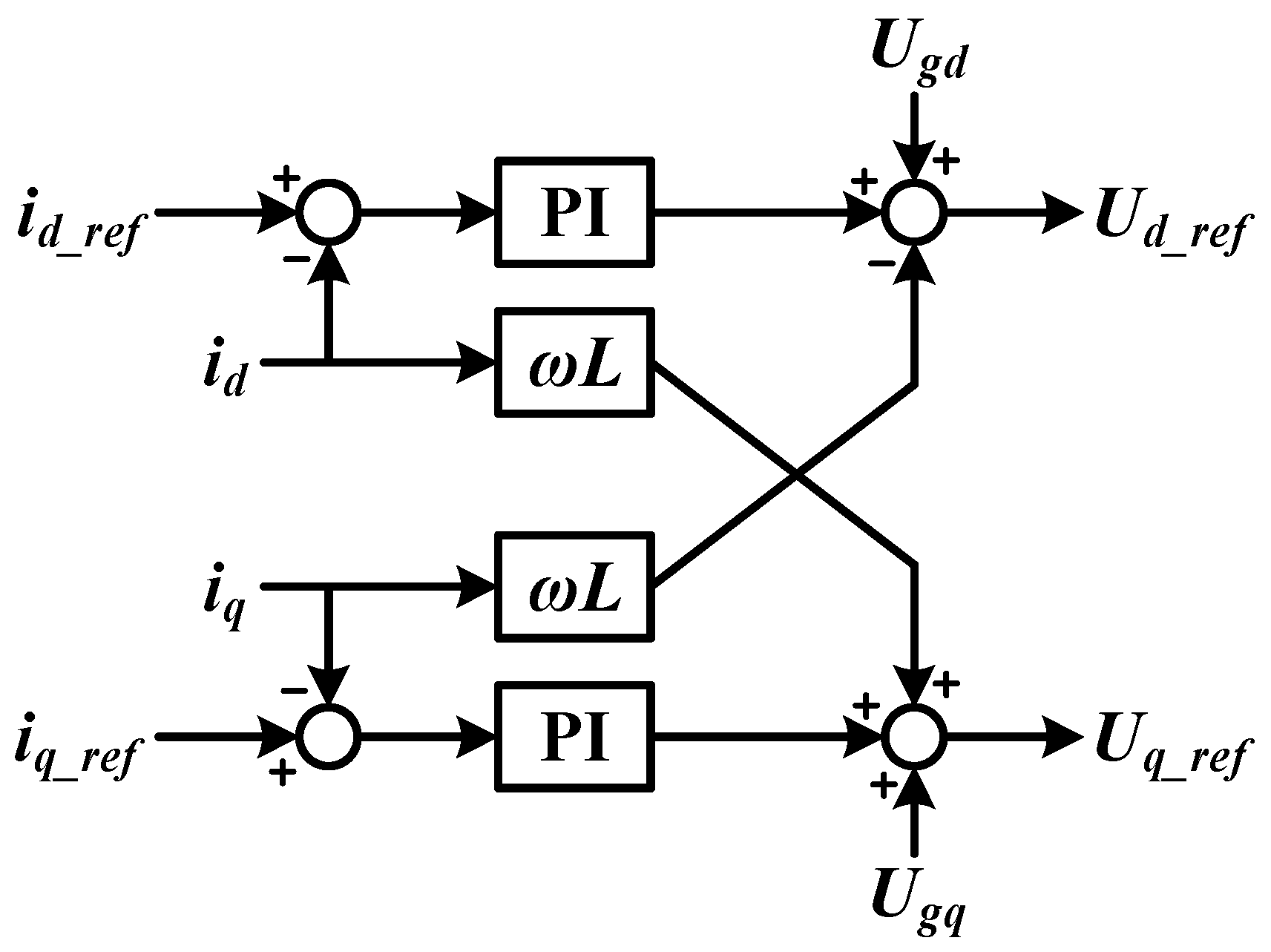

3.2. Power Control of MMC-BESS

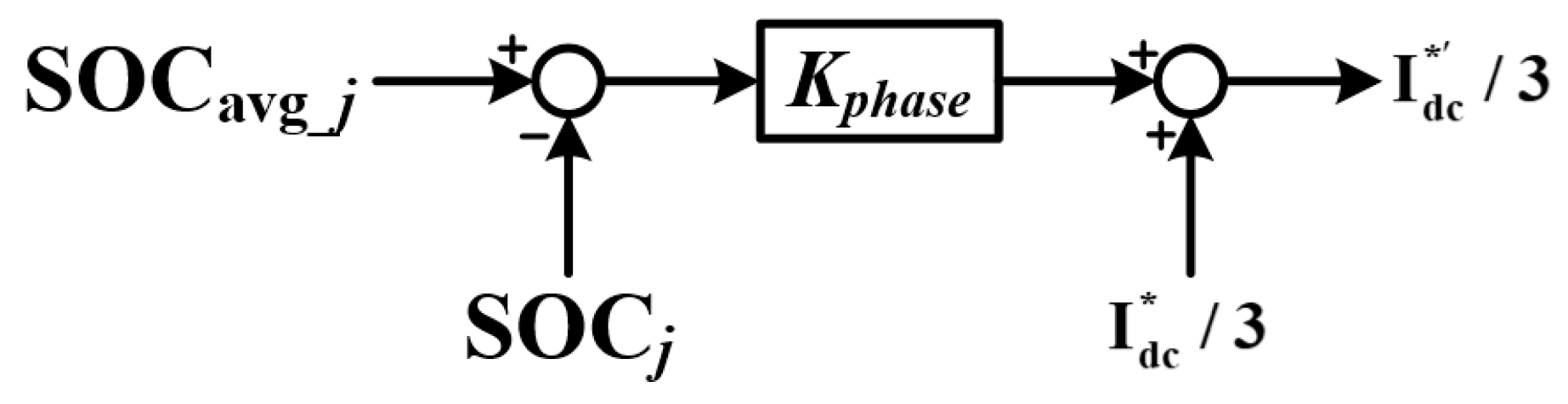

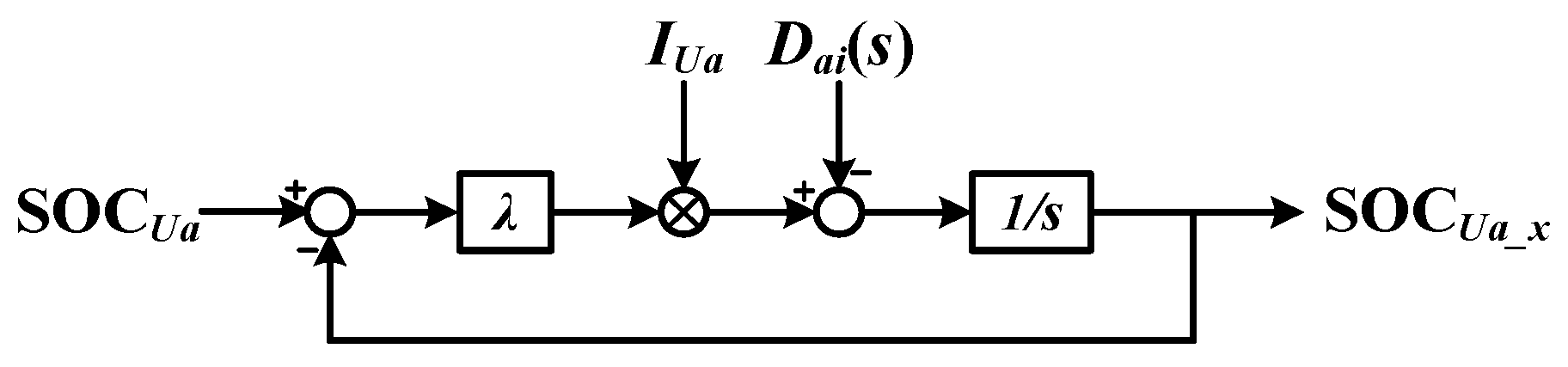

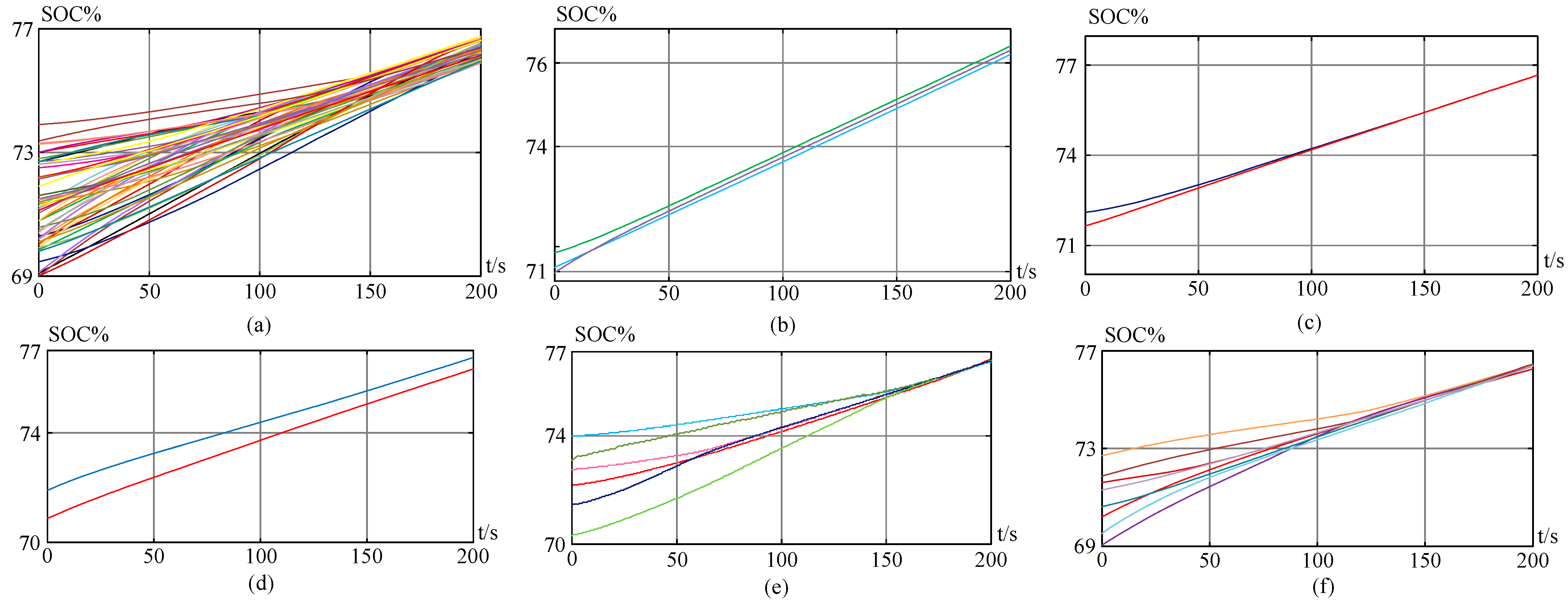

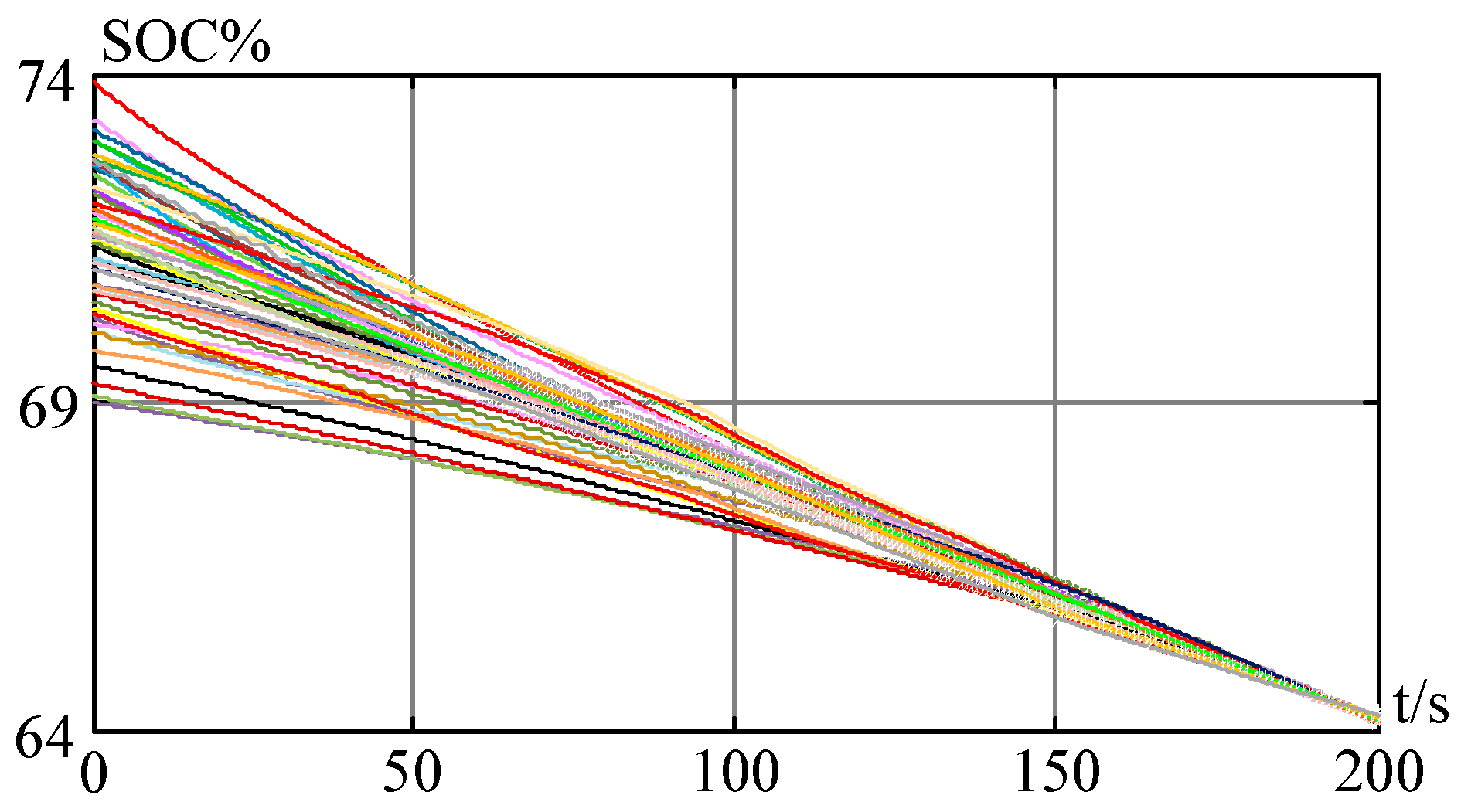

3.3. SOC Balancing

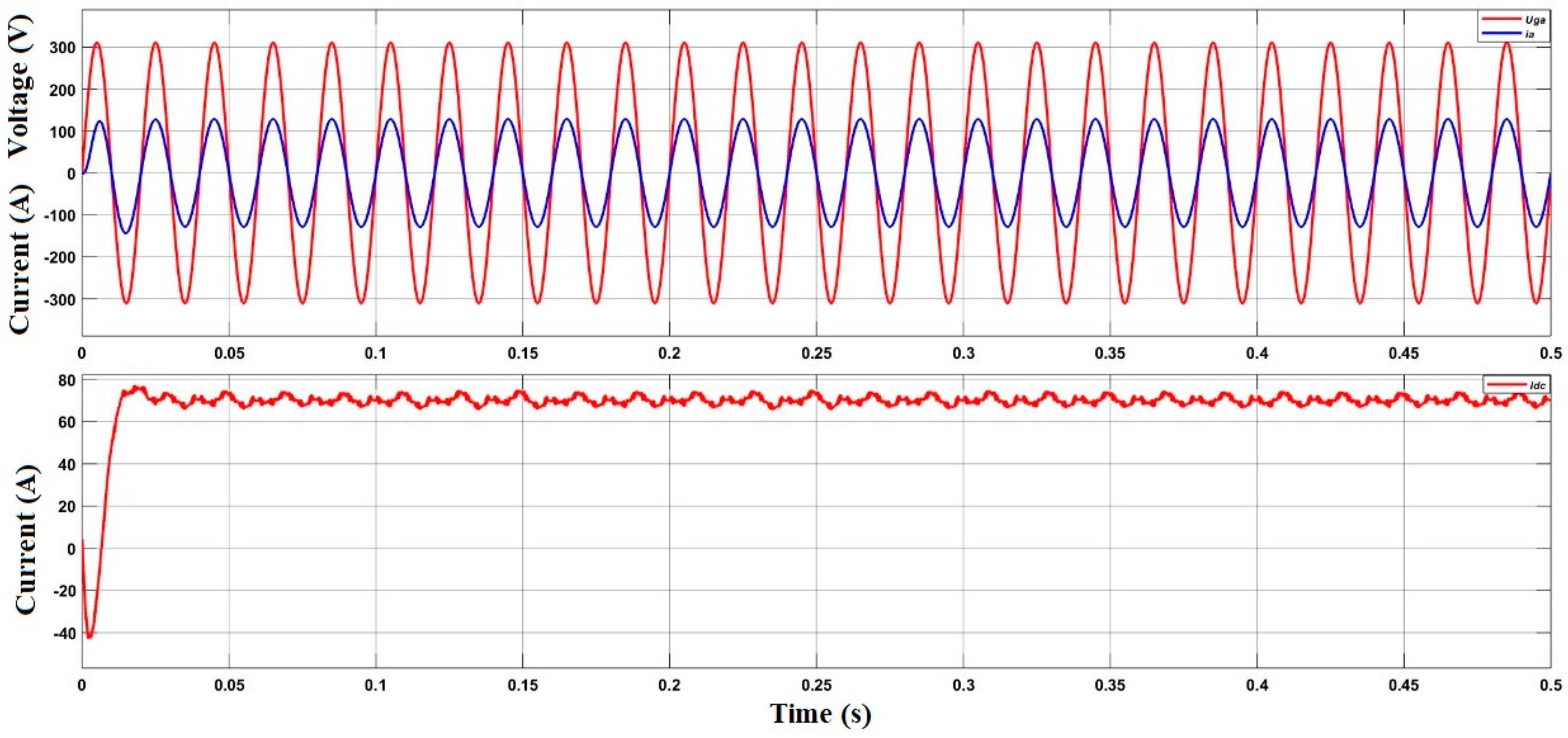

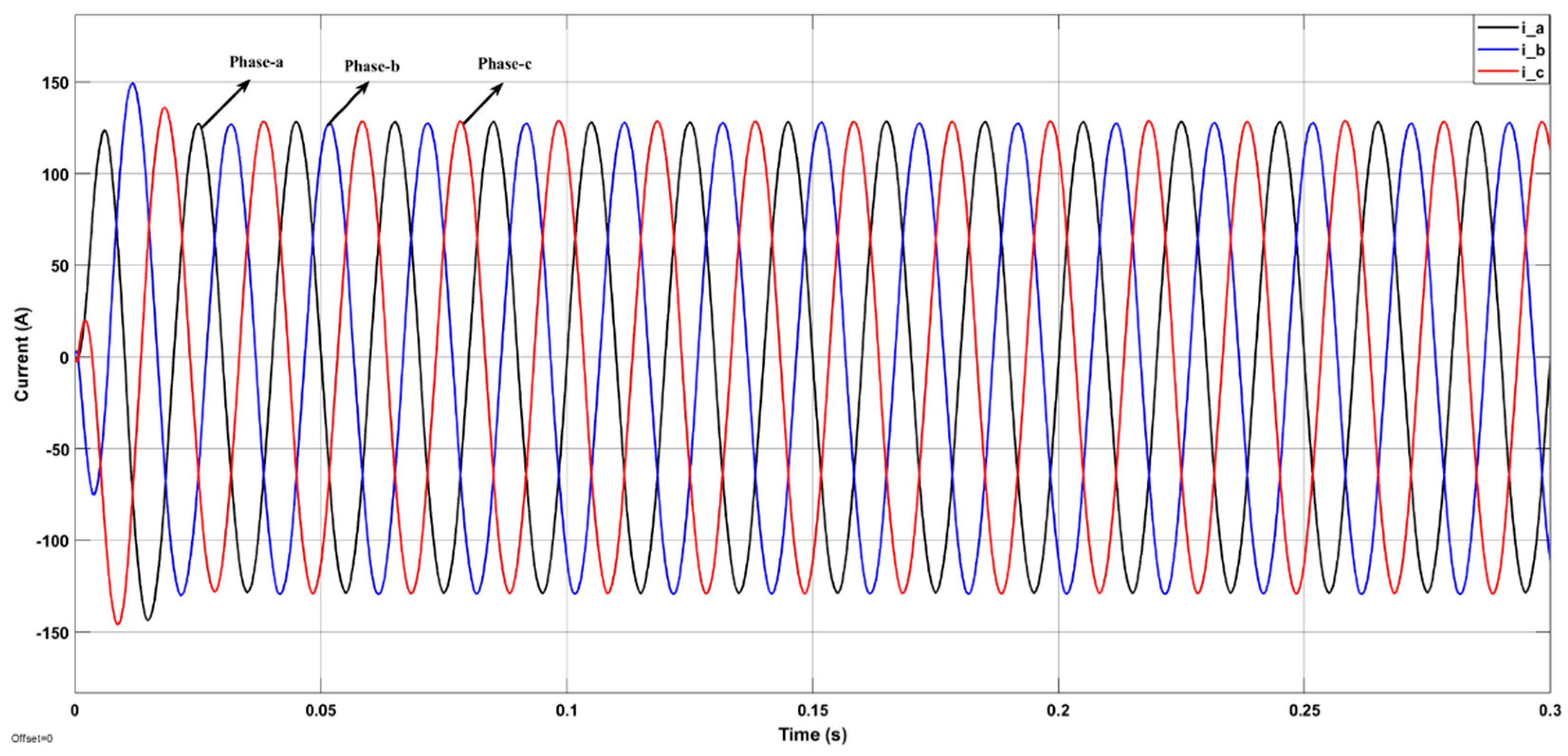

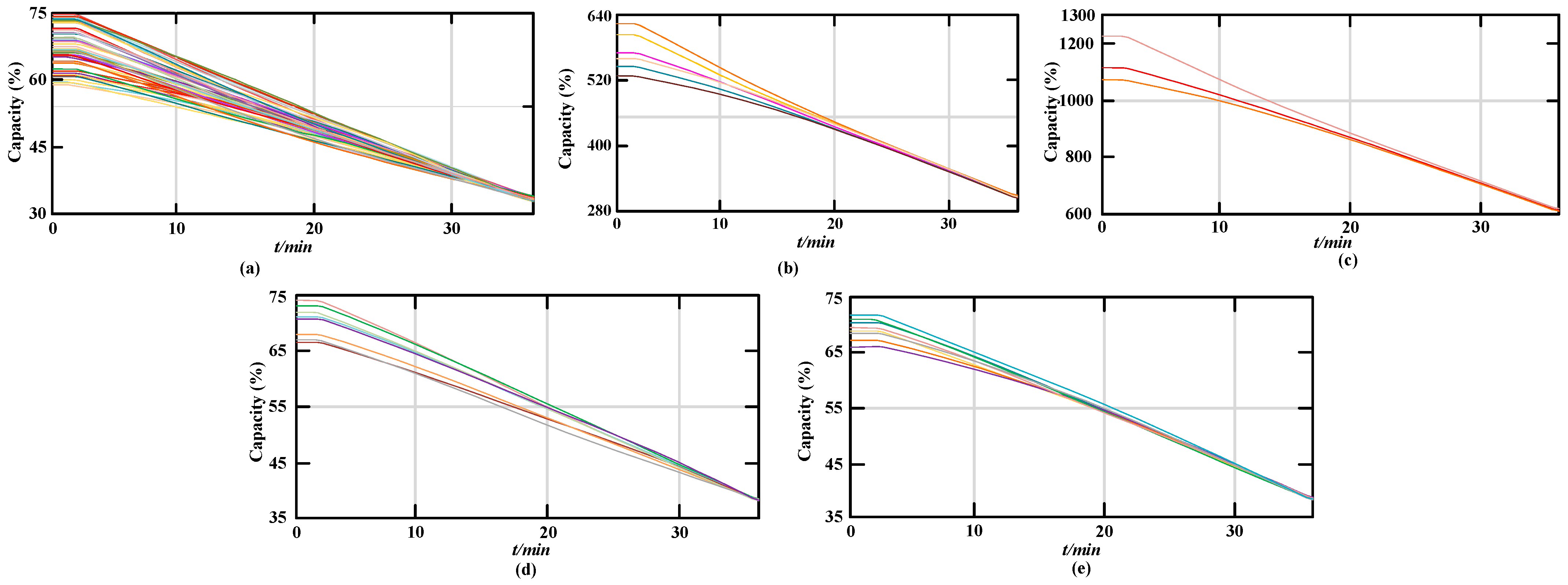

4. Simulation Results

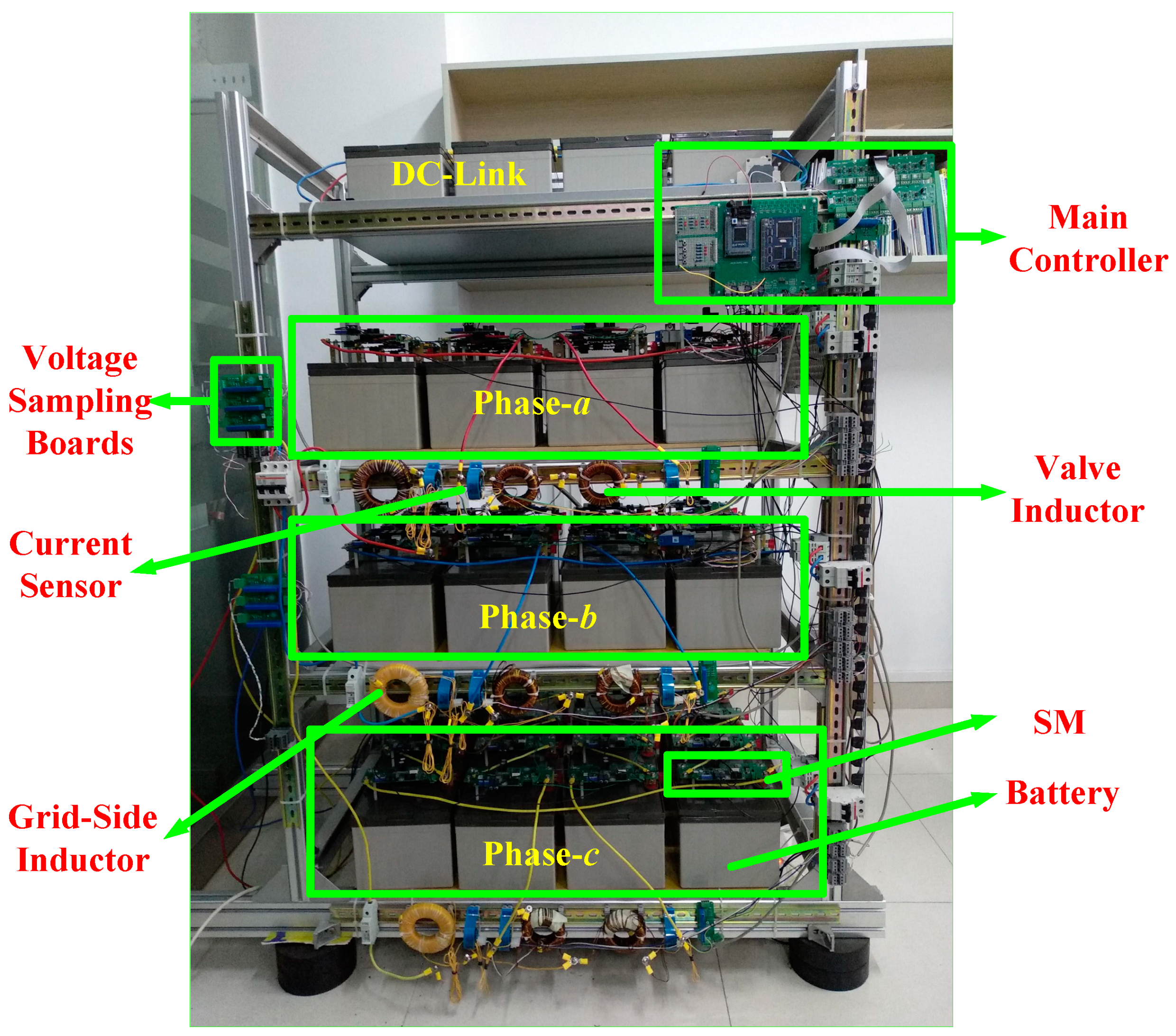

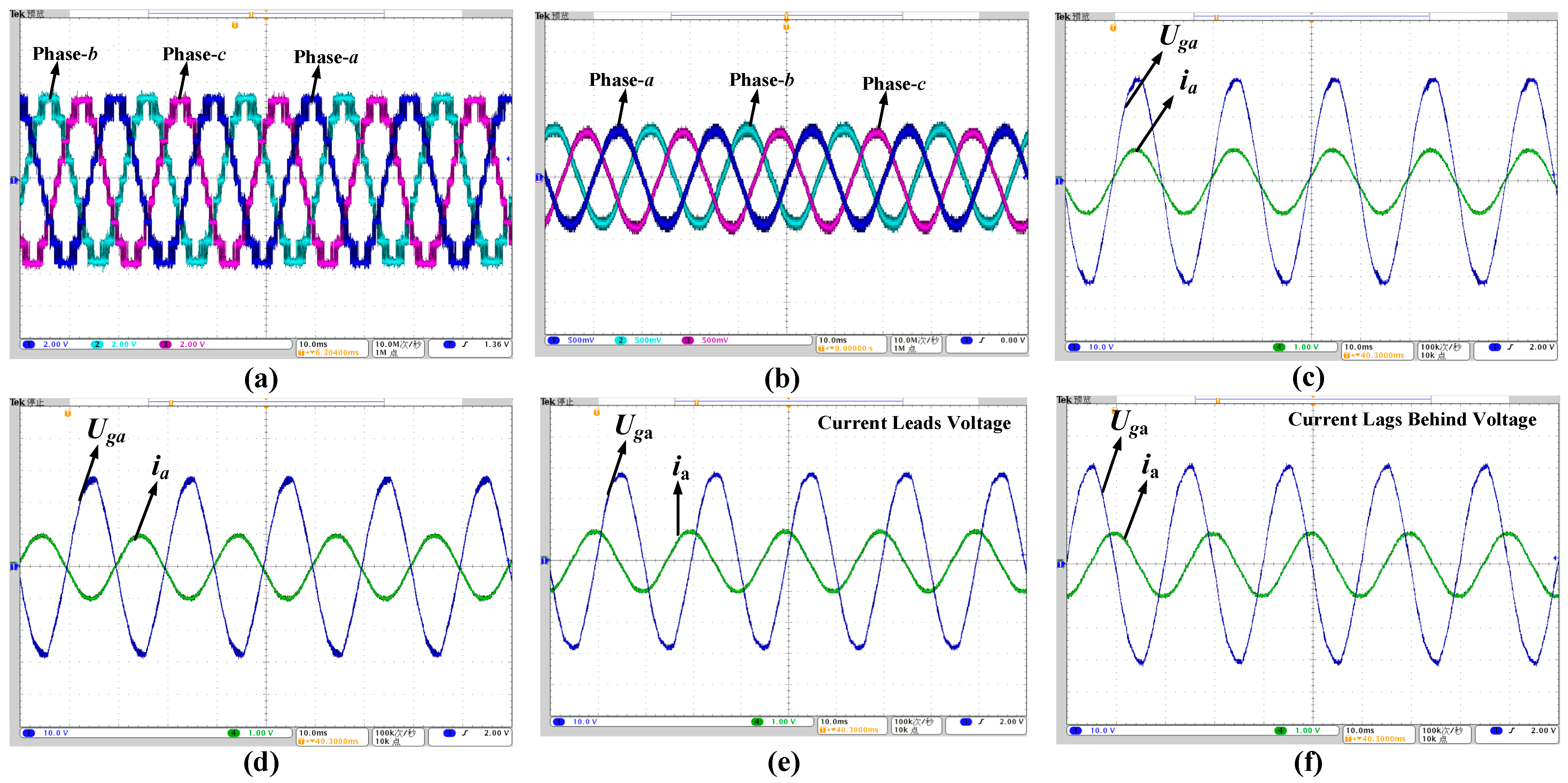

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviations

| BESS | Battery Energy Storage System |

| PCS | Power Conversion System |

| MMC | Modular Multilevel Converter |

| MMC-BESS-SBs | MMC-BESS with Secondary Batteries |

| SOC-BC | State of Charge Balancing Control |

| SMs | Submodules |

| CC | Control Complexity |

| HBSM | Half-Bridge Submodule |

| FBSM | Full-Bridge Submodule |

| CVR | Capacitor Voltage Ripple |

| CBs | Circuit Breakers |

| CSSM | Clamped Single Submodule |

| HVCSM | Half Voltage Clamped Submodule |

| AU-FBSM | Asymmetrical Unipolar Full-Bridge Submodule |

| DSMC | Double Submodule Circuit |

| SOH | State of Health |

| CDSM | Clamp-Double Submodule |

| FCSM | Flying Capacitor Submodule |

| TL-CCSM | Three Level Cross-Connected Submodule |

| MSCSM | Modified Switched Capacitor Submodule |

| ISCSM | Improved Switched Capacitor Submodule |

| IMSM | Improved Mixed Submodule |

| NPCSM | Neutral Point Clamped Submodule |

| ANPCSM | Active Neutral Point Clamped Submodule |

| T-NPCSM | T-Type Neural Point Clamped Submodule |

| HBCSM | Half-Bridge Clamp Submodule |

| T2HBSM | T-Type Half-Bridge based Submodule |

| ISCSM | Improved Switched Capacitor Submodule |

| DBSM | Diagonal Bridge Submodule |

| MMCSC | Modular Multilevel Current Source Converter |

| SFBSM | Semi-Full Bridge Submodule |

| 4-LT2NPCSM | 4-Level T-Type NPCSM |

| FL-CCSM | Five Level Cross-Connected Submodule |

| AMSM | Asymmetrical Mixed Submodule |

| SC-FCHBSM | Series Connected Flying Capacitor with Half Bridge Submodule |

| VLs | Voltage Levels |

| MBV | Maximum Blocking Voltage |

| TS | Total Switches |

| CS | Conduction Switches |

| NC | Number of Capacitor |

| AD | Additional Diode |

| DC-FHC | DC Fault Handling Capability |

| CD | Complexity of Design |

| SOC-BCC | State of Charge Balancing Control Complexity |

References

- Dell, R.M.; Rand, D.A.J. Energy Storage—A Key Technology for Global Energy Sustainability. J. Power Sources 2001, 100, 2–17. [Google Scholar] [CrossRef]

- Vasiladiotis, M.; Rufer, A. Analysis and Control of Modular Multilevel Converters With Integrated Battery Energy Storage. IEEE Trans. Power Electron. 2015, 30, 163–175. [Google Scholar] [CrossRef]

- Hadjipaschalis, I.; Poullikkas, A.; Efthimiou, V. Overview of Current and Future Energy Storage Technologies for Electric Power Applications. Renew. Sustain. Energy Rev. 2009, 13, 1513–1522. [Google Scholar] [CrossRef]

- Jafari, S.; Shahbazi, Z.; Byun, Y.-C. Lithium-Ion Battery Health Prediction on Hybrid Vehicles Using Machine Learning Approach. Energies 2022, 15, 4753. [Google Scholar] [CrossRef]

- Jafari, S.; Shahbazi, Z.; Byun, Y.; Lee, S.-J. Lithium-Ion Battery Estimation in Online Framework Using Extreme Gradient Boosting Machine Learning Approach. Mathematics 2022, 10, 888. [Google Scholar] [CrossRef]

- Soong, T.; Lehn, P.W. Evaluation of Emerging Modular Multilevel Converters for BESS Applications. IEEE Trans. Power Deliv. 2014, 29, 2086–2094. [Google Scholar] [CrossRef]

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Perez, M.A.; Leon, J.I. Recent Advances and Industrial Applications of Multilevel Converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Wu, B.; Pontt, J.O.; Kouro, S. Multilevel Voltage-Source-Converter Topologies for Industrial Medium-Voltage Drives. IEEE Trans. Ind. Electron. 2007, 54, 2930–2945. [Google Scholar] [CrossRef]

- Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Perez, M.A. A Survey on Cascaded Multilevel Inverters. IEEE Trans. Ind. Electron. 2010, 57, 2197–2206. [Google Scholar] [CrossRef]

- Tian, K.; Ali, S.; Huang, Z.; Ling, Z. Power Control and Experiment of 2MW/10kV Cascaded H-Bridge Power Conversion System for Battery Energy Storage System. In Proceedings of the 8th Renewable Power Generation Conference (RPG 2019), Shanghai, China, 24–25 October 2019; pp. 1–7. [Google Scholar] [CrossRef]

- Guan, M.; Xu, Z. Modeling and Control of a Modular Multilevel Converter-Based HVDC System Under Unbalanced Grid Conditions. IEEE Trans. Power Electron. 2012, 27, 4858–4867. [Google Scholar] [CrossRef]

- Ilves, K.; Antonopoulos, A.; Norrga, S.; Nee, H. A New Modulation Method for the Modular Multilevel Converter Allowing Fundamental Switching Frequency. In Proceedings of the 8th International Conference on Power Electronics—ECCE Asia, Jeju, Republic of Korea, 30 May–3 June 2011; pp. 991–998. [Google Scholar] [CrossRef]

- Lesnicar, A.; Marquardt, R. A New Modular Voltage Source Inverter Topology. In Proceedings of the EPE 2003, 10th European Conference on Power Electronics and Applications, Toulouse, France, 2–September 2003. [Google Scholar]

- Trintis, I.; Munk-Nielsen, S.; Teodorescu, R. A Ne4 w Modular Multilevel Converter with Integrated Energy Storage. In Proceedings of the IECON 2011—37th Annual Conference of the IEEE Industrial Electronics Society, Melbourne, VIC, Australia, 7–10 November 2011; pp. 1075–1080. [Google Scholar] [CrossRef]

- Perez, M.A.; Arancibia, D.; Kouro, S.; Rodriguez, J. Modular Multilevel Converter with Integrated Storage for Solar Photovoltaic Applications. In Proceedings of the IECON 2013—39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013; pp. 6993–6998. [Google Scholar] [CrossRef]

- Ali, S.; Ling, Z.; Tian, K.; Huang, Z. Recent Advancements in Submodule Topologies and Applications of MMC. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 3407–3435. [Google Scholar] [CrossRef]

- Neubauer, J.; Pesaran, A. The Ability of Battery Second Use Strategies to Impact Plug-in Electric Vehicle Prices and Serve Utility Energy Storage Applications. J. Power Sources 2011, 196, 10351–10358. [Google Scholar] [CrossRef]

- Ali, S.; Tian, K.; Huang, Z.; Ling, Z. Comparison of Modulation and Power Control between Modular Multilevel Converter Based Large Scale Battery Energy Storage System and MMC-HVDC. In Proceedings of the 8th International Conference on Renewable Power Generation, Shanghai, China, 24–25 October 2019. [Google Scholar] [CrossRef]

- Quraan, M.; Yeo, T.; Tricoli, P. Design and Control of Modular Multilevel Converters for Battery Electric Vehicles. IEEE Trans. Power Electron. 2016, 31, 507–517. [Google Scholar] [CrossRef]

- Xu, B.; Tu, H.; Du, Y.; Yu, H.; Liang, H.; Lukic, S. A Distributed Control Architecture for Cascaded H-Bridge Converter With Integrated Battery Energy Storage. IEEE Trans. Ind. Appl. 2021, 57, 845–856. [Google Scholar] [CrossRef]

- Mukherjee, N.; Strickland, D. Analysis and Comparative Study of Different Converter Modes in Modular Second-Life Hybrid Battery Energy Storage Systems. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 547–563. [Google Scholar] [CrossRef]

- Huang, Z.; Tian, K.; Ali, S.; Ling, Z. Analysis and Comparison of Power Quality and Inter-Phase Circulation for One-Stage and Two-Stage Modular Battery Energy Storage System. In Proceedings of the 8th Renewable Power Generation Conference (RPG 2019), Shanghai, China, 24–25 October 2019; pp. 1–7. [Google Scholar] [CrossRef]

- Chen, Q.; Li, R.; Cai, X. Analysis and Fault Control of Hybrid Modular Multilevel Converter With Integrated Battery Energy Storage System. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 64–78. [Google Scholar] [CrossRef]

- Zhao, P.; Wang, C.; Xu, J.; Zong, B.; Zhao, C. A Sub-Module Topology of Mmc with DC Fault Ride-through Capability. Power Syst. Technol. 2014, 38, 3441–3446. [Google Scholar] [CrossRef]

- Xu, J.; Zhao, P.; Zhao, C. Reliability Analysis and Redundancy Configuration of MMC With Hybrid Submodule Topologies. IEEE Trans. Power Electron. 2016, 31, 2720–2729. [Google Scholar] [CrossRef]

- Li, X.; Liu, W.; Song, Q.; Rao, H.; Xu, S. An Enhanced MMC Topology with DC Fault Ride-through Capability. In Proceedings of the IECON 2013—39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013; pp. 6182–6188. [Google Scholar] [CrossRef]

- Konstantinou, G.; Zhang, J.; Ceballos, S.; Pou, J.; Agelidis, V.G. Comparison and Evaluation of Sub-Module Configurations in Modular Multilevel Converters. In Proceedings of the 2015 IEEE 11th International Conference on Power Electronics and Drive Systems, Sydney, NSW, Australia, 9–12 June 2015; pp. 958–963. [Google Scholar] [CrossRef]

- Kim, H.; Kang, J.; Kim, S.; Kim, C.; Hur, K. DC Fault Protection for Modular Multilevel Converter HVDC Using Asymmetrical Unipolar Full-Bridge Submodule. In Proceedings of the 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Sapporo, Japan, 21–24 June 2015; pp. 1083–1089. [Google Scholar] [CrossRef]

- Zeng, R.; Xu, L.; Yao, L.; Williams, B.W. Design and Operation of a Hybrid Modular Multilevel Converter. IEEE Trans. Power Electron. 2015, 30, 1137–1146. [Google Scholar] [CrossRef]

- Marquardt, R. Modular Multilevel Converter: An Universal Concept for HVDC-Networks and Extended DC-Bus-Applications. In Proceedings of the The 2010 International Power Electronics Conference—ECCE ASIA, Sapporo, Japan, 21–24 June 2010; pp. 502–507. [Google Scholar] [CrossRef]

- Lebre, J.R.; Watanabe, E.H. Fullbridge MMC Control for Hybrid HVDC Systems. In Proceedings of the 2017 Brazilian Power Electronics Conference (COBEP), Juiz de Fora, Brazil, 19–22 November 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Ilves, K.; Taffner, F.; Norrga, S.; Antonopoulos, A.; Harnefors, L.; Nee, H. A Submodule Implementation for Parallel Connection of Capacitors in Modular Multilevel Converters. In Proceedings of the 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 3–5 September 2013; pp. 1–10. [Google Scholar] [CrossRef]

- Marquardt, R. Modular Multilevel Converter Topologies with DC-Short Circuit Current Limitation. In Proceedings of the 8th International Conference on Power Electronics—ECCE Asia, Jeju, Republic of Korea, 30 May–3 June 2011; pp. 1425–1431. [Google Scholar] [CrossRef]

- Qin, J.; Saeedifard, M.; Rockhill, A.; Zhou, R. Hybrid Design of Modular Multilevel Converters for HVDC Systems Based on Various Submodule Circuits. IEEE Trans. Power Deliv. 2015, 30, 385–394. [Google Scholar] [CrossRef]

- Grégoire, L.; Blanchette, H.F.; Li, W.; Antonopoulos, A.; Ängquist, L.; Al-Haddad, K. Modular Multilevel Converters Overvoltage Diagnosis and Remedial Strategy During Blocking Sequences. IEEE Trans. Power Electron. 2015, 30, 2777–2785. [Google Scholar] [CrossRef]

- Dekka, A.; Wu, B.; Zargari, N.R.; Fuentes, R.L. Dynamic Voltage Balancing Algorithm for Modular Multilevel Converter: A Unique Solution. IEEE Trans. Power Electron. 2016, 31, 952–963. [Google Scholar] [CrossRef]

- Lizana, R.; Perez, M.; Dekka, A.; Wu, B. Capacitor Voltage Balancing Method for Modular Multilevel Converter with Flying Capacitor Submodules. In Proceedings of the 2017 IEEE International Conference on Industrial Technology (ICIT), Toronto, ON, Canada, 22–25 March 2017; pp. 60–65. [Google Scholar] [CrossRef]

- Sallam, A.; Hamdy, R.A.R.; Moustafa, M.M.Z.; Hossam-Eldin, A. New Topology for Three-Level Modified Switched Capacitor Submodule for Modular Multilevel Converter with DC Fault Blocking Capability. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; pp. 1–9. [Google Scholar] [CrossRef]

- Zhang, J.; Zhao, C.; Guo, L. Simulation Analysis on Submodule Topology of Modular Multilevel Converter. Autom. Electr. Power Syst. 2015, 39, 106–111. [Google Scholar] [CrossRef]

- Solas, E.; Abad, G.; Barrena, J.A.; Aurtenetxea, S.; Cárcar, A.; Zając, L. Modular Multilevel Converter With Different Submodule Concepts—Part I: Capacitor Voltage Balancing Method. IEEE Trans. Ind. Electron. 2013, 60, 4525–4535. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A Survey on Neutral-Point-Clamped Inverters. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Barbosa, P.; Steimer, P.; Meysenc, L.; Winkelnkemper, M.; Steinke, J.; Celanovic, N. Active Neutral-Point-Clamped Multilevel Converters. In Proceedings of the 2005 IEEE 36th Power Electronics Specialists Conference, Dresden, Germany, 16 June 2005; pp. 2296–2301. [Google Scholar] [CrossRef]

- Bruckner, T.; Bemet, S. Loss Balancing in Three-Level Voltage Source Inverters Applying Active NPC Switches. In Proceedings of the 2001 IEEE 32nd Annual Power Electronics Specialists Conference (IEEE Cat. No.01CH37230), Vancouver, BC, Canada, 17–21 June 2001; Volume 2, pp. 1135–1140. [Google Scholar] [CrossRef]

- Soeiro, T.B.; Kolar, J.W. Novel 3-Level Hybrid Neutral-Point-Clamped Converter. In Proceedings of the IECON 2011—37th Annual Conference of the IEEE Industrial Electronics Society, Melbourne, VIC, Australia, 7–10 November 2011; pp. 4457–4462. [Google Scholar] [CrossRef]

- Sahoo, A.K.; Otero-De-Leon, R.; Chandrasekaran, V.; Mohan, N. New 3-Level Submodules for a Modular Multilevel Converter Based HVDC System with Advanced Features. In Proceedings of the IECON 2013—39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013; pp. 6269–6274. [Google Scholar] [CrossRef]

- Nami, A.; Adabi, J. A New T-Type NPC-Based Submodule for Modular Multilevel Cascaded Converters. In Proceedings of the The 5th Annual International Power Electronics, Drive Systems and Technologies Conference (PEDSTC 2014), Tehran, Iran, 5–6 February 2014; pp. 137–142. [Google Scholar] [CrossRef]

- Zhao, F.; Xiao, G.; Yang, D.; Liu, M.; Han, X.; Liu, B. A Novel T-Type Half-Bridge Cell for Modular Multilevel Converter with DC Fault Blocking Capability. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–6. [Google Scholar] [CrossRef]

- Elserougi, A.A.; Massoud, A.M.; Ahmed, S. A Switched-Capacitor Submodule for Modular Multilevel HVDC Converters With DC-Fault Blocking Capability and a Reduced Number of Sensors. IEEE Trans. Power Deliv. 2016, 31, 313–322. [Google Scholar] [CrossRef]

- Yu, X.; Wei, Y.; Jiang, Q. New Submodule Circuits for Modular Multilevel Current Source Converters with DC Fault Ride through Capability. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 1468–1474. [Google Scholar] [CrossRef]

- Ilves, K.; Bessegato, L.; Harnefors, L.; Norrga, S.; Nee, H. Semi-Full-Bridge Submodule for Modular Multilevel Converters. In Proceedings of the 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Seoul, Republic of Korea, 1–5 June 2015; pp. 1067–1074. [Google Scholar] [CrossRef]

- Nami, A.; Wang, L.; Dijkhuizen, F.; Shukla, A. Five Level Cross Connected Cell for Cascaded Converters. In Proceedings of the 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 2–6 September 2013; pp. 1–9. [Google Scholar] [CrossRef]

- Mondal, G.; Nielebock, S. Reduced Switch Count 5-Level Modules for Modular Multi-Level Converters. In Proceedings of the IECON 2018-44th Annual Conference of the IEEE Industrial Electronics Society, Washington, DC, USA, 21–23 October 2018. [Google Scholar] [CrossRef]

- Lizana, R.; Dekka, A.; Rivera, S.; Wu, B. Modular Multilevel Converter Based on 5-Level Submodule with DC Fault Blocking Capability. In Proceedings of the IECON 2016—42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 23–26 October 2016; pp. 3482–3487. [Google Scholar] [CrossRef]

- Zhang, L.; Gao, F.; Li, N.; Zhang, Q.; Wang, C. Interlinking Modular Multilevel Converter of Hybrid AC-DC Distribution System with Integrated Battery Energy Storage. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 70–77. [Google Scholar] [CrossRef]

- Quraan, M.; Tricoli, P.; D’Arco, S.; Piegari, L. Efficiency Assessment of Modular Multilevel Converters for Battery Electric Vehicles. IEEE Trans. Power Electron. 2017, 32, 2041–2051. [Google Scholar] [CrossRef]

- Diao, W.; Jiang, J.; Zhang, C.; Liang, H.; Pecht, M. Energy State of Health Estimation for Battery Packs Based on the Degradation and Inconsistency. Energy Procedia 2017, 142, 3578–3583. [Google Scholar] [CrossRef]

- Hillers, A.; Biela, J. Fault-Tolerant Operation of the Modular Multilevel Converter in an Energy Storage System Based on Split Batteries. In Proceedings of the 2014 16th European Conference on Power Electronics and Applications, Lappeenranta, Finland, 26–28 August 2014; pp. 1–8. [Google Scholar] [CrossRef]

- Liang, H.; Guo, L.; Song, J.; Yang, Y.; Zhang, W.; Qi, H. State-of-Charge Balancing Control of a Modular Multilevel Converter with an Integrated Battery Energy Storage. Energies 2018, 11, 873. [Google Scholar] [CrossRef]

| SM Type | VLs | MBV | TS | CS | NC | AD | DC-FHC | CD | CC | SOC-BCC |

|---|---|---|---|---|---|---|---|---|---|---|

| HBSM | 2 | VB | 2 | 1 | 1 | 0 | No | Low | Low | Low |

| CSSM | 2 | VB | 3 | 2 | 1 | 1 | Yes | Low | Low | Low |

| HVCSM | 2 | 2VB | 3 | 2 | 2 | 1 | Yes | Moderate | Moderate | Complex |

| AU-FBSM | 2 | VB | 3 | 2 | 2 | 1 | Yes | Moderate | Moderate | Complex |

| FBSM | 3 | VB | 4 | 2 | 1 | 0 | Yes | Low | Low | Low |

| DSMC | 3 | 2VB | 8 | 4 | 2 | 0 | Yes | Moderate | Moderate | Moderate |

| CDSM | 3 | 2VB | 5 | 3 | 2 | 2 | Yes | Moderate | Moderate | High |

| FCSM | 3 | 2VB | 4 | 2 | 2 | 0 | No | High | High | High |

| TL-CCSM | 3 | 2VB | 5 | 3 | 2 | 1 | Yes | High | High | High |

| MSCSM | 3 | 2VB | 6 | 4 | 2 | 0 | Yes | High | High | Moderate |

| IMSM | 3 | 2VB | 5 | 3 | 2 | 1 | Yes | High | High | High |

| NPCSM | 3 | 2VB | 4 | 2 | 2 | 2 | No | High | High | Complex |

| ANPCSM | 3 | 2VB | 6 | 2 | 2 | 0 | No | High | High | Complex |

| T-NPCSM-I | 3 | 2VB | 4 | 2 | 2 | 0 | No | Moderate | High | Complex |

| T-NPCSM-II | 3 | 2VB | 3 | 1 | 2 | 4 | No | Moderate | Low | Complex |

| HBCSM | 3 | 2VB | 6 | 3 | 2 | 2 | Yes | High | High | High |

| T2HBSM | 3 | 2VB | 5 | 3 | 2 | 1 | Yes | High | High | High |

| ISCSM | 3 | VB | 6 | 5 | 2 | 1 | Yes | High | High | Moderate |

| DBSM | 3 | 2VB | 2 | 2 | 1 | 2 | Yes | Low | Low | Low |

| SFBSM | 4 | 2VB | 7 | 3 | 2 | 0 | Yes | High | Moderate | Moderate |

| 4-LT2NPCSM | 4 | 2VB | 5 | 2 | 2 | 0 | Yes | High | High | High |

| FL-CCSM | 5 | 2VB | 6 | 3 | 2 | 0 | Yes | Low | Moderate | High |

| AMSM | 5 | 2VB | 6 | 3 | 2 | 0 | Yes | High | High | High |

| SC-FCHBSM | 5 | 4VB | 7 | 4 | 3 | 1 | Yes | High | High | High |

| Parameter | Value |

|---|---|

| SMs per valve | 8 |

| Rated AC side phase-phase voltage (Vrms) | 380 V |

| Rated AC side power/Phase current amplitude | 60 kW/128.6 A |

| Rated DC voltage | 960 V |

| Rated SM battery voltage | 120 V |

| SM battery rated capacity | 10 Ah |

| Valve inductance | 2 mH |

| Grid side inductance | 0.5 mH |

| Carrier frequency | 1 kHz |

| Phase | Valve | Submodules SOC and Capacity (Ah) | Mean SOC/Capacity (Ah) | Mean SOC/Capacity (Ah) | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | ||||

| a | U | 70.9/8 | 70.8/8 | 72.9/8 | 71.4/8 | 70.7/8 | 73.0/8 | 71.6/8 | 72.3/8 | 71.7/8 | 71.181/8 |

| L | 70.1/8 | 71.2/8 | 72.4/8 | 70.6/8 | 69.0/8 | 72.1/8 | 69.4/8 | 70.5/8 | 70.6625/8 | ||

| b | U | 72.7/10 | 70.1/10 | 70.3/11 | 71.6/11 | 72.2/13 | 73.0/13 | 73.4/14 | 73.9/14 | 72.15/12 | 71.356/10 |

| L | 70.5/8 | 70.7/8 | 69.5/8 | 71.7/8 | 69.3/8 | 72.4/8 | 71.2/8 | 69.2/8 | 70.5625/8 | ||

| c | U | 72.3/10 | 71.6/10 | 71.4/10 | 72.1/10 | 73.0/10 | 71.3/10 | 71.7/10 | 72.2/10 | 71.95/10 | 71.906/12 |

| L | 71.7/14 | 73.3/14 | 71.9/14 | 72.3/14 | 70.8/14 | 71.5/14 | 71.3/14 | 72.1/14 | 71.8625/14 | ||

| Parameter | Value |

|---|---|

| SM battery voltage | 12 V |

| SM battery rated capacity | 6 Ah |

| AC side rated phase voltage (Vrms) | 20 V |

| AC side power | 424.26 W |

| Phase current amplitude | 10 A |

| Valve inductance Grid side inductance | 1 mH 1 mH |

| Number of SMs per valve | 8 |

| DC side voltage | 96 V |

| DC side power/current | 960 W/10 A |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ali, S.; Bogarra, S.; Khan, M.M.; Taha, A.; Phyo, P.P.; Byun, Y.-C. Prospective Submodule Topologies for MMC-BESS and Its Control Analysis with HBSM. Electronics 2023, 12, 20. https://doi.org/10.3390/electronics12010020

Ali S, Bogarra S, Khan MM, Taha A, Phyo PP, Byun Y-C. Prospective Submodule Topologies for MMC-BESS and Its Control Analysis with HBSM. Electronics. 2023; 12(1):20. https://doi.org/10.3390/electronics12010020

Chicago/Turabian StyleAli, Salman, Santiago Bogarra, Muhammad Mansooor Khan, Ahmad Taha, Pyae Pyae Phyo, and Yung-Cheol Byun. 2023. "Prospective Submodule Topologies for MMC-BESS and Its Control Analysis with HBSM" Electronics 12, no. 1: 20. https://doi.org/10.3390/electronics12010020

APA StyleAli, S., Bogarra, S., Khan, M. M., Taha, A., Phyo, P. P., & Byun, Y.-C. (2023). Prospective Submodule Topologies for MMC-BESS and Its Control Analysis with HBSM. Electronics, 12(1), 20. https://doi.org/10.3390/electronics12010020