A New Fully Closed-Loop, High-Precision, Class-AB CCII for Differential Capacitive Sensor Interfaces

Abstract

1. Introduction

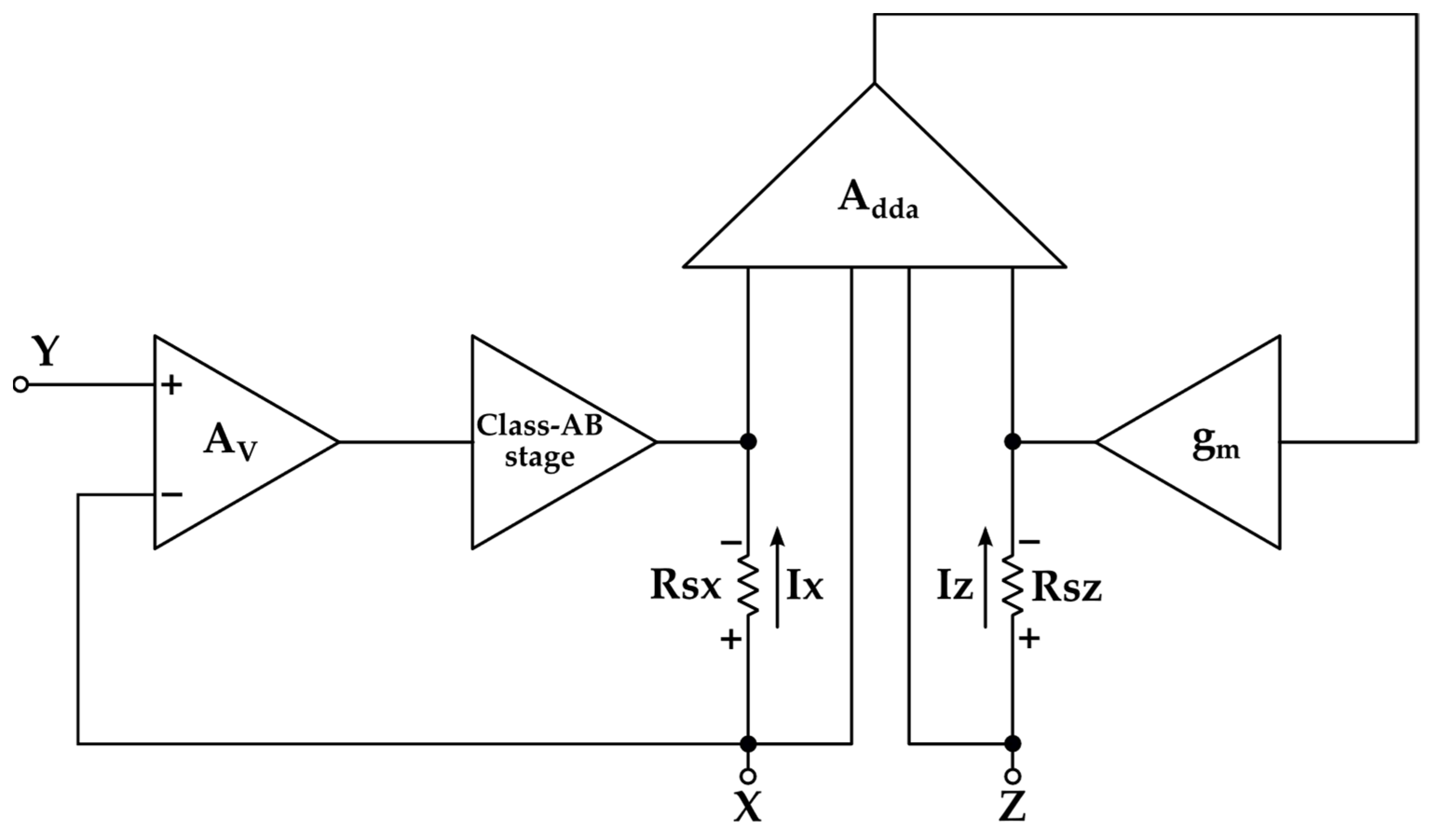

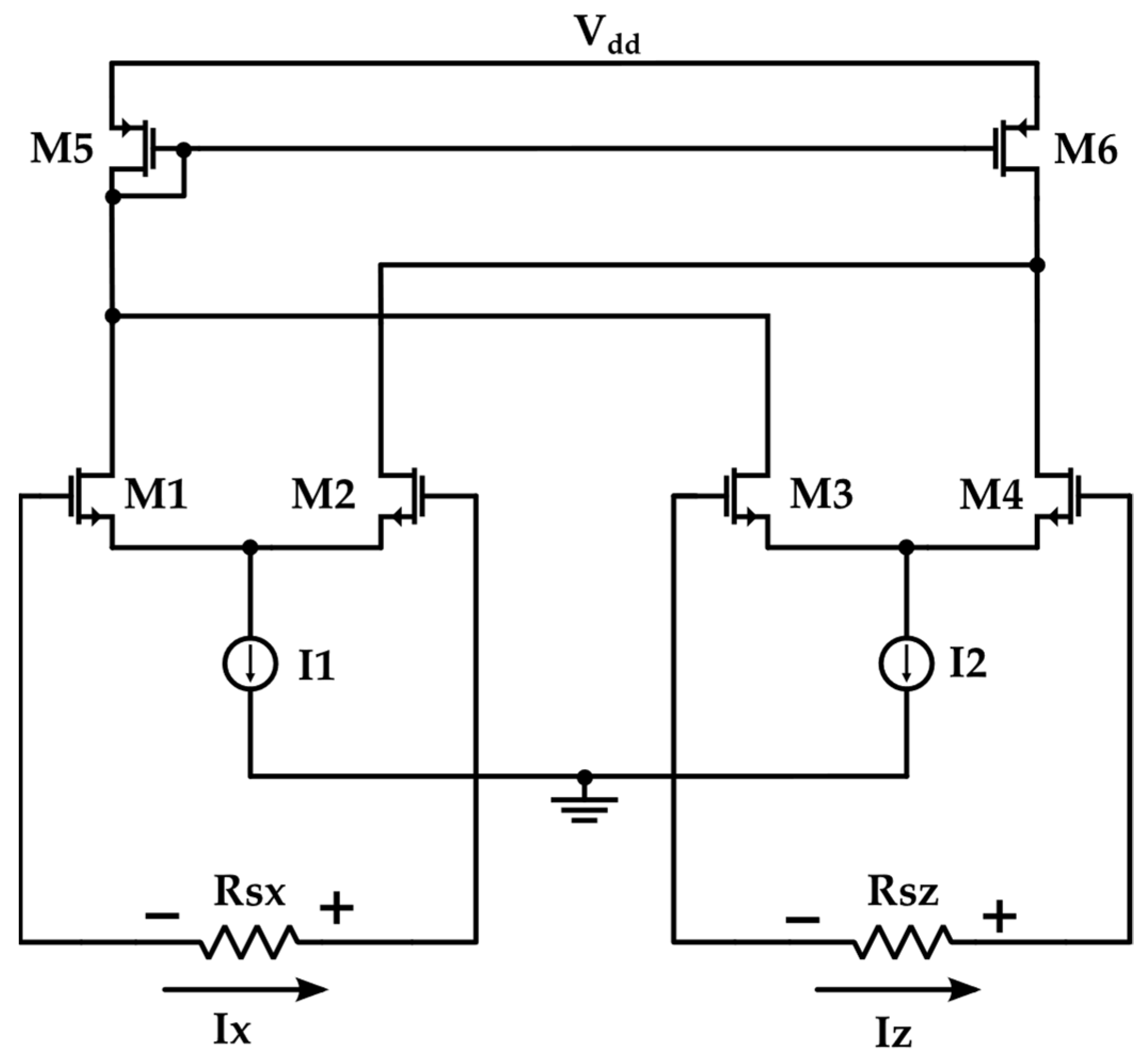

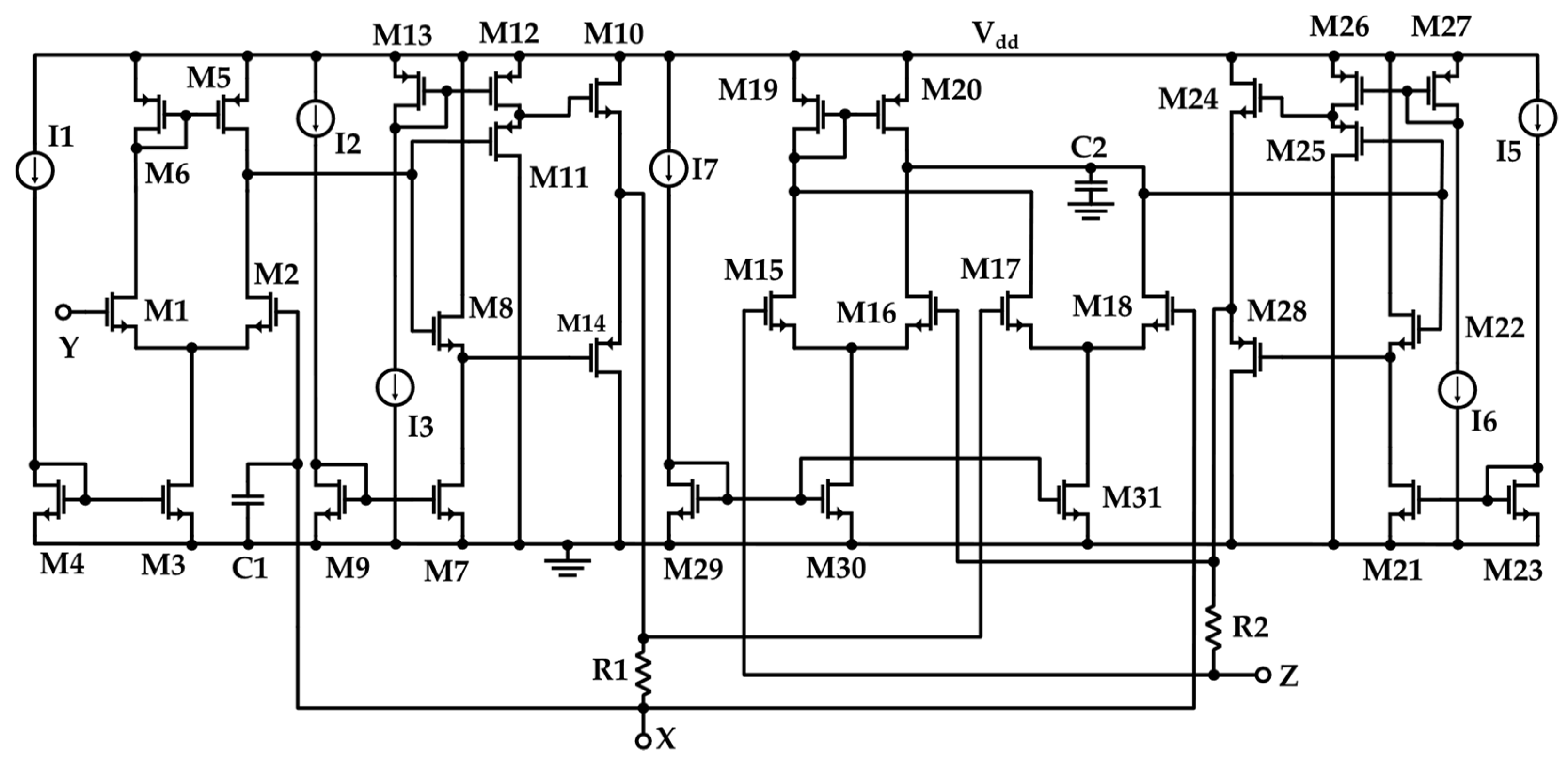

2. The Proposed Topology

3. Circuit Analysis

3.1. Analysis of the Proposed CCII

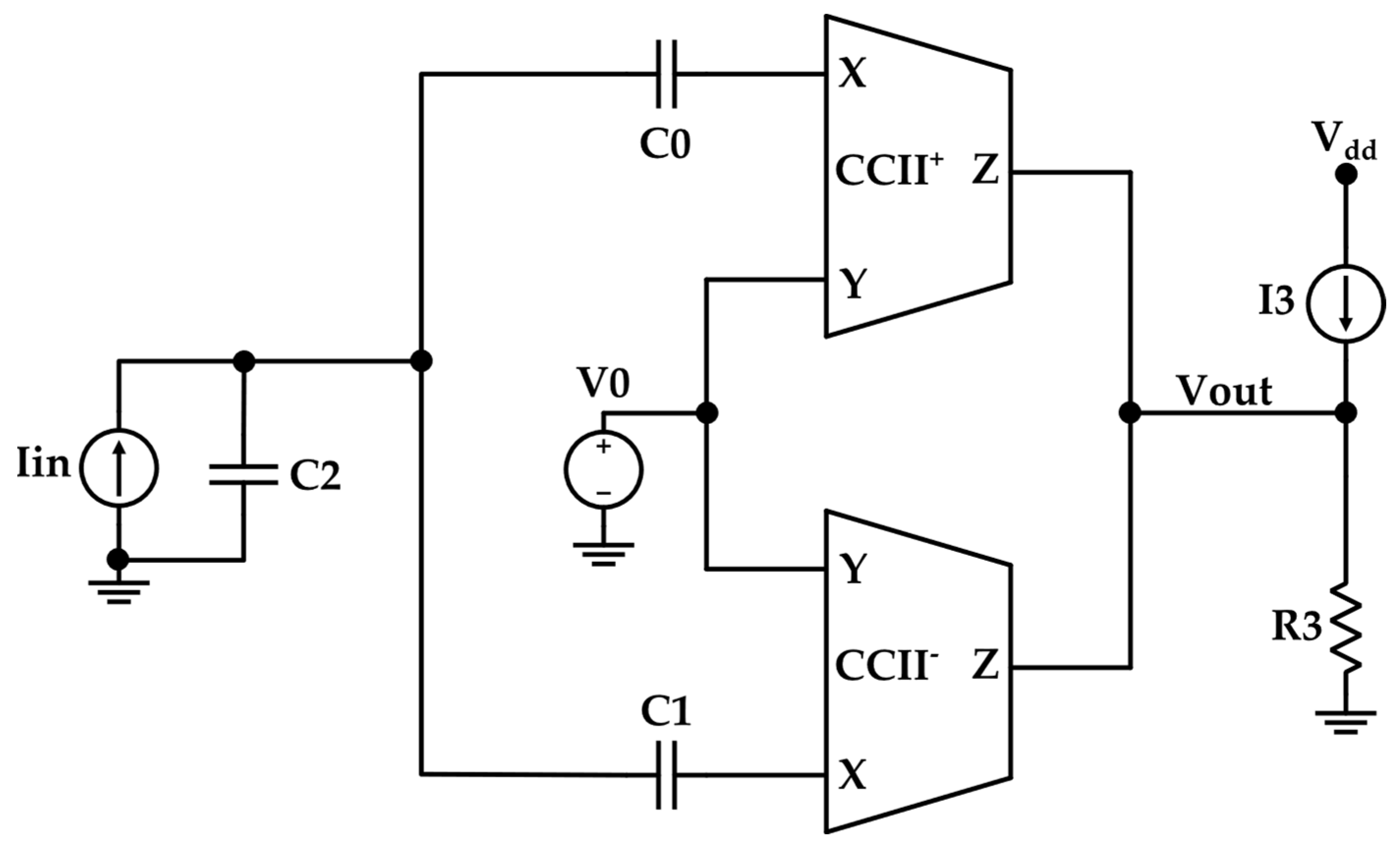

3.2. Application as Differential Capacitive Sensor Interface

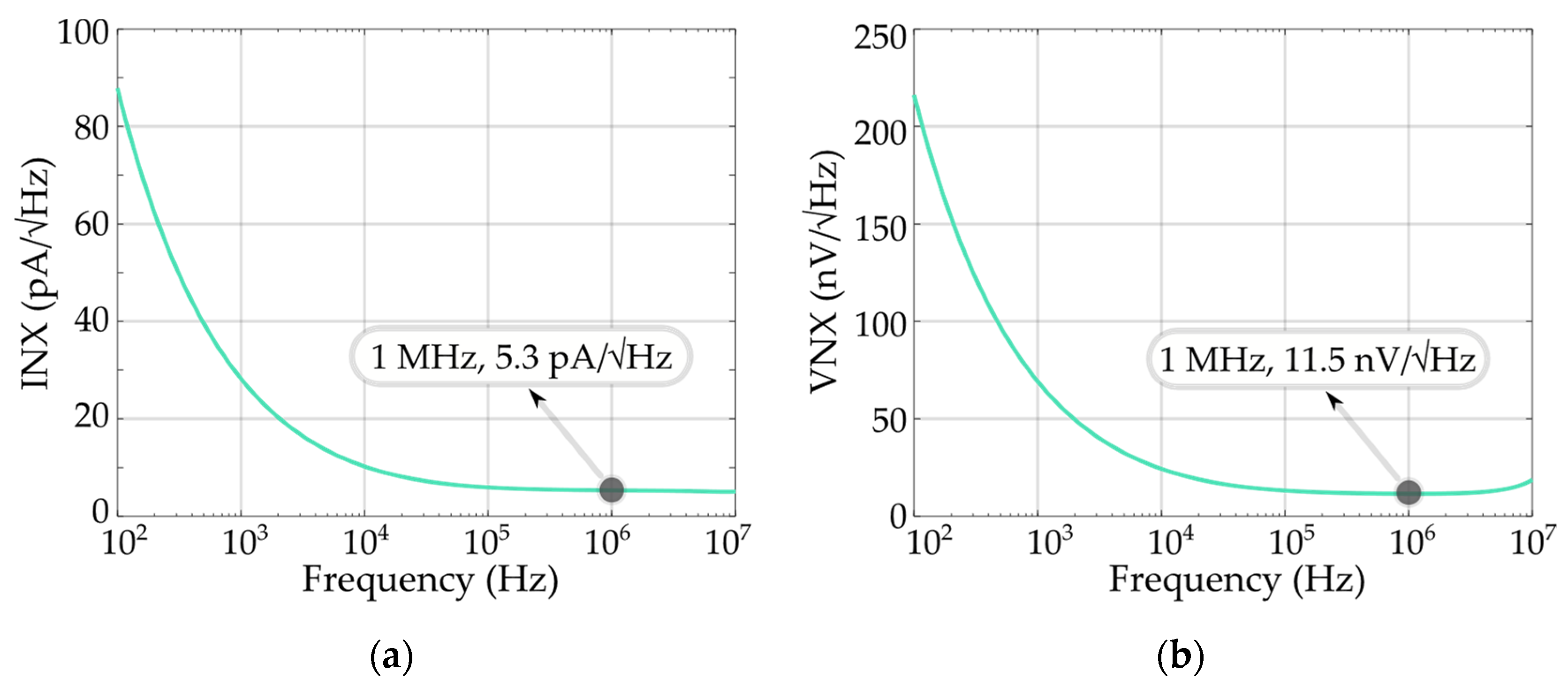

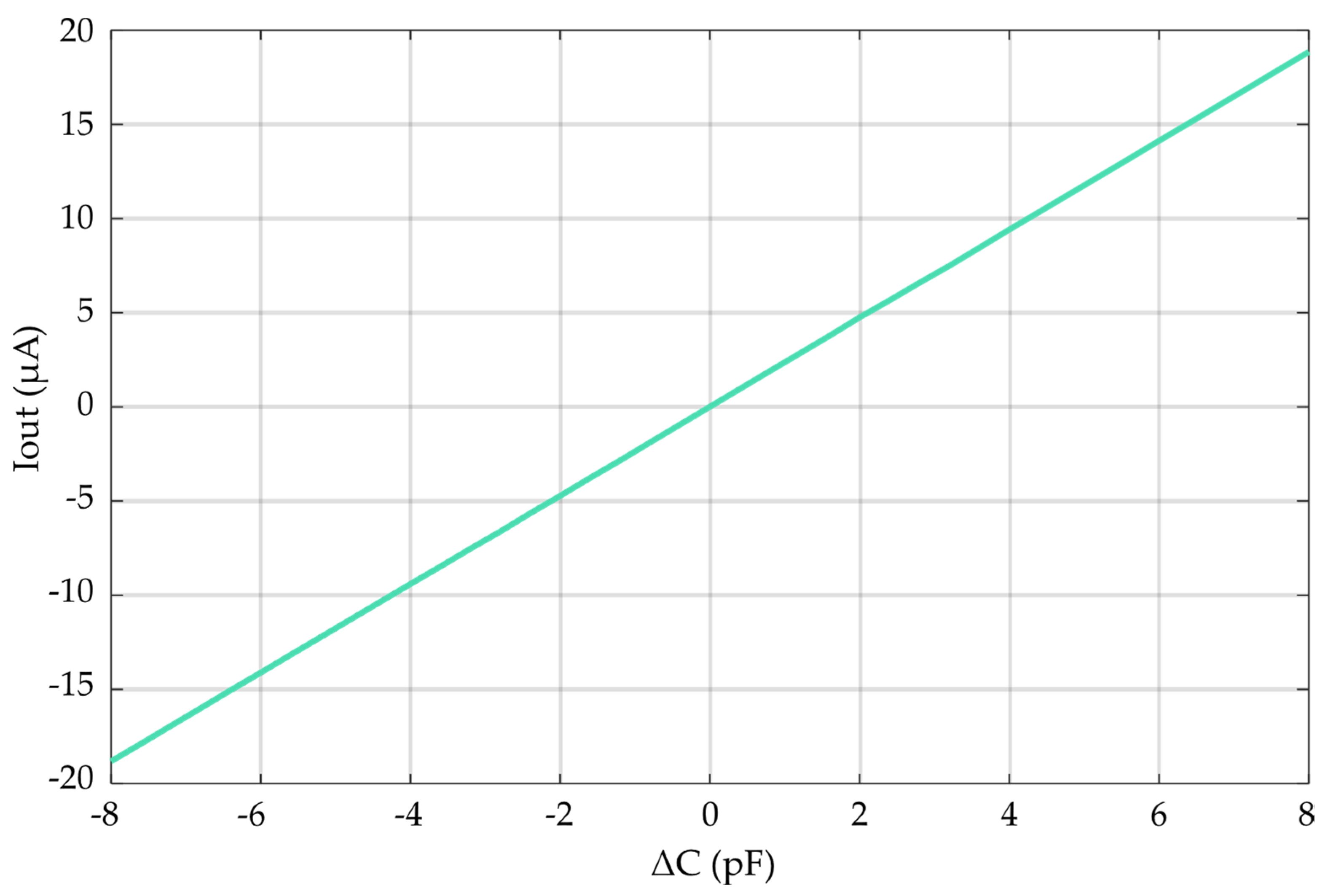

4. Simulation Results of a Sensor Design Case Study

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Capacitive Sensors: Design and Applications; Wiley-IEEE Press: Hoboken, NJ, USA, 1997; Available online: https://ieeexplore.ieee.org/book/5264832 (accessed on 18 January 2022).

- Puers, R. Capacitive sensors: When and how to use them. Sens. Actuators A Phys. 1993, 37–38, 93–105. [Google Scholar] [CrossRef]

- Dong, T.; Gu, Y.; Liu, T.; Pecht, M. Resistive and capacitive strain sensors based on customized compliant electrode: Comparison and their wearable applications. Sens. Actuators A Phys. 2021, 326, 112720. [Google Scholar] [CrossRef]

- Qian, H.; Hrnjak, P. Characterization of R134a two-phase flow regimes in horizontal and vertical smooth tubes with capacitive sensors. Int. J. Refrig. 2021, 125, 90–103. [Google Scholar] [CrossRef]

- Wang, W.; Zhao, K.; Zhang, P.; Bao, J.; Xue, S. Application of three self-developed ECT sensors for monitoring the moisture content in sand and mortar. Constr. Build. Mater. 2021, 267, 121008. [Google Scholar] [CrossRef]

- Zeng, T.; Lu, Y.; Liu, Y.; Yang, H.; Bai, Y.; Hu, P.; Li, Z.; Zhang, Z.; Tan, J. A Capacitive Sensor for the Measurement of Departure From the Vertical Movement. IEEE Trans. Instrum. Meas. 2015, 65, 458–466. [Google Scholar] [CrossRef]

- Ferlito, U.; Grasso, A.; Vaiana, M.; Bruno, G. A Time-Based Electronic Front-End for a Capacitive Particle Matter Detector. Sensors 2021, 21, 1840. [Google Scholar] [CrossRef]

- Andrés, M.A.; Vijjapu, M.T.; Surya, S.G.; Shekhah, O.; Salama, K.N.; Serre, C.; Eddaoudi, M.; Roubeau, O.; Gascón, I. Methanol and Humidity Capacitive Sensors Based on Thin Films of MOF Nanoparticles. ACS Appl. Mater. Interfaces 2020, 12, 4155–4162. [Google Scholar] [CrossRef]

- Ramakrishnan, J.; Gaurav, P.T.R.; Chandar, N.S.; Sudharsan, N.M. Structural design, analysis and DOE of MEMS-based capacitive accelerometer for automotive airbag application. Microsyst. Technol. 2020, 27, 763–777. [Google Scholar] [CrossRef]

- Martínez, J.; Asiain, D.; Beltrán, J. Lightweight Thermal Compensation Technique for MEMS Capacitive Accelerometer Oriented to Quasi-Static Measurements. Sensors 2021, 21, 3117. [Google Scholar] [CrossRef]

- Li, R.; Zhou, Q.; Bi, Y.; Cao, S.; Xia, X.; Yang, A.; Li, S.; Xiao, X. Research progress of flexible capacitive pressure sensor for sensitivity enhancement approaches. Sens. Actuators A Phys. 2021, 321, 112425. [Google Scholar] [CrossRef]

- Okasha, A.; Ibrahim, H.; Elmetwalli, A.; Khedher, K.; Yaseen, Z.; Elsayed, S. Designing Low-Cost Capacitive-Based Soil Moisture Sensor and Smart Monitoring Unit Operated by Solar Cells for Greenhouse Irrigation Management. Sensors 2021, 21, 5387. [Google Scholar] [CrossRef] [PubMed]

- Shiah, J.; Rashtian, H.; Mirabbasi, S. A Low-Noise Parasitic-Insensitive Switched-Capacitor CMOS Interface Circuit for MEMS Capacitive Sensors. In Proceedings of the 2011 IEEE 9th International New Circuits and Systems Conference, Bordeaux, France, 26–29 June 2011; pp. 470–473. [Google Scholar]

- Litvinov, A.; Samotaev, N.; Etrekova, M.; Ivanova, A.; Filipchuk, D. Hydrogen Concentration Control in Oil-Filled Power Transformers Using Field Effect Capacitive Gas Sensors. J. Electrochem. Soc. 2021, 168, 017503. [Google Scholar] [CrossRef]

- Gupta, N.; Dutta, S.; Panchal, A.; Yadav, I.; Kumar, S.; Parmar, Y.; Vanjari, S.R.K.; Jain, K.K.; Bhattacharya, D.K. Design and Fabrication of SOI Technology Based MEMS Differential Capacitive Accelerometer Structure. J. Mater. Sci. 2019, 30, 15705–15714. Available online: https://www.springerprofessional.de/en/design-and-fabrication-of-soi-technology-based-mems-differential/17036044 (accessed on 13 March 2022). [CrossRef]

- Eswaran, P.; Malarvizhi, S. Design Analysis of MEMS Capacitive Differential Pressure Sensor for Aircraft Altimeter. Int. J. Appl. Phys. Math. 2012, 2, 14–20. [Google Scholar] [CrossRef]

- Li, R.; Mohammed, Z.; Rasras, M.; Elfadel, I.; Abe, M.; Choi, D. Design, modelling and characterization of comb drive MEMS gap-changeable differential capacitive accelerometer. Measurement 2021, 169, 108377. [Google Scholar] [CrossRef]

- Aydemir, A.; Terzioglu, Y.; Akin, T. A new design and a fabrication approach to realize a high performance three axes capacitive MEMS accelerometer. Sens. Actuators A Phys. 2016, 244, 324–333. [Google Scholar] [CrossRef]

- Depari, A.; Sisinni, E.; Flammini, A.; Ferri, G.; Stornelli, V.; Barile, G.; Parente, F.R. Autobalancing Analog Front End for Full-Range Differential Capacitive Sensing. IEEE Trans. Instrum. Meas. 2018, 67, 885–893. [Google Scholar] [CrossRef]

- Barile, G.; Ferri, G.; Parente, F.R.; Stornelli, V.; Depari, A.; Flammini, A.; Sisinni, E. A Standard CMOS Bridge-Based Analog Interface for Differential Capacitive Sensors. In Proceedings of the 2017 13th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Giardini Naxos-Taormina, Italy, 12–15 June 2017; pp. 281–284. [Google Scholar]

- Li, X.; Hu, J.; Liu, X. A High-Performance Digital Interface Circuit for a High-Q Micro-Electromechanical System Accelerometer. Micromachines 2018, 9, 675. [Google Scholar] [CrossRef]

- Depari, A.; Sisinni, E.; Bellagente, P.; Ferrari, P.; Flammini, A.; Rinaldi, S. Simple and robust microcontroller-based acquisition system for differential capacitive sensors. In Proceedings of the 2021 IEEE International Instrumentation and Measurement Technology Conference (I2MTC), Glasgow, UK, 17–20 May 2021; pp. 1–6. [Google Scholar]

- Barile, G.; Safari, L.; Ferri, G.; Stornelli, V. A VCII-Based Stray Insensitive Analog Interface for Differential Capacitance Sensors. Sensors 2019, 19, 3545. [Google Scholar] [CrossRef]

- Sisinni, E.; Depari, A.; Flammini, A.; Ferri, G.; Stornelli, V.; Barile, G. Full-Analog Parasitic Capacitance Compensation for AC-Excited Differential Sensors. IEEE Trans. Instrum. Meas. 2020, 69, 5890–5899. [Google Scholar] [CrossRef]

- Pennisi, S. High-performance and simple CMOS interface circuit for differential capacitive sensors. IEEE Trans. Circuits Syst. II Express Briefs 2005, 52, 327–330. [Google Scholar] [CrossRef]

- Singh, T.; Saether, T.; Ytterdal, T. Current-Mode Capacitive Sensor Interface Circuit With Single-Ended to Differential Output Capability. IEEE Trans. Instrum. Meas. 2009, 58, 3914–3920. [Google Scholar] [CrossRef]

- Scotti, G.; Pennisi, S.; Monsurro, P.; Trifiletti, A. 88-μ A 1-MHz Stray-Insensitive CMOS Current-Mode Interface IC for Differential Capacitive Sensors. IEEE Trans. Circuits Syst. I 2014, 61, 1905–1916. [Google Scholar] [CrossRef]

- Ghallab, Y.H.; Badawy, W. A New Design of a Current-mode Wheatstone Bridge Using Operational Floating Current Conveyor. In Proceedings of the 2006 International Conference on MEMS, NANO, and Smart Systems, Cairo, Egypt, 27–29 December 2006; pp. 41–44. [Google Scholar]

- Zhong, L.; Shang, P.; Cao, W.; Zhu, Z.; Liu, S. Capacitance-to-voltage converter employing parallel-series passive charge integrator for low noise power efficient MEMS capacitive sensor. Microelectron. J. 2022, 121, 105369. [Google Scholar] [CrossRef]

- Sedra, A.; Smith, K. A second-generation current conveyor and its applications. IEEE Trans. Circuit Theory 1970, 17, 132–134. [Google Scholar] [CrossRef]

- Ferri, G.; De Marcellis, A.; Di Carlo, C.; Stornelli, V.; Flammini, A.; Depari, A.; Marioli, D.; Sisinni, E. A CCII-Based Low-Voltage Low-Power Read-Out Circuit for DC-Excited Resistive Gas Sensors. IEEE Sens. J. 2009, 9, 2035–2041. [Google Scholar] [CrossRef]

- Abolila, A.H.M.; Hamed, H.F.A.; Hasaneen, E.-S.A.M. High performance wideband CMOS current conveyor for low voltage low power applications. In Proceedings of the 10th IEEE International Symposium on Signal Processing and Information Technology, Luxor, Egypt, 15–18 December 2010; pp. 433–438. [Google Scholar]

- Hassen, N.; Ettaghzouti, T.; Besbes, K. High-Performance Second-Generation Controlled Current Conveyor CCCII and High Frequency Applications. Int. J. Electron. Commun. Eng. 2011, 5, 1764–1773. [Google Scholar]

- Hwang, Y.-S.; Ku, Y.-T.; Chen, J.-J.; Yu, C.-C. Inverter-Based Low-Voltage CCII- Design and Its Filter Application. Radioengineering 2013, 22, 1026–1033. [Google Scholar]

- Suwansawang, S.; Thongleam, T. A 1-V bulk-driven CMOS fully differential second-generation current conveyor. In Proceedings of the 2013 International Symposium on Intelligent Signal Processing and Communication Systems, Naha, Japan, 12–15 November 2013; pp. 662–665. [Google Scholar]

- Ettaghzouti, T.; Hassen, N.; Besbes, K. A novel low-voltage low-power CCII based on super class AB CMOS OTA cells and filter application. In Proceedings of the 2015 IEEE 12th International Multi-Conference on Systems, Signals & Devices (SSD15), Mahdia, Tunisia, 16–19 March 2015; pp. 1–6. [Google Scholar]

- Reda, A.; Ibrahim, M.F.; Farag, F. Input–output Rail-to-Rail CMOS CCII for low voltage & low power applications. Microelectron. J. 2016, 48, 60–75. [Google Scholar] [CrossRef]

- Stornelli, V.; Pantoli, L.; Ferri, G.; Liberati, L.; Centurelli, F.; Monsurrò, T.; Trifiletti, A. The AB-CCII, a novel adaptive biasing LV-LP current conveyor. AEU Int. J. Electron. Commun. 2017, 79, 301–306. [Google Scholar] [CrossRef]

- Centurelli, F.; Monsurrò, P.; Stornelli, V.; Barile, G.; Trifiletti, A. Low-power class-AB 4th-order low-pass filter based on current conveyors with dynamic mismatch compensation of biasing errors. Int. J. Circuit Theory Appl. 2020, 48, 472–484. [Google Scholar] [CrossRef]

| Transistor | Dimensions (W, L) |

|---|---|

| M1, M2 | 43.2 μm, 3.1 μm |

| M3, M4 | 86.4 μm, 3.1 μm |

| M5, M6, M19, M20 | 14.4 μm, 3.1 μm |

| M7, M9, M21, M23 | 576 μm, 1.6 μm |

| M8, M22 | 36 μm, 0.2 μm |

| M10, M24 | 144 μm, 0.2 μm |

| M11, M25 | 144 μm, 0.3 μm |

| M12, M13, M26, M27 | 576 μm, 3.1 μm |

| M14, M28 | 576 μm, 0.3 μm |

| M15, M16, M17, M18 | 21.1 μm, 3.1 μm |

| M29, M30, M31 | 42.2 μm, 3.1 μm |

| Item | This Work | [31] | [32] | [33] | [34] | [35] | [36] | [37] | [38] | |

|---|---|---|---|---|---|---|---|---|---|---|

| Rsense = 5 kΩ | Rsense = 0.5 Ω | |||||||||

| CMOS tech. (μm) | 0.13 | 0.35 | 0.18 | 0.18 | 0.18 | 0.18 | 0.18 | 0.13 | 0.35 | |

| Power supply (V) | 1.2 | ±0.75 | ±0.75 | ±1 | ±0.5 | 1.0 | ±0.75 | 1.5 | ±0.75 | |

| Power diss. (mW) | 0.605 | 0.118 | 0.27 | - | 120 | 0.4 | 0.23 | 1.5 | 0.00015 | |

| Y Input range (V) | ±0.250 | - | ±0.75 | ±0.4 | ±0.24 | ±1.0 | ±0.75 | 1.5 | - | |

| X Input range (μA) | ±30 | ±225 | - | ±125 | ±350 | ±24 | ±1000 | ±220 | ±20 | - |

| DC-α (dB) | −0.088 | −0.088 | 0 | 0.009 | −0.464 | −0.087 | 0 | 0 | −0.005 | −0.04 |

| f-3dB of α (MHz) | 12 | 18.6 | 10.5 | 1200 | 3340 | 36 | 25.7 | 3000 | 94 | 4.2 |

| DC-β (dB) | −0.181 | −0.271 | 0 | 0 | 0 | −0.141 | 0 | 0 | −0.130 | −0.82 |

| f-3dB of β (MHz) | 12.8 | 17.6 | 10.5 | 1200 | 4370 | 30.2 | 30 | 2960 | 99 | 4.4 |

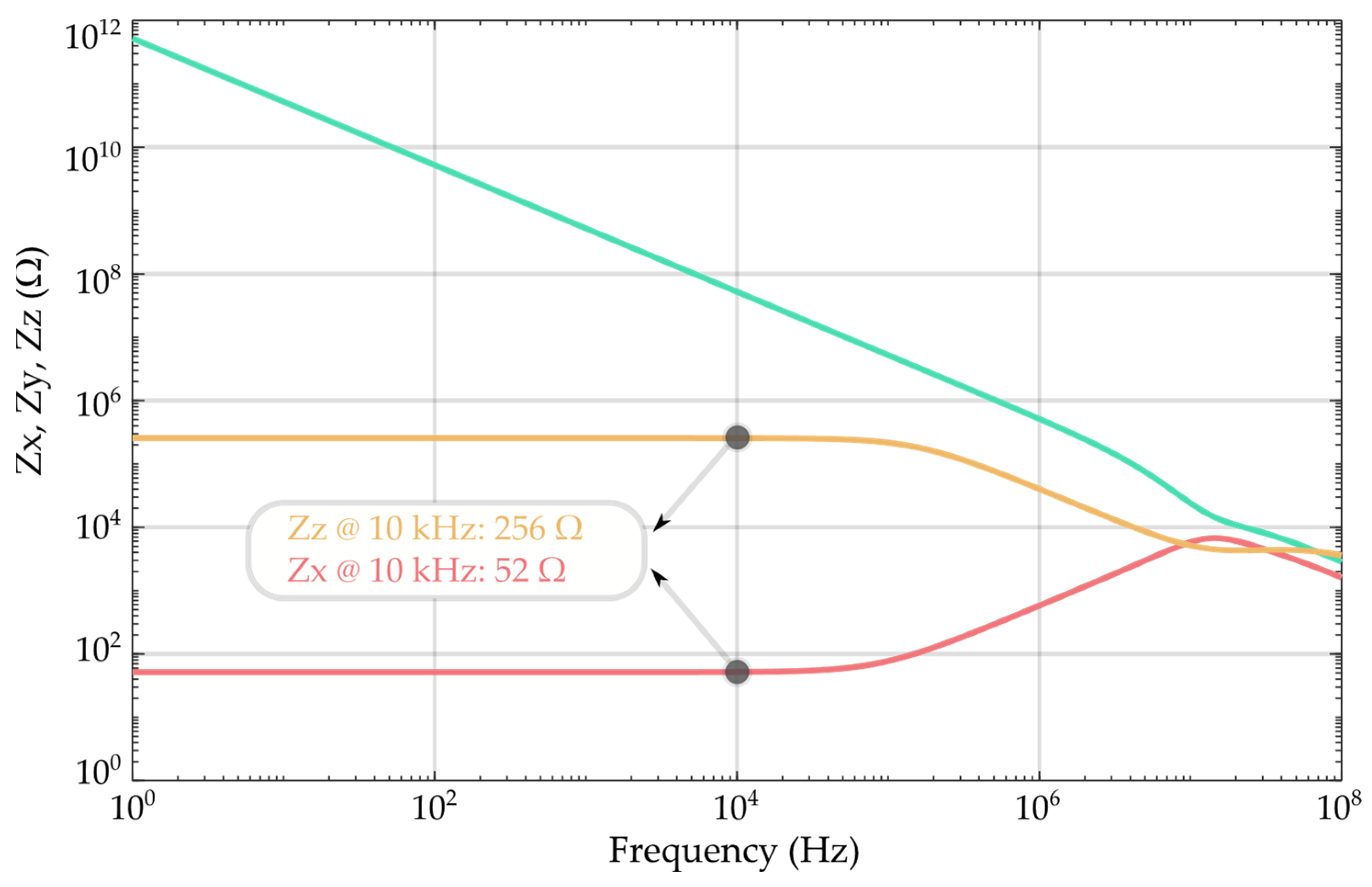

| RX (Ω) | 51 | 7.8 | 13 | 2.4 | 169 | 137 | - | 8.26 | 200 | 52 |

| RZ (kΩ) | 256 | 25.8 | 2600 | - | 6.81 | 225 | - | 46.5 | 560 | 700 |

| CY (pF) | 0.305 | 0.305 | 0.5 | 0.004 | 0.164 | 3 × 10−6 | - | 0.012 | 10 | 0.5 |

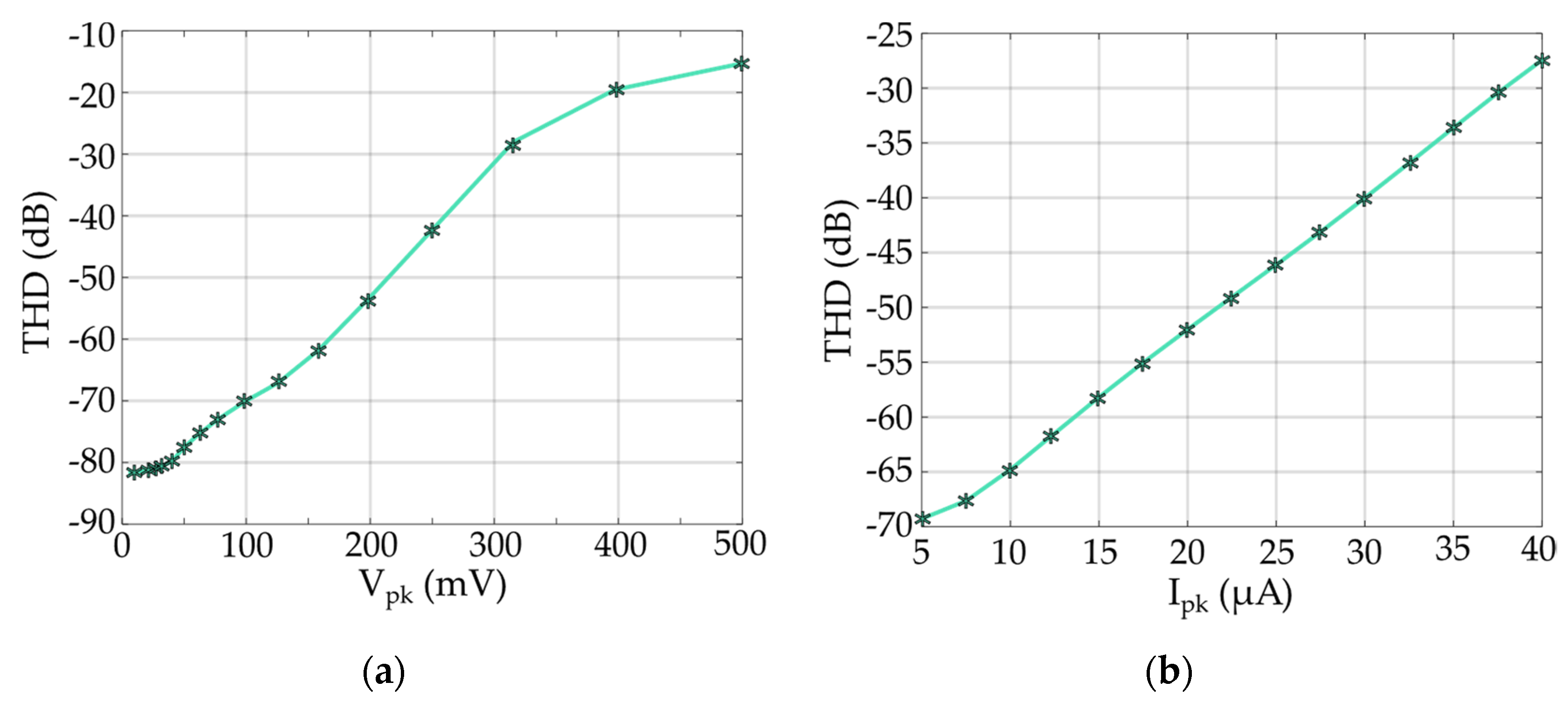

| IZ THD (dB) | −46.4 @225 mV 100 kHz | −46.4 @225 mV 100 kHz | - | - | −52.4 @300 mV 1 MHz | - | - | - | - | |

| VX THD (dB) | −46.1 @25 μA 1 kHz | −46.1 @200 μA 1 kHz | - | - | −47.7 @300 μA 1 MHz | - | - | −35 @10 μA 1 kHz | - | |

| Item | Temperature | Supply | FF | FS | SF | SS | ||

|---|---|---|---|---|---|---|---|---|

| Temperature (°C) | 0 | 70 | 27 | 27 | 27 | 27 | 27 | 27 |

| Power supply (V) | 1.2 | 1.2 | 1.14 | 1.26 | 1.2 | 1.2 | 1.2 | 1.2 |

| Power diss. (mW) | 585 | 639 | 572 | 640 | 631 | 605 | 607 | 583 |

| DC-α (dB) | −0.085 | −0.093 | −0.095 | −0.082 | −0.086 | −0.103 | −0.084 | −0.090 |

| f−3dB of α (MHz) | 12.7 | 11.1 | 11.9 | 12.1 | 12.5 | 12.1 | 11.9 | 11.5 |

| DC-β (dB) | −0.177 | −0.193 | −0.191 | −0.173 | −0.180 | −0.230 | −0.171 | −0.184 |

| f−3dB of β (MHz) | 13.7 | 11.7 | 12.6 | 13 | 13.5 | 13.0 | 12.7 | 12.1 |

| RX (Ω) | 51.4 | 53.9 | 53.3 | 50.2 | 52.3 | 66.2 | 48.3 | 51.4 |

| RZ (kΩ) | 268 | 233 | 237 | 270 | 259 | 219 | 272 | 250 |

| IZ THD (dB) | −46.2 | −45.7 | −42.1 | −53.2 | −50.2 | −36.9 | −37.5 | −42.5 |

| VX THD (dB) | −44.1 | −47.5 | −44.3 | −46.9 | −46.1 | −38.1 | −44.4 | −45.2 |

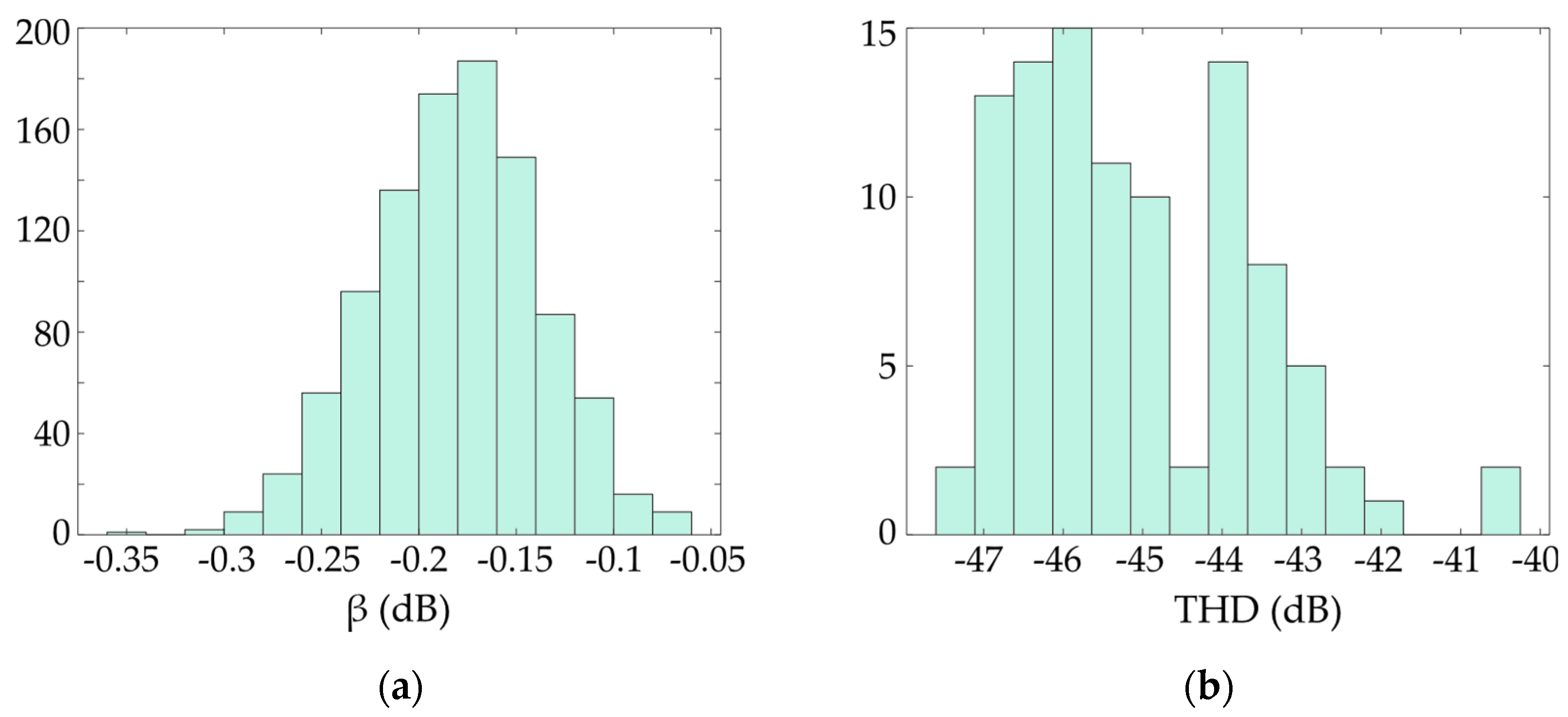

| Item | Mean | Std |

|---|---|---|

| Power diss. (mW) | 0.606 | 0.0018 |

| DC-α (dB) | −0.087 | 0.0002 |

| f−3dB of α (MHz) | 12 | 0.04 |

| DC-β (dB) | −0.181 | 0.043 |

| f−3dB of β (MHz) | 12.8 | 0.05 |

| RX (Ω) | 51.6 | 0.12 |

| RZ (kΩ) | 246 | 16.5 |

| IZ THD (dB) | −46.4 | 0.13 |

| VX THD (dB) | −45.1 | 1.3 |

| Item | This Work * | [23] * | [27] | [28] | [29] * |

|---|---|---|---|---|---|

| CMOS tech. (μm) | 0.13 | 0.35 | 0.065 | 0.8 | 0.18 |

| Sensor type | Differential | Differential | Differential | Single ended | Differential |

| Power supply (V) | 1.2 | ±1.65 | 2.5 | 5 | 1.8 |

| Power diss. (mW) | 1.2 | 5.6 | 0.22 | 0.725 | 0.04 |

| Bandwidth (kHz) | 1000 | 50 | 500 | 290 | 50 |

| Sensitivity | 2.34 nA/fF | 6.1 mV/pF | 5 nA/fF | 1.2 nA/fF | N.A. |

| Full-scale ΔC (pF) | 8 | 20 | 1.8 | 1 | 0.01 |

| Minimum ΔC (fF) | 40 ** | N.A. | 0.8 | N.A. | 0.23 ** |

| Conversion type | C-I | C-V | C-I | C-I | C-V |

| ΔCmax/ΔCmin | 200 | N.A. | 2250 | N.A. | 43.5 |

| FOM (MHz/mW) | 167 | N.A. | 5134 | N.A. | 54 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Barile, G.; Centurelli, F.; Ferri, G.; Monsurrò, P.; Pantoli, L.; Stornelli, V.; Tommasino, P.; Trifiletti, A. A New Fully Closed-Loop, High-Precision, Class-AB CCII for Differential Capacitive Sensor Interfaces. Electronics 2022, 11, 903. https://doi.org/10.3390/electronics11060903

Barile G, Centurelli F, Ferri G, Monsurrò P, Pantoli L, Stornelli V, Tommasino P, Trifiletti A. A New Fully Closed-Loop, High-Precision, Class-AB CCII for Differential Capacitive Sensor Interfaces. Electronics. 2022; 11(6):903. https://doi.org/10.3390/electronics11060903

Chicago/Turabian StyleBarile, Gianluca, Francesco Centurelli, Giuseppe Ferri, Pietro Monsurrò, Leonardo Pantoli, Vincenzo Stornelli, Pasquale Tommasino, and Alessandro Trifiletti. 2022. "A New Fully Closed-Loop, High-Precision, Class-AB CCII for Differential Capacitive Sensor Interfaces" Electronics 11, no. 6: 903. https://doi.org/10.3390/electronics11060903

APA StyleBarile, G., Centurelli, F., Ferri, G., Monsurrò, P., Pantoli, L., Stornelli, V., Tommasino, P., & Trifiletti, A. (2022). A New Fully Closed-Loop, High-Precision, Class-AB CCII for Differential Capacitive Sensor Interfaces. Electronics, 11(6), 903. https://doi.org/10.3390/electronics11060903