A Fully Integrated Passive Self-Jamming Cancellation Architecture with Fast Settling Time for UHF RFID Reader

Abstract

:1. Introduction

2. Analysis and Design

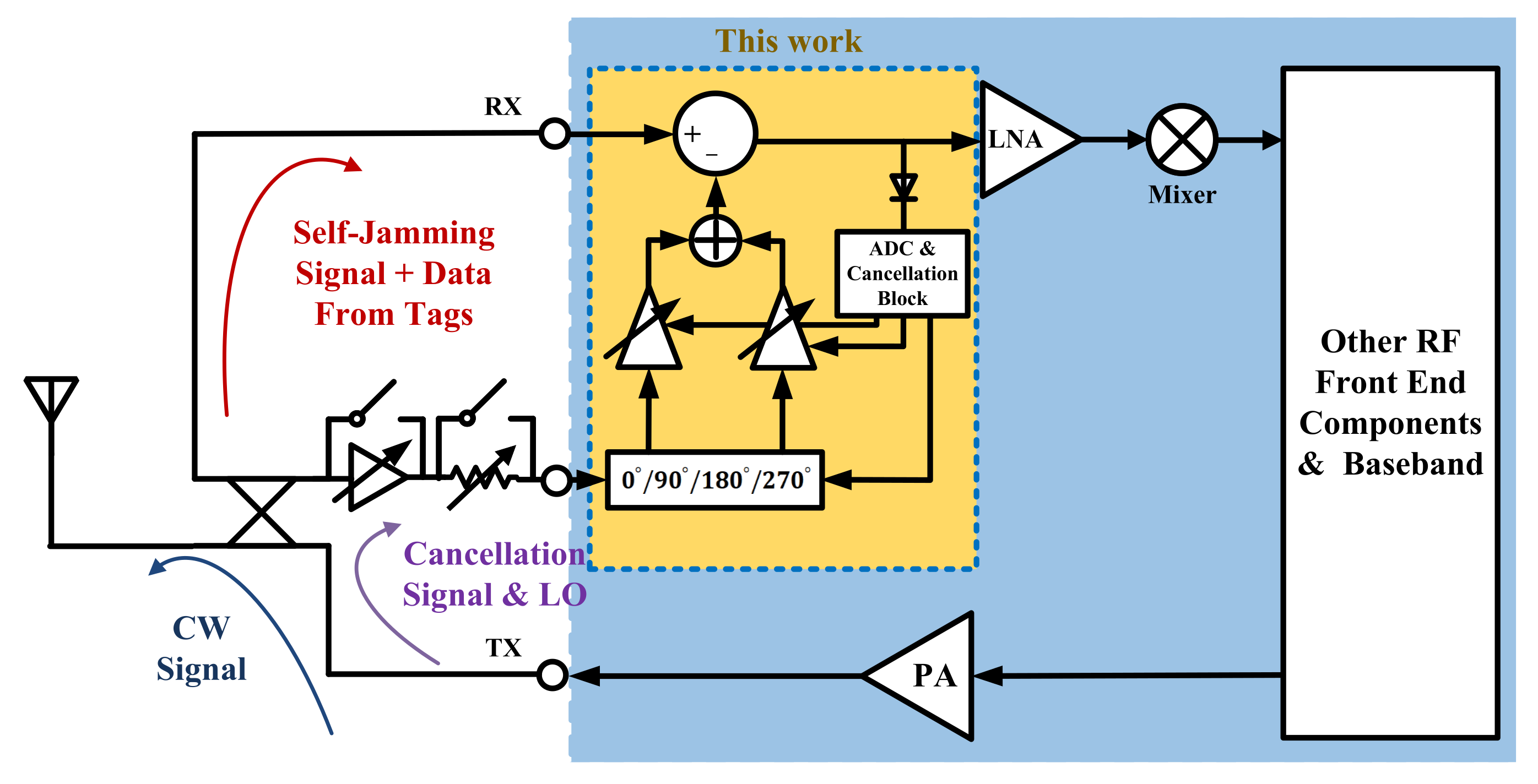

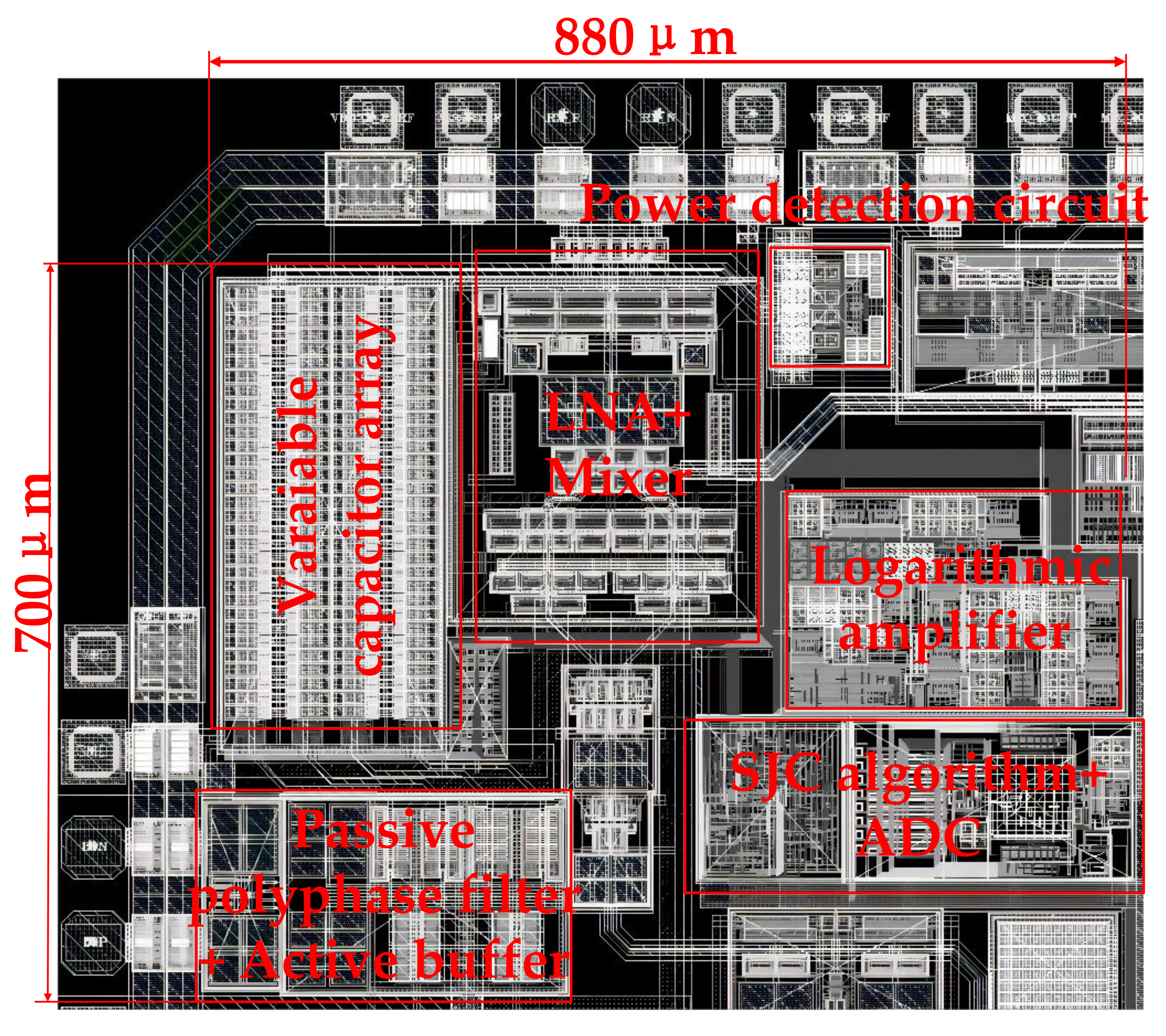

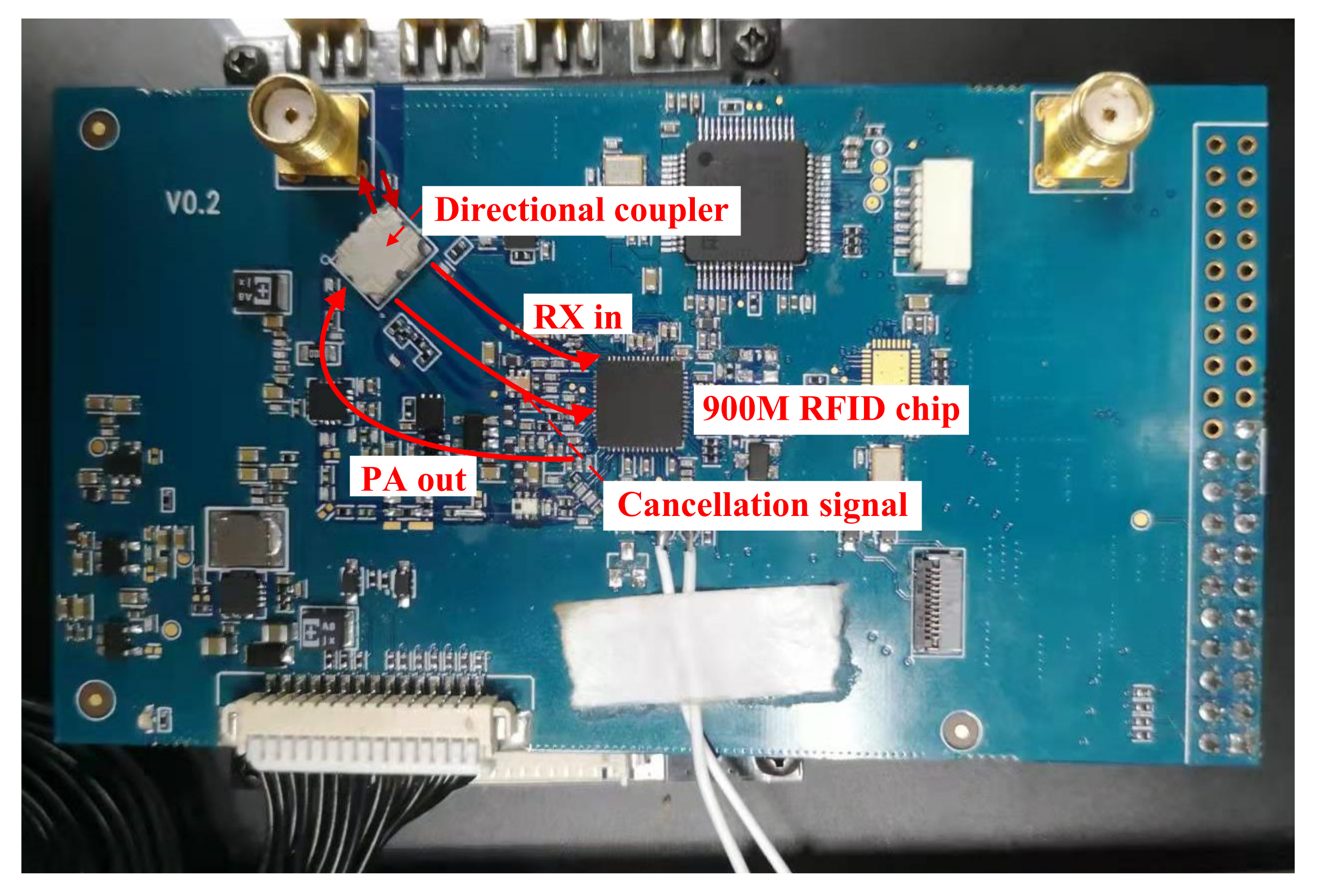

2.1. Overall Architecture of UHF RFID Transceiver and SJC Circuit

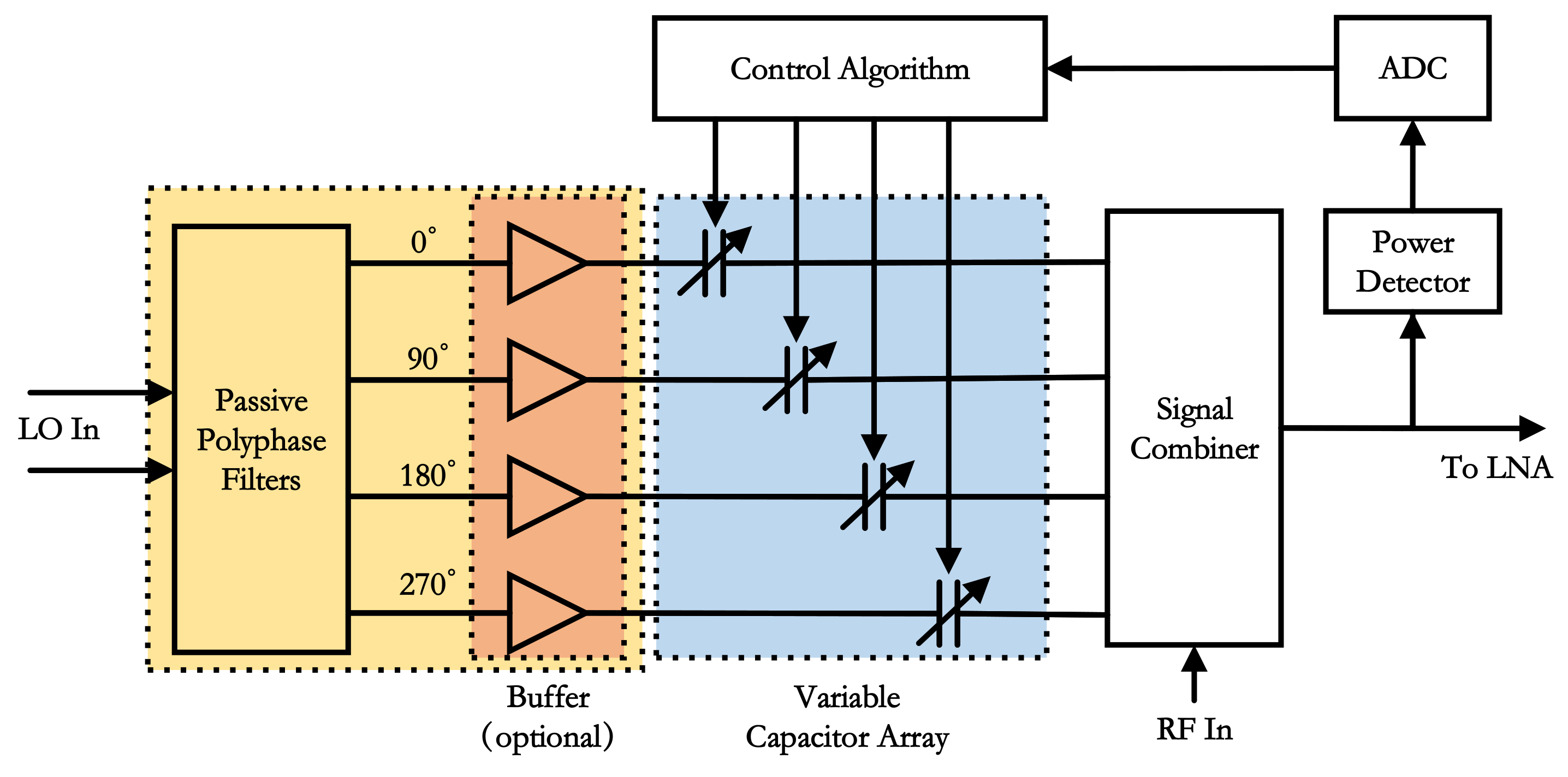

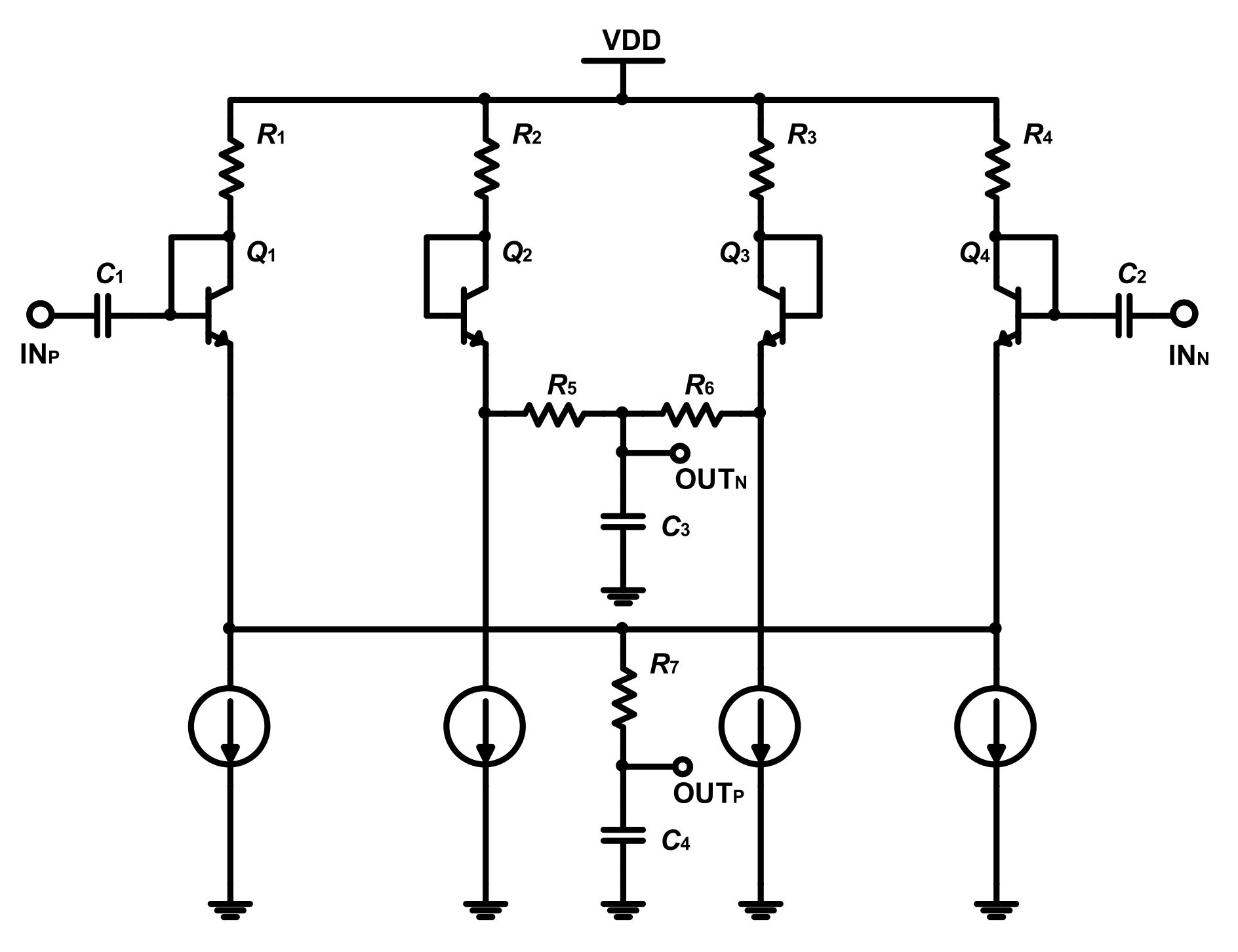

2.2. SJC Circuit Design

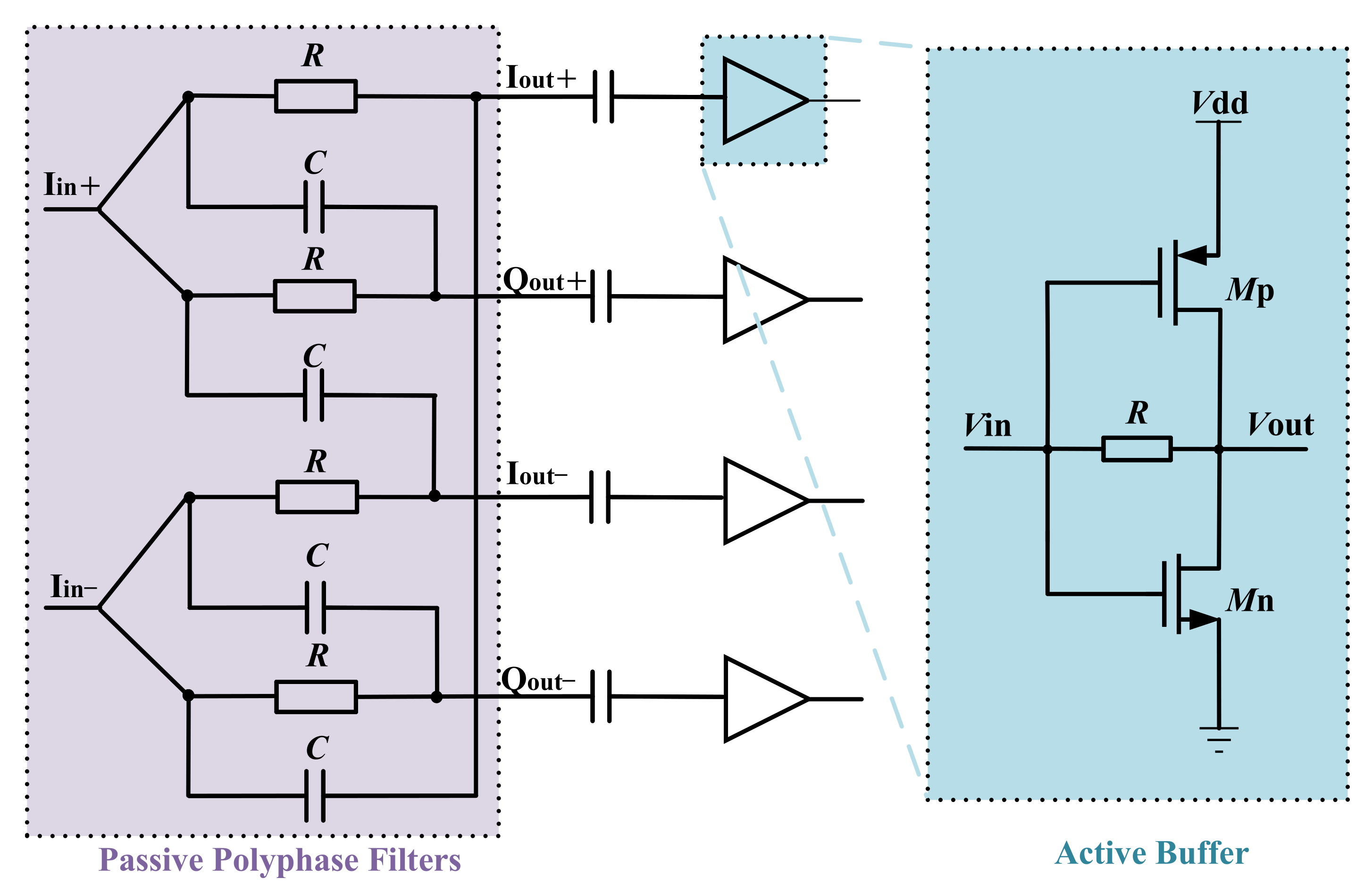

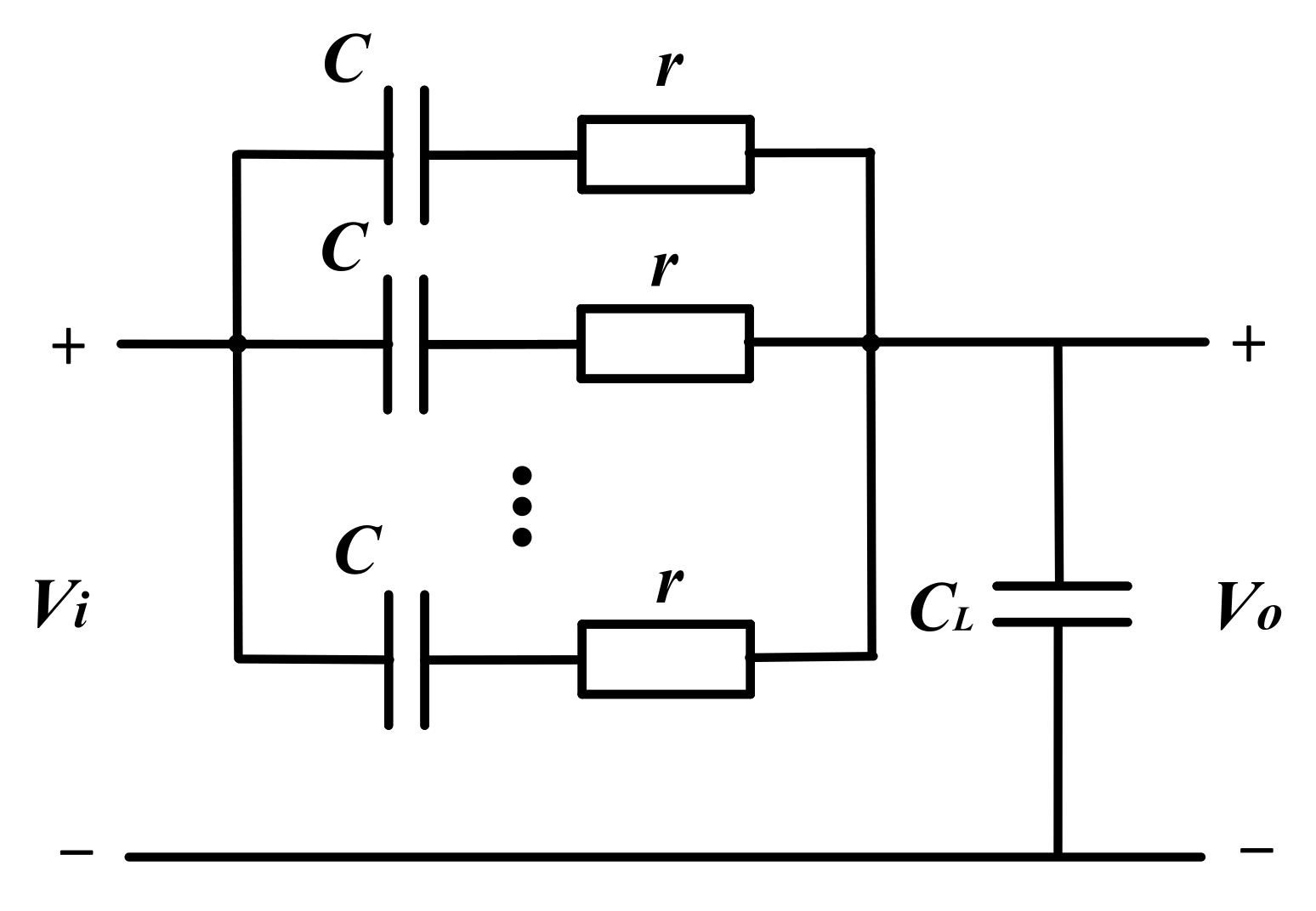

2.2.1. Passive Polyphase Filter

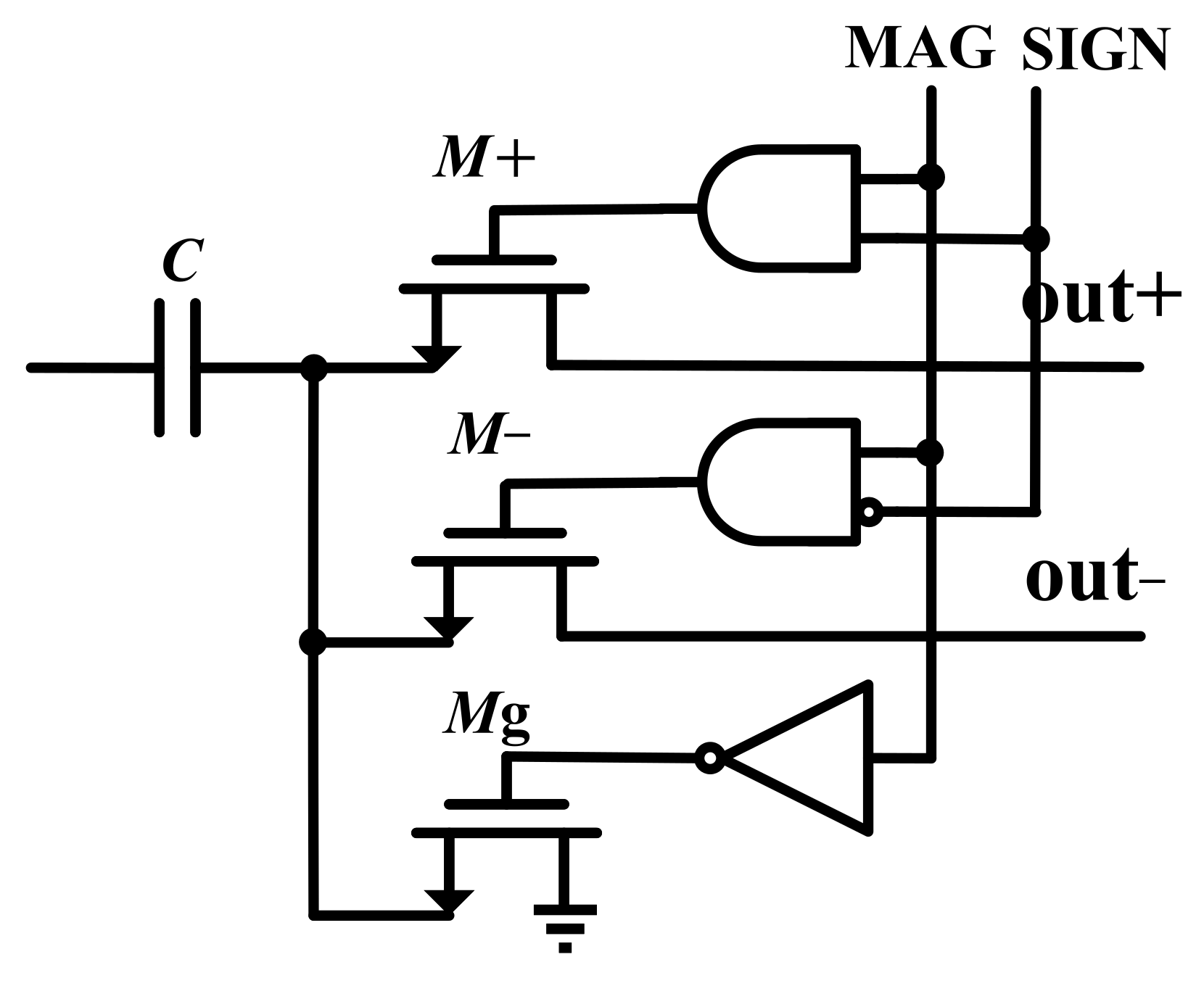

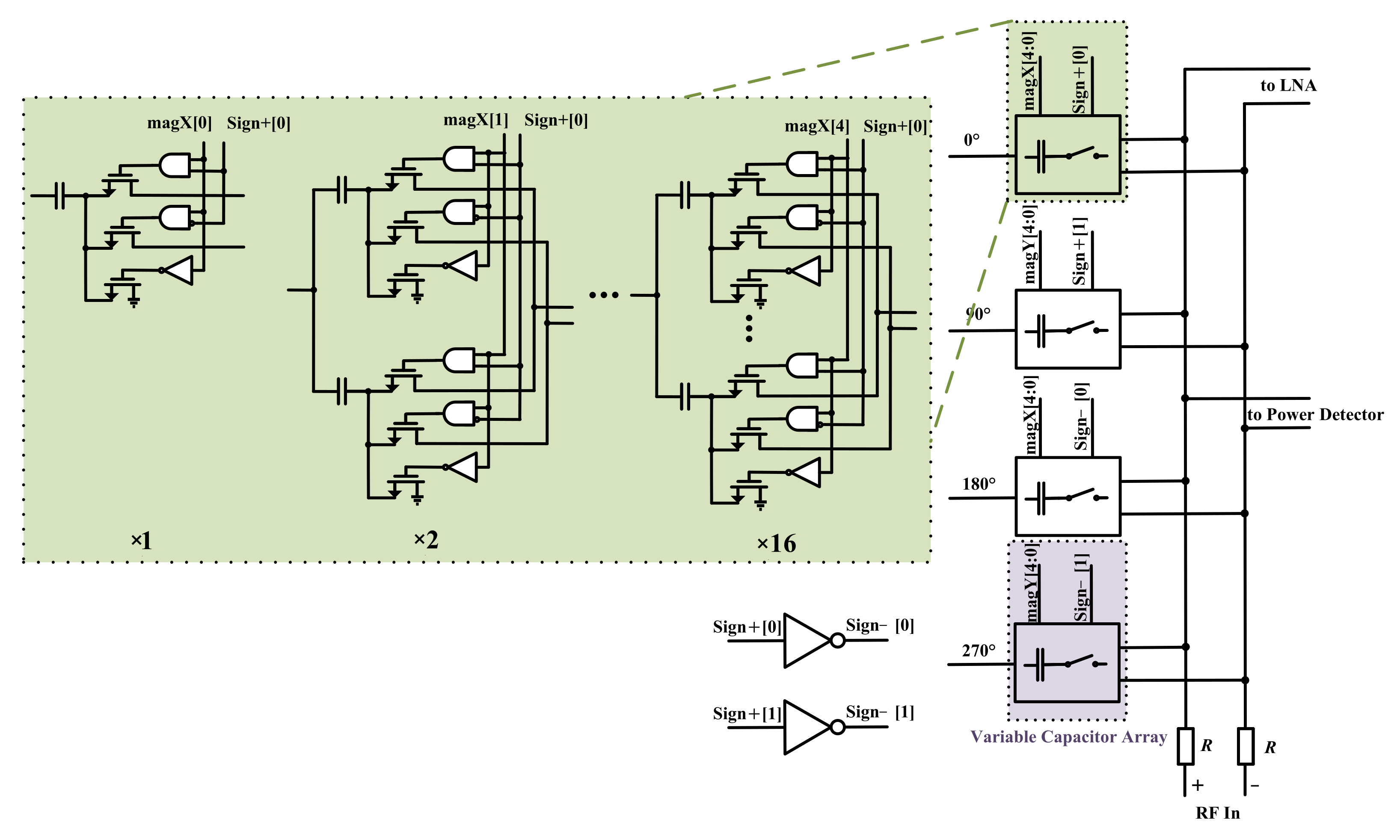

2.2.2. Variable Capacitor Array and Signal Combiner

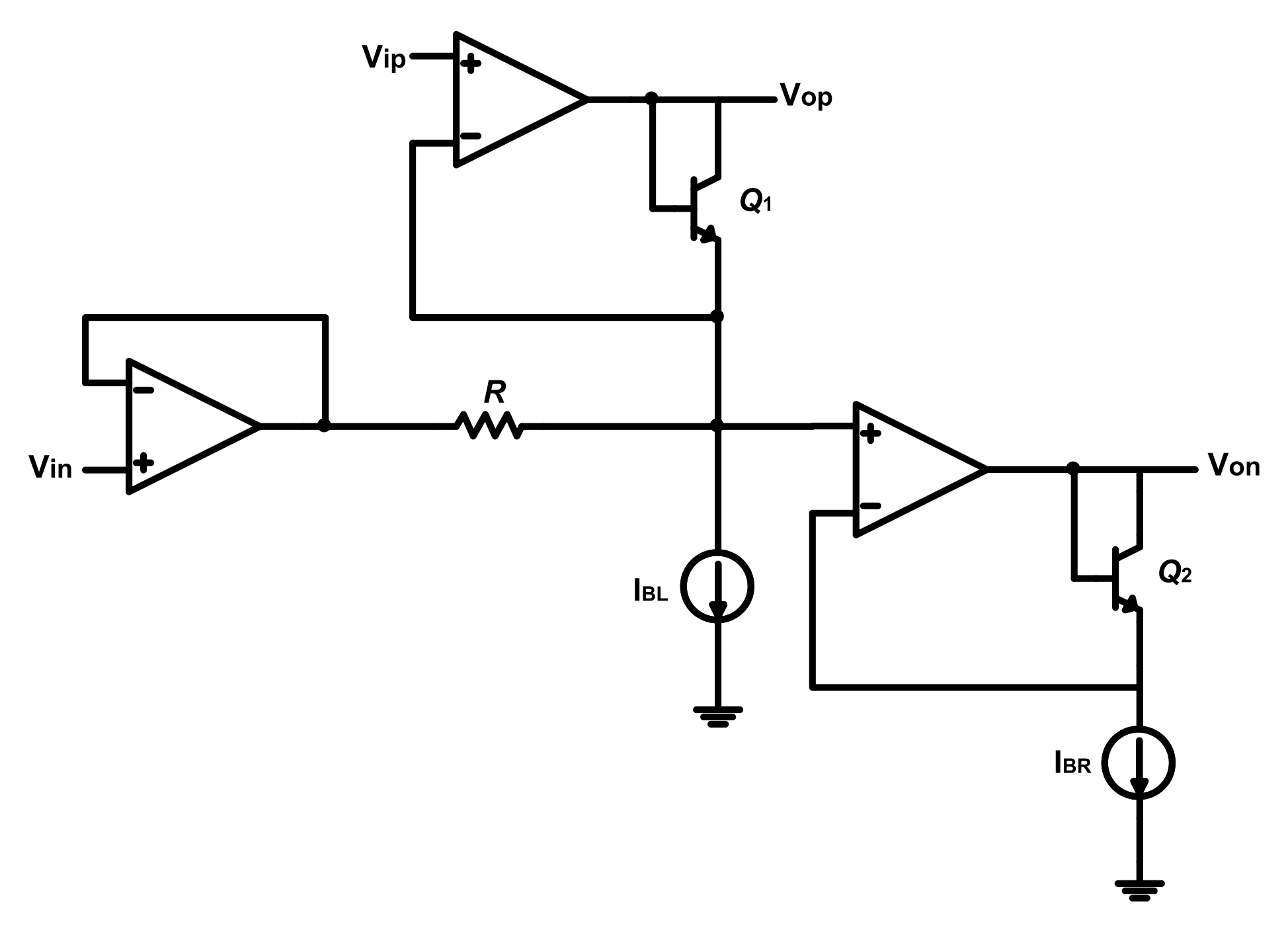

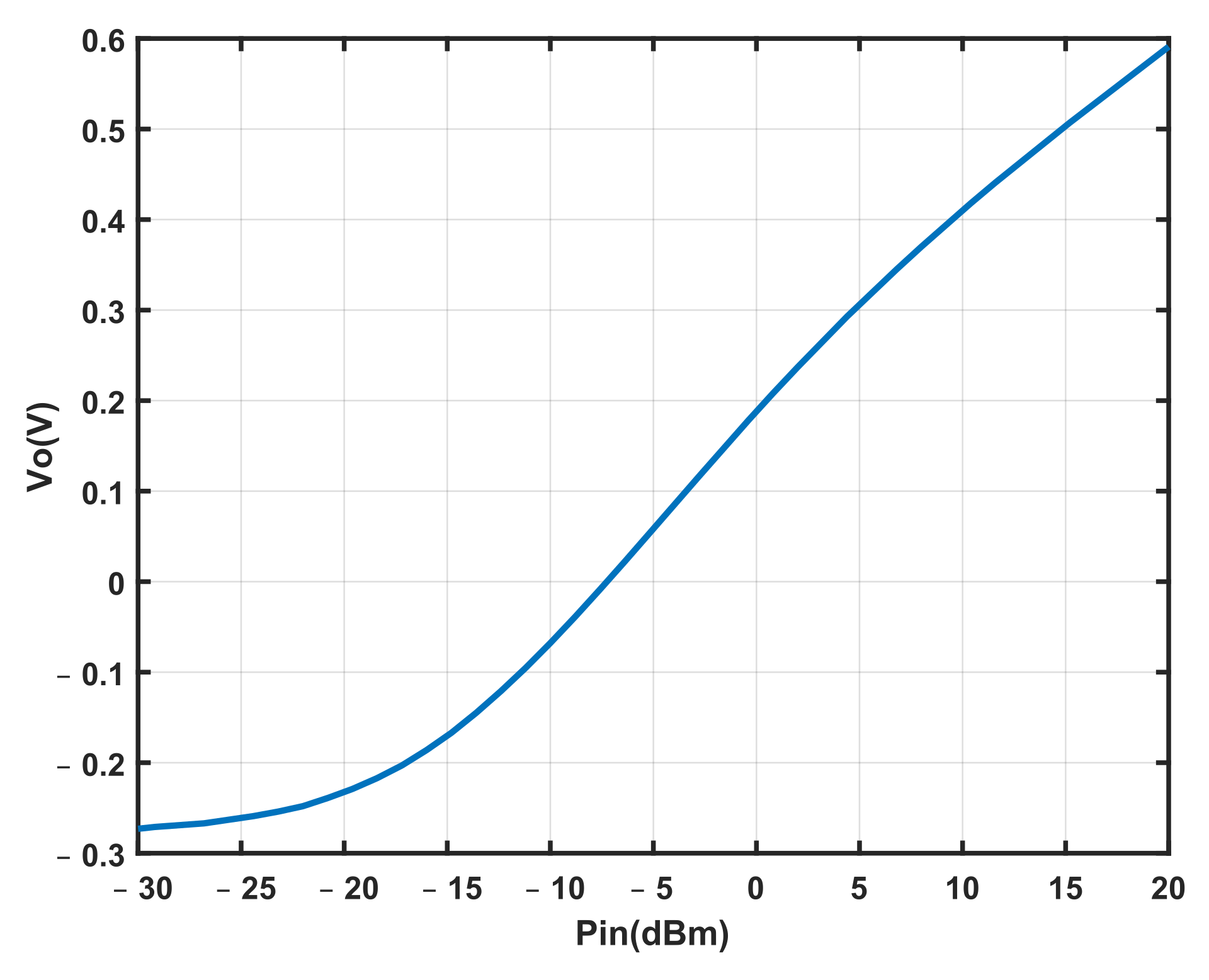

2.2.3. Power Detector

2.2.4. Self-Jammer Cancellation Algorithm

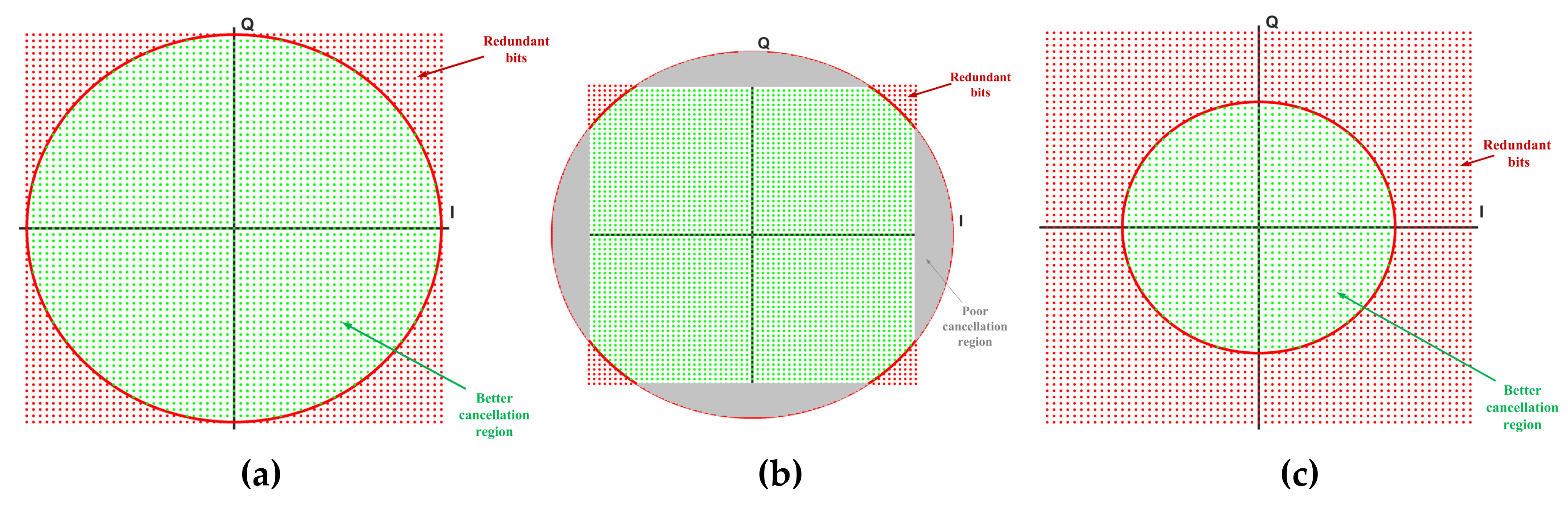

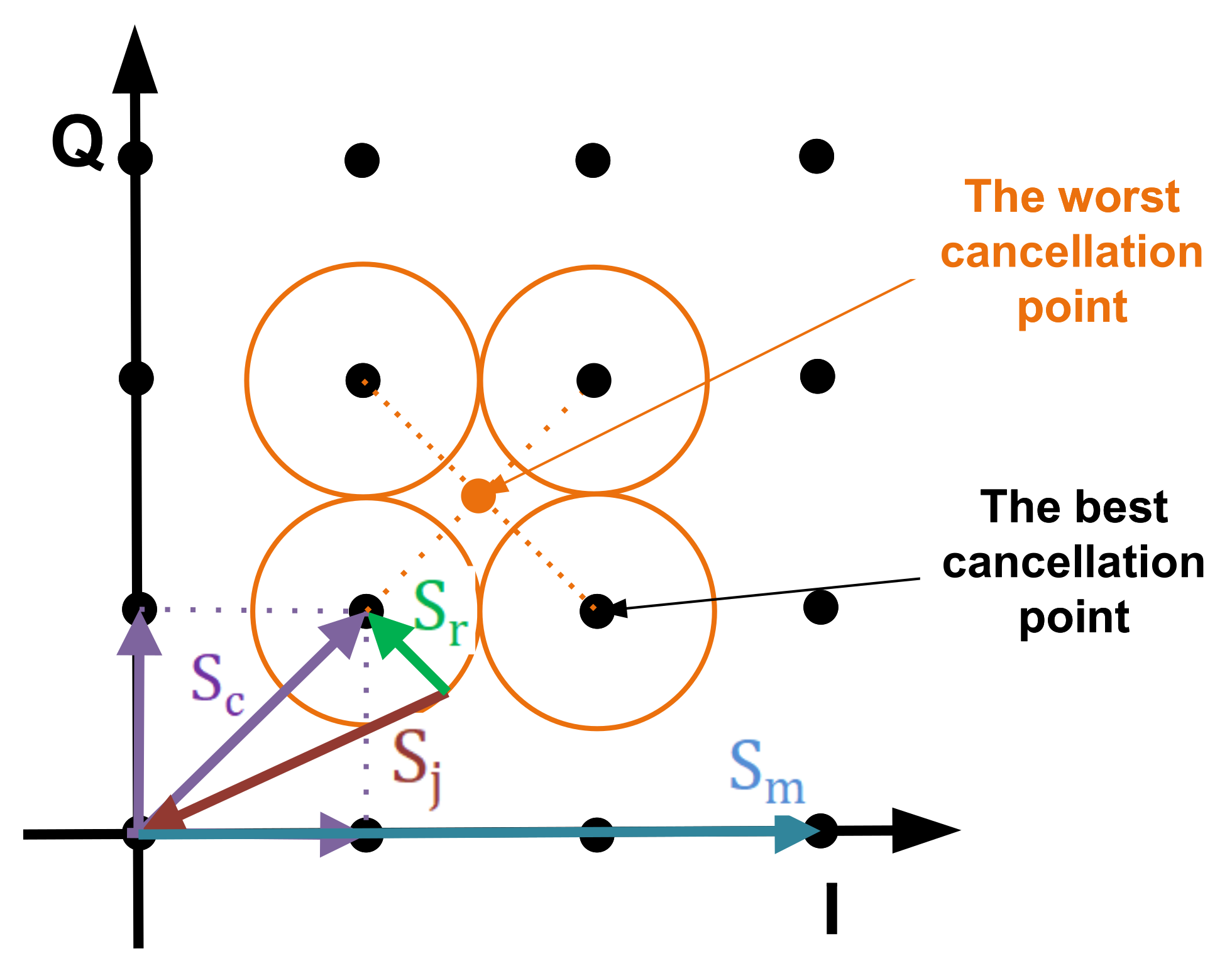

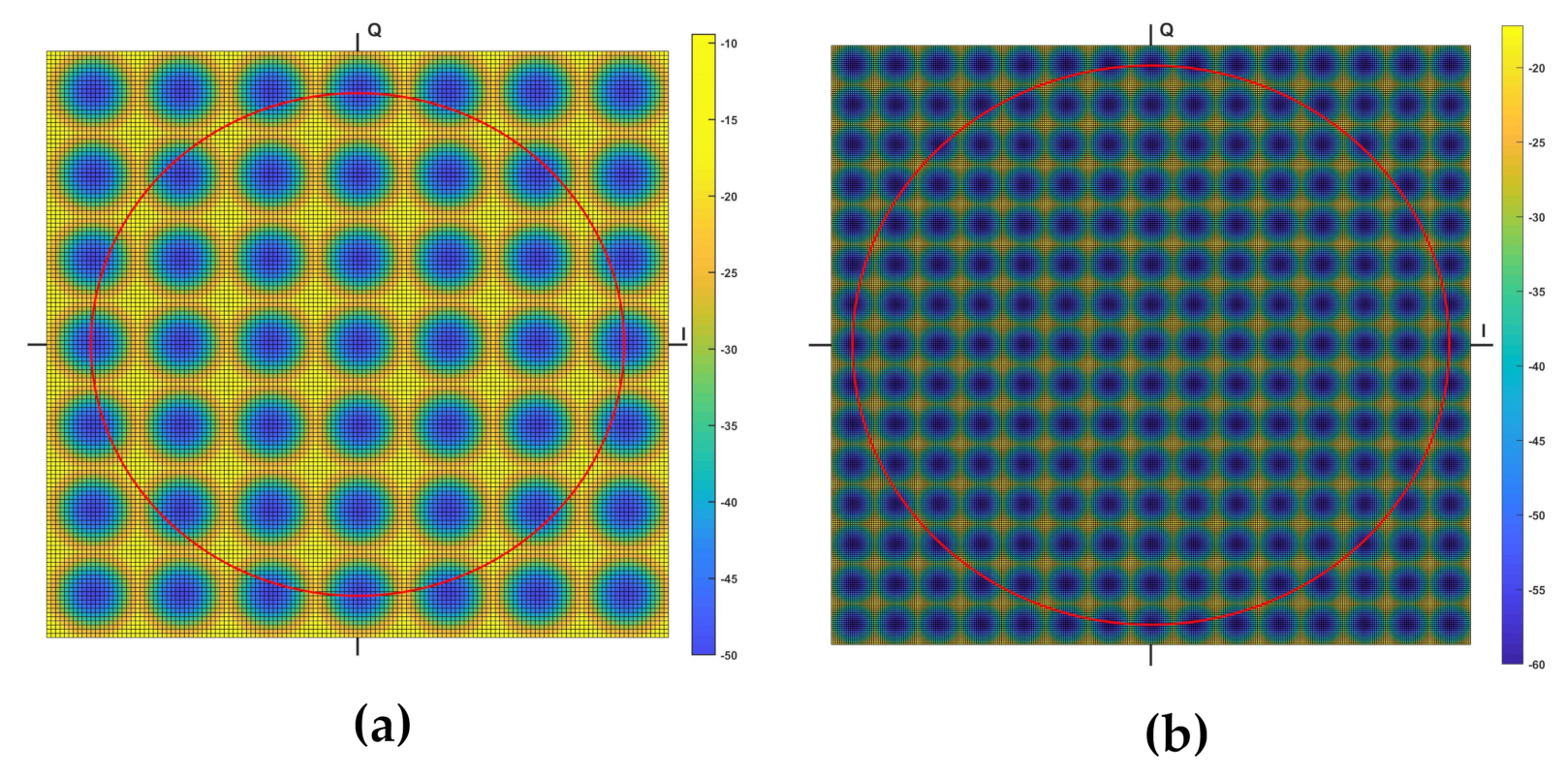

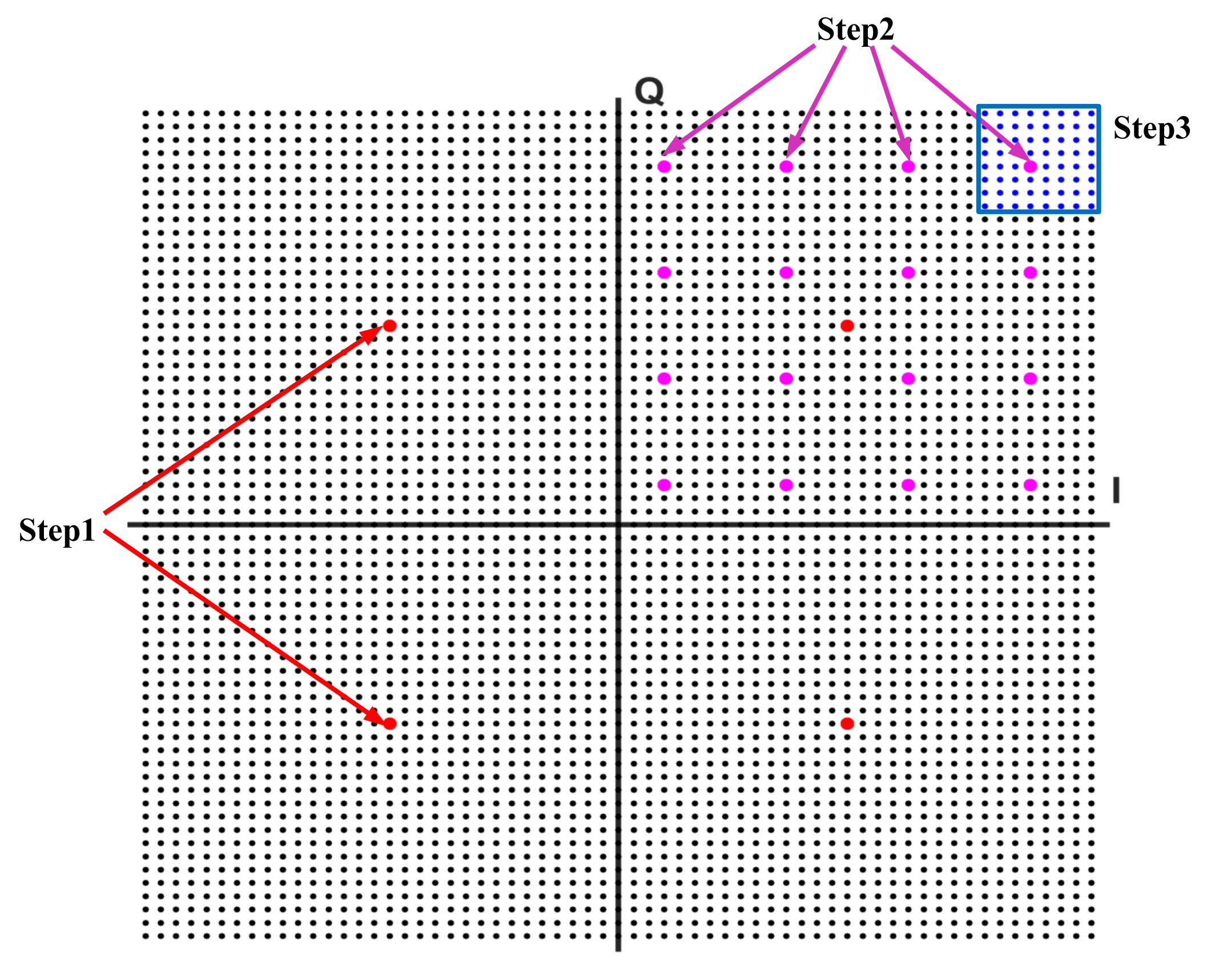

- Block search algorithm.

- Rough search: Divide the whole coordinate system into equal parts according to the lattice. Take any point with the same relative position in each lattice as the input. Find the point that minimizes the residual signal power under this step and record this point as A;

- Fine search: Search each point in the lattice where point A is located. Find the point that minimizes the residual signal power under this step. Record this point as B. B is the best cancellation point to minimize the residual signal power;

- After obtaining the best cancellation point, monitor the residual signal power constantly. If the change of residual signal power exceeds the preset value, skip to step 1. Otherwise, it will be monitored all the time.

- N-step block search algorithm.

- It is assumed that the I-channel and Q-channel signals are divided into points. Divide all points into m equal parts. In order to make the length and width after each bisection an integer, m takes the positive integer power of 2. Take any point with the same relative position in each lattice as the input. Find the point in the lattice where the residual signal power is minimized in this step;

- Continue to divide the lattice obtained in step 1 into m equal parts. Repeat step 1. The lattice obtained in the previous step is divided into a new lattice set in each step. Finally, when the size of the lattice reaches the set minimum value, all points of the minimum lattice are traversed and searched until the best cancellation point is found;

- After the best cancellation point is obtained, monitor the residual signal power constantly. If the change of residual signal power exceeds the preset value, skip to step 1. Otherwise, it will be monitored all the time.

- Divide all points into four parts according to the four quadrants in the coordinates. Use the coordinates of the central point of each part to control the variable capacitor network, and take the point that minimizes the residual power of the self-jamming signal so as to determine the quadrant;

- Divide all determined quadrants into an lattice on average. Take the coordinates of the central point of each lattice into the variable capacitor network. Take the point that minimizes the residual power of the self-jamming signal;

- Search the last 64 points. The point with the minimum residual power of the self-jamming signal is the best cancellation point.

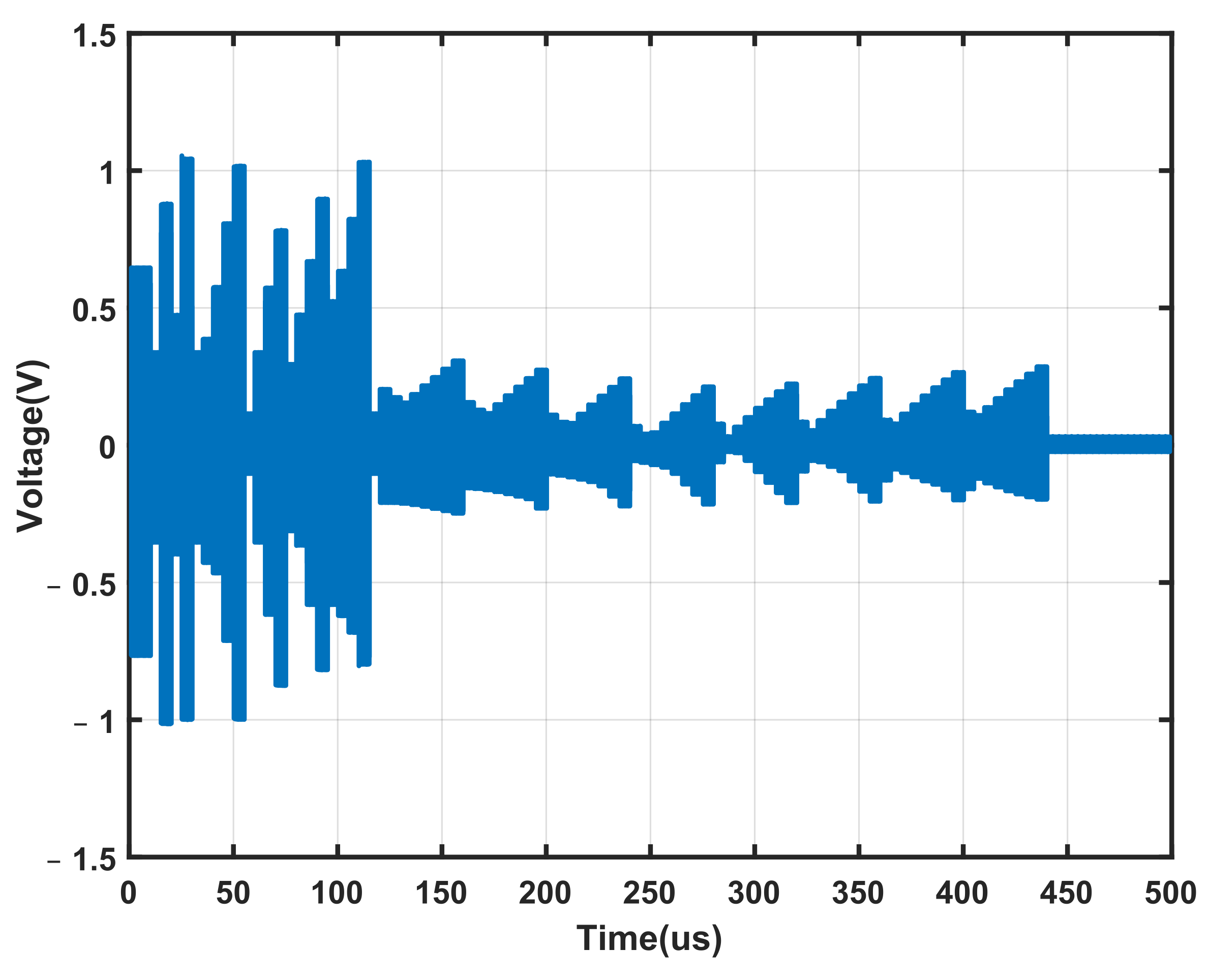

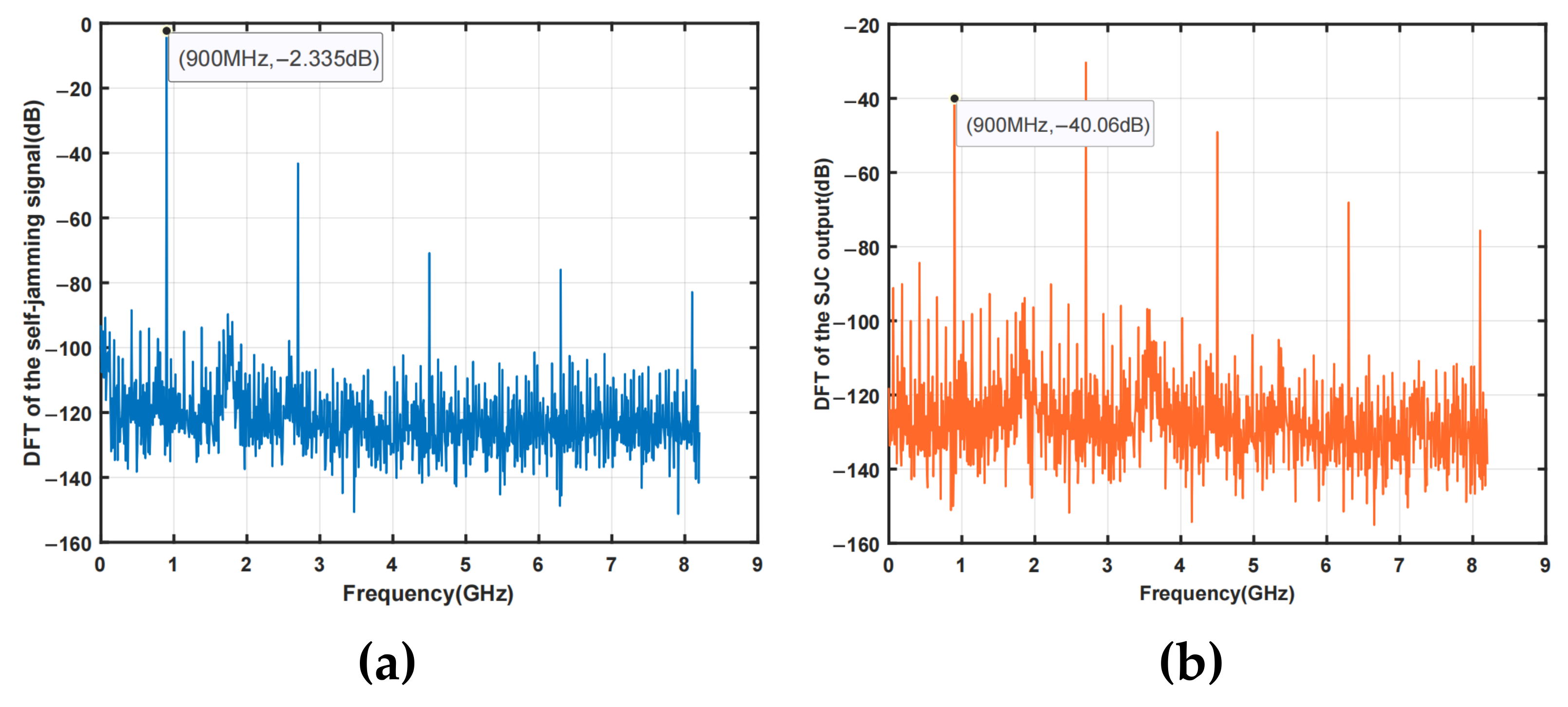

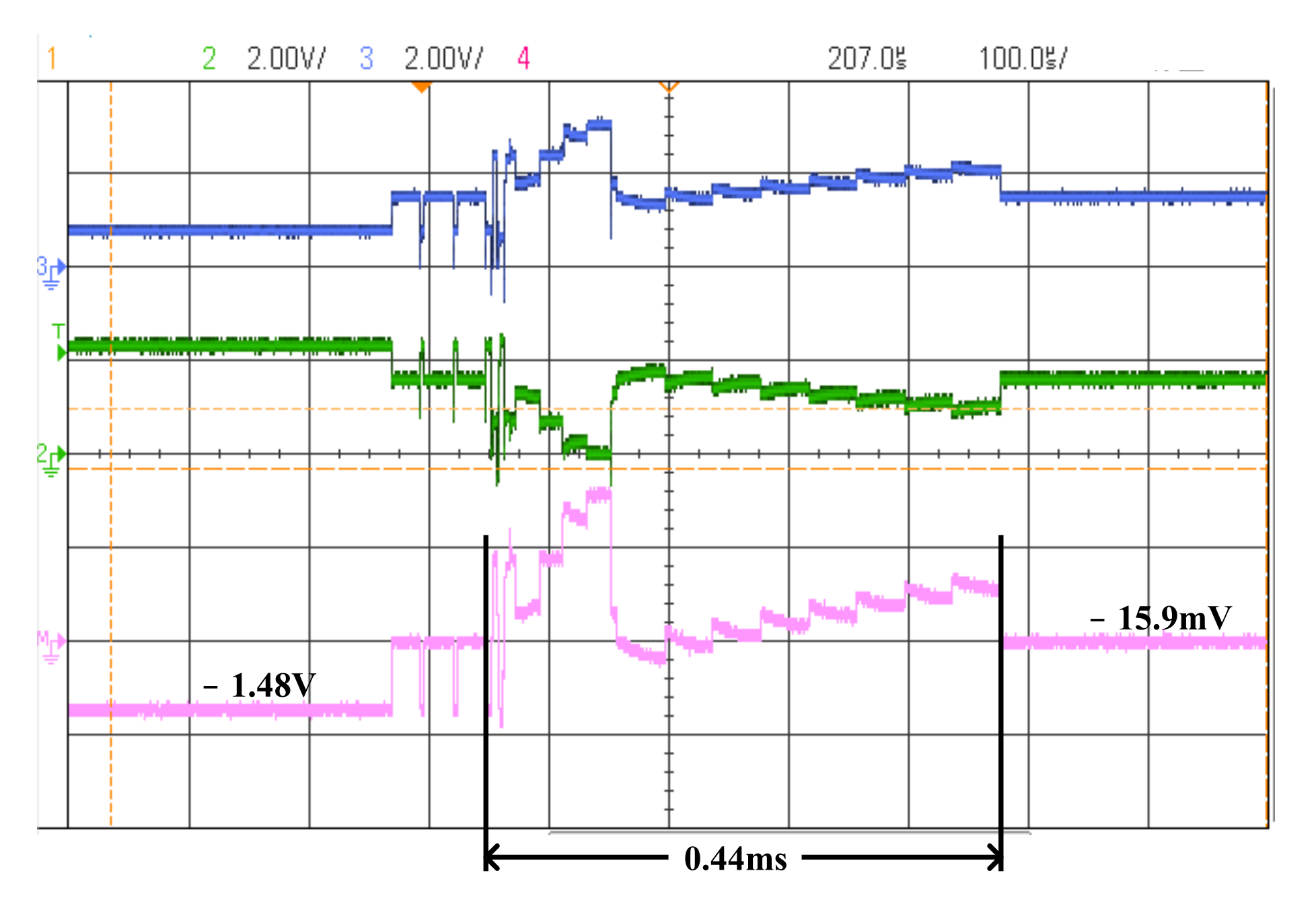

3. Simulation and Experimental Results

- Add SJC circuit before the RF front end to avoid the gain compression of the amplifier;

- The noise produced by the SJC circuit and the LO signal must be low enough to ensure a sufficient SNR of the CW signal and the cancellation signal;

- Lower the time delay between the two inputs of the SJC circuit and the mixer of the receiver to maintain the high correlation of the noise of these signals.

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Finkenzeller, K. RFID Handbook: Radio-Frequency Identification Fundamentals and Applications; Wiley: New York, NY, USA, 2003. [Google Scholar]

- Hua, G.; Ma, Y. Study on carrier cancellation in UHF RFID test system. In Proceedings of the 2015 IEEE 6th International Symposium on Microwave, Antenna, Propagation, and EMC Technologies (MAPE), Shanghai, China, 28–30 October 2015; pp. 648–651. [Google Scholar] [CrossRef]

- Chiu, S.; Kipnis, I.; Loyer, M.; Rapp, J.; Westberg, D.; Johansson, J.; Johansson, P. A 900 MHz UHF RFID Reader Transceiver IC. IEEE J.-Solid-State Circuits 2007, 42, 2822–2833. [Google Scholar] [CrossRef]

- Khannur, P.B.; Chen, X.; Yan, D.L.; Shen, D.; Zhao, B.; Raja, M.K.; Wu, Y.; Sindunata, R.; Yeoh, W.G.; Singh, R. A Universal UHF RFID Reader IC in 0.18-µm CMOS Technology. IEEE J.-Solid-State Circuits 2008, 43, 1146–1155. [Google Scholar] [CrossRef]

- Wang, W.; Lou, S.; Chui, K.W.C.; Rong, S.; Lok, C.F.; Zheng, H.; Chan, H.T.; Man, S.W.; Luong, H.C.; Lau, V.K.; et al. A Single-Chip UHF RFID Reader in 0.18 μm CMOS Process. IEEE J.-Solid-State Circuits 2008, 43, 1741–1754. [Google Scholar] [CrossRef]

- Guo, Q.; Zhai, Y.; Tan, X.; Min, H. An On-Chip Configurable Receiver With >55-dB Tx Leakage Suppression for UHF RFID Reader. IEEE Microw. Wirel. Compon. Lett. 2019, 29, 357–359. [Google Scholar] [CrossRef]

- Kim, S.; Choi, K.S.; Kim, K.M.; Ko, J.; Kim, J.; Lee, S.G. A Low-Noise and Fast-Settling UHF RFID Receiver with Digitally Controlled Leakage Cancellation. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 2810–2814. [Google Scholar] [CrossRef]

- Koller, M.; Küng, R. Adaptive carrier supression for UHF RFID using digitally tunable capacitors. In Proceedings of the 2013 European Microwave Conference, Nuremberg, Germany, 6–10 October 2013; pp. 943–946. [Google Scholar]

- Kim, M.S.; Jung, S.C.; Jeong, J.; Kim, H.; Seo, M.; Ham, J.; Park, C.S.; Yang, Y. Adaptive TX Leakage Canceler for the UHF RFID Reader Front End Using a Direct Leaky Coupling Method. IEEE Trans. Ind. Electron. 2014, 61, 2081–2087. [Google Scholar] [CrossRef]

- Ma, Z.; Jiang, Y. Carrier extraction cancellation circuit in RFID reader for improving the Tx-to-Rx isolation. Circuits Devices Syst. IET 2019, 13, 622–629. [Google Scholar]

- Mayordomo, I.; Bernhard, J. Implementation of an adaptive leakage cancellation control for passive UHF RFID readers. In Proceedings of the 2011 IEEE International Conference on RFID, Orlando, FL, USA, 12–14 April 2011; pp. 121–127. [Google Scholar] [CrossRef]

- You, B.; Bo, Y.; Wen, X.; Qu, L. Implementation of Low-Cost UHF RFID Reader Front-Ends with Carrier Leakage Suppression Circuit. Int. J. Antennas Propag. 2013, 2013, 135203. [Google Scholar] [CrossRef]

- Xiong, H.; Shen, C.; Ye, T.T. Broadband and Fast Carrier Cancellation for Backscattered RFID Communications. IEEE Microw. Wirel. Compon. Lett. 2021, 31, 84–87. [Google Scholar] [CrossRef]

- Kapucu, K.; Pauli, M.; Dehollain, C. A fast active leakage cancellation method for UHF RFID readers. In Proceedings of the 2017 IEEE International Conference on RFID (RFID), Phoenix, AZ, USA, 9–11 May 2017; pp. 182–186. [Google Scholar] [CrossRef]

- Rossi, M.; Liberati, R.M.; Frasca, M.; Richardson, J. Experimental Implementation of a Low-Cost, Fully-Analog Self-Jamming Canceller for UHF RFID Devices. Electronics 2020, 9, 786. [Google Scholar] [CrossRef]

- Budge, M.; Burt, M. Range correlation effects on phase and amplitude noise. In Proceedings of the Southeastcon 1993, Charlotte, NC, USA, 4–7 April 1993; pp. 1–5. [Google Scholar] [CrossRef]

- Wang, C.W.; Wu, H.S.; Tzuang, C.K.C. CMOS Passive Phase Shifter With Group-Delay Deviation of 6.3 ps at K-Band. IEEE Trans. Microw. Theory Tech. 2011, 59, 1778–1786. [Google Scholar] [CrossRef]

- Fang, H.R.; Tang, X.; Mouthaan, K.; Guinvarc’h, R. 180∘ and 90∘ Reflection-Type Phase Shifters Using Over-Coupled Lange Couplers. IEEE Trans. Microw. Theory Tech. 2012, 60, 3440–3448. [Google Scholar] [CrossRef]

- Lee, H.S.; Min, B.W. W-Band CMOS 4-Bit Phase Shifter for High Power and Phase Compression Points. IEEE Trans. Circuits Syst. II: Express Briefs 2015, 62, 1–5. [Google Scholar] [CrossRef]

- Huang, Y.Y.; Jeon, H.; Yoon, Y.; Woo, W.; Lee, C.H.; Kenney, J.S. An Ultra-Compact, Linearly-Controlled Variable Phase Shifter Designed With a Novel RC Poly-Phase Filter. IEEE Trans. Microw. Theory Tech. 2012, 60, 301–310. [Google Scholar] [CrossRef]

- Kaukovuori, J.; Stadius, K.; Ryynanen, J.; Halonen, K.A.I. Analysis and Design of Passive Polyphase Filters. IEEE Trans. Circuits Syst. I Regul. Pap. 2008, 55, 3023–3037. [Google Scholar] [CrossRef]

- Meyer, R. Low-power monolithic RF peak detector analysis. IEEE J.-Solid-State Circuits 1995, 30, 65–67. [Google Scholar] [CrossRef]

- Boaventura, A.; Santos, J.; Oliveira, A.; Carvalho, N.B. Perfect Isolation: Dealing with Self-Jamming in Passive RFID Systems. IEEE Microw. Mag. 2016, 17, 20–39. [Google Scholar] [CrossRef]

- Hong, C.M.; Chen, C.M.; Fan, H.K. A New Gradient-Based Search Method: Grey-Gradient Search Method; Springer Inc.: New York, NY, USA, 1999. [Google Scholar]

- Lasser, G.; Langwieser, R. Automatic leaking carrier canceller adjustment techniques. EURASIP J. Embed. Syst. 2013, 2013, 8. [Google Scholar] [CrossRef] [Green Version]

- Jung, J.Y.; Park, C.W.; Yeom, K.W. A Novel Carrier Leakage Suppression Front-End for UHF RFID Reader. IEEE Trans. Microw. Theory Tech. 2012, 60, 1468–1477. [Google Scholar] [CrossRef]

- Ghahremani, A.; Rezaei, V.D.; Sharif Bakhtiar, M. A UHF-RFID Transceiver with a Blocker-Canceller Feedback and +30 dBm Output Power. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 3043–3054. [Google Scholar] [CrossRef]

| MWCL 2021 [13] | RFID 2017 [14] | TMTT 2012 [26] | TCAS-I 2013 [27] | MWCL 2019 [6] | TCAS-II 2021 [7] | This Work | |

|---|---|---|---|---|---|---|---|

| Technology | N/A | N/A | N/A | 0.18 µm CMOS | 0.13 µm CMOS | 55 nm CMOS | 0.18 µm CMOS |

| Integration (-chip) | off | off | off | on | on | on | on |

| Self-jamming Suppression (dB) | 46.2–61.7 | 50 | 36 | 35 | 14.7 | 43.8 | 38 |

| Settling Time (ms) | 0.5 | 20 | 0.4 | 0.033 | 0.009 | 0.027 | 0.44 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, Q.; Li, Z.; Jiang, D.; Shan, Q.; Wei, Z.; Xiao, J.; Huang, S.; Liu, Y. A Fully Integrated Passive Self-Jamming Cancellation Architecture with Fast Settling Time for UHF RFID Reader. Electronics 2022, 11, 2311. https://doi.org/10.3390/electronics11152311

Chen Q, Li Z, Jiang D, Shan Q, Wei Z, Xiao J, Huang S, Liu Y. A Fully Integrated Passive Self-Jamming Cancellation Architecture with Fast Settling Time for UHF RFID Reader. Electronics. 2022; 11(15):2311. https://doi.org/10.3390/electronics11152311

Chicago/Turabian StyleChen, Qinan, Zheng Li, Dahai Jiang, Qiang Shan, Zihui Wei, Jinjin Xiao, Shuilong Huang, and Yu Liu. 2022. "A Fully Integrated Passive Self-Jamming Cancellation Architecture with Fast Settling Time for UHF RFID Reader" Electronics 11, no. 15: 2311. https://doi.org/10.3390/electronics11152311

APA StyleChen, Q., Li, Z., Jiang, D., Shan, Q., Wei, Z., Xiao, J., Huang, S., & Liu, Y. (2022). A Fully Integrated Passive Self-Jamming Cancellation Architecture with Fast Settling Time for UHF RFID Reader. Electronics, 11(15), 2311. https://doi.org/10.3390/electronics11152311