Improving Symbolic System-Level Synthesis by Solver Coordination and Domain-Specific Heuristics

Abstract

:1. Introduction

- (I)

- We present a coordinated SMT-based synthesis approach that eases the task of the -solver to compute a feedback to the logic solver. This is realized by introducing a scheduling-aware binding and routing refinement in the logic solver.

- (II)

- We present how domain-specific heuristics (DSH) applied within the logic solver allow us to further increase scalability of our approach by utilizing our domain knowledge.

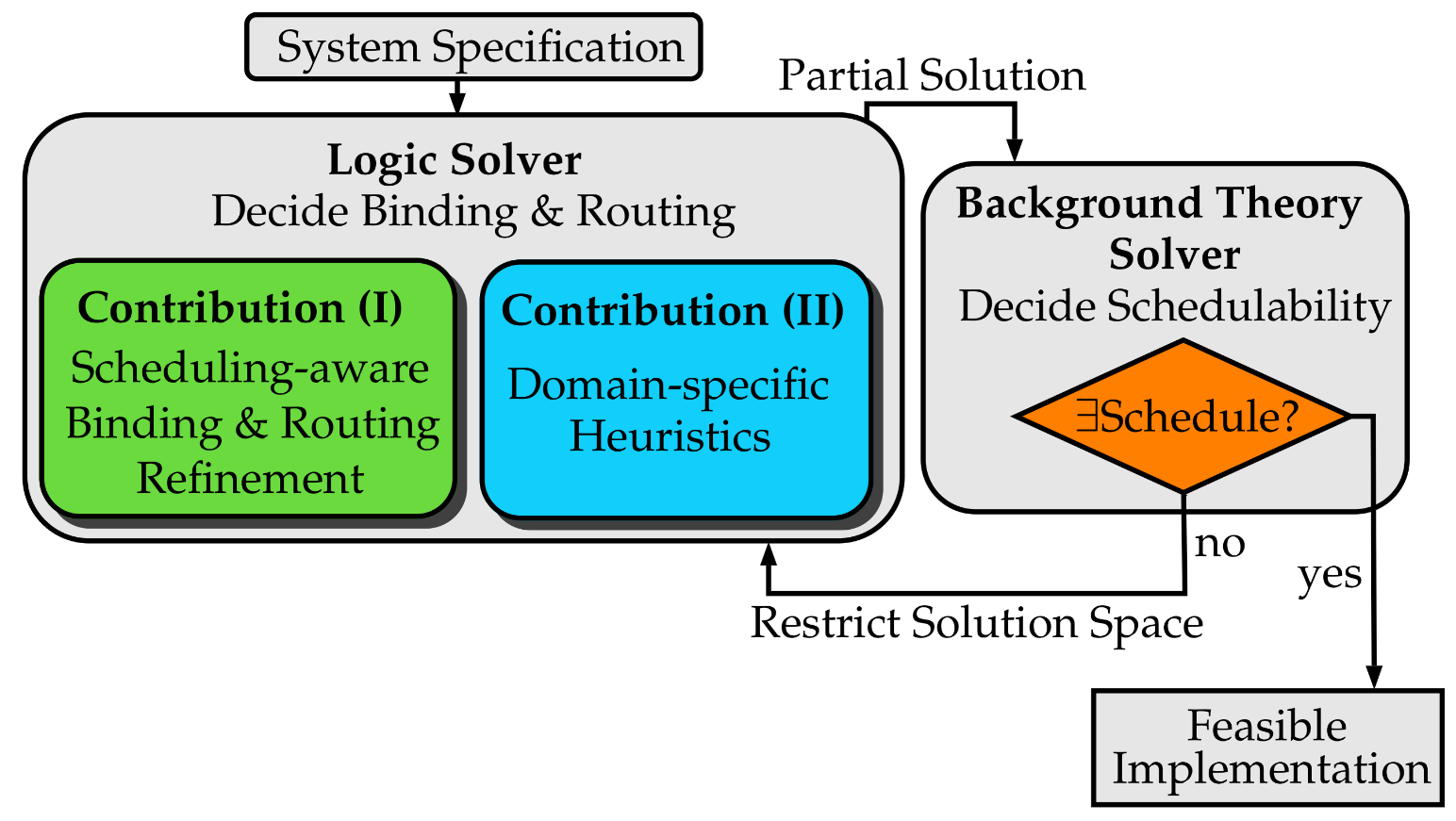

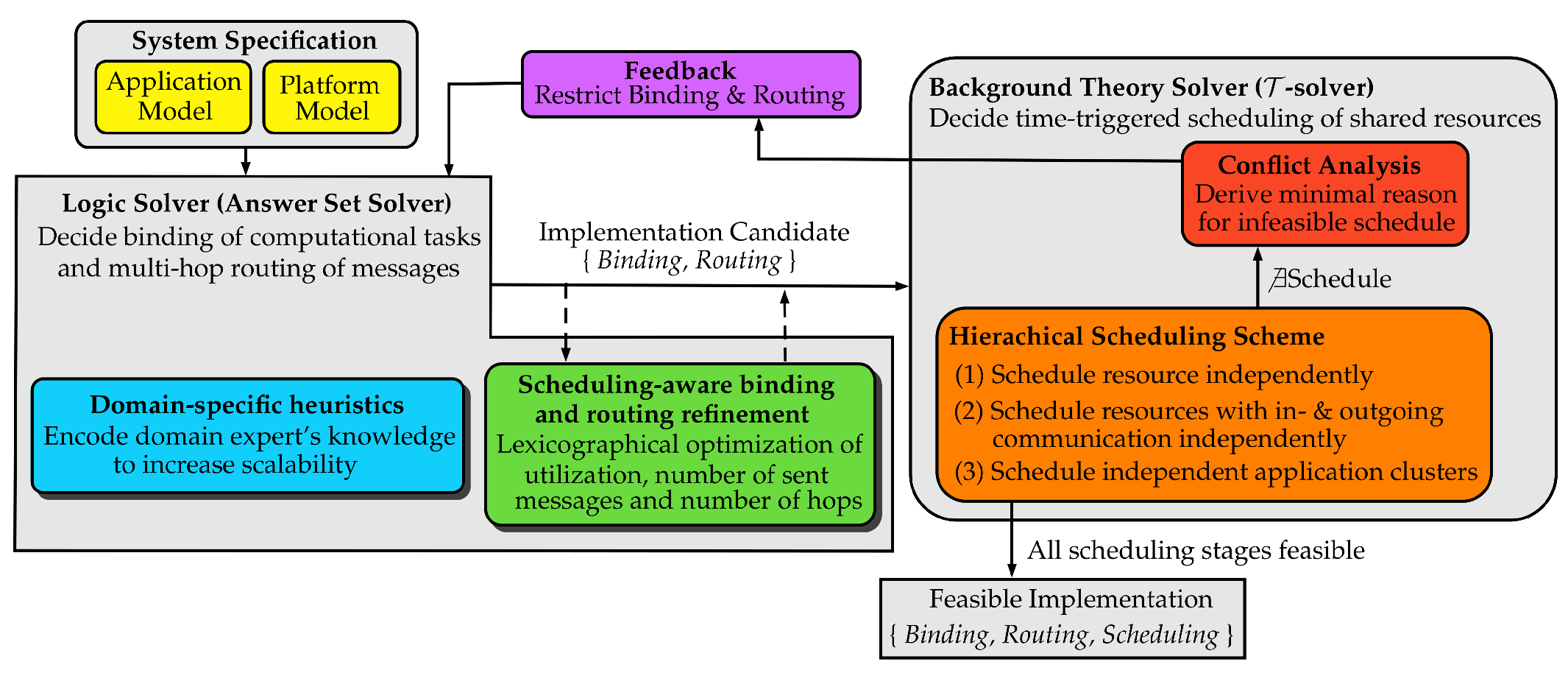

2. Coordinated SMT-Based Synthesis Approach: Motivation & Detailed Overview

2.1. (Classical) SMT-Based System Synthesis

2.2. Coordinated SMT-Based System Synthesis

2.3. Increasing Scalability of Coordinated SMT-Based Synthesis by Domain-Specific Heuristics

3. Related Work

4. System Model

4.1. Platform Model

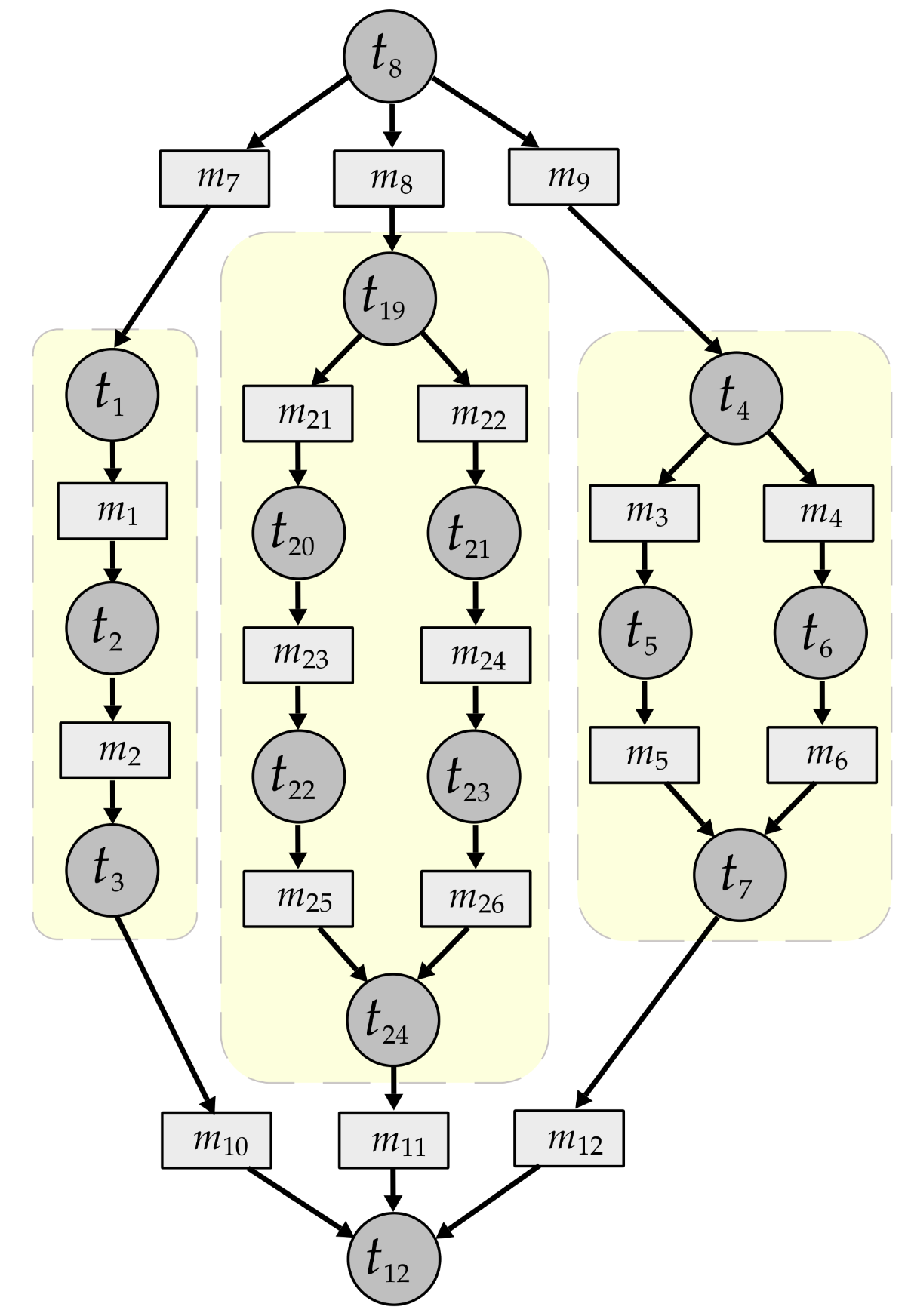

4.2. Application Model

- (i)

- An application graph with two computational tasks exchanging one message is a TTSP application graph.

- (ii)

- If the application graphs and are TTSP application graphs, so is the resulting application graph of the following two operations:

- (a)

- Two terminal parallel composition:Replace the source computational task of TTSP graph with the source computational task of TTSP graph and replace the sink computational task of with the sink computational task of .

- (b)

- Two terminal series composition:Replace the sink computational task of TTSP graph with the source computational task of TTSP graph .

4.3. Formal Problem Formulation

5. Answer Set Programming (ASP)—Binding & Routing

5.1. Scheduling-Aware Binding & Routing Refinement

5.2. Domain-Specific Heuristics in ASP

6. Time-Triggered Scheduling

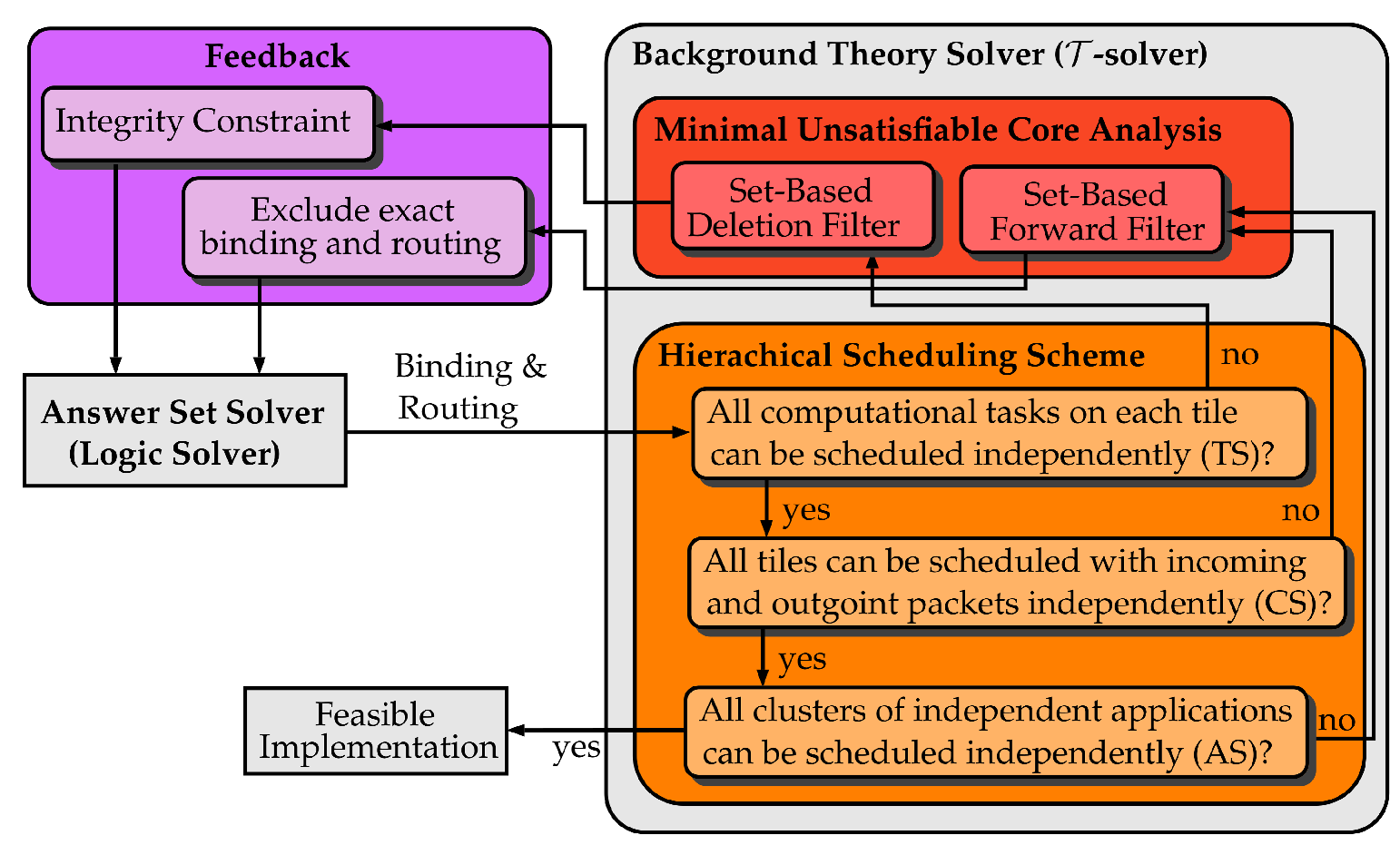

7. Coupling ASP and Background Theory

- Schedule computational tasks on each tile independently (TS),

- Schedule computational tasks on each tile with the incoming and outgoing packets of the tile independently (CS),

- Schedule clusters of independent applications independently (AS).

| Algorithm 1 Set-based Deletion Filter for stage (TS). |

| Input: Unsatisfiable scheduling problem constraints C⊥ of stage (TS) and the corresponding set of tasks |

| Output: A minimal set of infeasible computational tasks |

| 1: C = C⊥ |

| 2: |

| 3: for t ∈ do |

| 4: if then |

| 5: |

| 6: |

| 7: end if |

| 8: end for |

| 9: return |

8. Experimental Results

8.1. Test Instances

8.2. Experimental Setup

8.3. Experimental Results

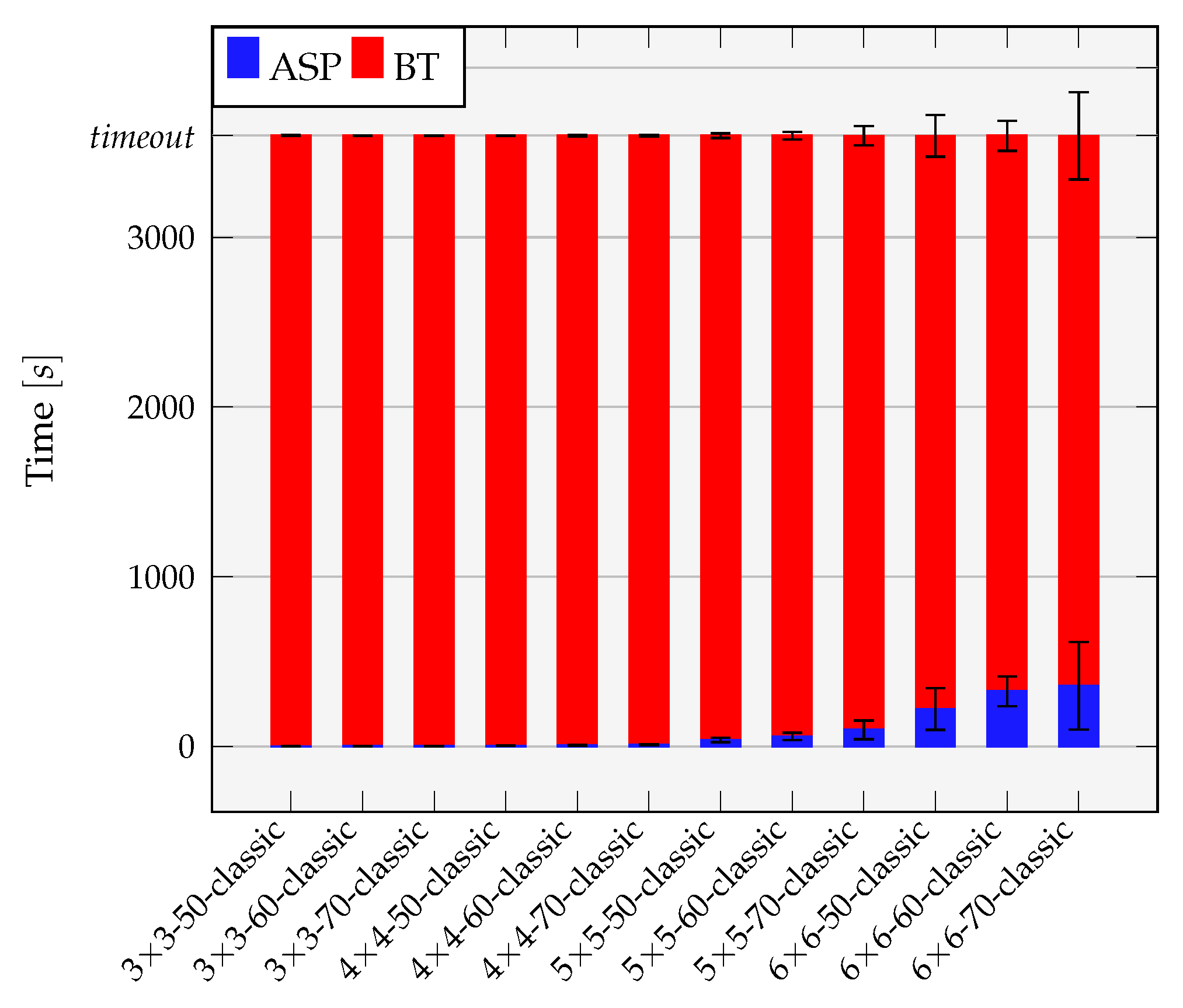

8.3.1. Results of Classical Approach without Coordination

8.3.2. Results of Coordinated Approach

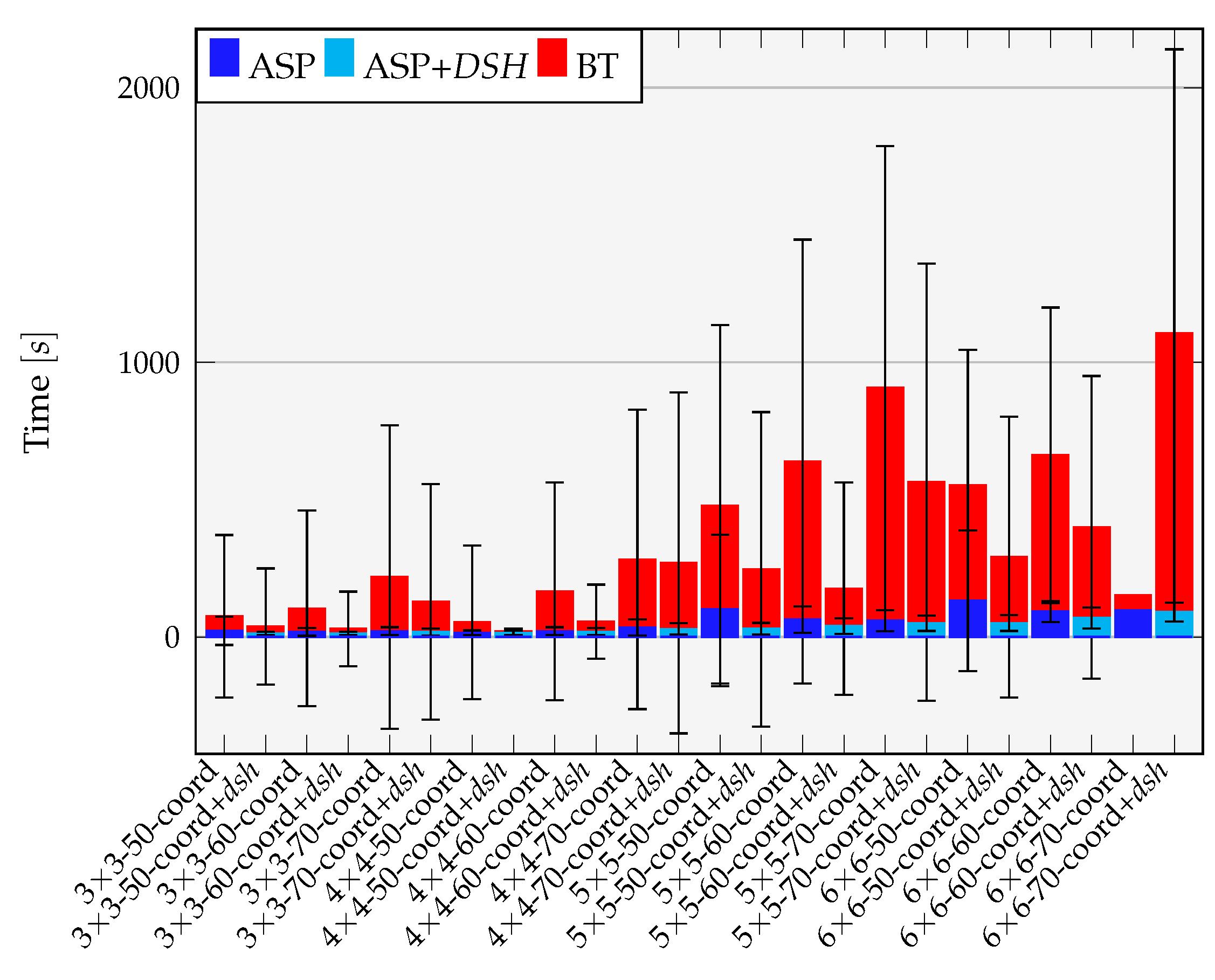

8.3.3. Results of Coordinated Approach with DSH

9. Concluding Remarks

Author Contributions

Funding

Conflicts of Interest

References

- Gerstlauer, A.; Haubelt, C.; Pimentel, A.D.; Stefanov, T.P.; Gajski, D.D.; Teich, J. Electronic System-Level Synthesis Methodologies. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2009, 28, 1517–1530. [Google Scholar] [CrossRef] [Green Version]

- Infineon. AURIX 32-Bit TriCore TC2xx Product Specification. Available online: https://www.infineon.com/cms/en/product/microcontroller/32-bit-tricore-microcontroller/32-bit-tricore-aurix-tc2xx/ (accessed on 14 June 2022).

- Bjerregaard, T.; Mahadevan, S. A survey of research and practices of Network-on-chip. ACM Comput. Surv. 2006, 38, 1. [Google Scholar] [CrossRef]

- Hennessy, J.L.; Patterson, D.A. Computer Architecture—A Quantitative Approach, 5th ed.; Appendix F: Interconnection Networks; Morgan Kaufmann: Waltham, MA, USA, 2012. [Google Scholar]

- Reimann, F.; Glaß, M.; Haubelt, C.; Eberl, M.; Teich, J. Improving platform-based system synthesis by satisfiability modulo theories solving. In Proceedings of the 8th International Conference on Hardware/Software Codesign and System Synthesis, CODES+ISSS, Scottsdale, AZ, USA, 24–28 October 2010; pp. 135–144. [Google Scholar] [CrossRef]

- Reimann, F.; Lukasiewycz, M.; Glaß, M.; Haubelt, C.; Teich, J. Symbolic system synthesis in the presence of stringent real-time constraints. In Proceedings of the 48th Design Automation Conference, DAC, San Diego, CA, USA, 5–10 June 2011; pp. 393–398. [Google Scholar] [CrossRef]

- Lukasiewycz, M.; Chakraborty, S. Concurrent architecture and schedule optimization of time-triggered automotive systems. In Proceedings of the 10th International Conference on Hardware/Software Codesign and System Synthesis, CODES+ISSS, Tampere, Finland, 7–12 October 2012; pp. 383–392. [Google Scholar] [CrossRef]

- Valdes, J.; Tarjan, R.E.; Lawler, E.L. The recognition of Series Parallel digraphs. In Proceedings of the 11th Annual ACM Symposium on Theory of Computing, Atlanta, GE, USA, 30 April–2 May 1979; pp. 1–12. [Google Scholar] [CrossRef]

- Neubauer, K.; Wanko, P.; Schaub, T.; Haubelt, C. Enhancing symbolic system synthesis through ASPmT with partial assignment evaluation. In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition, DATE, Lausanne, Switzerland, 27–31 March 2017; pp. 306–309. [Google Scholar] [CrossRef]

- Kumar, P.; Chokshi, D.B.; Thiele, L. A satisfiability approach to speed assignment for distributed real-time systems. In Proceedings of the Design, Automation and Test in Europe, DATE, Grenoble, France, 18–22 March 2013; pp. 749–754. [Google Scholar] [CrossRef]

- Baral, C. Knowledge Representation, Reasoning and Declarative Problem Solving; Cambridge University Press: Cambridge, UK, 2003. [Google Scholar] [CrossRef] [Green Version]

- Gelfond, M.; Kahl, Y. Knowledge Representation, Reasoning, and the Design of Intelligent Agents: The Answer-Set Programming Approach; Cambridge University Press: Cambridge, UK, 2014. [Google Scholar] [CrossRef] [Green Version]

- Gebser, M.; Kaminski, R.; Kaufmann, B.; Schaub, T. Answer Set Solving in Practice; Synthesis Lectures on Artificial Intelligence and Machine Learning; Morgan & Claypool Publishers: San Rafael, CA, USA, 2012. [Google Scholar] [CrossRef]

- Andres, B.; Gebser, M.; Schaub, T.; Haubelt, C.; Reimann, F.; Glaß, M. Symbolic System Synthesis Using Answer Set Programming. In Proceedings of the 12th International Conference on Logic Programming and Nonmonotonic Reasoning, LPNMR, Corunna, Spain, 15–19 September 2013; Volume 8148, pp. 79–91. [Google Scholar] [CrossRef]

- Barrett, C.W.; Sebastiani, R.; Seshia, S.A.; Tinelli, C. Satisfiability Modulo Theories. In Handbook of Satisfiability; IOS Press: Amsterdam, The Netherlands, 2009; Volume 185, pp. 825–885. [Google Scholar] [CrossRef]

- Gebser, M.; Kaufmann, B.; Schaub, T. Conflict-driven answer set solving: From theory to practice. Artif. Intell. 2012, 187, 52–89. [Google Scholar] [CrossRef] [Green Version]

- Gebser, M.; Kaufmann, B.; Romero, J.; Otero, R.; Schaub, T.; Wanko, P. Domain-Specific Heuristics in Answer Set Programming. In Proceedings of the Twenty-Seventh AAAI Conference on Artificial Intelligence, Bellevue, WA, USA, 14–18 July 2013. [Google Scholar]

- Lukasiewycz, M.; Streubühr, M.; Glaß, M.; Haubelt, C.; Teich, J. Combined system synthesis and communication architecture exploration for MPSoCs. In Proceedings of the Design, Automation and Test in Europe, DATE, Nice, France, 20–24 April 2009; pp. 472–477. [Google Scholar] [CrossRef] [Green Version]

- Nieuwenhuis, R.; Oliveras, A.; Tinelli, C. Solving SAT and SAT Modulo Theories: From an abstract Davis–Putnam–Logemann–Loveland procedure to DPLL(T). J. ACM 2006, 53, 937–977. [Google Scholar] [CrossRef]

- Satish, N.; Ravindran, K.; Keutzer, K. A decomposition-based constraint optimization approach for statically scheduling task graphs with communication delays to multiprocessors. In Proceedings of the Design, Automation and Test in Europe, DATE, Nice, France, 16–20 April 2007; pp. 57–62. [Google Scholar] [CrossRef] [Green Version]

- Liu, W.; Gu, Z.; Xu, J.; Wu, X.; Ye, Y. Satisfiability Modulo Graph Theory for Task Mapping and Scheduling on Multiprocessor Systems. IEEE Trans. Parallel Distrib. Syst. 2011, 22, 1382–1389. [Google Scholar] [CrossRef]

- Jackson, E.K.; Kang, E.; Dahlweid, M.; Seifert, D.; Santen, T. Components, platforms and possibilities: Towards generic automation for MDA. In Proceedings of the 10th International Conference on Embedded Software, EMSOFT, Scottsdale, AZ, USA, 24–29 October 2010; pp. 39–48. [Google Scholar] [CrossRef]

- Chakraborty, S.; Künzli, S.; Thiele, L. A General Framework for Analysing System Properties in Platform-Based Embedded System Designs. In Proceedings of the Design, Automation and Test in Europe, DATE, Munich, Germany, 3–7 March 2003; pp. 10190–10195. [Google Scholar] [CrossRef]

- Gebser, M.; Kaminski, R.; Kaufmann, B.; Ostrowski, M.; Schaub, T.; Wanko, P. Theory Solving Made Easy with Clingo 5. In Proceedings of the Technical Communications of the 32nd International Conference on Logic Programming, ICLP, New York, NY, USA, 16–21 October 2016; Volume 52, pp. 2:1–2:5. [Google Scholar] [CrossRef]

- Neubauer, K.; Beichler, B.; Haubelt, C. Exact Design Space Exploration Based on Consistent Approximations. Electronics 2020, 9, 1057. [Google Scholar] [CrossRef]

- Biewer, A.; Andres, B.; Gladigau, J.; Schaub, T.; Haubelt, C. A symbolic system synthesis approach for hard real-time systems based on coordinated SMT-solving. In Proceedings of the Design, Automation & Test in Europe, DATE, Grenoble, France, 9–13 March 2015; pp. 357–362. [Google Scholar]

- Andres, B.; Biewer, A.; Romero, J.; Haubelt, C.; Schaub, T. Improving Coordinated SMT-Based System Synthesis by Utilizing Domain-Specific Heuristics. In Proceedings of the 13th International Logic Programming and Nonmonotonic Reasoninh Conference, LPNMR, Lexington, KY, USA, 27–30 September 2015; pp. 55–68. [Google Scholar] [CrossRef]

- Korst, J.H.M.; Aarts, E.H.L.; Lenstra, J.K.; Wessels, J. Periodic Multiprocessor Scheduling. In Proceedings of the Parallel Architectures and Languages Europe, PARLE, Eindhoven, The Netherlands, 10–13 June 1991; pp. 166–178. [Google Scholar] [CrossRef] [Green Version]

- Biewer, A.; Munk, P.; Gladigau, J.; Haubelt, C. On the Influence of Hardware Design Options on Schedule Synthesis in Time-Triggered Real-Time Systems. In Proceedings of the Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen, MBMV, Chemnitz, Germany, 3–4 March 2015; pp. 105–114. [Google Scholar]

- Lukasiewycz, M.; Schneider, R.; Goswami, D.; Chakraborty, S. Modular scheduling of distributed heterogeneous time-triggered automotive systems. In Proceedings of the 17th Asia and South Pacific Design Automation Conference, ASP-DAC, Sydney, Australia, 30 January–2 February 2012; pp. 665–670. [Google Scholar] [CrossRef]

- Minaeva, A.; Akesson, B.; Hanzálek, Z.; Dasari, D. Time-Triggered Co-Scheduling of Computation and Communication with Jitter Requirements. IEEE Trans. Comput. 2018, 67, 115–129. [Google Scholar] [CrossRef] [Green Version]

- Steiner, W. An Evaluation of SMT-Based Schedule Synthesis for Time-Triggered Multi-hop Networks. In Proceedings of the 31st IEEE Real-Time Systems Symposium, RTSS, San Diego, CA, USA, 30 November–3 December 2010; pp. 375–384. [Google Scholar] [CrossRef]

- Steiner, W. Synthesis of Static Communication Schedules for Mixed-Criticality Systems. In Proceedings of the 14th IEEE International Symposium on Object/Component/Service-Oriented Real-Time Distributed Computing Workshops, ISORC Workshops, Newport Beach, CA, USA, 28–31 March 2011; pp. 11–18. [Google Scholar] [CrossRef]

- Huang, J.; Blech, J.O.; Raabe, A.; Buckl, C.; Knoll, A.C. Static scheduling of a Time-Triggered Network-on-Chip based on SMT solving. In Proceedings of the Design, Automation & Test in Europe, DATE, Dresden Germany, 12–16 March 2012; pp. 509–514. [Google Scholar] [CrossRef] [Green Version]

- Craciunas, S.S.; Oliver, R.S. SMT-based Task- and Network-level Static Schedule Generation for Time-Triggered Networked Systems. In Proceedings of the 22nd International Conference on Real-Time Networks and Systems, RTNS, Versailles, France, 8–10 October 2014; p. 45. [Google Scholar] [CrossRef] [Green Version]

- Zhang, L.; Goswami, D.; Schneider, R.; Chakraborty, S. Task- and network-level schedule co-synthesis of Ethernet-based time-triggered systems. In Proceedings of the 19th Asia and South Pacific Design Automation Conference, ASP-DAC, Singapore, 20–23 January 2014; pp. 119–124. [Google Scholar] [CrossRef]

- Schweissguth, E.B.; Danielis, P.; Timmermann, D.; Parzyjegla, H.; Mühl, G. ILP-based joint routing and scheduling for time-triggered networks. In Proceedings of the 25th International Conference on Real-Time Networks and Systems, RTNS, Grenoble, France, 4–6 October 2017; pp. 8–17. [Google Scholar] [CrossRef]

- Ostrowski, M.; Schaub, T. ASP modulo CSP: The clingcon system. Theory Pract. Log. Program. 2012, 12, 485–503. [Google Scholar] [CrossRef] [Green Version]

- Kramer, S.; Ziegenbein, D.; Hamann, A. Real world automotive benchmarks for free. In Proceedings of the 6th International Workshop on Analysis Tools and Methodologies for Embedded and Real-time Systems, WATERS, Lund, Sweden, 7 July 2015. [Google Scholar]

- Beyer, D. Reliable and Reproducible Competition Results with BenchExec and Witnesses (Report on SV-COMP 2016). In Proceedings of the 22nd International Conference Tools and Algorithms for the Construction and Analysis of Systems, TACAS, Eindhoven, The Netherlands, 2–8 April 2016; Volume 9636, pp. 887–904. [Google Scholar] [CrossRef]

- Dutertre, B. Yices 2.2. In Proceedings of the 26th International Conference on Computer Aided Verification, CAV, Vienna, Austria, 18–22 July 2014; Volume 8559, pp. 737–744. [Google Scholar] [CrossRef] [Green Version]

- De Moura, L.M.; Bjørner, N. Z3: An Efficient SMT Solver. In Proceedings of the 14th International Conference on Tools and Algorithms for the Construction and Analysis of Systems, TACAS, Munich, Germany, 29 March–6 April 2008; Volume 4963, pp. 337–340. [Google Scholar] [CrossRef] [Green Version]

- Pozo, F.; Rodríguez-Navas, G.; Hansson, H.; Steiner, W. SMT-based synthesis of TTEthernet schedules: A performance study. In Proceedings of the 10th IEEE International Symposium on Industrial Embedded Systems, SIES, Siegen, Germany, 8–10 June 2015; pp. 162–165. [Google Scholar] [CrossRef]

| Set | Applications | Tasks | Messages | Packets |

|---|---|---|---|---|

| 3 × 3-50 | 9.5 ± 1.3 | 129.9 ± 5.4 | 163.6 ± 8.0 | 1641.2 ± 97.4 |

| 3 × 3-60 | 11.2 ± 1.1 | 156.0 ± 4.3 | 198.8 ± 7.6 | 1980.8 ± 75.8 |

| 3 × 3-70 | 13.3 ± 1.2 | 179.5 ± 4.2 | 228.8 ± 7.2 | 2293.0 ± 101.0 |

| 4 × 4-50 | 17.2 ± 1.9 | 227.5 ± 6.1 | 286.3 ± 8.7 | 2853.6 ± 102.8 |

| 4 × 4-60 | 19.6 ± 1.4 | 272.8 ± 7.2 | 346.3 ± 11.7 | 3467.9 ± 118.5 |

| 4 × 4-70 | 23.8 ± 1.7 | 319.9 ± 7.5 | 405.1 ± 13.5 | 4046.6 ± 135.6 |

| 5 × 5-50 | 26.9 ± 2.1 | 359.9 ± 6.8 | 453.5 ± 12.5 | 4516.1 ± 140.8 |

| 5 × 5-60 | 31.8 ± 3.1 | 433.4 ± 10.4 | 548.4 ± 16.4 | 5491.0 ± 170.8 |

| 5 × 5-70 | 37.1 ± 2.1 | 501.0 ± 9.0 | 634.2 ± 12.0 | 6339.4 ± 124.7 |

| 6 × 6-50 | 38.8 ± 2.7 | 515.1 ± 11.3 | 649.8 ± 15.3 | 6488.0 ± 163.2 |

| 6 × 6-60 | 46.1 ± 2.8 | 620.2 ± 10.7 | 788.1 ± 15.0 | 7888.8 ± 180.0 |

| 6 × 6-70 | 53.4 ± 2.8 | 723.6 ± 13.1 | 916.2 ± 19.5 | 9118.6 ± 174.2 |

| Solved Runs (out of 5) | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 5/5 | 4/5 | 3/5 | 2/5 | 1/5 | 0/5 | |||||||||||||

| Instances | Classical | Coord | DSH | Classical | Coord | DSH | Classical | Coord | DSH | Classical | Coord | DSH | Classical | Coord | DSH | Classical | Coord | DSH |

| 3 × 3-50 | 0 | 25 | 24 | 2 | 0 | 1 | 8 | 0 | 0 | 3 | 0 | 0 | 11 | 0 | 0 | 1 | 0 | 0 |

| 3 × 3-60 | 0 | 17 | 22 | 0 | 2 | 2 | 4 | 3 | 1 | 3 | 0 | 0 | 4 | 1 | 0 | 14 | 2 | 0 |

| 3 × 3-70 | 0 | 6 | 10 | 0 | 3 | 9 | 1 | 5 | 3 | 2 | 3 | 2 | 1 | 3 | 1 | 21 | 5 | 0 |

| 4 × 4-50 | 0 | 22 | 25 | 0 | 3 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 5 | 0 | 0 | 19 | 0 | 0 |

| 4 × 4-60 | 0 | 11 | 17 | 0 | 7 | 5 | 0 | 4 | 3 | 0 | 3 | 0 | 0 | 0 | 0 | 25 | 0 | 0 |

| 4 × 4-70 | 0 | 2 | 7 | 0 | 2 | 4 | 0 | 6 | 7 | 0 | 7 | 5 | 0 | 6 | 0 | 25 | 2 | 2 |

| 5 × 5-50 | 0 | 13 | 15 | 0 | 7 | 6 | 0 | 3 | 1 | 1 | 1 | 3 | 2 | 1 | 0 | 22 | 0 | 0 |

| 5 × 5-60 | 0 | 2 | 7 | 0 | 4 | 7 | 0 | 2 | 5 | 0 | 8 | 4 | 0 | 5 | 2 | 25 | 4 | 0 |

| 5 × 5-70 | 0 | 0 | 0 | 0 | 2 | 5 | 0 | 1 | 4 | 0 | 3 | 10 | 0 | 4 | 5 | 25 | 15 | 1 |

| 6 × 6-50 | 0 | 0 | 7 | 0 | 4 | 8 | 0 | 0 | 6 | 0 | 1 | 3 | 0 | 5 | 1 | 25 | 15 | 0 |

| 6 × 6-60 | 0 | 0 | 2 | 0 | 0 | 1 | 0 | 1 | 8 | 0 | 4 | 7 | 0 | 1 | 4 | 25 | 19 | 3 |

| 6 × 6-70 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 4 | 0 | 1 | 8 | 25 | 24 | 13 |

| Instances | ASP [s] | BT [s] | #Runs |

|---|---|---|---|

| 5 × 5-70-coord | 73.2 ± 59.29 | 3524.52 ± 61.79 | 101 |

| 6 × 6-50-coord | 56.08 ± 38.35 | 3543.35 ± 38.98 | 16 |

| 6 × 6-60-coord | 182.29 ± 262.79 | 3414.78 ± 265.51 | 43 |

| 6 × 6-70-coord | 95.96 ± 69.58 | 3502.41 ± 71.61 | 88 |

| Instances | ASP [s] | BT [s] | #Runs |

|---|---|---|---|

| 6 × 6-50-coord | 3544.33 ± 232.81 | 53.4 ± 232.83 | 61 |

| 6 × 6-60-coord | 3406.34 ± 508.62 | 192.16 ± 508.21 | 63 |

| 6 × 6-70-coord | 3429.24 ± 389.46 | 169.56 ± 389.26 | 36 |

| Instances | #Runs out of Memory in BT |

|---|---|

| 5 × 5-50-coord | 7 |

| 5 × 5-60-coord | 2 |

| 5 × 5-70-coord | 2 |

| 6 × 6-50-coord | 25 |

| 6 × 6-60-coord | 7 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Haubelt, C.; Rausch, A. Improving Symbolic System-Level Synthesis by Solver Coordination and Domain-Specific Heuristics. Electronics 2022, 11, 1888. https://doi.org/10.3390/electronics11121888

Haubelt C, Rausch A. Improving Symbolic System-Level Synthesis by Solver Coordination and Domain-Specific Heuristics. Electronics. 2022; 11(12):1888. https://doi.org/10.3390/electronics11121888

Chicago/Turabian StyleHaubelt, Christian, and Alexander Rausch. 2022. "Improving Symbolic System-Level Synthesis by Solver Coordination and Domain-Specific Heuristics" Electronics 11, no. 12: 1888. https://doi.org/10.3390/electronics11121888

APA StyleHaubelt, C., & Rausch, A. (2022). Improving Symbolic System-Level Synthesis by Solver Coordination and Domain-Specific Heuristics. Electronics, 11(12), 1888. https://doi.org/10.3390/electronics11121888