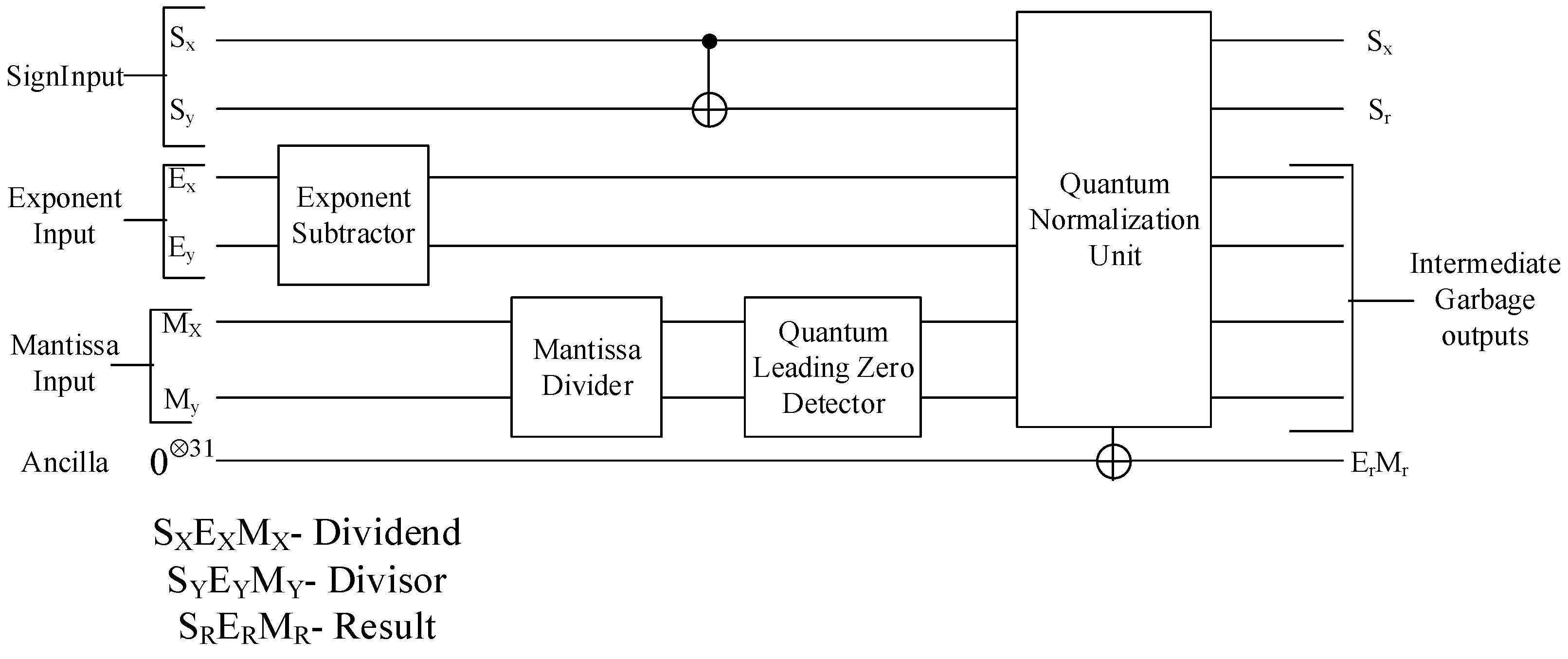

T-Count Optimized Quantum Circuit Designs for Single-Precision Floating-Point Division

Abstract

1. Introduction

2. Preliminaries

| Algorithm 1: Algorithm for floating-point division. |

| Input: Two input floating-point numbers Result: Floating-point number |

- T-Count: The number of T-gates employed in the quantum circuit.

- T-depth: The number of T-gate layers in the quantum circuit that can perform parallel quantum information processing.

- Qubits: The total number of qubits required to implement the quantum circuit.

- Circuit size (KQ): T-depth × No. of qubits.

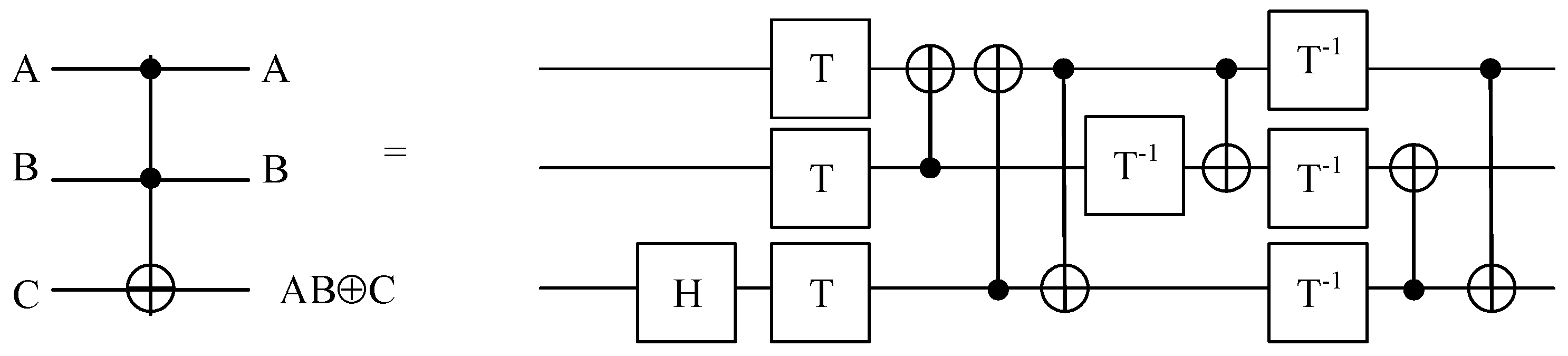

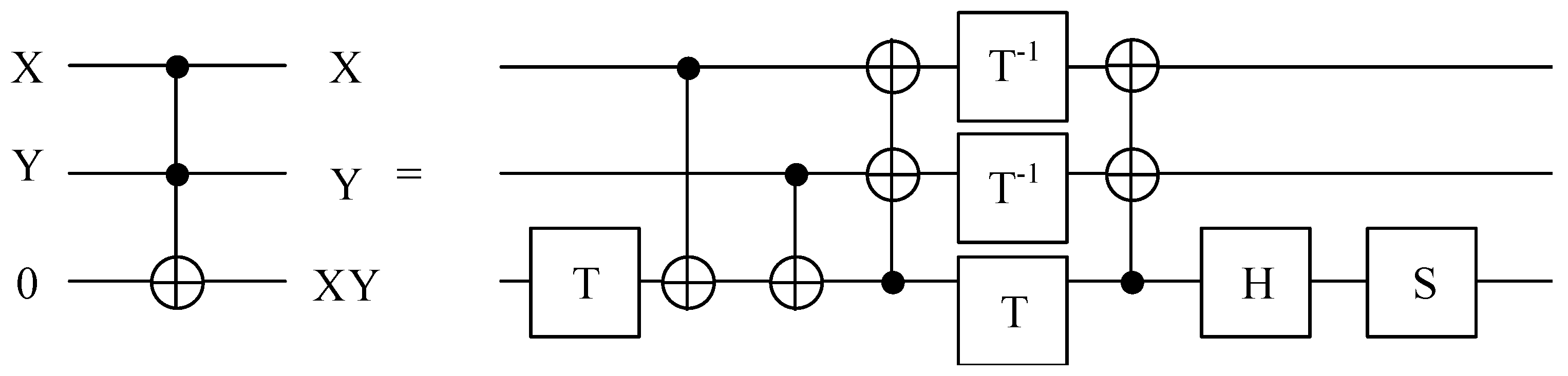

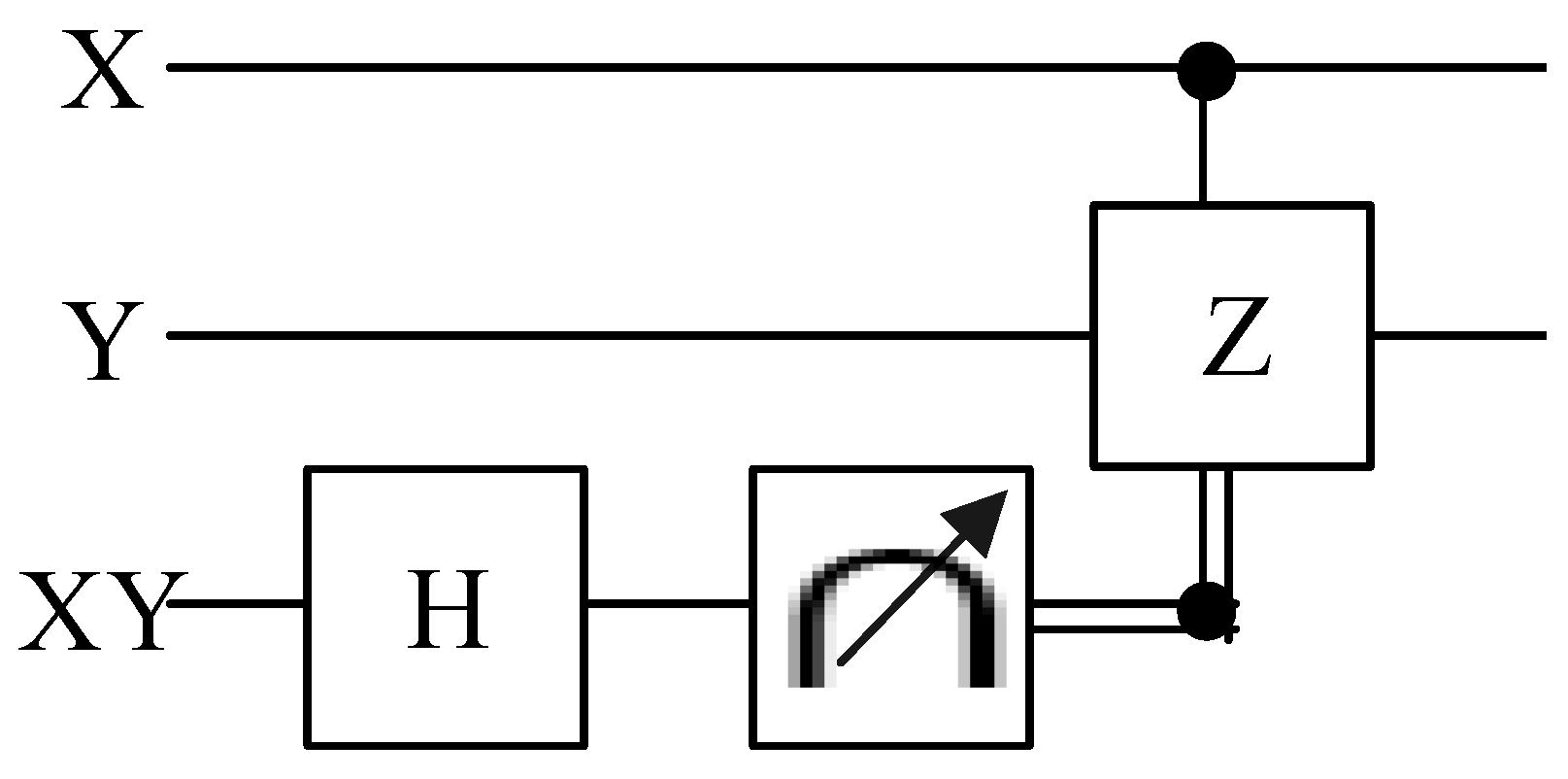

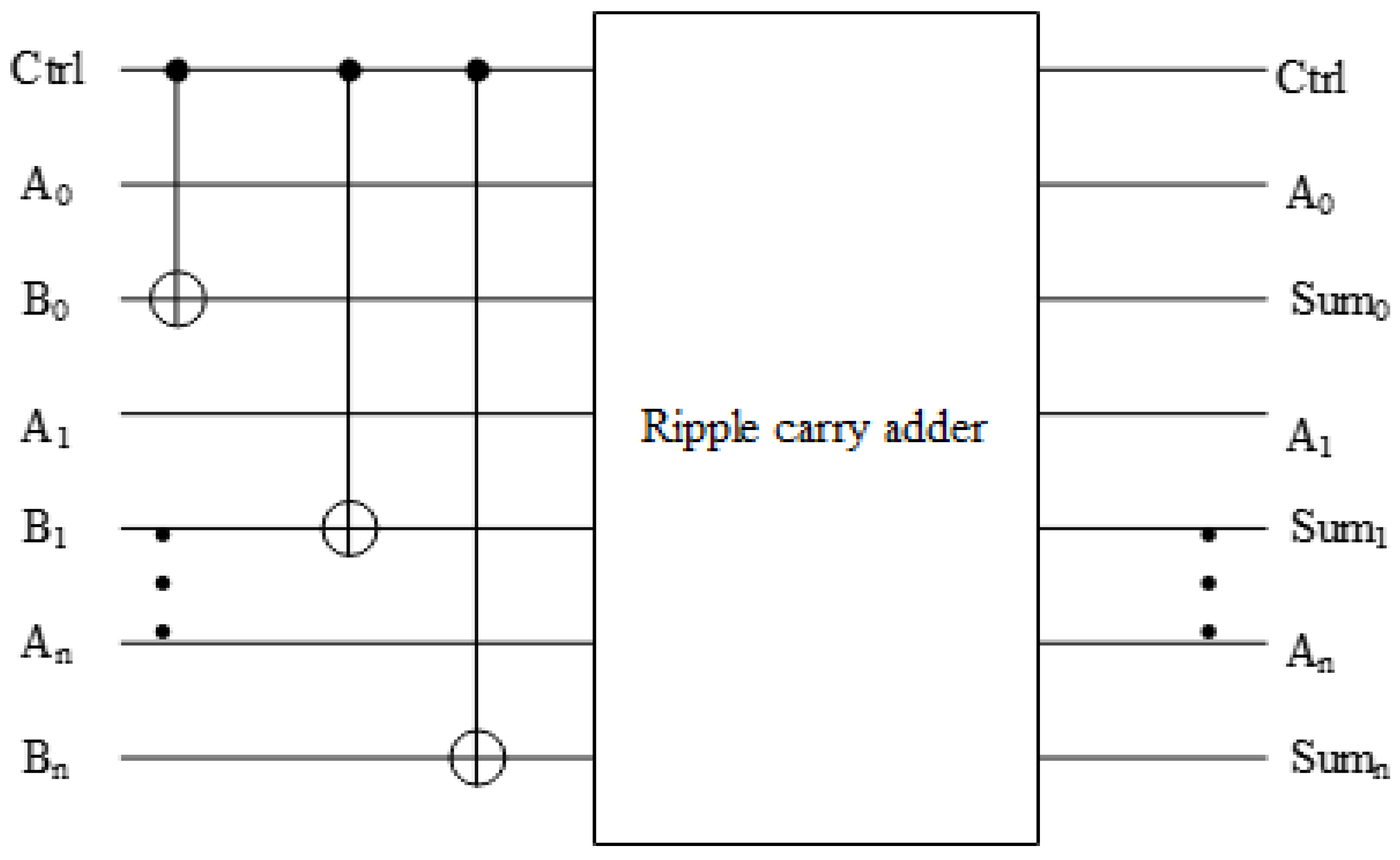

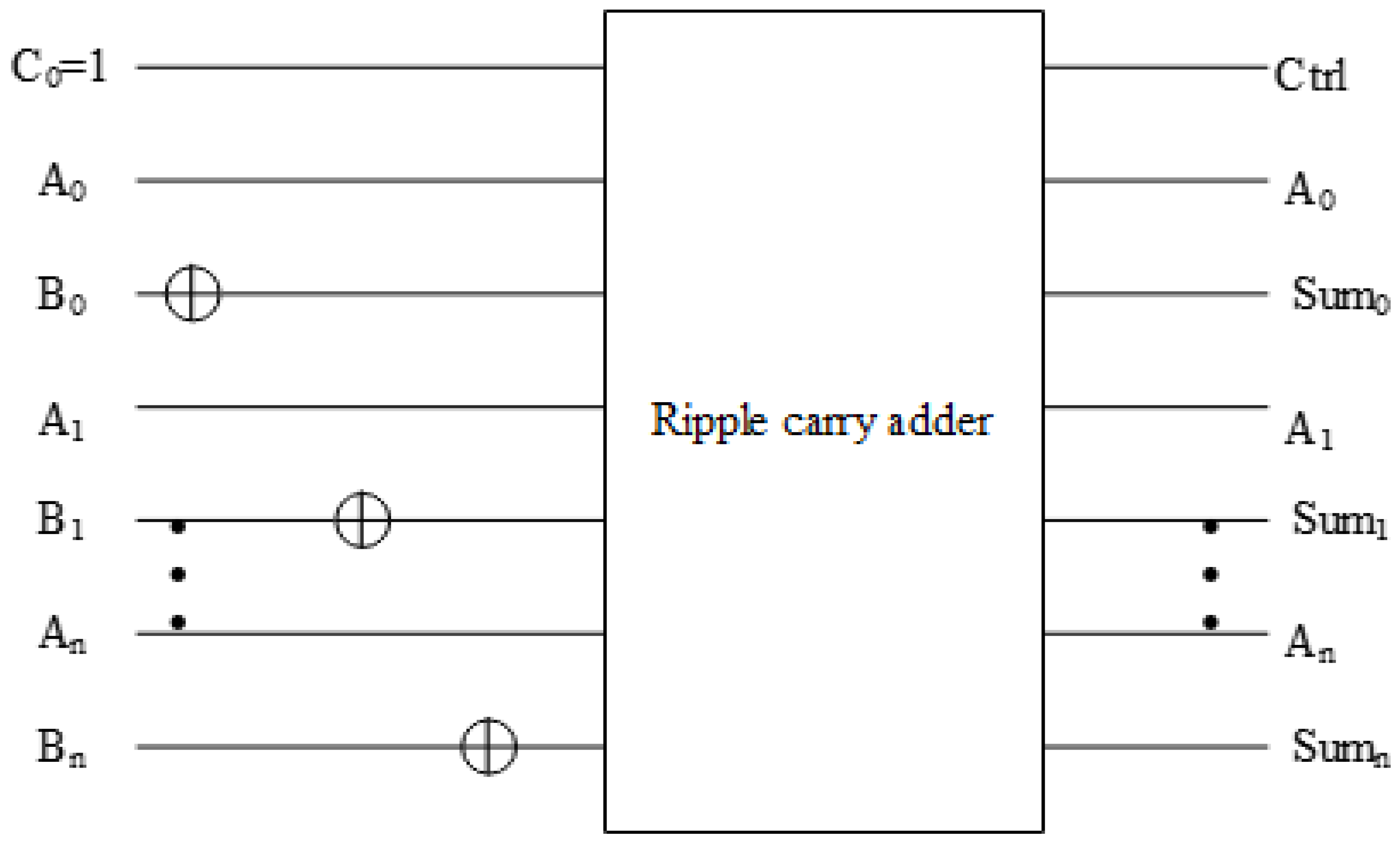

2.1. Elementary Quantum Circuits for Single-Precision Operands Used in Designing the Proposed Quantum Floating-Point Divider

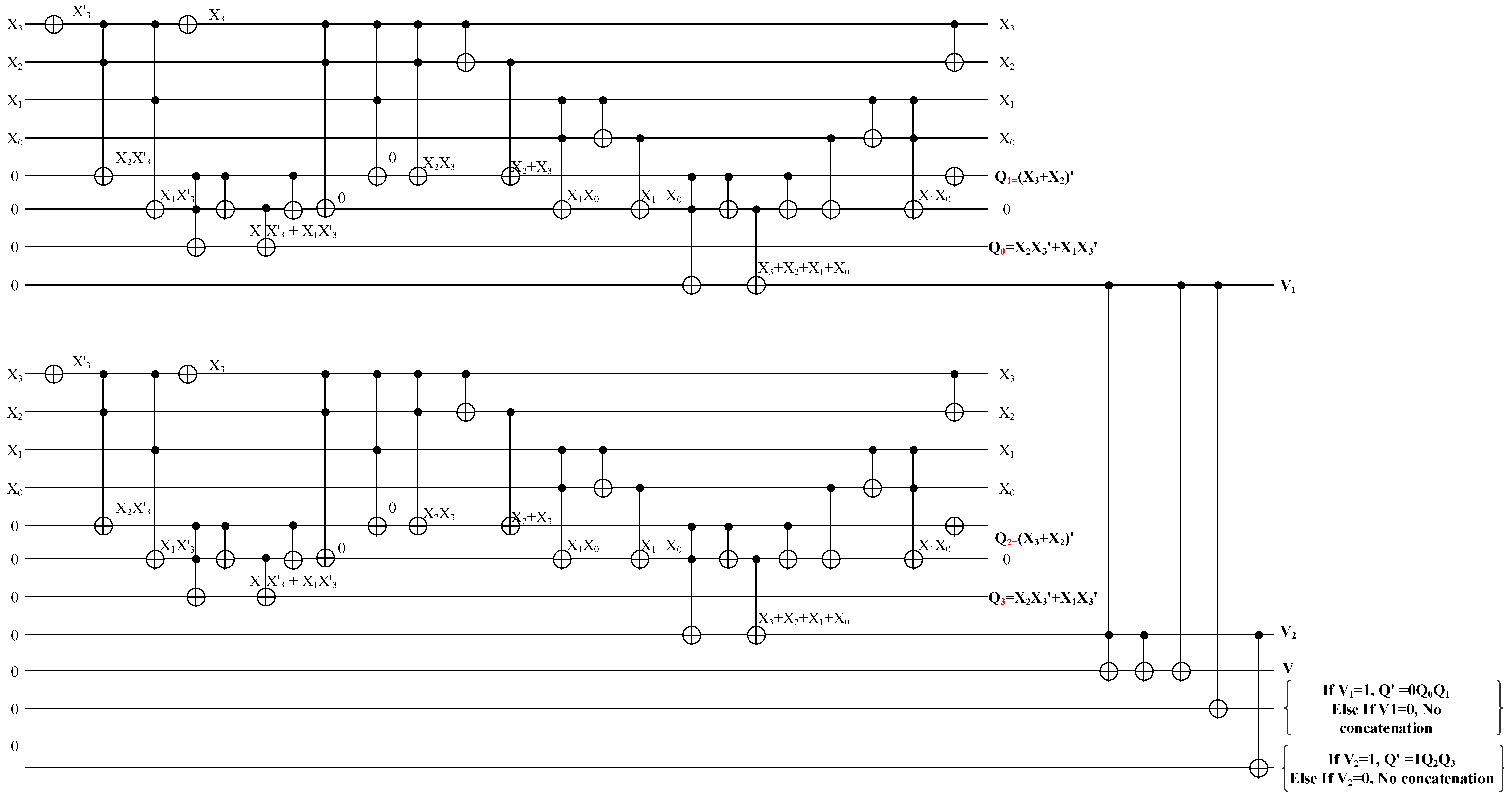

3. Proposed Quantum Leading Zero Detector

4. Quantum Circuit Designs for Mantissa Division of the Floating-Point Number Using Restoring and Non-Restoring Division Algorithm

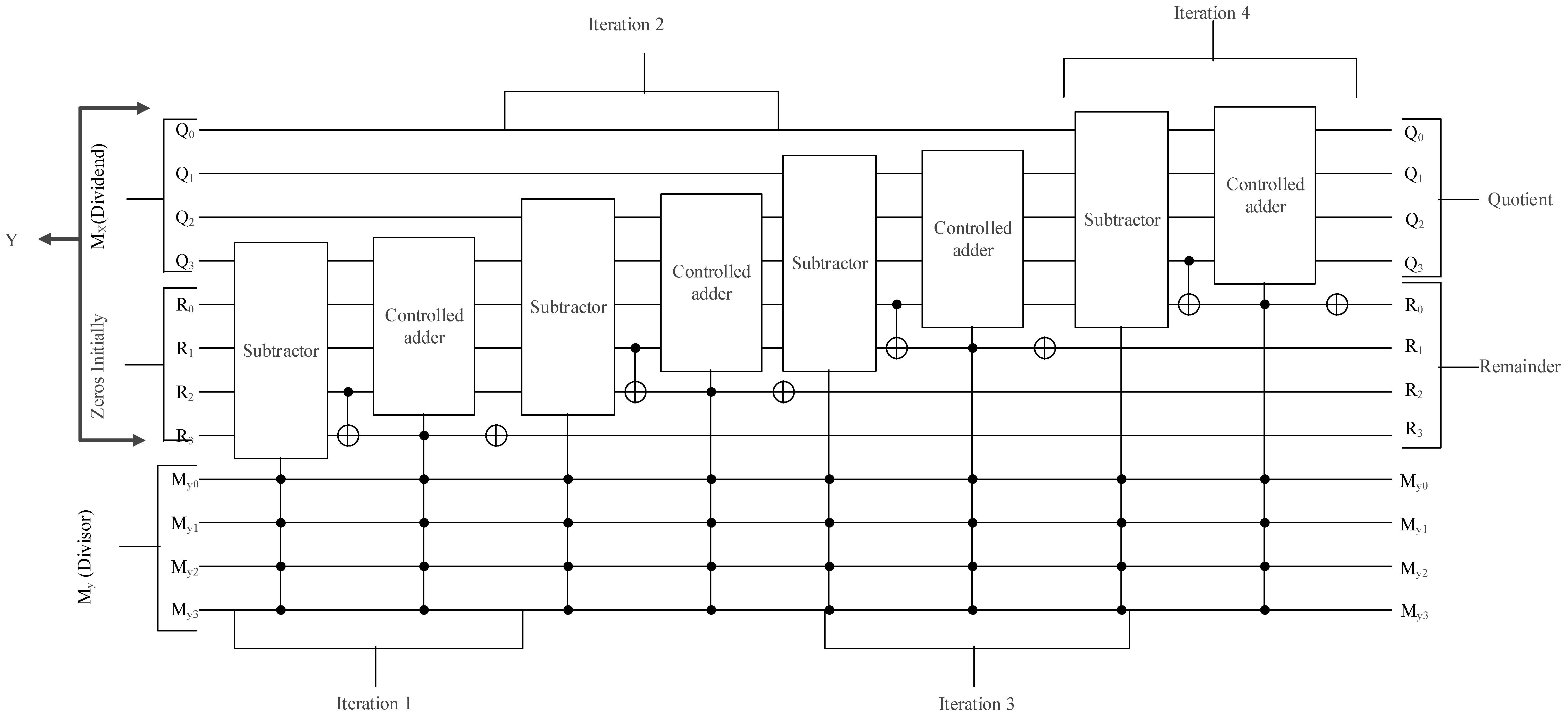

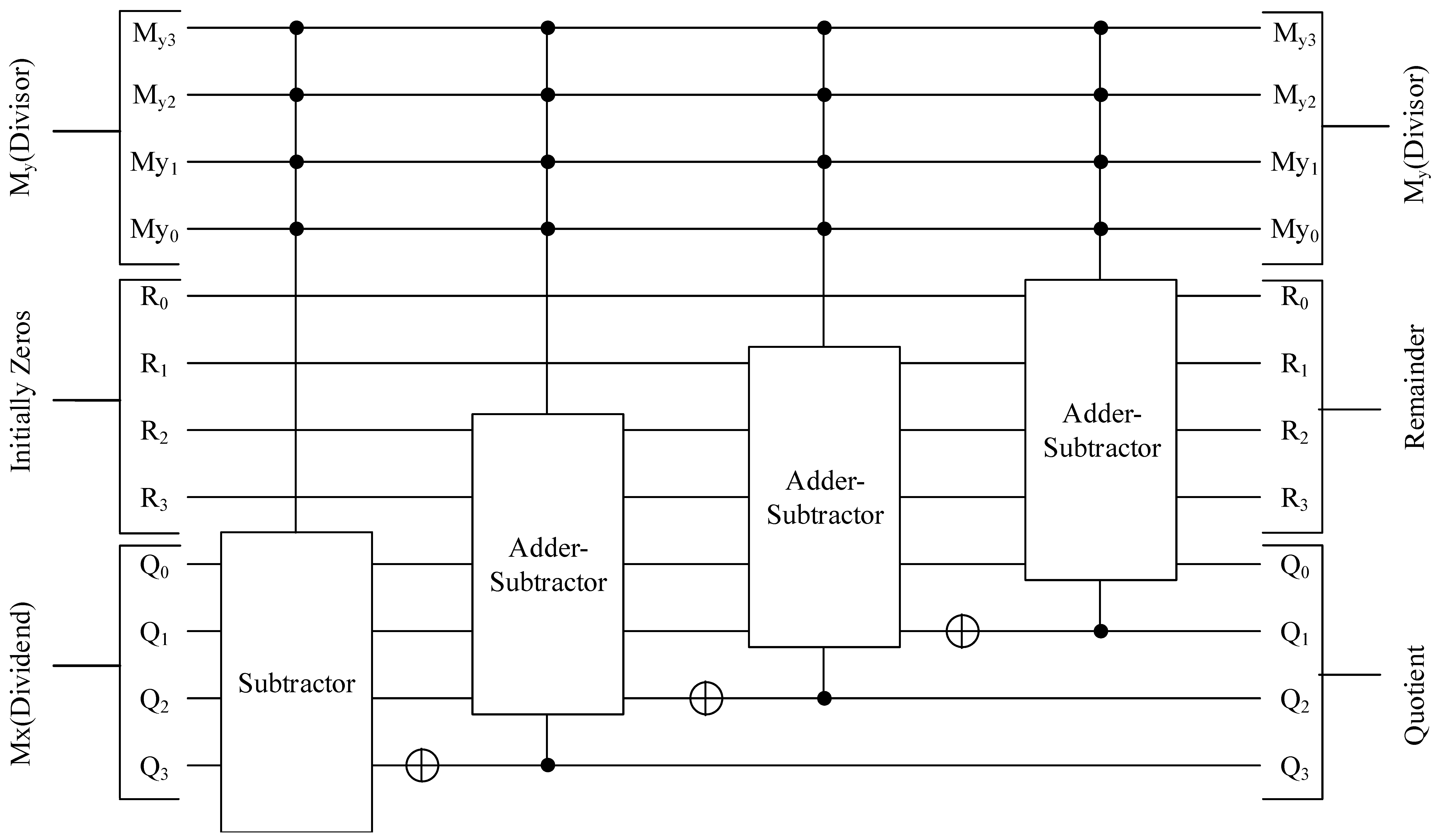

4.1. Quantum Restoring Circuit for Mantissa Division

| Algorithm 2: Restoring division algorithm for mantissa of the floating-point number. |

| Input: Two input numbers and Result: Quotient Q, Remainder Assign Initialize for if end end if end |

4.2. Quantum Circuit for Mantissa Division Using Non-Restoring Algorithm

| Algorithm 3: Non-restoring division algorithm for mantissa of the floating-point number. |

| Input: Two input numbers and Output: Quotient Q, Remainder Initialize Initialize for if else end end If end |

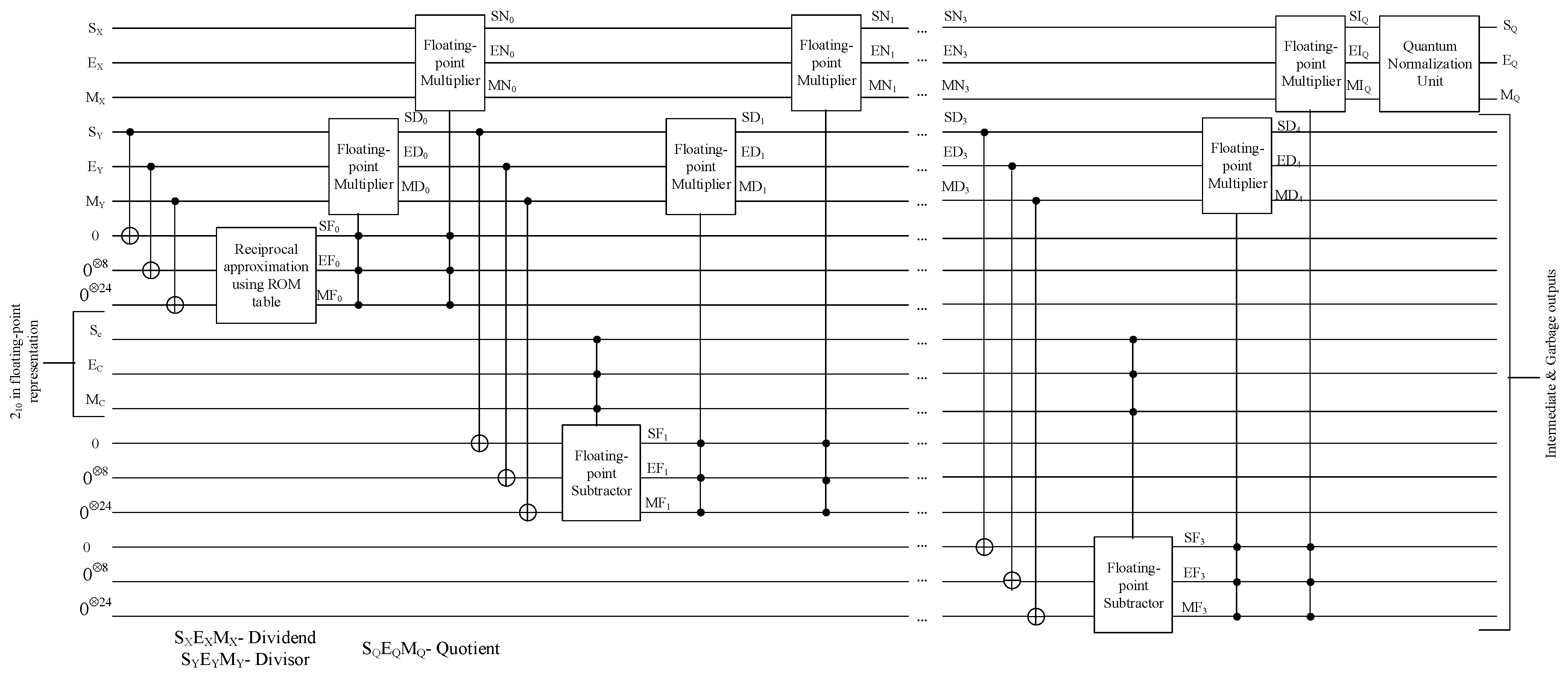

5. Quantum Division Circuit Design Proposed for SPFP Number Using Goldschmidt Division Algorithm

| Algorithm 4: Goldschmidt Division Algorithm for floating-point number with single-precision. |

| Input: X and Y Initialize If for end |

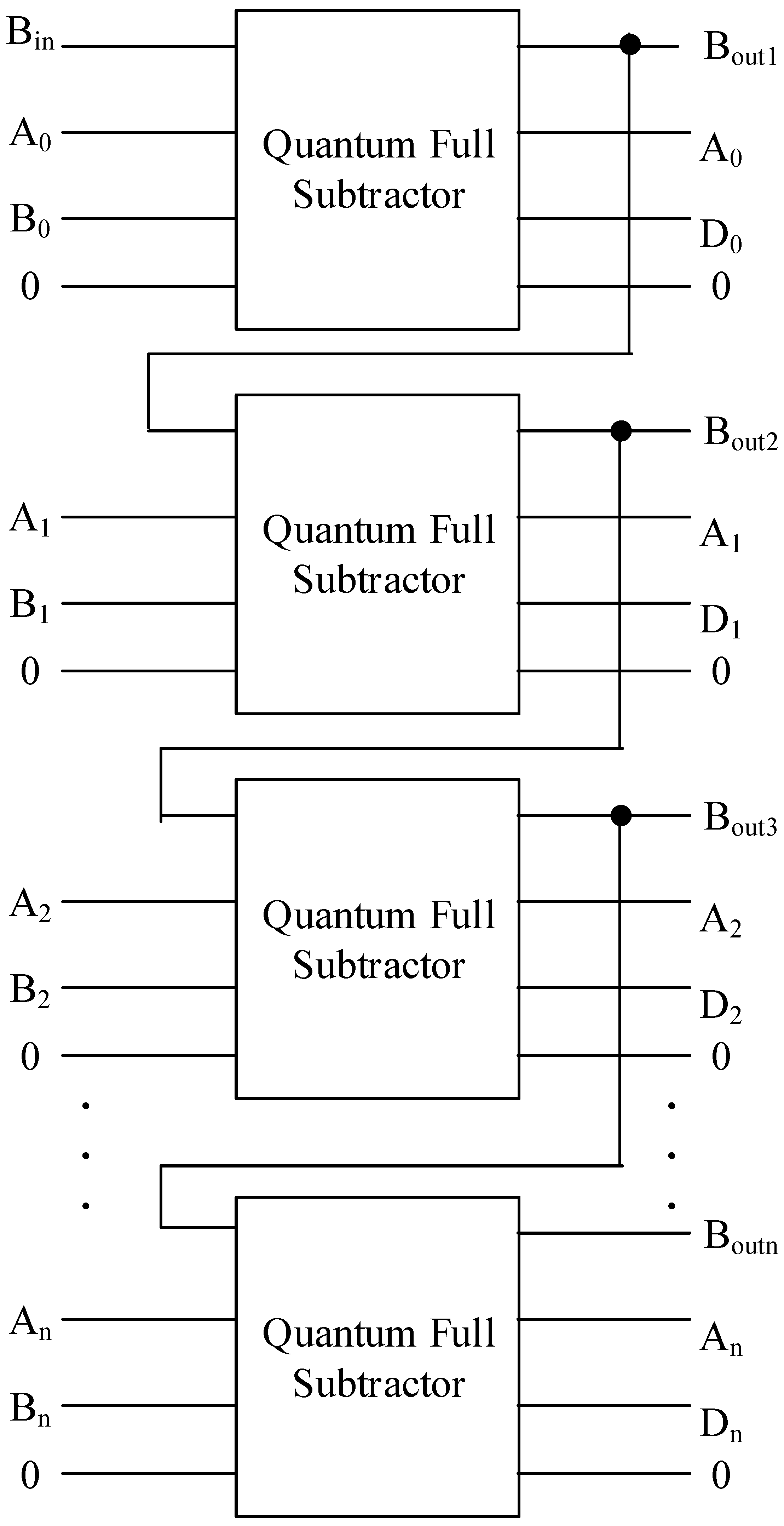

5.1. Quantum Subtractor Circuit Design for SPFP Input

| Algorithm 5: Floating-point addition and subtraction algorithm. |

|

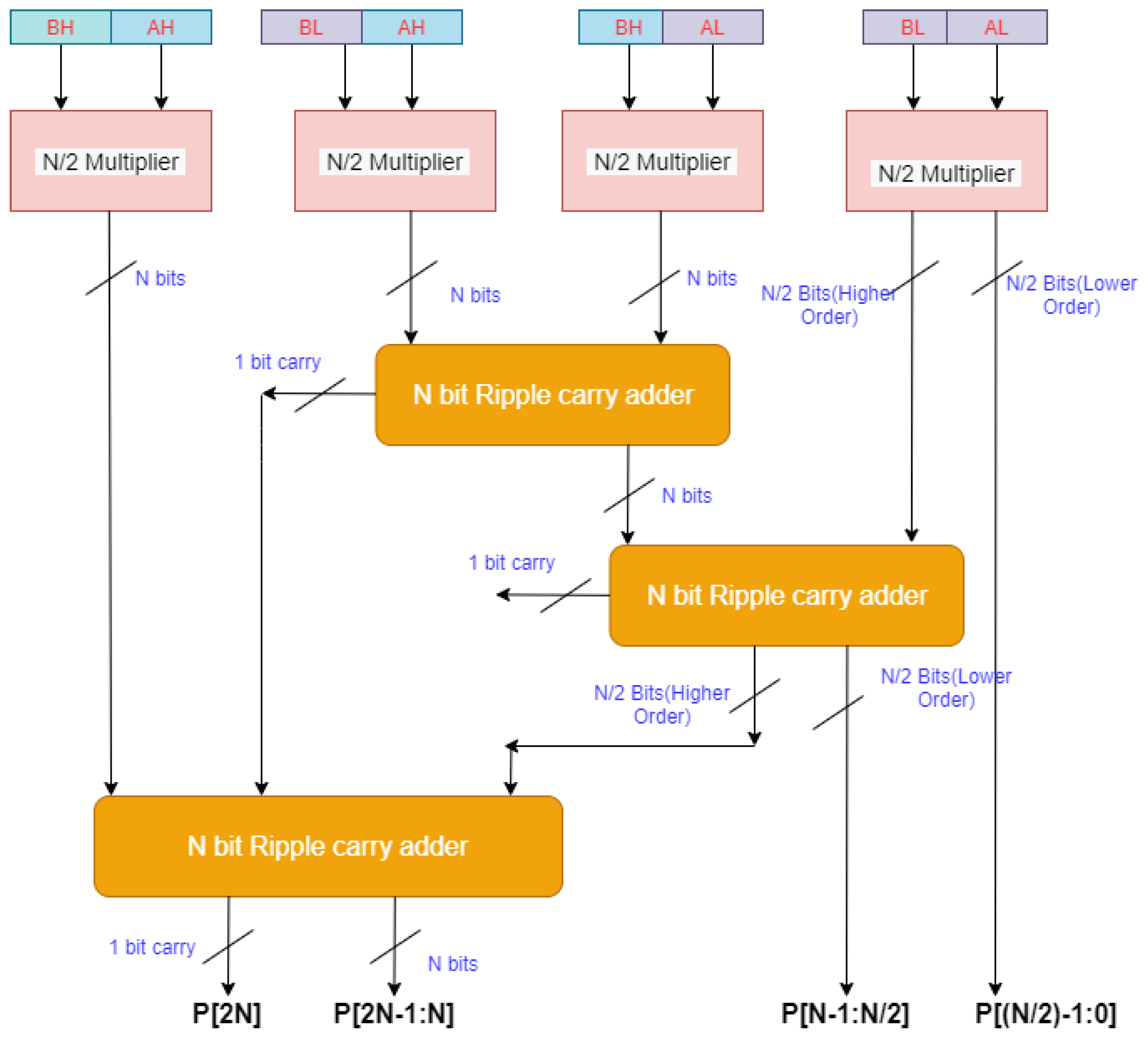

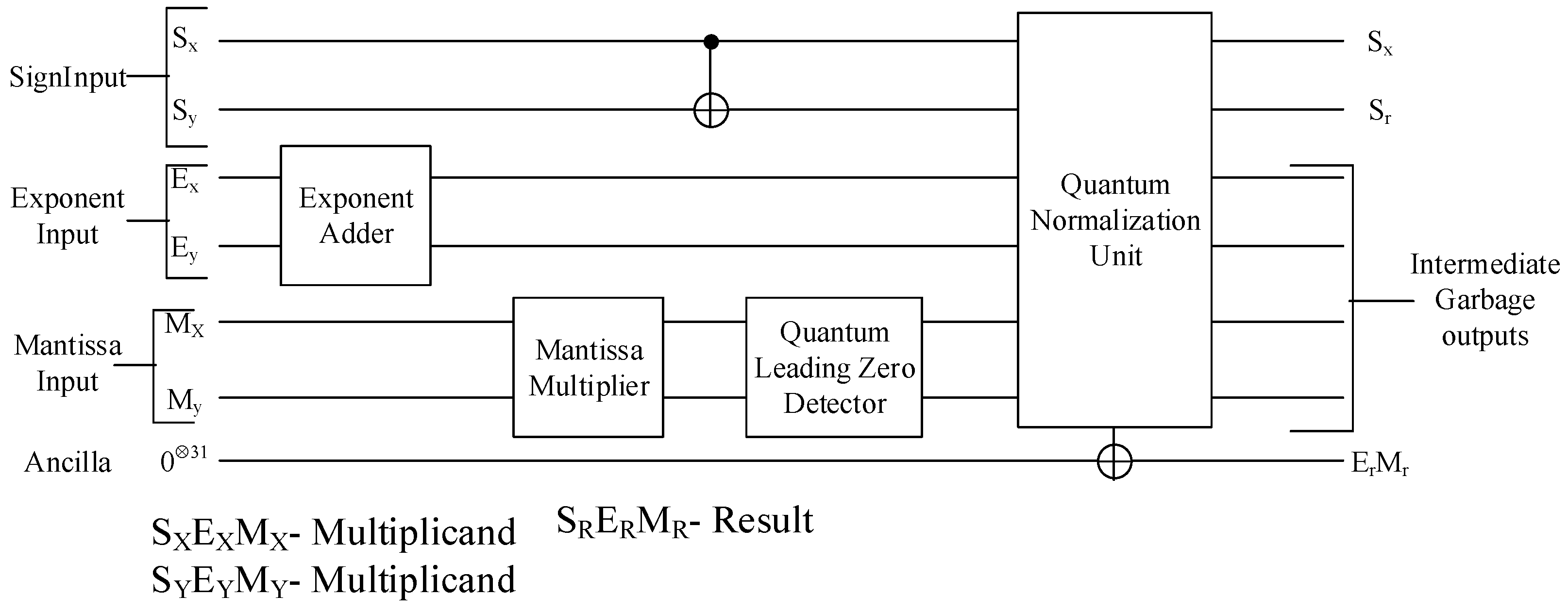

5.2. Quantum Circuit Design of a Multiplier for Floating-Point Number with Single-Precision

| Algorithm 6: Floating-point multiplication algorithm. |

| Input: Two input floating-point numbers and Output: Floating-point number |

5.3. N × N Vedic Multiplier

6. Resource Utilization of the Proposed Quantum Divider Circuits for SPFP Number

6.1. Resource Analysis of the Proposed Quantum SPFP Divider Circuit Using Restoring and Non-Restoring Algorithms

6.2. Resource Analysis of the Proposed Quantum SPFP Division Circuit Using Goldschmidt Algorithm

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Beauregard, S. Circuit for Shor’s Algorithm Using 2n + 3 Qubits. arXiv 2002, arXiv:quant-ph/0205095. [Google Scholar]

- Babbush, R.; Berry, D.W.; Kivlichan, I.D.; Wei, A.Y.; Love, P.J.; Aspuru-Guzik, A. Exponentially more precise quantum simulation of fermions in second quantization. New J. Phys. 2016, 18, 033032. [Google Scholar] [CrossRef]

- Reiher, M.; Wiebe, N.; Svore, K.M.; Wecker, D.; Troyer, M. Elucidating reaction mechanisms on quantum computers. Proc. Natl. Acad. Sci. USA 2017, 114, 7555–7560. [Google Scholar] [CrossRef]

- Harrow, A.W.; Hassidim, A.; Lloyd, S. Quantum algorithm for linear systems of equations. Phys. Rev. Lett. 2009, 103, 150502. [Google Scholar] [CrossRef]

- Haener, T.; Soeken, M.; Roetteler, M.; Svore, K.M. Quantum circuits for floating-point arithmetic. In Proceedings of the International Conference on Reversible Computation, Leicester, UK, 12–14 September 2018; pp. 162–174. [Google Scholar]

- Bennett, C.H. Logical reversibility of computation. IBM J. Res. Dev. 1973, 17, 525–532. [Google Scholar] [CrossRef]

- Bravyi, S.; Kitaev, A. Universal quantum computation with ideal Clifford gates and noisy ancillas. Phys. Rev. A 2005, 71, 022316. [Google Scholar] [CrossRef]

- Paler, A.; Polian, I.; Nemoto, K.; Devitt, S.J. Fault-tolerant, high-level quantum circuits: Form, compilation and description. Quantum Sci. Technol. 2017, 2, 025003. [Google Scholar] [CrossRef]

- Cuccaro, S.A.; Draper, T.G.; Kutin, S.A.; Moulton, D.P. A new quantum ripple-carry addition circuit. arXiv 2004, arXiv:quant-ph/0410184. [Google Scholar]

- Gidney, C. Halving the cost of quantum addition. Quantum 2018, 2, 74. [Google Scholar] [CrossRef]

- Thapliyal, H. Mapping of subtractor and adder-subtractor circuits on reversible quantum gates. In Transactions on Computational Science XXVII; Springer: Berlin/Heidelberg, Germany, 2016; pp. 10–34. [Google Scholar]

- Muñoz-Coreas, E.; Thapliyal, H. Quantum circuit design of a t-count optimized integer multiplier. IEEE Trans. Comput. 2018, 68, 729–739. [Google Scholar] [CrossRef]

- Dutta, S.; Bhattacharjee, D.; Chattopadhyay, A. Quantum circuits for Toom-Cook multiplication. Phys. Rev. A 2018, 98, 012311. [Google Scholar] [CrossRef]

- Thapliyal, H.; Munoz-Coreas, E.; Varun, T.; Humble, T. Quantum circuit designs of integer division optimizing T-count and T-depth. IEEE Trans. Emerg. Top. Comput. 2019. [Google Scholar] [CrossRef]

- Häner, T.; Jaques, S.; Naehrig, M.; Roetteler, M.; Soeken, M. Improved quantum circuits for elliptic curve discrete logarithms. In Proceedings of the International Conference on Post-Quantum Cryptography, Paris, France, 15–17 April 2020; pp. 425–444. [Google Scholar]

- Thapliyal, H.; Muñoz-Coreas, E.; Khalus, V. T-count and Qubit Optimized Quantum Circuit Designs of Carry Lookahead Adder. arXiv 2020, arXiv:2004.01826. [Google Scholar] [CrossRef]

- Shor, P.W. Polynomial-time algorithms for prime factorization and discrete logarithms on a quantum computer. SIAM Rev. 1999, 41, 303–332. [Google Scholar] [CrossRef]

- Goto, H. Resource requirements for a fault-tolerant quantum Fourier transform. Phys. Rev. A 2014, 90, 052318. [Google Scholar] [CrossRef]

- Nam, Y.; Su, Y.; Maslov, D. Approximate quantum Fourier transform with O (n log (n)) T gates. NPJ Quantum Inf. 2020, 6, 1–6. [Google Scholar] [CrossRef]

- Jones, N.C.; Whitfield, J.D.; McMahon, P.L.; Yung, M.H.; Van Meter, R.; Aspuru-Guzik, A.; Yamamoto, Y. Faster quantum chemistry simulation on fault-tolerant quantum computers. New J. Phys. 2012, 14, 115023. [Google Scholar] [CrossRef]

- Weinstein, Y.S.; Pravia, M.; Fortunato, E.; Lloyd, S.; Cory, D.G. Implementation of the quantum Fourier transform. Phys. Rev. Lett. 2001, 86, 1889. [Google Scholar] [CrossRef] [PubMed]

- Ruiz-Perez, L.; Garcia-Escartin, J.C. Quantum arithmetic with the quantum Fourier transform. Quantum Inf. Process. 2017, 16, 152. [Google Scholar] [CrossRef]

- Clader, B.D.; Jacobs, B.C.; Sprouse, C.R. Quantum algorithm to calculate electromagnetic scattering cross sections. In Proceedings of the Quantum Information and Measurement, Optical Society of America, Rochester, NY, USA, 17–20 June 2013; pp. W6–W26. [Google Scholar]

- Lloyd, S.; Mohseni, M.; Rebentrost, P. Quantum algorithms for supervised and unsupervised machine learning. arXiv 2013, arXiv:1307.0411. [Google Scholar]

- Jain, J.; Agrawal, R. Design and development of efficient reversible floating point arithmetic unit. In Proceedings of the 2015 Fifth International Conference on Communication Systems and Network Technologies, Gwalior, India, 4–6 April 2015; pp. 811–815. [Google Scholar]

- Nguyen, T.D.; Van Meter, R. A resource-efficient design for a reversible floating point adder in quantum computing. ACM J. Emerg. Technol. Comput. Syst. 2014, 11, 1–18. [Google Scholar] [CrossRef]

- AnanthaLakshmi, A.; Sudha, G.F. A novel power efficient 0.64-GFlops fused 32-bit reversible floating point arithmetic unit architecture for digital signal processing applications. Microprocess. Microsyst. 2017, 51, 366–385. [Google Scholar] [CrossRef]

- Kamaraj, A.; Marichamy, P. Design of Fault-Tolerant Reversible Floating Point Division. Inf. MIDEM 2018, 48, 161–172. [Google Scholar]

- Daumas, M.; Finot, C. Division of floating point expansions with an application to the computation of a determinant. J. Univers. Comput. Sci. 1999, 5, 323–338. [Google Scholar]

- Schulte, M.J.; Tan, D.; Lemonds, C.E. Floating-point division algorithms for an x86 microprocessor with a rectangular multiplier. In Proceedings of the 2007 25th International Conference on Computer Design, Lake Tahoe, CA, USA, 7–10 October 2007; pp. 304–310. [Google Scholar]

- Amy, M.; Maslov, D.; Mosca, M.; Roetteler, M. A meet-in-the-middle algorithm for fast synthesis of depth-optimal quantum circuits. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2013, 32, 818–830. [Google Scholar] [CrossRef]

- Jones, C. Novel constructions for the fault-tolerant Toffoli gate. Phys. Rev. A 2013, 87, 022328. [Google Scholar] [CrossRef]

- Welch, J.; Bocharov, A.; Svore, K.M. Efficient approximation of diagonal unitaries over the Clifford+ T basis. arXiv 2014, arXiv:1412.5608. [Google Scholar]

- Oklobdzija, V.G. An algorithmic and novel design of a leading zero detector circuit: Comparison with logic synthesis. IEEE Trans. Very Large Scale Integr. Syst. 1994, 2, 124–128. [Google Scholar] [CrossRef]

- AnanthaLakshmi, A.; Sudha, G.F. Design of an efficient reversible single precision floating point adder. Int. J. Comput. Intell. Stud. 2015, 4, 2–30. [Google Scholar] [CrossRef]

- Even, G.; Seidel, P.M.; Ferguson, W.E. A parametric error analysis of Goldschmidt’s division algorithm. J. Comput. Syst. Sci. 2005, 70, 118–139. [Google Scholar] [CrossRef][Green Version]

- Wang, D.; Liu, Z.H.; Zhu, W.N.; Li, S.Z. Design of quantum comparator based on extended general Toffoli gates with multiple targets. Comput. Sci. 2012, 39, 302–306. [Google Scholar]

- Al-Rabadi, A.N. Closed-system quantum logic network implementation of the viterbi algorithm. Facta Univ. Ser. Electron. Energ. 2009, 22, 1–33. [Google Scholar] [CrossRef]

- Thapliyal, H.; Ranganathan, N.; Ferreira, R. Design of a comparator tree based on reversible logic. In Proceedings of the 10th IEEE International Conference on Nanotechnology, Ilsan, Korea, 17–20 August 2010; pp. 1113–1116. [Google Scholar]

- Xia, H.; Li, H.; Zhang, H.; Liang, Y.; Xin, J. Novel multi-bit quantum comparators and their application in image binarization. Quantum Inf. Process. 2019, 18, 229. [Google Scholar] [CrossRef]

- Vijeyakumar, K.; Elango, S.; Kalaiselvi, S. VLSI implementation of high speed energy-efficient truncated multiplier. J. Circuits Syst. Comput. 2018, 27, 1850077. [Google Scholar] [CrossRef]

- Vijayan, A.E.; John, A.; Sen, D. Efficient implementation of 8-bit vedic multipliers for image processing application. In Proceedings of the 2014 International Conference on Contemporary Computing and Informatics (IC3I), Mysore, India, 27–29 November 2014; pp. 544–552. [Google Scholar]

- Miao, J.; Li, S. A design for high speed leading-zero counter. In Proceedings of the 2017 IEEE International Symposium on Consumer Electronics (ISCE), Kuala Lumpur, Malaysia, 14–15 November 2017; pp. 22–23. [Google Scholar]

- Biswal, L.; Bhattacharjee, A.; Das, R.; Thirunavukarasu, G.; Rahaman, H. Quantum Domain Design of Clifford+ T-Based Bidirectional Barrel Shifter. In Proceedings of the International Symposium on VLSI Design and Test, Madurai, India, 28–30 June 2018; pp. 606–618. [Google Scholar]

- Jamal, L.; Babu, H.M.H. Efficient approaches to design a reversible floating point divider. In Proceedings of the 2013 IEEE International Symposium on Circuits and Systems (ISCAS), Beijing, China, 19–23 May 2013; pp. 3004–3007. [Google Scholar]

| S.No | Gate | Symbol | Matrix |

|---|---|---|---|

| 1 | Pauli-x | X (or) ⊕ | |

| 2 | Hadamard | H | |

| 3 | CNOT |  | |

| 4 | T-Gate | T | |

| 5 | T-Gate Hermitian Transpose | T−1 or T † | |

| 6 | Phase Gate | S | |

| 7 | Phase Gate Hermitian Transpose | S−1 or S † |

| Parameter | Existing Design [26] | Modified Design [35] | Proposed Design | % of imp. over [26] | % of imp. over Modified [35] |

|---|---|---|---|---|---|

| T-count | 112 | 84 | 76 | 32.14% | 45.23% |

| T-depth | 54 | 63 | 38 | 29.62% | 65.78% |

| Ancilla | 38 | 21 | 11 | 71.05% | 47.61% |

| Component | T-Count | T-Depth | Ancilla |

|---|---|---|---|

| 8-Qubit exponent subtractor | 32 | 16 | 8 |

| 24-Qubit controlled adder (Restoring division) | 432 × 23 = 9936 | 192 × 23 = 4416 | 24 × 23 = 552 |

| 24-Qubit adder/subtractor (Non-restoring) | 96 × 23 = 2208 | 48 × 23 = 1104 | 24 × 23 = 552 |

| 24-Qubit subtractor | 96 × 23 = 2208 | 48 × 23 = 1104 | 24 × 23 = 552 |

| Proposed 32 Qubit LZD | 408 | 46 | 178 |

| Barrel shifter | 1687 | 2 | 620 |

| Final exponent adjust | 32 | 16 | 8 |

| Uncomputation circuit | Nil | Nil | 32 |

| Total (Restoring) | 14,303 | 5600 | 1950 |

| Total (Non-Restoring) | 6575 | 2288 | 1950 |

| Component | T-Count | T-Depth | Ancilla |

|---|---|---|---|

| Proposed quantum SPFP multiplier | 7936 × 12 = 95,232 | 1448 × 12 = 17,376 | 1984 × 12 = 23,808 |

| Proposed quantum SPFP subtractor | 3965 × 5 = 19,825 | 82 × 5 = 410 | 1034 × 5 = 5170 |

| Proposed 32 Qubit LZD | 408 | 46 | 178 |

| Barrel shifter | 1687 | 2 | 620 |

| Final exponent adjust | 32 | 16 | 8 |

| Copying intermediate outputs | Nil | Nil | 128 |

| Uncomputation circuit | Nil | Nil | 32 |

| Total | 117,187 | 17,850 | 29,944 |

| Designs | Qubits | T-Count | T-Depth |

|---|---|---|---|

| Existing Design [45] | 2207 | 28,672 | NA |

| Proposed Restoring divider | 2014 | 14,303 | 5584 |

| Proposed Non-restoring divider | 2046 | 6575 | 2288 |

| Designs | Qubits | T-Count | T-Depth |

|---|---|---|---|

| Existing Design (Modified) [27] | 29,074 | 227,920 | 59,916 |

| Proposed Goldschmidt divider | 30,008 | 117,187 | 17,850 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gayathri, S.S.; Kumar, R.; Dhanalakshmi, S.; Dooly, G.; Duraibabu, D.B. T-Count Optimized Quantum Circuit Designs for Single-Precision Floating-Point Division. Electronics 2021, 10, 703. https://doi.org/10.3390/electronics10060703

Gayathri SS, Kumar R, Dhanalakshmi S, Dooly G, Duraibabu DB. T-Count Optimized Quantum Circuit Designs for Single-Precision Floating-Point Division. Electronics. 2021; 10(6):703. https://doi.org/10.3390/electronics10060703

Chicago/Turabian StyleGayathri, S. S., R. Kumar, Samiappan Dhanalakshmi, Gerard Dooly, and Dinesh Babu Duraibabu. 2021. "T-Count Optimized Quantum Circuit Designs for Single-Precision Floating-Point Division" Electronics 10, no. 6: 703. https://doi.org/10.3390/electronics10060703

APA StyleGayathri, S. S., Kumar, R., Dhanalakshmi, S., Dooly, G., & Duraibabu, D. B. (2021). T-Count Optimized Quantum Circuit Designs for Single-Precision Floating-Point Division. Electronics, 10(6), 703. https://doi.org/10.3390/electronics10060703