Functionalized Three-Dimensional Multilayer Ceramic Modules

Abstract

:1. Introduction

2. Experimental Procedure

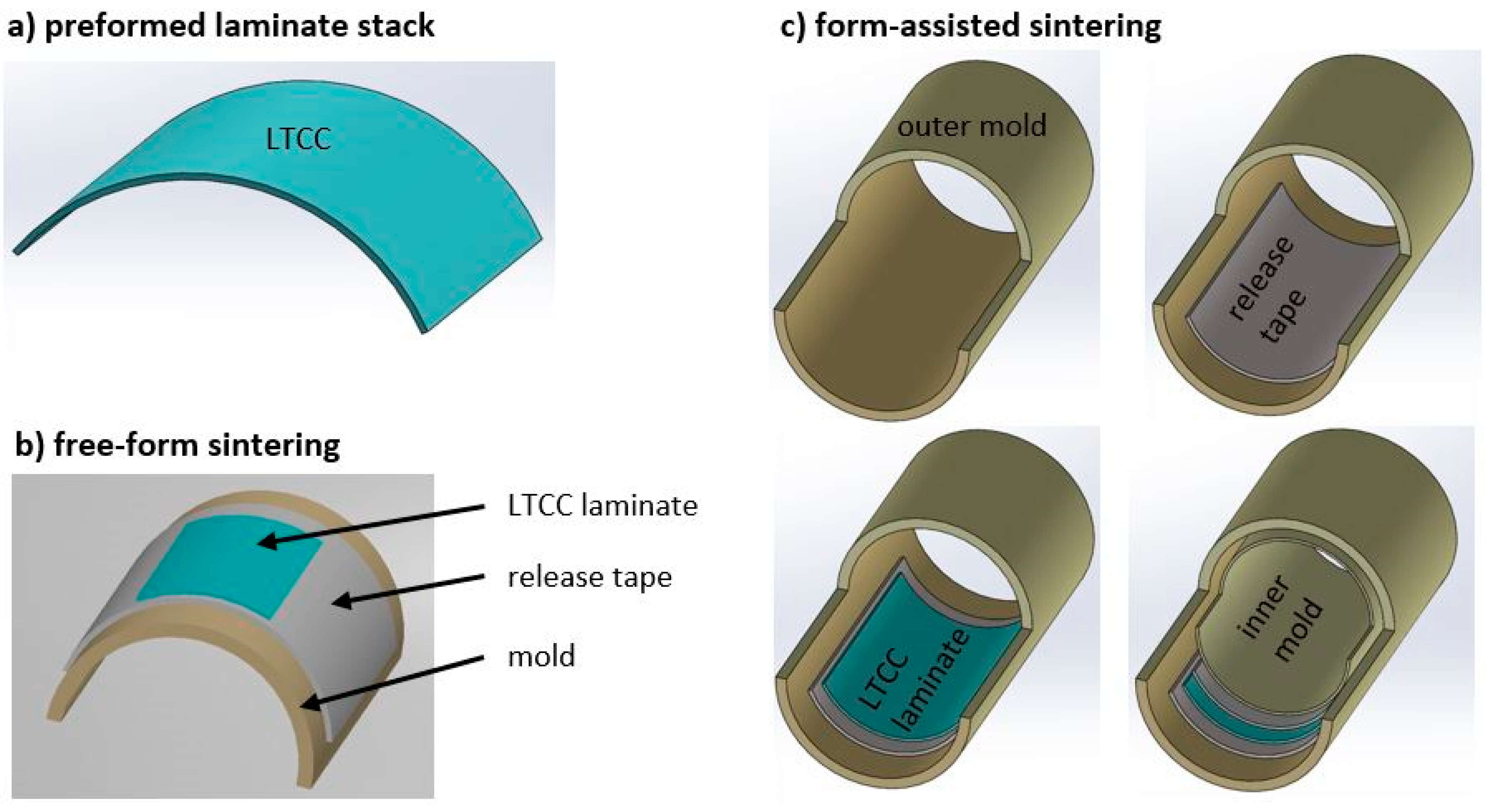

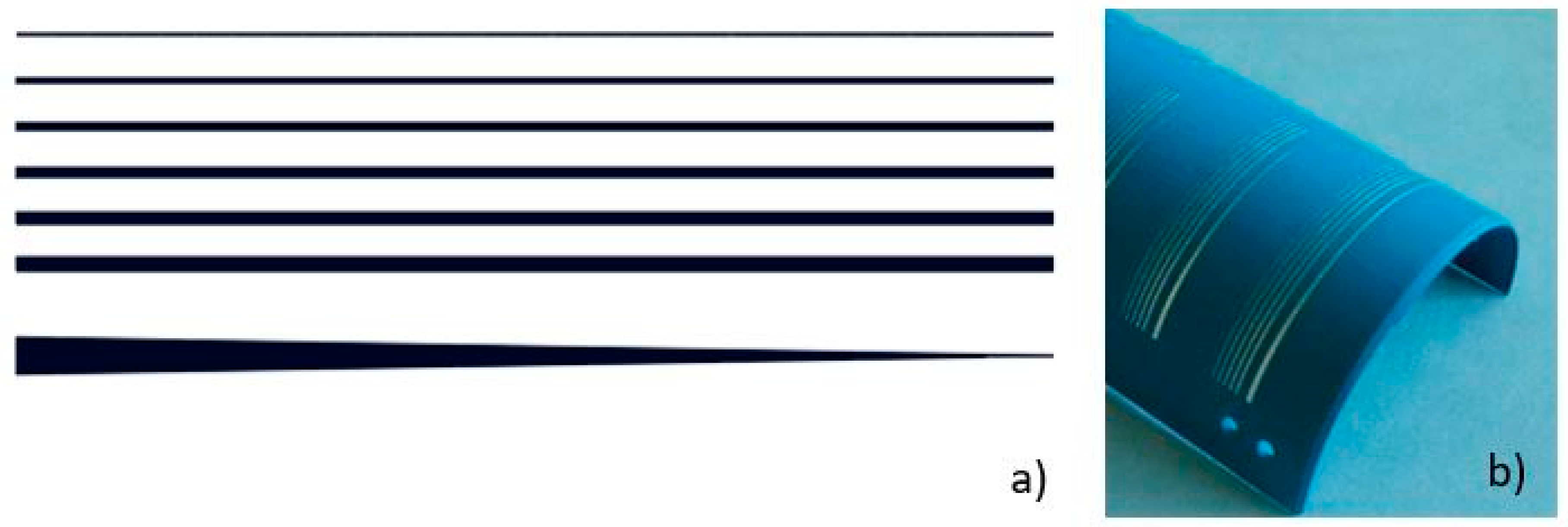

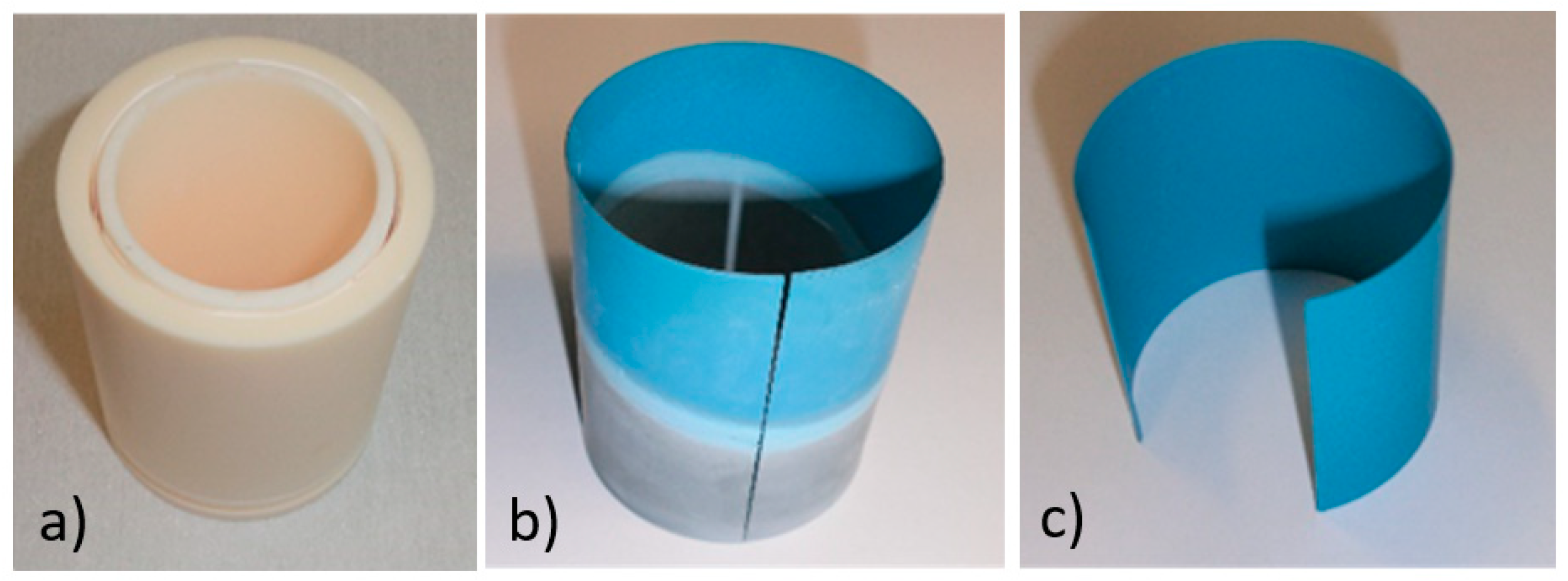

2.1. Technological Approach

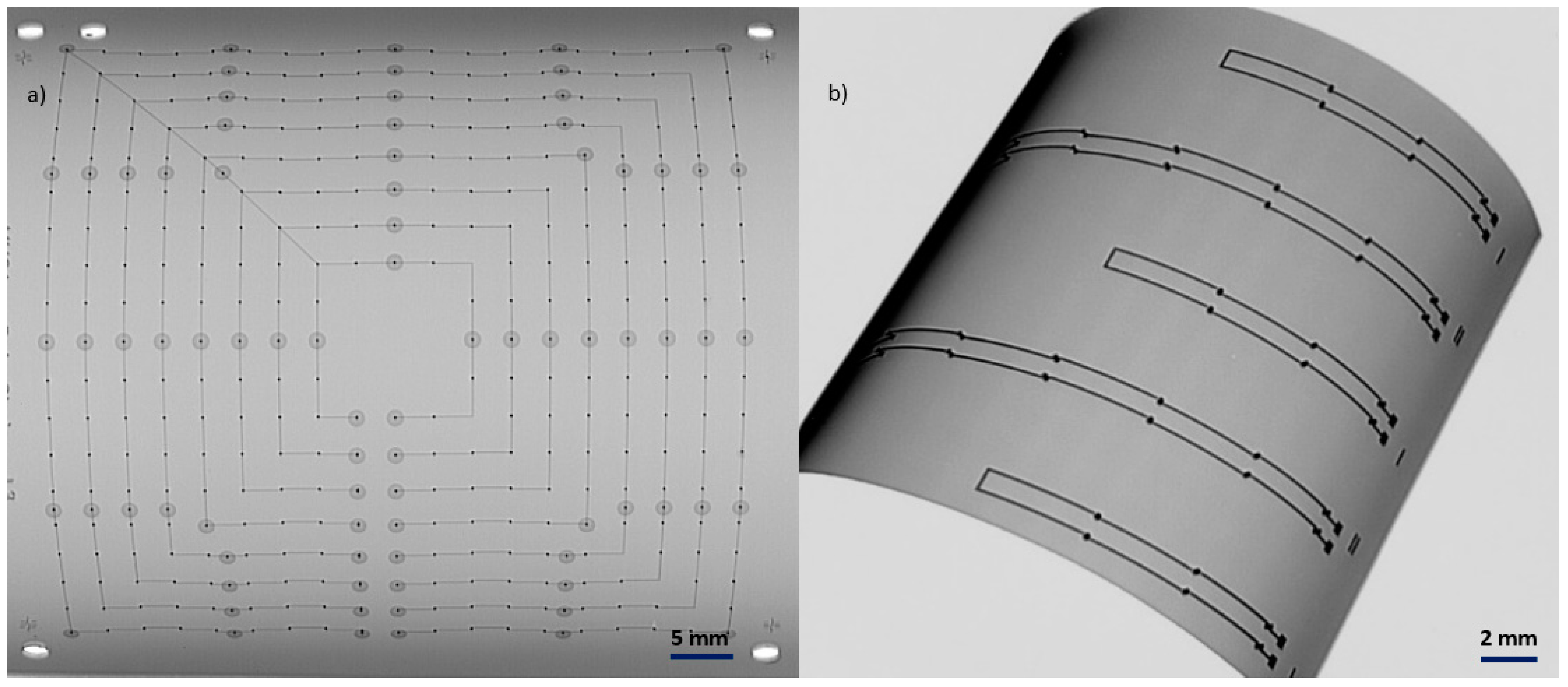

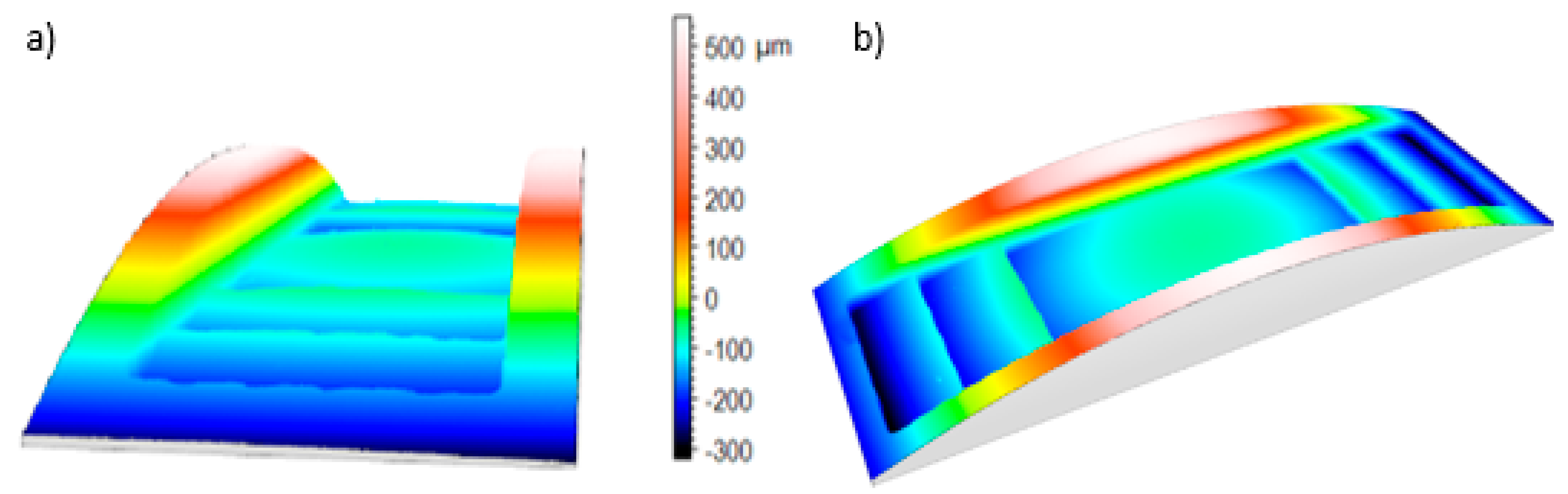

2.2. Shape Measurement

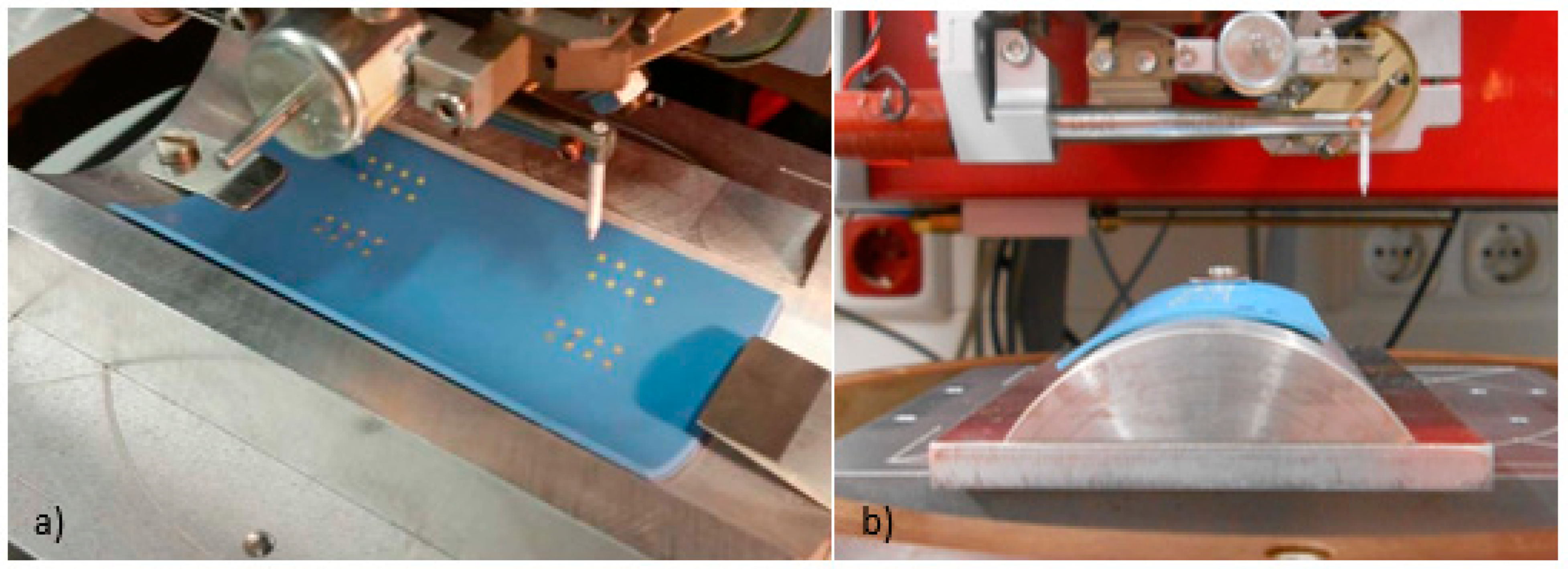

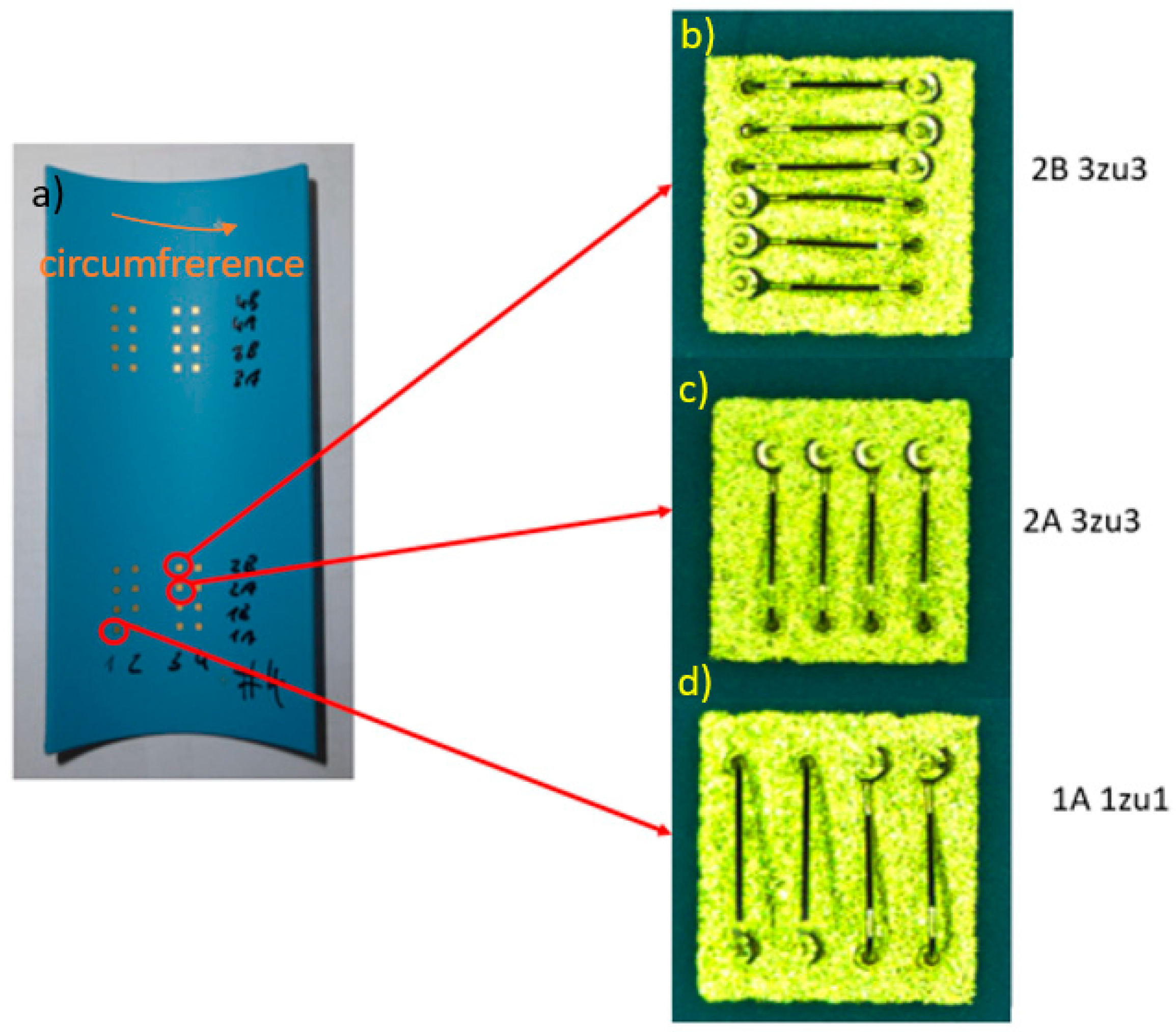

2.3. Adaption for the Assembly with Components

3. Results and Discussion

3.1. Shaping Results and Visual Inspection

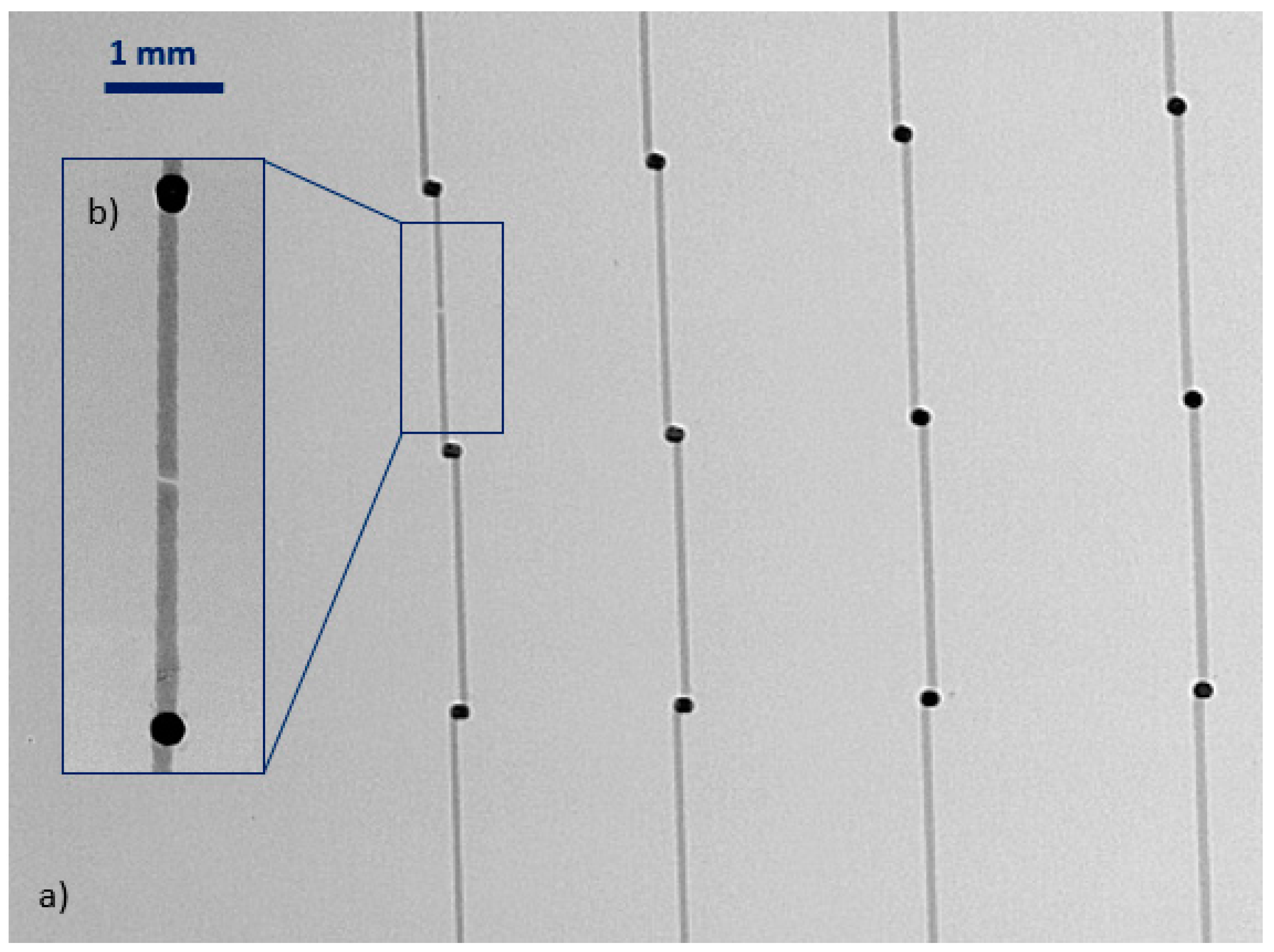

3.2. Electrical Properties of Internal Connections

3.3. Assembly Aspects

4. Conclusions and Outlook

Author Contributions

Funding

Conflicts of Interest

References

- Vitriol, W.A.; Johnson, G.W. Three Dimensional Microcircuit Structure and Process for Fabricating the Same from Ceramic Tape. U.S. Patent 5,028,473, 2 July 1991. [Google Scholar]

- Bauer, R.; Wolter, K.-J.; Sauer, W. Three Dimensionally Formed Thick Film Devices with LTCC Multilayer Technology. In Proceedings of the 1995 International Symposium on Microelectronics (ISHM), Los Angeles, CA, USA, 24–26 October 1995; pp. 481–487. [Google Scholar]

- Slosarcık, S.; Urbancık, J.; Pietriková, A.; Banský, J.; Bauer, R. LTCC based technology for 3D formed modules. J. Electr. Eng. 2004, 55, 265–268. [Google Scholar]

- Peterson, K.A.; Rohde, S.B.; Pfeifer, K.B.; Turner, T.S. Novel LTCC Fabrication Techniques Applied to a Rolled Micro Ion Mobility Spectrometer. In Proceedings-Electro-Chemi-Cal Society Pv; Electrochemical Society: Pennington, NJ, USA, 2004. [Google Scholar]

- Peterson, K.A.; Rohde, S.B.; Pfeifer, K.B.; Turner, T.S. Method for Producing a Tube. U.S. Patent 7,155,812, 2 January 2007. [Google Scholar]

- Peterson, K.A. Sandia Report. 2007. Available online: https://www.researchgate.net/publication/228780409_Macro-Meso-Microsystems_Integration_in_LTCC_LDRD_Report (accessed on 16 January 2021).

- Slosarčík, S.; Vehec, I.; Gmiterko, A.; Cabúk, P.; Jurčišin, M. Technology and Application of 3D Shaped LTCC Modules for Pressure Sensors and Microsystems. J. Microelectron. Electron. Packag. 2009, 6, 158–163. [Google Scholar] [CrossRef]

- Krueger, D.S.; Fadner, C.E.; Miller, G.V. Method and System for Fabricating Dome Shaped LTCC Substrates. U.S. Patent 8,968,637, 2 February 2015. [Google Scholar]

- Brandenburg, A.; Kita, J.; Groß, A.; Moos, R. Novel tube-type LTCC transducers with buried heaters and inner interdigitated electrodes as a platform for gas sensing at various high temperatures. Sens. Actuators B Chem. 2013, 189, 80–88. [Google Scholar] [CrossRef]

- Parrish, K.; Taff, J.; Yates, M.; Reis, D.; Plumlee, D. Plumlee, Characterization of the Fabrication Process of Rolled LTCC Structures. Int. J. Appl. Ceram. Technol. 2013, 10, 458–467. [Google Scholar] [CrossRef]

| Name of Sample Group | Degree of Complexity | Material |

|---|---|---|

| level 1 | only LTCC substrate | DP 951 PX |

| level 2 | surface metallization | DP 6145, DP 6146, DP 5740A, DP 5742 |

| level 3 | inner conductor lines and vias | DP 6145, DP 6141, DP 6138 |

| level 4 | daisy chains | DP 6145, DP 6141, DP 6138 |

| level 5 | complex layout with assembled components | DP 5740A, DP 5742, DP 6138, DP 6141, DP6145, DP 6146 |

| Ball | Wedge | |

|---|---|---|

| Utrasonic time (ms) | 200 | 200 |

| Ultrasonic power (digits) | 120 | 120 |

| Bondforce (cN) | 25 | 20 |

| Substrate | Chain No. | ||||

|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | |

| Resistance (Ω) | Resistance (Ω) | Resistance (Ω) | Resistance (Ω) | Resistance (Ω) | |

| A | 0.27 | 0.41 | 0.42 | 0.4 | Open circuit |

| B | Open circuit | Open circuit | 1.26 | 0.7 | 0.4 |

| C | 1.29 | 0.67 | 1.32 | 0.67 | 0.35 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kloska, M.; Bartsch, H.; Müller, J.; Haas, T.; Zeilmann, C. Functionalized Three-Dimensional Multilayer Ceramic Modules. Electronics 2021, 10, 248. https://doi.org/10.3390/electronics10030248

Kloska M, Bartsch H, Müller J, Haas T, Zeilmann C. Functionalized Three-Dimensional Multilayer Ceramic Modules. Electronics. 2021; 10(3):248. https://doi.org/10.3390/electronics10030248

Chicago/Turabian StyleKloska, Manja, Heike Bartsch, Jens Müller, Thomas Haas, and Christian Zeilmann. 2021. "Functionalized Three-Dimensional Multilayer Ceramic Modules" Electronics 10, no. 3: 248. https://doi.org/10.3390/electronics10030248

APA StyleKloska, M., Bartsch, H., Müller, J., Haas, T., & Zeilmann, C. (2021). Functionalized Three-Dimensional Multilayer Ceramic Modules. Electronics, 10(3), 248. https://doi.org/10.3390/electronics10030248