Memristive System Based Image Processing Technology: A Review and Perspective

Abstract

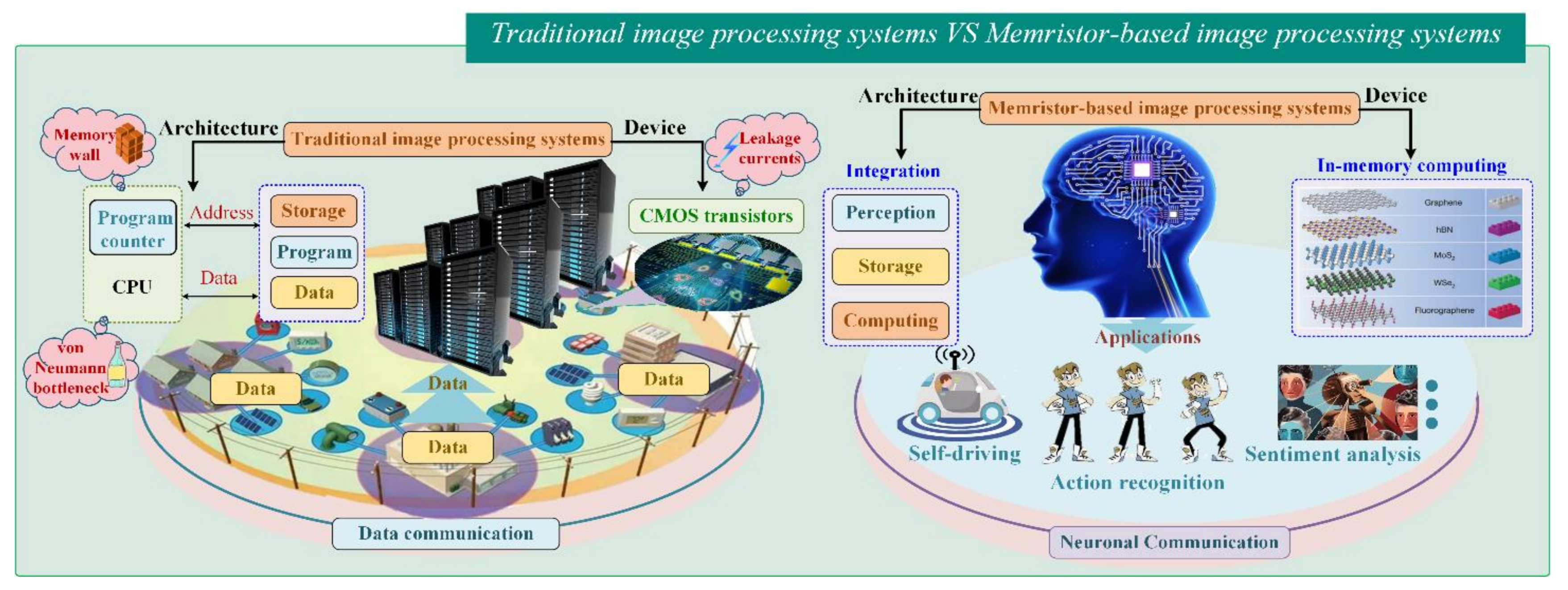

:1. Introduction

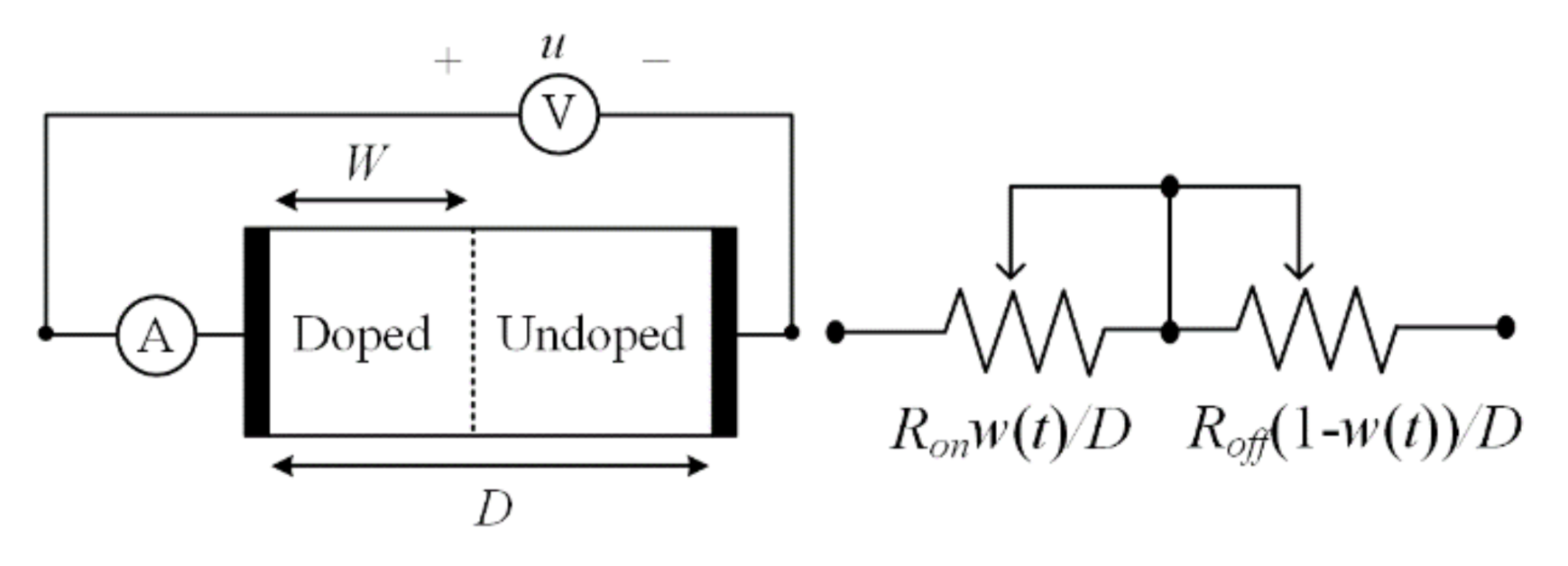

2. Mathematical Models

- (1)

- Ionic migration: This memristor type usually has the active metal (e.g., Ag) as the top electrode and the inert metal (e.g., Pt) as the bottom electrode. By applying a positive voltage to the top electrode, the active metal will be electrolyzed into metal cations. They will move toward the bottom electrode under the external electric field and then return to metal atoms, the accumulation of which form a metal filament conductive channel for the memristor to transit from the HRS to the LRS. Conversely, by applying a positive voltage to the bottom electrode, the formed conductive channel will gradually break, and the memristor will switch from the LRS to the HRS.

- (2)

- Quantum tunnelling: The internal functional layer of this type of memristor is mainly a metal oxide (e.g., TiOx). The Schottky barrier between the metal electrode and the functional layer is adjusted by applying an external voltage to switch the resistive state of the memristor. It disappears when the memristor is in the LRS, whereas it reappears when the memristor is in the HRS.

- (3)

- Charge trapping/de-trapping: For a memristor whose functional layer is the metal oxide film, there exists an empty state in the film. When a positive voltage is applied to the top electrode, the empty state traps the injected electrons and stores them, and when the empty state is filled, a conductive channel is formed, after which the memristor switches from the HRS to the LRS. By contrast, when a positive voltage is applied to the bottom electrode, the electrons in the empty state are released, the formed conductive channel is broken, and the memristor changes from the LRS to the HRS.

3. Traditional Image Processing Based on Memristive Systems

3.1. Image Storage Based on Memristive Systems

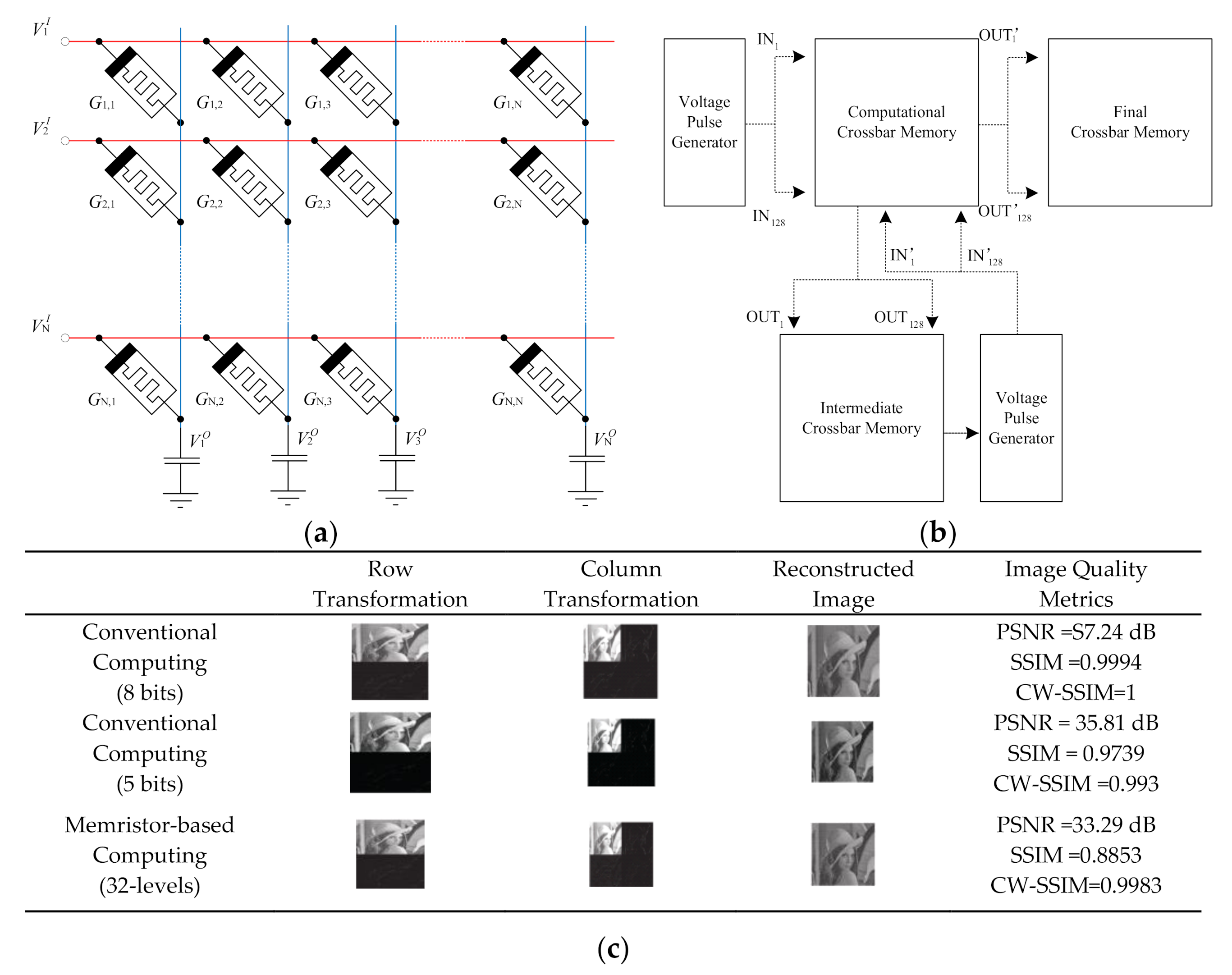

3.2. Image Compression Based on Memristive Systems

3.3. Image Reconstruction Based on Memristive Systems

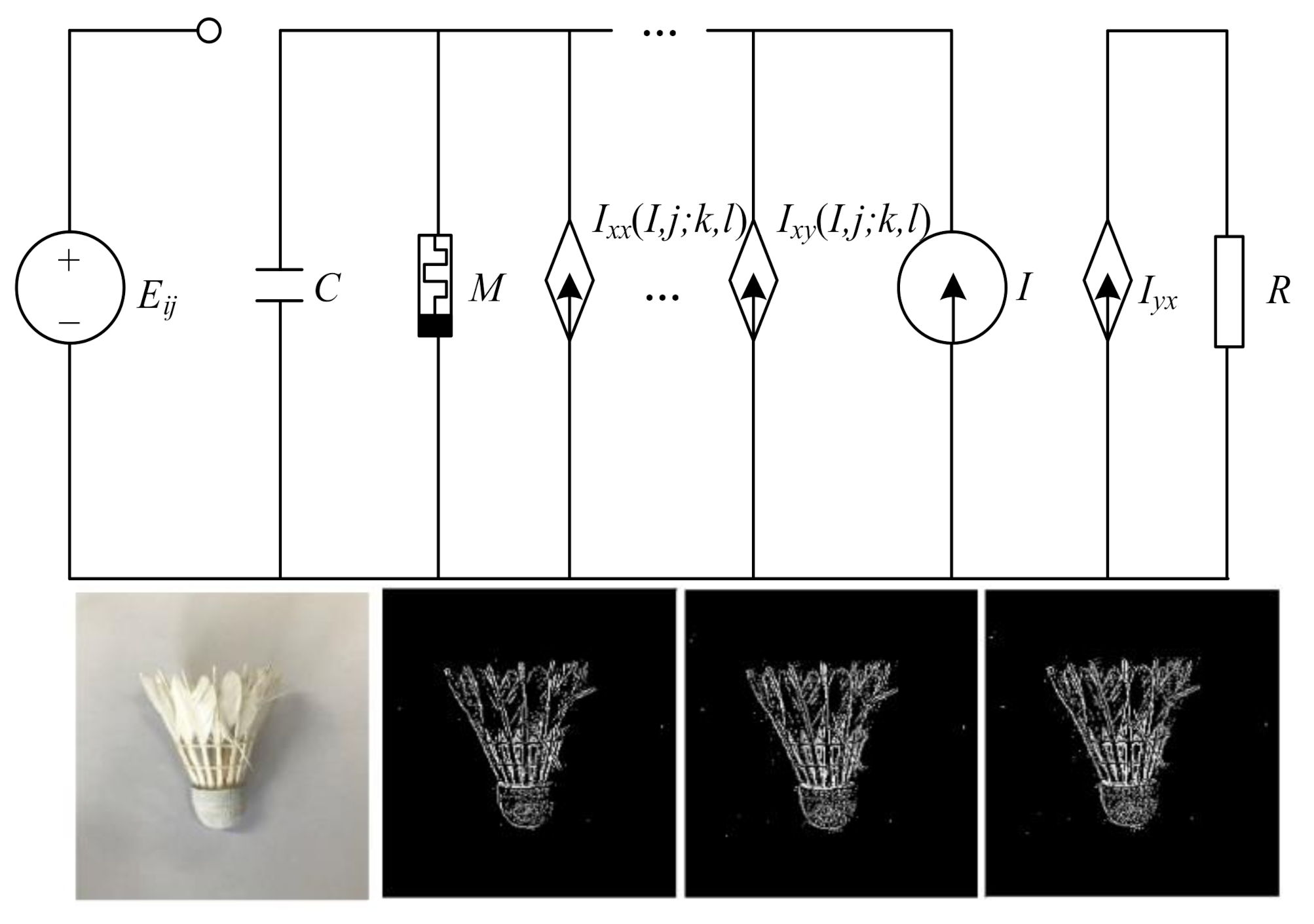

3.4. Others

3.5. Summary

- (1)

- The instability and variability of memristive devices have an impact on the accuracy of image processing. Therefore, it will be a significant study to explore the internal physical mechanism of memristive devices and to study their electrochemical properties under the influence of different external factors, to build a mathematical model that can accurately describe their behaviour.

- (2)

- Conventional image processing circuits do not consider the possible faults of memristive circuits in practice. Nevertheless, research on fault diagnosis can effectively help reduce the circuit overhead as well as improve algorithm operation efficiency and image processing accuracy while increasing the robustness and anti-interference capability of the circuit.

- (3)

- On the one hand, the design of the peripheral circuits in some image processing applications is too complex, which increases the power consumption of the system operation. On the other hand, the one with a simple structure and high compatibility can result in enhanced efficiency for complex conventional image processing tasks.

4. Image Processing Based on Memristive Neural Networks

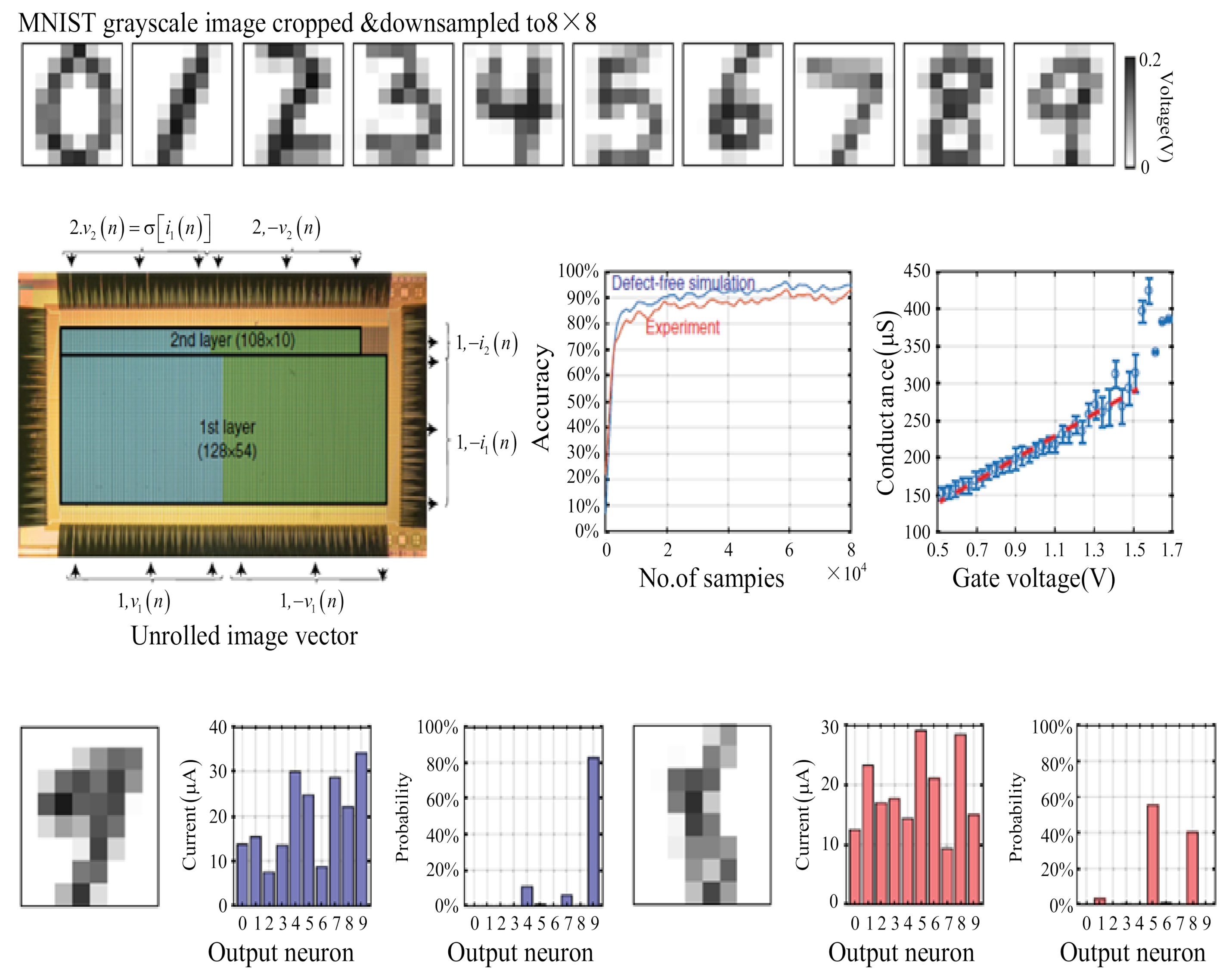

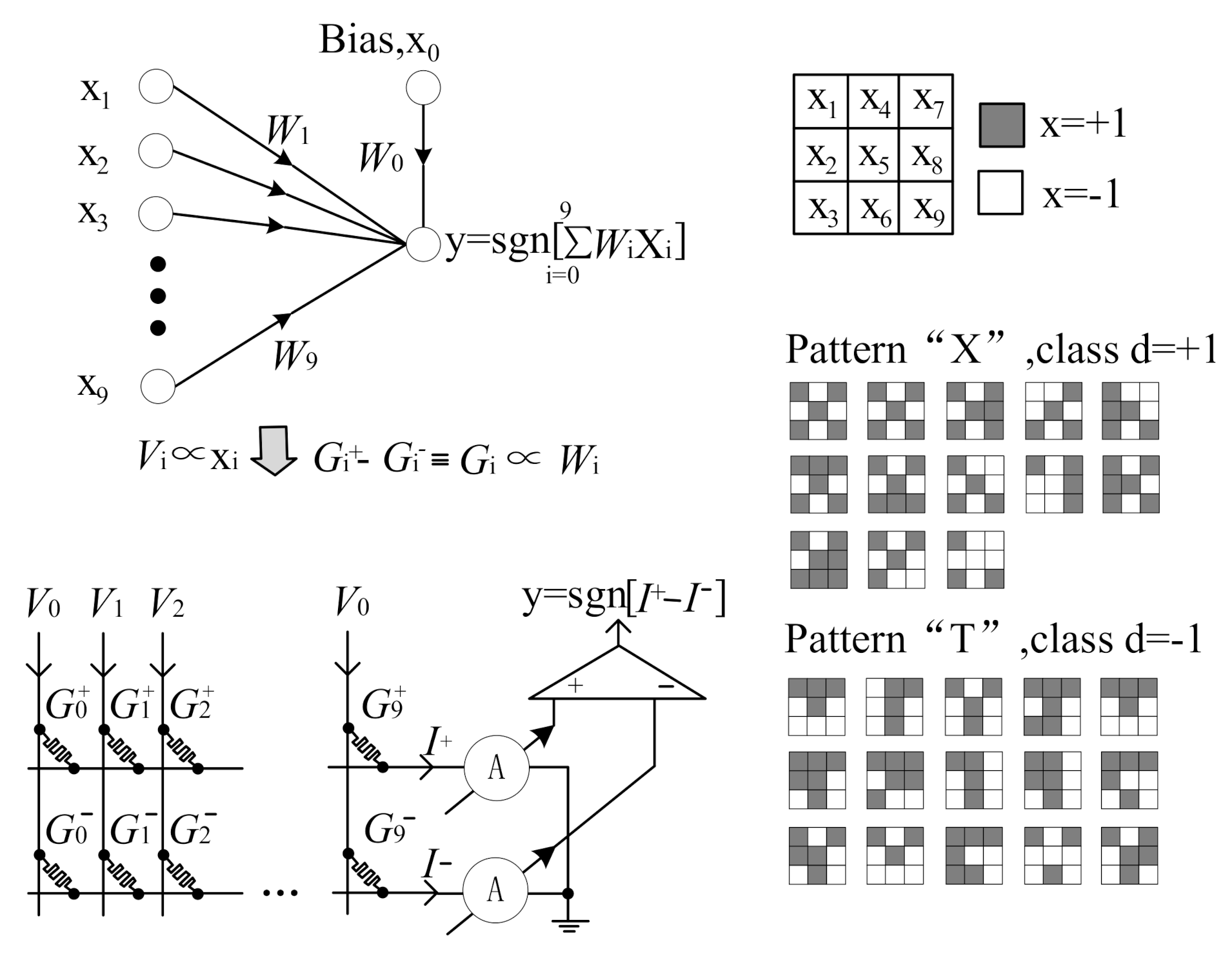

4.1. Image Recognition Based on Memristive Neural Networks

4.2. Image Classification Based on Memristive Neural Networks

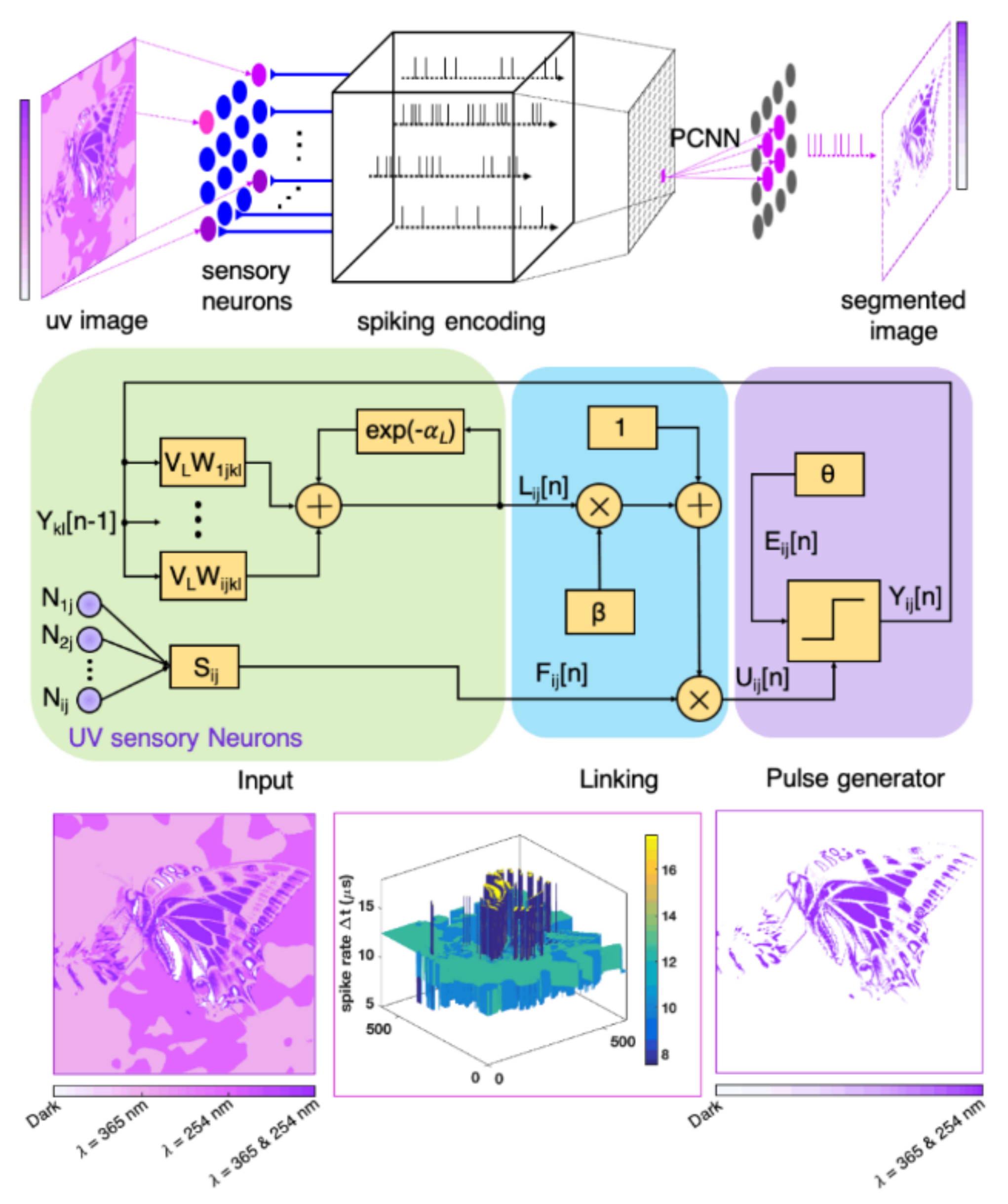

4.3. Image Segmentation Based on Memristive Neural Networks

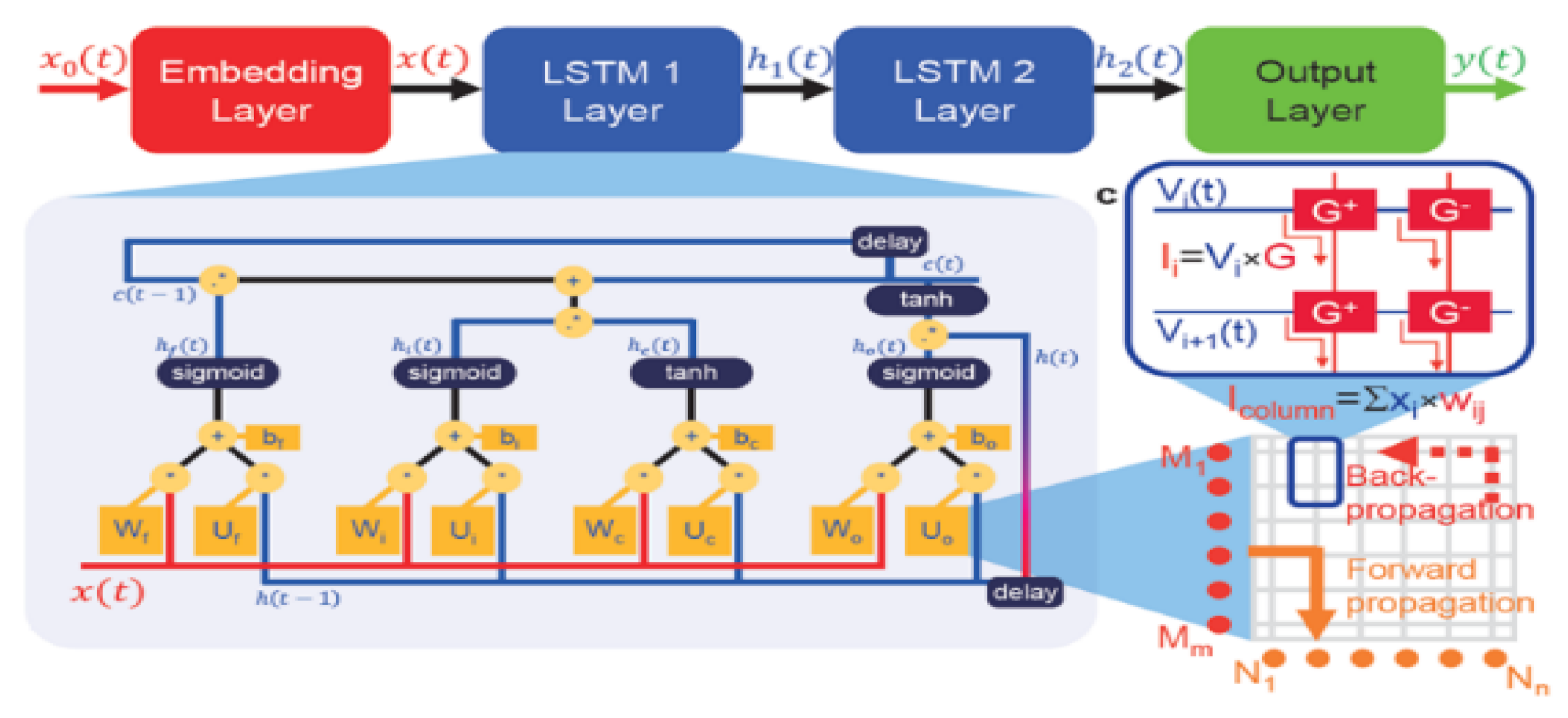

4.4. Others

4.5. Summary

- (1)

- The existing memristive synaptic circuits can only simulate the basic functions and behavioural characteristics of biological synapses, and they lack enough theoretical support from computational neuroscience. Therefore, it is crucial to design a fully functional and simple structured memristive synaptic circuit, which can address the problems of insufficient portray, unclear mechanism, and single plasticity of the conventional ones.

- (2)

- There is the accumulation of computational errors in memristor-based neural network circuits, which is mainly owing to the discrete nature of memristors, and it is difficult to avoid at the device level. Therefore, designing a newly structured memristor crossbar array that offsets the accumulated errors can provide a new perspective for the hardware implementation of neural networks.

- (3)

- The current research on image processing based on memristive neural networks is still stuck in the simulation of existing artificial neural networks. Therefore, the next research hotspot will involve taking both the advantages of neurocomputing science and image processing studies, exploring brain-inspired neural network training algorithms, and building memristive neural networks with brain-like memory.

5. Prospects

- (1)

- At the device level, the device stability is critical to the computing accuracy, as the drift of conductance states with time or environmental changes will result in undesired synaptic weight changes. On the one hand, more reliable and eco-friendly memory devices and memristive arrays are required. On the other hand, the construction of scalable and highly stable memristive mathematical models, following the physical mechanisms of memristor devices and the special properties of memristors, is one of the future directions to further promote image processing research based on memristive systems.

- (2)

- At the hardware level, in the short term, memristors will be specially utilized to accelerate the construction of artificial neural networks. Compared with conventional computer processors, their analogue signals are processed in a massively parallel manner, which increases the computational speed and fault tolerance simultaneously and significantly reduces the system power consumption. This parallel computing and low power consumption feature is well suited for image processing tasks with large data volumes and high computational complexity. In the long term, artificial synapses built on memristors will be one of the new approaches for facilitating the hardware implementation of brain-like neural networks. Nevertheless, the current memristive synaptic circuits can merely simulate the basic functions and behavioural characteristics of biological synapses, and they receive insufficient theoretical support from computational neuroscience. Therefore, the design of the memristive synaptic circuits with multiple biological synaptic properties can provide a new idea and platform for exploring a general memristive system-based image processing architecture to address the problems of insufficient portray, unclear mechanism, single plasticity, etc. Meanwhile, peripheral circuits control the read/write process in the memristor-based image processing systems. memristor-based image processing systems are expected to further improve the performance of online learning and reduce the complexity of peripheral programming circuits in the future.

- (3)

- At the algorithm level, the learning algorithms of memristor based image processing systems are still under development. The conventional computing system has the problems of high cost and difficult training when simulating impulsive neural networks, whereas the unique dynamic memory and reconfigurable characteristics of memristors can realize not only the diverse biological synaptic plasticity for artificial synapses but also the natural compatibility of artificial neural networks and impulsive neural networks. The image processing algorithm based on memristive systems can learn from deep learning and computational neuroscience to solve the problems of slow training speed and the insufficient online processing capability of conventional artificial neural networks in image processing applications. With better understanding of neuronal communications and functionalities, general learning algorithms should be designed to promote hardware development as well.

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Zidan, M.A.; Strachan, J.P.; Lu, W.D. The future of electronics based on memristive systems. Nat. Electron. 2018, 1, 22–29. [Google Scholar] [CrossRef]

- Wang, Z.; Joshi, S.; Savel’ev, S.E.; Jiang, H.; Midya, R.; Lin, P.; Hu, M.; Ge, N.; Strachan, J.P.; Li, Z.; et al. Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. Nat. Mater. 2017, 16, 101–108. [Google Scholar] [CrossRef] [Green Version]

- Dong, Z.; Sing Lai, C.; Zhang, Z.; Qi, D.; Gao, M.; Duan, S. Neuromorphic extreme learning machines with bimodal memristive synapses. Neurocomputing 2021, 453, 38–49. [Google Scholar] [CrossRef]

- Schuman, C.D.; Potok, T.E.; Patton, R.M.; Birdwell, J.D.; Dean, M.E.; Rose, G.S.; Plank, J.S. A survey of neuromorphic computing and neural networks in hardware. arXiv 2017, arXiv:1705.06963. [Google Scholar]

- Davies, M.; Srinivasa, N.; Lin, T.H.; Chinya, G.; Cao, Y.; Choday, S.H.; Dimou, G.; Joshi, P.; Imam, N.; Jain, S.; et al. Loihi: A neuromorphic manycore processor with on-chip learning. IEEE Micro 2018, 38, 82–99. [Google Scholar] [CrossRef]

- Jo, S.H.; Chang, T.; Ebong, I.; Bhadviya, B.B.; Mazumder, P.; Lu, W. Nanoscale memristor device as synapse in neuromorphic systems. Nano Lett. 2010, 10, 1297–1301. [Google Scholar] [CrossRef] [PubMed]

- Schmidhuber, J. Deep Learning in neural networks: An overview. Neural Netw. 2015, 61, 85–117. [Google Scholar] [CrossRef] [Green Version]

- Ji, X.; Qi, D.; Dong, Z.; Lai, C.S.; Zhou, G.; Hu, X. TSSM: Three-state switchable memristor model based on Ag/TiOx nanobelt/Ti configuration. Int. J. Bifurc. Chaos 2021, 31, 2130020. [Google Scholar] [CrossRef]

- Yang, J.J.; Strukov, D.B.; Stewart, D.R. Memristive devices for computing. Nat. Nanotechnol. 2013, 8, 13–24. [Google Scholar] [CrossRef]

- Prezioso, M.; Merrikh-Bayat, F.; Hoskins, B.D.; Adam, G.C.; Likharev, K.K.; Strukov, D.B. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. Nature 2015, 521, 61–64. [Google Scholar] [CrossRef] [Green Version]

- Pi, S.; Li, C.; Jiang, H.; Xia, W.; Xin, H.; Yang, J.J.; Xia, Q. Memristor crossbar arrays with 6-nm half-pitch and 2-nm critical dimension. Nat. Nanotechnol. 2019, 14, 35–39. [Google Scholar] [CrossRef] [PubMed]

- Gokmen, T.; Onen, M.; Haensch, W. Training deep convolutional neural networks with resistive cross-point devices. Front. Neurosci. 2017, 11, 538. [Google Scholar] [CrossRef] [PubMed]

- Esser, S.K.; Merolla, P.A.; Arthur, J.V.; Cassidy, A.S.; Appuswamy, R.; Andreopoulos, A.; Berg, D.J.; McKinstry, J.L.; Melano, T.; Barch, D.R.; et al. Convolutional networks for fast, energy-efficient neuromorphic computing. Proc. Natl. Acad. Sci. USA 2016, 113, 11441–11446. [Google Scholar] [CrossRef] [Green Version]

- Choi, S.; Shin, J.H.; Lee, J.; Sheridan, P.; Lu, W.D. Experimental demonstration of feature extraction and dimensionality reduction using memristor networks. Nano Lett. 2017, 17, 3113–3118. [Google Scholar] [CrossRef] [PubMed]

- Chua, L.O. Memristor—The missing circuit element. IEEE Trans. Circuit Theory 1971, 18, 507–519. [Google Scholar] [CrossRef]

- Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The missing memristor found. Nature 2008, 453, 80–83. [Google Scholar] [CrossRef]

- Zhang, C.; Ye, W.B.; Zhou, K.; Chen, H.Y.; Yang, J.Q.; Ding, G.; Chen, X.; Zhou, Y.; Zhou, L.; Li, F.; et al. Bioinspired artificial sensory nerve based on nafion memristor. Adv. Funct. Mater. 2019, 29, 1970133. [Google Scholar] [CrossRef]

- Hu, L.; Fu, S.; Chen, Y.; Cao, H.; Liang, L.; Zhang, H.; Gao, J.; Wang, J.; Zhuge, F. Ultrasensitive memristive synapses based on lightly oxidized sulfide films. Adv. Mater. 2017, 29, 6927. [Google Scholar] [CrossRef]

- Xu, W.; Lee, Y.; Min, S.Y.; Park, C.; Lee, T.W. Simple, inexpensive, and rapid approach to fabricate cross-shaped memristors using an inorganic-nanowire-digital-alignment technique and a one-step reduction process. Adv. Mater. 2016, 28, 527–532. [Google Scholar] [CrossRef]

- Dong, Z.; Lai, C.S.; He, Y.; Qi, D.; Duan, S. Hybrid dual-complementary metal-oxide-semiconductor/memristor synapse-based neural network with its applications in image super-resolution. IET Circuits Devices Syst. 2019, 13, 1241–1248. [Google Scholar] [CrossRef]

- Sheri, A.M.; Hwang, H.; Jeon, M.; Lee, B.G. Neuromorphic character recognition system with two PCMO memristors as a synapse. IEEE Trans. Ind. Electron. 2014, 61, 2933–2941. [Google Scholar] [CrossRef]

- Hu, M.; Graves, C.E.; Li, C.; Li, Y.; Ge, N.; Montgomery, E.; Davila, N.; Jiang, H.; Williams, R.S.; Yang, J.J.; et al. Memristor-Based analog computation and neural network classification with a dot product engine. Adv. Mater. 2018, 30, 5914. [Google Scholar] [CrossRef] [PubMed]

- Xie, L.; Nguyen, H.A.D.; Yu, J.; Kaichouhi, A.; Taouil, M.; Alfailakawi, M.; Hamdioui, S. Scouting logic: A novel memristor-based logic design for resistive computing. In Proceedings of the IEEE Computer Society Annual Symposium on VLSI, ISVLSI, Bochum, Germany, 3–5 July 2017; IEEE Computer Society: Bochum, Germany, 2017; pp. 176–181. [Google Scholar]

- Kvatinsky, S.; Satat, G.; Wald, N.; Friedman, E.G.; Kolodny, A.; Weiser, U.C. Memristor-based material implication (IMPLY) logic: Design principles and methodologies. IEEE Trans. Very Large Scale Integr. Syst. 2014, 22, 2054–2066. [Google Scholar] [CrossRef]

- James, A.P. Memristor threshold logic: An overview to challenges and applications. arXiv 2016, arXiv:1612.01711. [Google Scholar]

- Wang, Z.; Wu, H.; Burr, G.W.; Hwang, C.S.; Wang, K.L.; Xia, Q.; Yang, J.J. Resistive switching materials for information processing. Nat. Rev. Mater. 2020, 5, 173–195. [Google Scholar] [CrossRef]

- Biolek, D.; Biolek, Z.; Biolkova, V. SPICE modeling of memristive, memcapacitative and meminductive systems. In Proceedings of the ECCTD 2009—European Conference on Circuit Theory and Design Conference Program, Sofia, Bulgaria, 7–10 September 2020; IEEE: Antalya, Turkey, 2009; pp. 249–252. [Google Scholar]

- Wang, X.; Chen, Y.; Xi, H.; Li, H.; Dimitrov, D. Spintronic memristor through spin-thorque-induced magnetization motion. IEEE Electron Device Lett. 2009, 30, 294–297. [Google Scholar] [CrossRef]

- Kvatinsky, S.; Friedman, E.G.; Kolodny, A.; Weiser, U.C. TEAM: Threshold adaptive memristor model. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 211–221. [Google Scholar] [CrossRef]

- Kvatinsky, S.; Ramadan, M.; Friedman, E.G.; Kolodny, A. VTEAM: A general model for voltage-controlled memristors. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 786–790. [Google Scholar] [CrossRef]

- Zhang, J.; Tang, Z.; Xu, N.; Wang, Y.; Sun, H.; Wang, Z.; Fang, L. A generalized model of TiOx-based memristive devices and its application for image processing. Chin. Phys. B 2017, 26, 502. [Google Scholar] [CrossRef]

- Chen, M.; Bao, B.; Jiang, T.; Bao, H.; Xu, Q.; Wu, H.; Wang, J. Flux-charge analysis of initial state-dependent dynamical behaviors of a memristor emulator-based chua’s circuit. Int. J. Bifurc. Chaos 2018, 28, e1850120. [Google Scholar] [CrossRef]

- Xie, X.; Zou, L.; Wen, S.; Zeng, Z.; Huang, T. A flux-controlled logarithmic memristor model and emulator. Circuits Syst. Signal Process. 2019, 38, 1452–1465. [Google Scholar] [CrossRef]

- Ginoux, J.M.; Muthuswamy, B.; Meucci, R.; Euzzor, S.; Di Garbo, A.; Ganesan, K. A physical memristor based Muthuswamy–Chua–Ginoux system. Sci. Rep. 2020, 10, 6108. [Google Scholar] [CrossRef] [PubMed]

- Hu, X.; Wang, L.; Duan, S.; Liao, X. Memristor cross array and its application in image processing. Sci. Sin. Informationis 2011, 41, 500–512. [Google Scholar] [CrossRef]

- Tan, H.; Liu, G.; Zhu, X.; Yang, H.; Chen, B.; Chen, X.; Shang, J.; Lu, W.D.; Wu, Y.; Li, R.W. An optoelectronic resistive switching memory with integrated demodulating and arithmetic functions. Adv. Mater. 2015, 27, 2797–2803. [Google Scholar] [CrossRef] [PubMed]

- Wang, Z.Y. Research on Memristor-Based Multilevel Storage Circuit Design and Applications. Master’s Thesis, Huazhong University of Science & Technology, Wuhan, China, 2016. [Google Scholar]

- Liu, Q.; Wang, L.; Yang, J.; Wang, Y.; Duan, S. Fusion of image storage and operation based on ag-chalcogenide memristor with synaptic plasticity. J. Circuits Syst. Comput. 2017, 26, 1614. [Google Scholar] [CrossRef]

- Wang, T.Y.; Meng, J.L.; Li, Q.X.; Chen, L.; Zhu, H.; Sun, Q.Q.; Ding, S.J.; Zhang, D.W. Forming-free flexible memristor with multilevel storage for neuromorphic computing by full PVD technique. J. Mater. Sci. Technol. 2021, 60, 21–26. [Google Scholar] [CrossRef]

- Li, C.; Hu, M.; Li, Y.; Jiang, H.; Ge, N.; Montgomery, E.; Zhang, J.; Song, W.; Dávila, N.; Graves, C.E.; et al. Analogue signal and image processing with large memristor crossbars. Nat. Electron. 2018, 1, 52–59. [Google Scholar] [CrossRef]

- Halawani, Y.; Mohammad, B.; Al-Qutayri, M.; Al-Sarawi, S.F. Memristor-based hardware accelerator for image compression. IEEE Trans. Very Large Scale Integr. Syst. 2018, 26, 2749–2758. [Google Scholar] [CrossRef]

- Berco, D.; Ang, D.S.; Kalaga, P.S. Programmable photoelectric memristor gates for in situ image compression. Adv. Intell. Syst. 2020, 2, 2000079. [Google Scholar] [CrossRef]

- Hu, H.; Cao, Y.; Xu, J.; Ma, C.; Yan, H. An image compression and encryption algorithm based on the fractional-order simplest chaotic circuit. IEEE Access 2021, 9, 22141–22155. [Google Scholar] [CrossRef]

- Sheridan, P.M.; Cai, F.; Du, C.; Ma, W.; Zhang, Z.; Lu, W.D. Sparse coding with memristor networks. Nat. Nanotechnol. 2017, 12, 784–789. [Google Scholar] [CrossRef]

- Dong, Z.; Lai, C.S.; Xu, Z.; Qi, D. Single image super-resolution via the implementation of the hardware-friendly sparse coding. In Proceedings of the 2018 37th Chinese Control Conference (CCC), Wuhan, China, 25–27 July 2018; IEEE Computer Society: Wuhan, China, 2018; Volume 2018, pp. 8132–8137. [Google Scholar]

- Dong, Z.; Du, C.; Lin, H.; Lai, C.S.; Hu, X.; Duan, S. Multi-channel Memristive Pulse Coupled Neural Network Based Multi-frame Images Super-resolution Reconstruction Algorithm. J. Electron. Inf. Technol. 2020, 42, 835–843. [Google Scholar] [CrossRef]

- Dong, Z.K.; Yan, Y.F.; Qi, D.L.; Chen, J.; Diam, S.C. Transmemristive cross array and its application in image processing. In Proceedings of the 36th China Control Conference, Dalian, China, 26–28 July 2017; Dalian University of Technology: Dalian, China, 2017. [Google Scholar]

- Shang, L.; Duan, S.; Wang, L.; Huang, T. SRMC: A multibit memristor crossbar for self-renewing image mask. IEEE Trans. Very Large Scale Integr. Syst. 2018, 26, 2830–2841. [Google Scholar] [CrossRef]

- Athreyas, N.; Song, W.; Perot, B.; Xia, Q.; Mathew, A.; Gupta, J.; Gupta, D.; Yang, J.J. Memristor-CMOS analog coprocessor for acceleration of high-performance computing applications. ACM J. Emerg. Technol. Comput. Syst. 2018, 14, 9985. [Google Scholar] [CrossRef]

- Pajouhi, Z.; Roy, K. Image edge detection based on swarm intelligence using memristive networks. IEEE Trans. Comput. Des. Integr. Circuits Syst. 2018, 37, 1774–1787. [Google Scholar] [CrossRef] [Green Version]

- Yang, H.; Duan, S.C.; Dong, Z.K.; Wang, L.D.; Hu, X.F.; Shang, L.T. General logic circuit based on memristor-cmos and its application. Sci. China Inf. Sci. 2020, 50, 14. [Google Scholar]

- Ye, X.; Wang, X.; Gao, S.; Mou, J.; Wang, Z.; Yang, F. A new chaotic circuit with multiple memristors and its application in image encryption. Nonlinear Dyn. 2020, 99, 1489–1506. [Google Scholar] [CrossRef]

- Wu, X.; Saxena, V.; Zhu, K. Homogeneous spiking neuromorphic system for real-world pattern recognition. IEEE J. Emerg. Sel. Top. Circuits Syst. 2015, 5, 254–266. [Google Scholar] [CrossRef] [Green Version]

- Yakopcic, C.; Alom, M.Z.; Taha, T.M. Memristor crossbar deep network implementation based on a Convolutional neural network. In Proceedings of the 2016 International Joint Conference on Neural Networks (IJCNN), Vancouver, BC, Canada, 24–29 July 2016; Institute of Electrical and Electronics Engineers Inc.: Vancouver, BC, Canada, 2016; Volume 2016, pp. 963–970. [Google Scholar]

- Zhang, Y.; Wang, X.; Friedman, E.G. Memristor-based circuit design for multilayer neural networks. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 677–686. [Google Scholar] [CrossRef]

- Zhou, Z.; Huang, P.; Xiang, Y.C.; Shen, W.S.; Zhao, Y.D.; Feng, Y.L.; Gao, B.; Wu, H.Q.; Qian, H.; Liu, L.F.; et al. A new hardware implementation approach of BNNs based on nonlinear 2T2R synaptic cell. Tech. Dig. Int. Electron Devices Meet. IEDM 2019, 18, 71–74. [Google Scholar] [CrossRef]

- Wang, Z.; Li, C.; Lin, P.; Rao, M.; Nie, Y.; Song, W.; Qiu, Q.; Li, Y.; Yan, P.; Strachan, J.P.; et al. In situ training of feed-forward and recurrent convolutional memristor networks. Nat. Mach. Intell. 2019, 1, 434–442. [Google Scholar] [CrossRef]

- Yao, P.; Wu, H.; Gao, B.; Tang, J.; Zhang, Q.; Zhang, W.; Yang, J.J.; Qian, H. Fully hardware-implemented memristor convolutional neural network. Nature 2020, 577, 641–646. [Google Scholar] [CrossRef]

- Yao, P.; Wu, H.; Gao, B.; Eryilmaz, S.B.; Huang, X.; Zhang, W.; Zhang, Q.; Deng, N.; Shi, L.; Wong, H.S.P.; et al. Face classification using electronic synapses. Nat. Commun. 2017, 8, 5199. [Google Scholar] [CrossRef]

- Liu, X.; Huang, Y.; Zeng, Z.; Wunsch, D.C. Memristor-based HTM spatial pooler with on-device learning for pattern recognition. IEEE Trans. Syst. Man Cybern. Syst. 2020, 3, 5612. [Google Scholar] [CrossRef]

- Krestinskaya, O.; James, A.P. Approximate probabilistic neural networks with gated threshold logic. In Proceedings of the 2018 IEEE 18th International Conference on Nanotechnology, Cork, Ireland, 23–26 July 2018; Volume 18, p. 6302. [Google Scholar] [CrossRef] [Green Version]

- Yu, Y.; Adu, K.; Tashi, N.; Anokye, P.; Wang, X.; Ayidzoe, M.A. RMAF: Relu-Memristor-Like Activation Function for Deep Learning. IEEE Access 2020, 8, 72727–72741. [Google Scholar] [CrossRef]

- Alibart, F.; Zamanidoost, E.; Strukov, D.B. Pattern classification by memristive crossbar circuits using ex situ and in situ training. Nat. Commun. 2013, 4, 3072. [Google Scholar] [CrossRef] [Green Version]

- Bayat, F.M.; Prezioso, M.; Chakrabarti, B.; Nili, H.; Kataeva, I.; Strukov, D. Implementation of multilayer perceptron network with highly uniform passive memristive crossbar circuits. Nat. Commun. 2018, 9, 4482. [Google Scholar] [CrossRef]

- Lin, P.; Li, C.; Wang, Z.; Li, Y.; Jiang, H.; Song, W.; Rao, M.; Zhuo, Y.; Upadhyay, N.K.; Barnell, M.; et al. Three-dimensional memristor circuits as complex neural networks. Nat. Electron. 2020, 3, 225–232. [Google Scholar] [CrossRef]

- Zhang, W.; Gao, B.; Yao, P.; Tang, J.; Qian, H.; Wu, H. Array-level boosting method with spatial extended allocation to improve the accuracy of memristor based computing-in-memory chips. Sci. China Inf. Sci. 2021, 64, 3198. [Google Scholar] [CrossRef]

- Chu, M.; Kim, B.; Park, S.; Hwang, H.; Jeon, M.; Lee, B.H.; Lee, B.G. Neuromorphic hardware system for visual pattern recognition with memristor array and CMOS neuron. IEEE Trans. Ind. Electron. 2015, 62, 2410–2419. [Google Scholar] [CrossRef]

- Chiu, P.F.; Nikolić, B. A differential 2R crosspoint RRAM array with zero standby current. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 461–465. [Google Scholar] [CrossRef]

- Wen, S.; Wei, H.; Zeng, Z.; Huang, T. Memristive fully convolutional network: An accurate hardware image-segmentor in deep learning. IEEE Trans. Emerg. Top. Comput. Intell. 2018, 2, 324–334. [Google Scholar] [CrossRef]

- Xiu, C.; Li, X. Edge extraction based on memristor cell neural network with fractional order template. IEEE Access 2019, 7, 90750–90759. [Google Scholar] [CrossRef]

- Wu, Q.; Dang, B.; Lu, C.; Xu, G.; Yang, G.; Wang, J.; Chuai, X.; Lu, N.; Geng, D.; Wang, H.; et al. Spike encoding with optic sensory neurons enable a pulse coupled neural network for ultraviolet image segmentation. Nano Lett. 2020, 20, 8015–8023. [Google Scholar] [CrossRef]

- Chen, J.; Wu, Y.; Yang, Y.; Wen, S.; Shi, K.; Bermak, A.; Huang, T. An efficient memristor-based circuit implementation of squeeze-and-excitation fully convolutional neural networks. IEEE Trans. Neural Netw. Learn. Syst. 2021, 4, 4047. [Google Scholar] [CrossRef]

- Tsai, H.; Ambrogio, S.; MacKin, C.; Narayanan, P.; Shelby, R.M.; Rocki, K.; Chen, A.; Burr, G.W. Inference of long-short term memory networks at software-equivalent accuracy using 2.5M analog phase change memory devices. Dig. Tech. Pap.—Symp. VLSI Technol. 2019, 2019, T82–T83. [Google Scholar] [CrossRef]

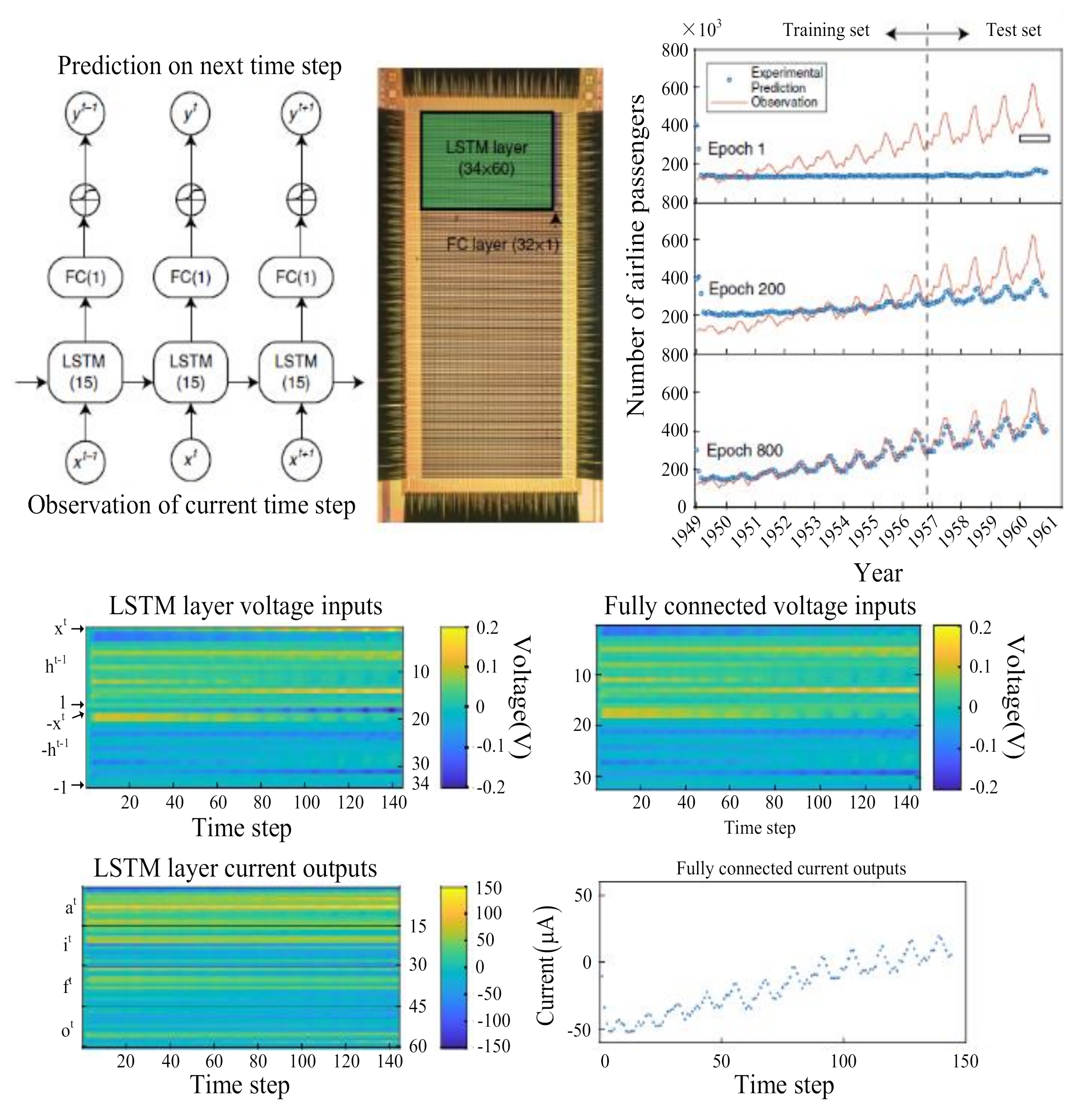

- Li, C.; Wang, Z.; Rao, M.; Belkin, D.; Song, W.; Jiang, H.; Yan, P.; Li, Y.; Lin, P.; Hu, M.; et al. Long short-term memory networks in memristor crossbar arrays. Nat. Mach. Intell. 2019, 1, 49–57. [Google Scholar] [CrossRef]

- Farkhani, H.; Tohidi, M.; Farkhani, S.; Madsen, J.K.; Moradi, F. A low-power high-speed spintronics-based neuromorphic computing system using real-time tracking method. IEEE J. Emerg. Sel. Top. Circuits Syst. 2018, 8, 627–638. [Google Scholar] [CrossRef]

- Hu, W.; Luo, H.; Chen, C.; Wei, R. A multi-interval homotopy analysis method using multi-objective optimization for analytically analyzing chaotic dynamics in memristive circuit. IEEE Access 2019, 7, 116328–116341. [Google Scholar] [CrossRef]

| Model Type | Current-Voltage Relationship | Dynamic Equation of State Variable |

|---|---|---|

| HP Memristive Model [16] | ||

| Nonlinear Memristive Model [27] | ||

| Simmons Memristive Model [28] | ||

| TEAM Memristive Model [29] | ||

| VTEAM Memristive Model [30] | ||

| General TiOx Memristive Model [31] |

| HP Memristive Model [16] | Nonlinear Memristive Model [27] | Simmons Memristive Model [28] | TEAM Memristive Model [29] | VTEAM Memristive Model [30] | General TiOx Memristive Model [31] | |

|---|---|---|---|---|---|---|

| Physical Support | Yes | No | Yes | No | No | No |

| Physical Mechanism | Ionic Migration | Ionic Migration | Quantum Tunneling | No | No | Ionic Migration |

| Model Complexity | Simple | Simple | Complex | Moderate | Moderate | Moderate |

| Applied Range | Wider | Wider | Narrower | Wider | Wider | Wider |

| Parameter | DRAM | NAND | STT-RAM | RRAM | FeRAM | PCM |

|---|---|---|---|---|---|---|

| Capacity | ~16 Gb | ~1 Tb | ~64 Mb | ~1 TB | ~64 MB | ~8 Gb |

| Technology level | ~20 nm | ~16 nm | ~32 nm | ~11 nm | ~65 nm | ~5 nm |

| Feature Size | 6–10 F2 | 4–11 F2 | 16–60 F2 | 4–14 F2 | 15–34 F2 | 4–8 F2 |

| Read Operation Time | <10 ns | 10–50 us | 2–20 ns | 10–50 ns | 20–80 ns | 10–100 ns |

| Write Operation Time | <10 ns | 0.1–1 ms | 5–35 ns | 10–50 ns | 10–5 ns | 20–120 ns |

| Lifetime | >1015 | 104–106 | 1012–1015 | 108–1010 | 1012–1014 | 108–1012 |

| Data Retention | Refresh | 10 Years | >10 Years | 10 Years | 10 Years | >10 Years |

| Write Power | 0.1 ~0.1 nJ/b | 0.1–1 nJ/b | 1.6–5 nJ/b | ~0.1 nJ/b | <1 nJ/b | <1 nJ/b |

| Idle Power | High | Low | Low | Low | Low | Low |

| Non-volatile | Volatile | Non-volatile | Non-volatile | Non-volatile | Non-volatile | Non-volatile |

| Destructive Read | Destructive | Non-destructive | Non-destructive | Non-destructive | Destructive | Non-destructive |

| Major Technical Bottlenecks | Memory refresh, volatility, limited memory process | Limited lifetime performance, low storage density | Small capacity, high write power consumption, poor stability | Unclear material storage mechanism | Small capacity, destructive read, low storage density | Small capacity, narrow range of material operable temperature |

| Reference | Architectural Characteristics of Image Processing Algorithms Based on Memristive Neural Networks | ||

|---|---|---|---|

| Input Coding | Weight Representation | Neural Network Communication | |

| [67] | Amplitude Encoding/Time Encoding Analogue Signal | Differential Amplifier | Multi-precision |

| [69] | Amplitude Encoding Analogue Signal | Multi-precision | MSB |

| [38] | Amplitude Encoding Analogue Signal | Differential Amplifier | Multi-precision |

| [40] | Amplitude Encoding Analogue Signal | Differential Amplifier | Multi-precision |

| [62] | Amplitude Encoding Analogue Signal | Peripheral Circuit Processing | MSB |

| Key Challenges | Possible Strategies | ||

|---|---|---|---|

| Device level | Materials | Fabricate standard-process and compatible new materials and interconnect materials with high conductance | Use alternative organic materials, 2D, and functional materials, and develop new processes for new materials |

| Models | Less computational complexity and high physics fidelity for large-scale system simulation | Build mathematical models of memristors, combined physical and empirical behavior of devices | |

| Hardware level | Peripheral circuits | Efficient read/write scheme for digital/analog mode | Use analog circuits, field programmable gate array (FPGA), and look-up-table (LUT) connected to the chips and approximate circuits |

| Synaptic circuits | The operating mechanism is still obscure, the cognition function modeling is not good, and the fault diagnosis system is still in progress. | Develop the novel memristive synapse circuit will possess biological synaptic features | |

| Algorithm level | Operations | Develop a general computing system for data mapping, dot product, and STDP | Experimentally build applications with a memristive crossbar |

| Training and testing accuracies | Develop practical network topology and learning algorithm | Develop hybrid algorithms, and brain-inspired systems consist of both ANNs and SNNs |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ji, X.; Dong, Z.; Zhou, G.; Lai, C.S.; Yan, Y.; Qi, D. Memristive System Based Image Processing Technology: A Review and Perspective. Electronics 2021, 10, 3176. https://doi.org/10.3390/electronics10243176

Ji X, Dong Z, Zhou G, Lai CS, Yan Y, Qi D. Memristive System Based Image Processing Technology: A Review and Perspective. Electronics. 2021; 10(24):3176. https://doi.org/10.3390/electronics10243176

Chicago/Turabian StyleJi, Xiaoyue, Zhekang Dong, Guangdong Zhou, Chun Sing Lai, Yunfeng Yan, and Donglian Qi. 2021. "Memristive System Based Image Processing Technology: A Review and Perspective" Electronics 10, no. 24: 3176. https://doi.org/10.3390/electronics10243176

APA StyleJi, X., Dong, Z., Zhou, G., Lai, C. S., Yan, Y., & Qi, D. (2021). Memristive System Based Image Processing Technology: A Review and Perspective. Electronics, 10(24), 3176. https://doi.org/10.3390/electronics10243176