A Fast Lock All-Digital MDLL Using a Cyclic Vernier TDC for Burst-Mode Links

Abstract

1. Introduction

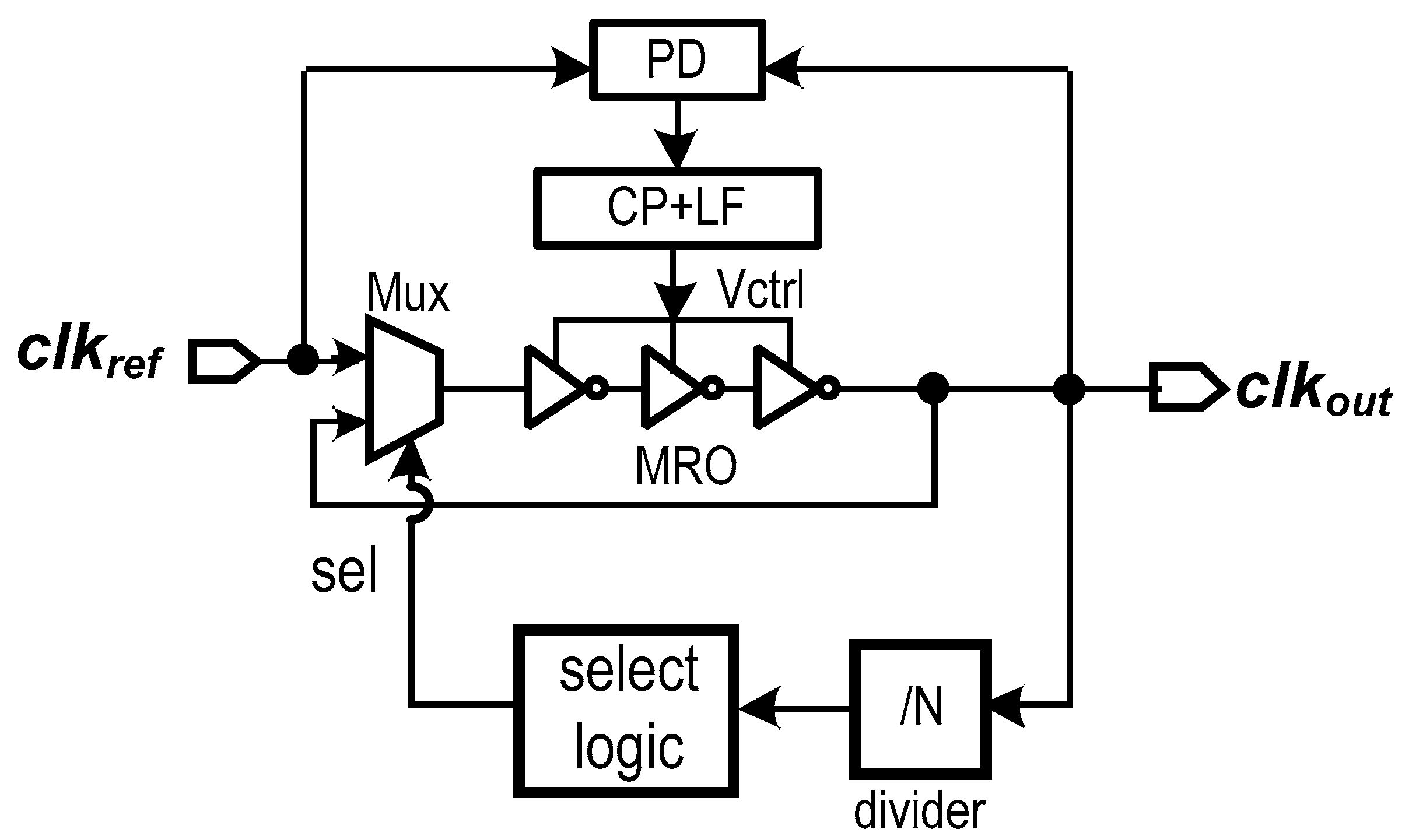

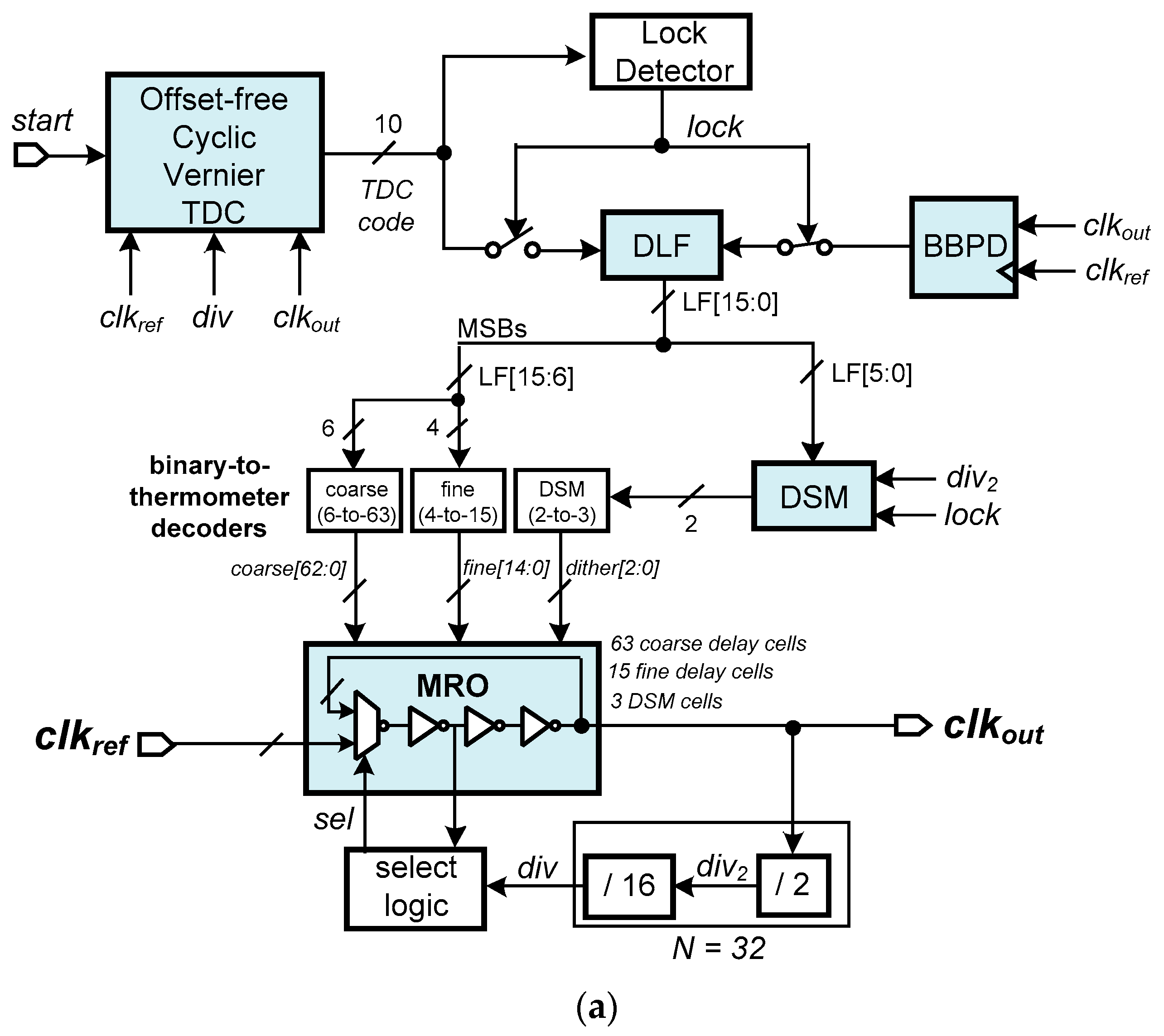

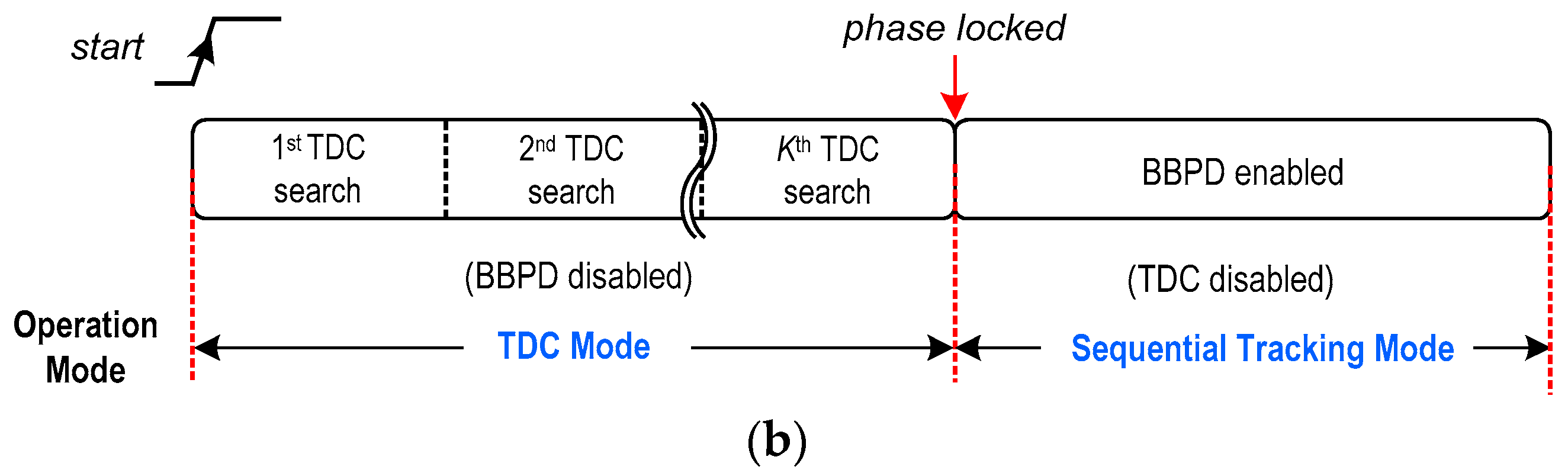

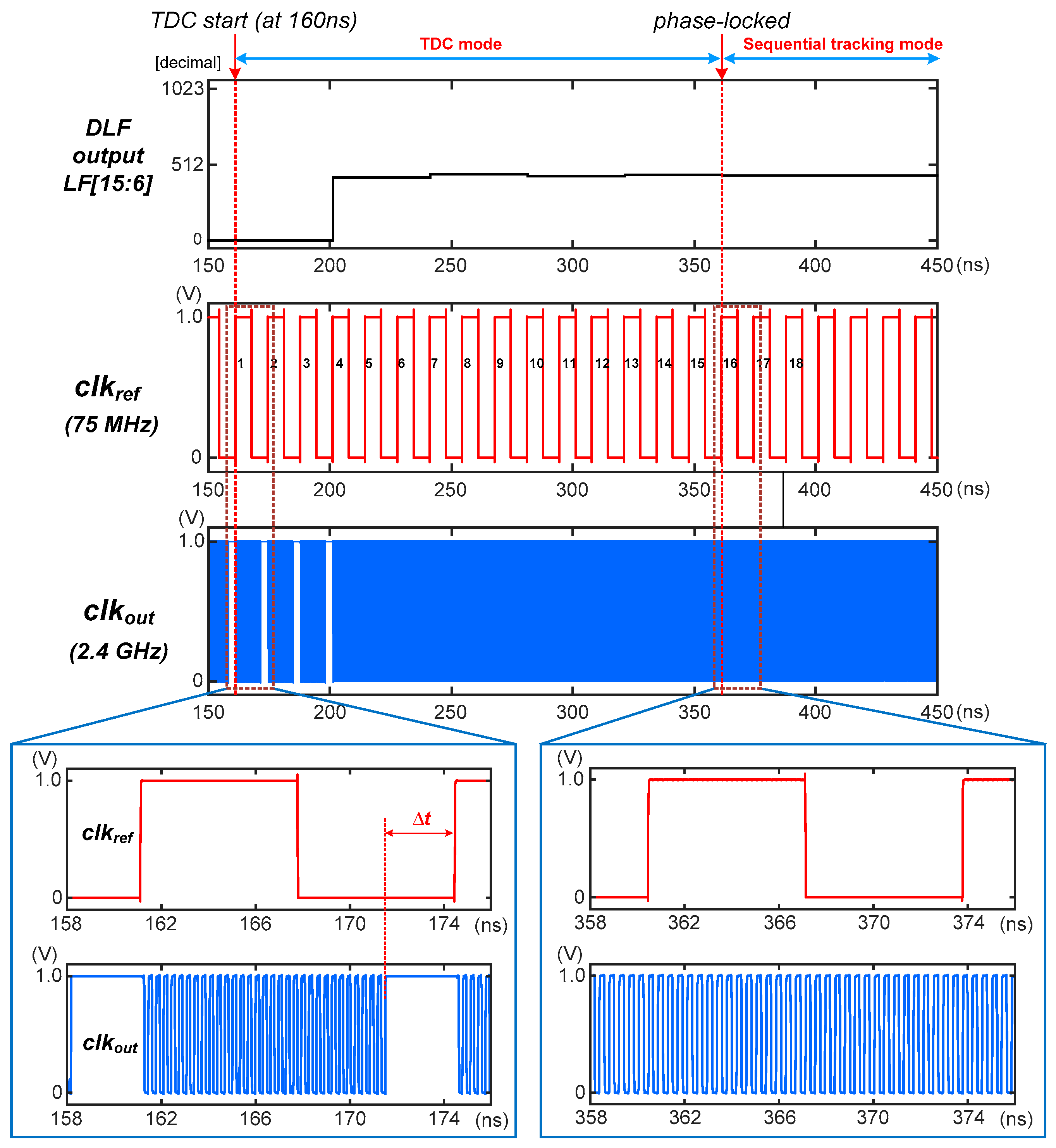

2. Proposed All-Digital MDLL

2.1. Proposed MDLL Architecture

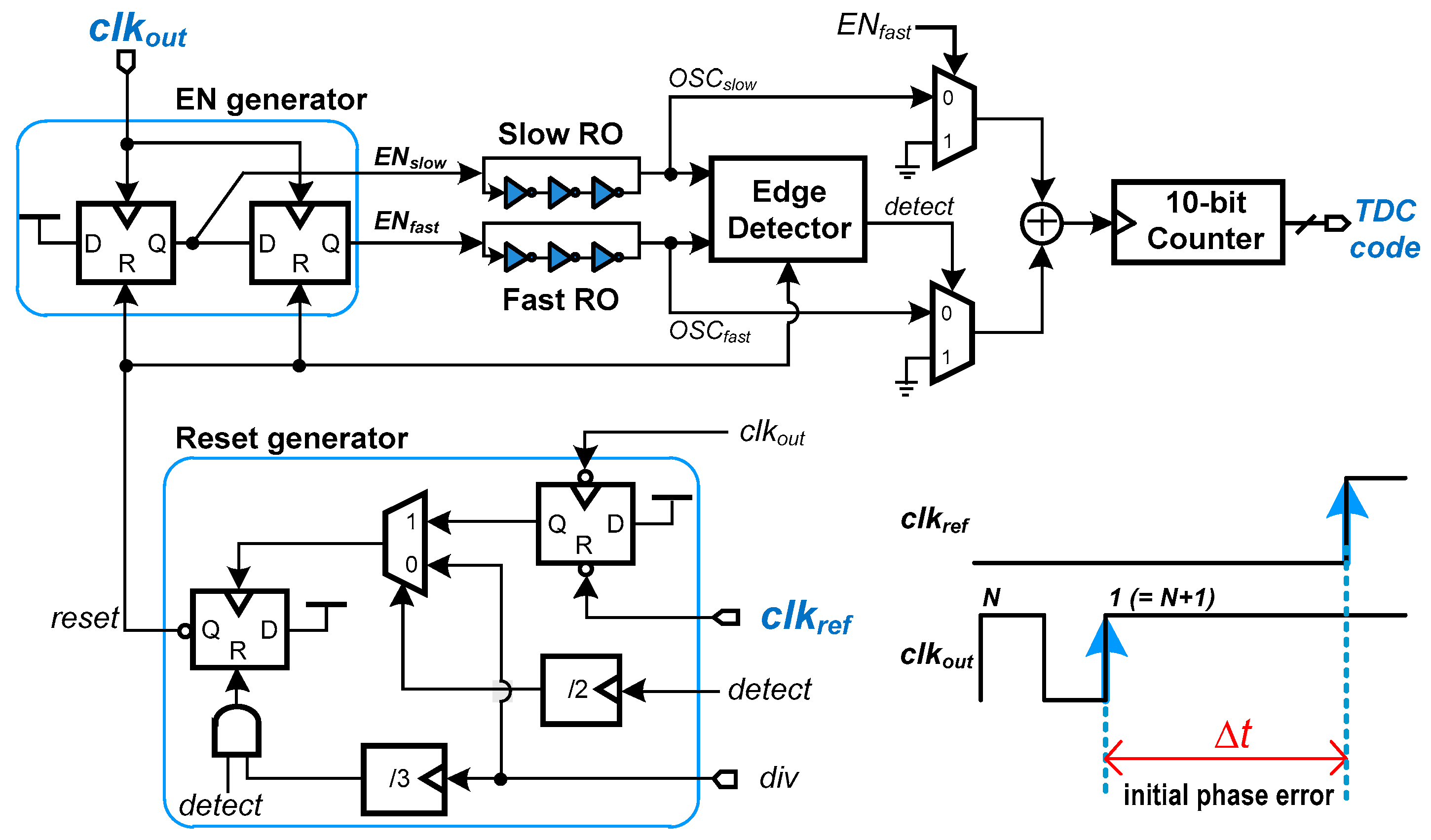

2.2. Proposed Offset-Free Cyclic Vernier TDC

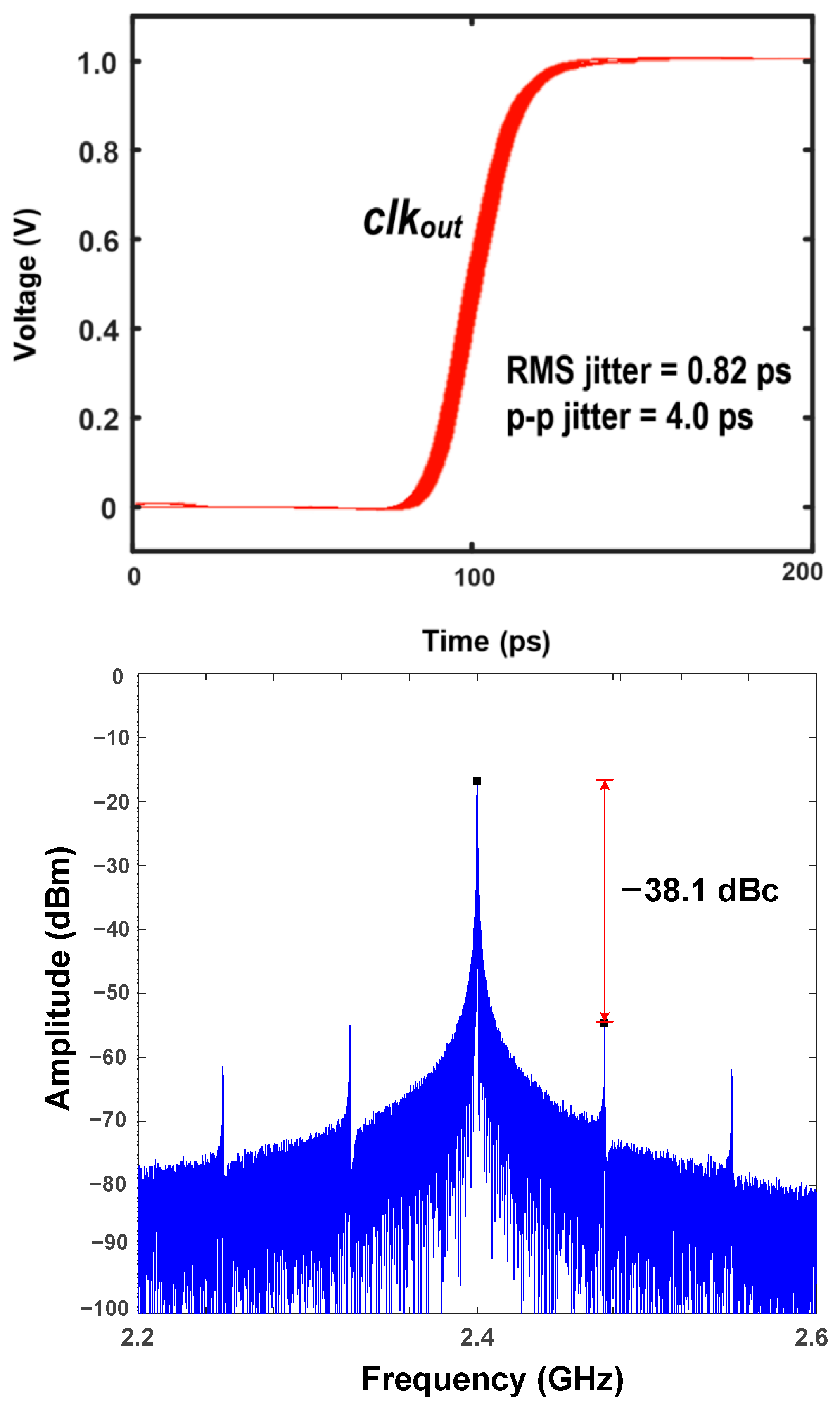

3. Experimental Results

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Leibowitz, B.; Palmer, R.; Poulton, J.; Frans, Y.; Li, S.; Wilson, J.; Bucher, M.; Fuller, A.; Eyles, J.; Aleksic, M.; et al. A 4.3 GB/s mobile memory interface with power-efficient bandwidth scaling. IEEE J. Solid State Circuits 2010, 45, 889–898. [Google Scholar] [CrossRef]

- Zerbe, J.; Daly, B.; Dettloff, W.; Stone, T.; Stonecypher, W.; Venkatesan, P.; Prabhu, K.; Su, B.; Ren, J.; Tsang, B.; et al. A 5.6Gb/s 2.4mW/Gb/s bidirectional link with 8ns power-on. In Proceedings of the 2011 Symposium on VLSI Circuits-Digest of Technical Papers, Honolulu, HI, USA, 15–17 June 2011; pp. 82–83. [Google Scholar]

- Hossain, M.; Aquil, F.; Chau, P.S.; Tsang, B.; Le, P.; Wei, J.; Stone, T.; Daly, B.; Tran, C.; Eble, J.C.; et al. A Fast-Lock, Jitter Filtering All-Digital DLL Based Burst-Mode Memory Interface. IEEE J. Solid State Circuits 2014, 49, 1048–1062. [Google Scholar] [CrossRef]

- Choi, W.S.; Anand, T.; Shu, G.; Elshazly, A.; Hanumolu, P.K. A burst-mode digital receiver with programmable input jitter filtering for energy proportional links. IEEE J. Solid State Circuits 2015, 50, 737–748. [Google Scholar] [CrossRef]

- Hanumolu, P.K.; Brownlee, M.; Mayaram, K.; Moon, U.K. Analysis of charge-pump phase-locked loops. IEEE Trans. Circuits Syst. I 2004, 51, 1665–1674. [Google Scholar] [CrossRef]

- Hekmat, M.; Aryanfar, F.; Wei, J.; Gadde, V.; Navid, R. A 25 GHz Fast-Lock Digital LC PLL With Multiphase Output Using a Magnetically-Coupled Loop of Oscillators. IEEE J. Solid State Circuits 2015, 50, 490–502. [Google Scholar] [CrossRef]

- Farjad-Rad, R.; Dally, W.; Ng, H.T.; Senthinathan, R.; Lee, M.-J.E.; Rathi, R.; Poulton, J. A low-power multiplying DLL for low-jitter multi-gigahertz clock generation in highly integrated digital chips. IEEE J. Solid State Circuits 2002, 37, 1804–1812. [Google Scholar] [CrossRef]

- Elshazly, A.; Inti, R.; Young, B.; Hanumolu, P.K. Clock multiplication techniques using digital multiplying delay-locked loops. IEEE J. Solid State Circuits 2013, 48, 1416–1428. [Google Scholar] [CrossRef]

- Kundu, S.; Kim, B.J.; Kim, C.H. A 0.2–1.45-GHz subsampling fractional-N digital MDLL with zero-offset aperture PD-based spur cancellation and in situ static phase offset detection. IEEE J. Solid State Circuits 2017, 52, 799–811. [Google Scholar] [CrossRef]

- Marucci, G.; Fenaroli, A.; Marzin, G.; Levantino, S.; Samori, C.; Lacaita, A.L. A 1.7 GHz MDLL-based fractional-N frequency synthesizer with 1.4ps RMS integrated jitter and 3 mW power using a 1b TDC. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 360–361. [Google Scholar]

- Nandwana, R.K.; Saxena, S.; Elshazly, A.; Mayaram, K.; Hanumolu, P.K. A 1-to-2048 fully-integrated cascaded digital frequency synthesizer for low frequency reference clocks using scrambling TDC. IEEE Tran. Circuits Syst. I 2017, 64, 283–295. [Google Scholar] [CrossRef]

- Kim, H.; Kim, Y.; Kim, T.; Ko, H.-J.; Cho, S. A 2.4-GHz 1.5-mW digital multiplying delay-locked loop using pulsewidth comparator and double injection technique. IEEE J. Solid State Circuits 2017, 52, 2934–2946. [Google Scholar] [CrossRef]

- Helal, B.M.; Straayer, M.Z.; Wei, G.Y.; Perrott, M.H. A highly digital MDLL-based clock multiplier that leverages a self-scrambling time-to-digital converter to achieve subpicosecond jitter performance. IEEE J. Solid State Circuits 2008, 43, 855–863. [Google Scholar] [CrossRef]

- Kim, J.; Han, S. A fast-locking all-digital Multiplying DLL for fractional-ratio dynamic frequency scaling. IEEE Tran. Circuits Syst. II 2018, 65, 276–280. [Google Scholar] [CrossRef]

- Park, D.; Kim, J. A low-jitter 2.4 GHz all-digital MDLL with a dithering jitter reduction scheme for 256 times frequency multiplication. IEICE Electron. Express 2020, 17. [Google Scholar] [CrossRef]

- Chiu, Y.-K.; Liu, S.-I. A PVT-tolerant MDLL using a frequency calibrator and a voltage monitor. IEEE Trans. Very Large Scale Integr. (VLSI) Syst 2019, 27, 2698. [Google Scholar] [CrossRef]

- Yang, S.; Yin, J.; Mak, P.-I.; Martins, R.P. A 0.0056-mm2 –249-dB-FoM all-digital MDLL using a block-sharing offset-free frequency-tracking loop and dual multiplexed-ring VCOs. IEEE J. Solid State Circuits 2019, 54, 88–98. [Google Scholar] [CrossRef]

- Levantino, S.; Marucci, G.; Marzin, G.; Fenaroli, A.; Samori, C.; Lacaita, A.-L. A 1.7 GHz fractional-N frequency synthesizer based on a multiplying delay-locked loop. IEEE J. Solid State Circuits 2015, 50, 2678–2691. [Google Scholar] [CrossRef]

- Ali, T.-A.; Hafez, A.-A.; Drost, R.; Ho, R.; Yang, C.-K. A 4.6GHz MDLL with −46dBc reference spur and aperture position tuning. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 20–24 February 2011; pp. 466–467. [Google Scholar]

- Chan, A.H.; Roberts, G.W. A jitter characterization system using a component-invariant Vernier delay line. IEEE Trans. Very Large Scale Integr. (VLSI) Syst 2004, 12, 79–95. [Google Scholar] [CrossRef]

- Chen, P.; Chen, C.; Zheng, J.C.; Shen, Y. A PVT insensitive Vernier-based time-to-digital converter with extended input range and high accuracy. IEEE Trans. Nucl. Sci. 2007, 54, 294–302. [Google Scholar] [CrossRef]

- Yu, J.; Dai, F.F.; Jaeger, R.C. A 12-Bit Vernier Ring Time-to-Digital Converter in 0.13 μm CMOS Technology. IEEE J. Solid State Circuits 2010, 45, 830–842. [Google Scholar] [CrossRef]

- Park, Y.; Wentzloff, D.D. A Cyclic Vernier TDC for ADPLLs Synthesized from a Standard Cell Library. IEEE Tran. Circuits Syst. I 2011, 58, 1511–1517. [Google Scholar] [CrossRef]

- Lu, P.; Liscidini, A.; Andreani, P. A 3.6 mW, 90 nm CMOS gated-Vernier time-to-digital converter with an equivalent resolution of 3.2 ps. IEEE J. Solid State Circuits 2012, 47, 1626–1635. [Google Scholar] [CrossRef]

- Lu, P.; Wu, Y.; Andreani, P. A 2.2-ps two-dimensional gated-Vernier time-to-digital converter with digital calibration. IEEE Tran. Circuits Syst. II 2016, 63, 1019–1023. [Google Scholar] [CrossRef]

- Dudek, P.; Szczepanski, S.; Hatfield, J.V. A high-resolution CMOS time-to-digital converter utilizing a Vernier delay line. IEEE J. Solid State Circuits 2000, 35, 240–247. [Google Scholar] [CrossRef]

- Enz, C.; Temes, G. Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization. Proc. IEEE 1996, 84, 1584–1614. [Google Scholar] [CrossRef]

| Reference | [9] | [12] | [13] | [14] | This Work |

|---|---|---|---|---|---|

| Process and Supply | 65 nm/1.2 V | 28 nm/1.0 V | 130 nm/1.2 V | 65 nm/1.1 V | 65 nm/1.0 V |

| Freq. range (GHz) | 0.2–1.45 | 2.4 | 1.6 | 0.7–2.0 | 2.0–3.0 |

| Output freq. (GHz) | 1.4 | 2.4 | 1.6 | 2.0 | 2.4 |

| Reference freq. (MHz) | 87.5 | 75 | 50 | 500 | 75 |

| Multiplication factor (N) | 16 | 32 | 32 | N/M = 8/2 | 32 |

| Locking time (cycles) | N/A | >6000 | N/A | 40 | 15 |

| p-p/RMS jitter (ps) | N/A | 15.9/1.53 | 11.1/0.93 | 22/2.86 | 17.46/2.58 |

| Power (mW) | 8.0 @1.4 GHz | 1.51 @2.4 GHz | 9.2 @1.6 GHz | 3.31 @1 GHz | 3.3 @2.4 GHz |

| Active area (mm2) | 0.054 | 0.024 | 0.76 | 0.019 | 0.043 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, D.; Choi, S.; Kim, J. A Fast Lock All-Digital MDLL Using a Cyclic Vernier TDC for Burst-Mode Links. Electronics 2021, 10, 177. https://doi.org/10.3390/electronics10020177

Park D, Choi S, Kim J. A Fast Lock All-Digital MDLL Using a Cyclic Vernier TDC for Burst-Mode Links. Electronics. 2021; 10(2):177. https://doi.org/10.3390/electronics10020177

Chicago/Turabian StylePark, Dongjun, Sungwook Choi, and Jongsun Kim. 2021. "A Fast Lock All-Digital MDLL Using a Cyclic Vernier TDC for Burst-Mode Links" Electronics 10, no. 2: 177. https://doi.org/10.3390/electronics10020177

APA StylePark, D., Choi, S., & Kim, J. (2021). A Fast Lock All-Digital MDLL Using a Cyclic Vernier TDC for Burst-Mode Links. Electronics, 10(2), 177. https://doi.org/10.3390/electronics10020177