1. Introduction

Recent advances of mobile audio devices such as true wireless stereos and cellular phones require microphone read-out integrated circuits (M-ROICs) with wide dynamic range (DR). Furthermore, the power consumption of the M-ROIC should be kept low to make the battery life acceptably long. Besides electrical performance, the silicon area occupied by the M-ROIC and the area occupied on the printed circuit board (PCB) by the silicon chip and auxiliary passive devices such as ac-coupling capacitors becomes more critical for the mobile applications, because the number of the required audio recording channels is increasing to enhance the audio quality by techniques such as echo cancellation and environmental noise cancellation [

1,

2].

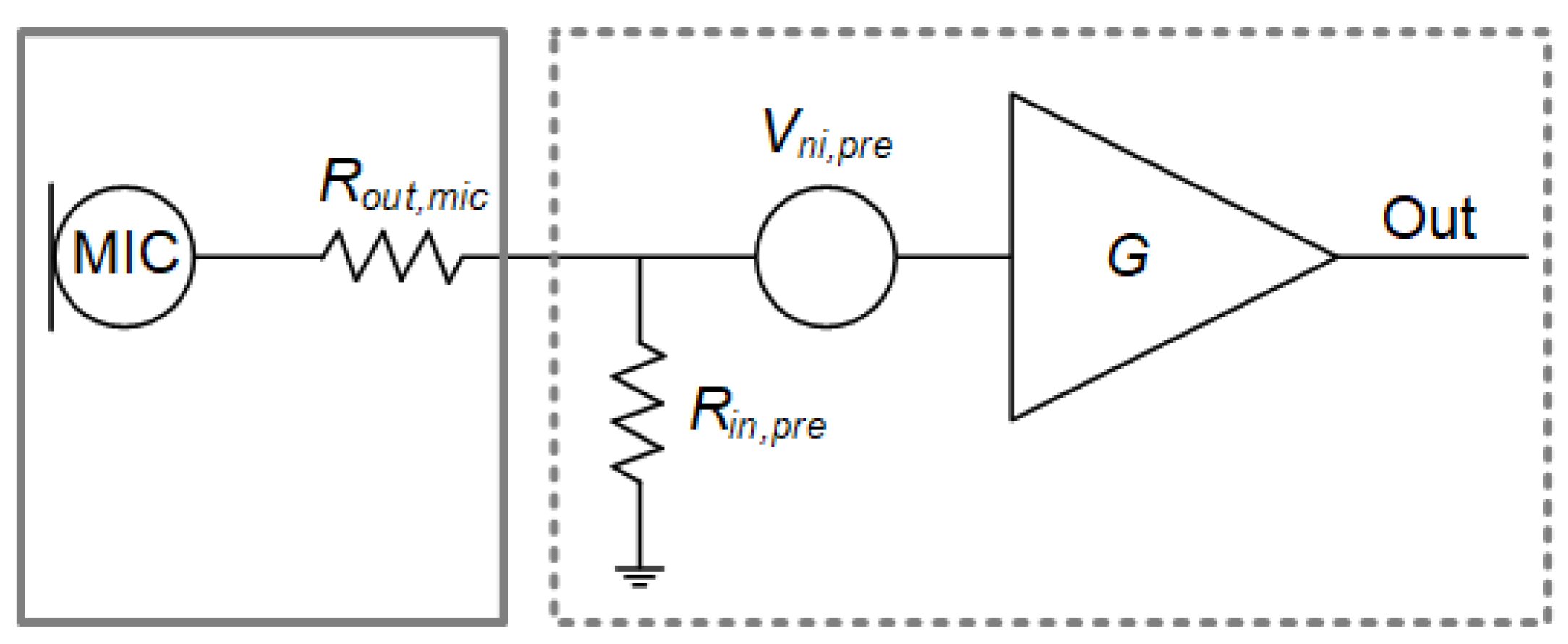

A microphone is a small sensor device that produces electrical signals from sound pressure. The electrical signals should be converted into digital signals by an audio ADC for the desired digital signal processing. However, the small amplitude of the microphone’s output signals, and the uncertain dc level of the output make it unpractical for a microphone to drive ADCs directly. Therefore, a preamplifier is usually used in an M-ROIC to handle such obstacle [

3,

4,

5,

6,

7,

8].

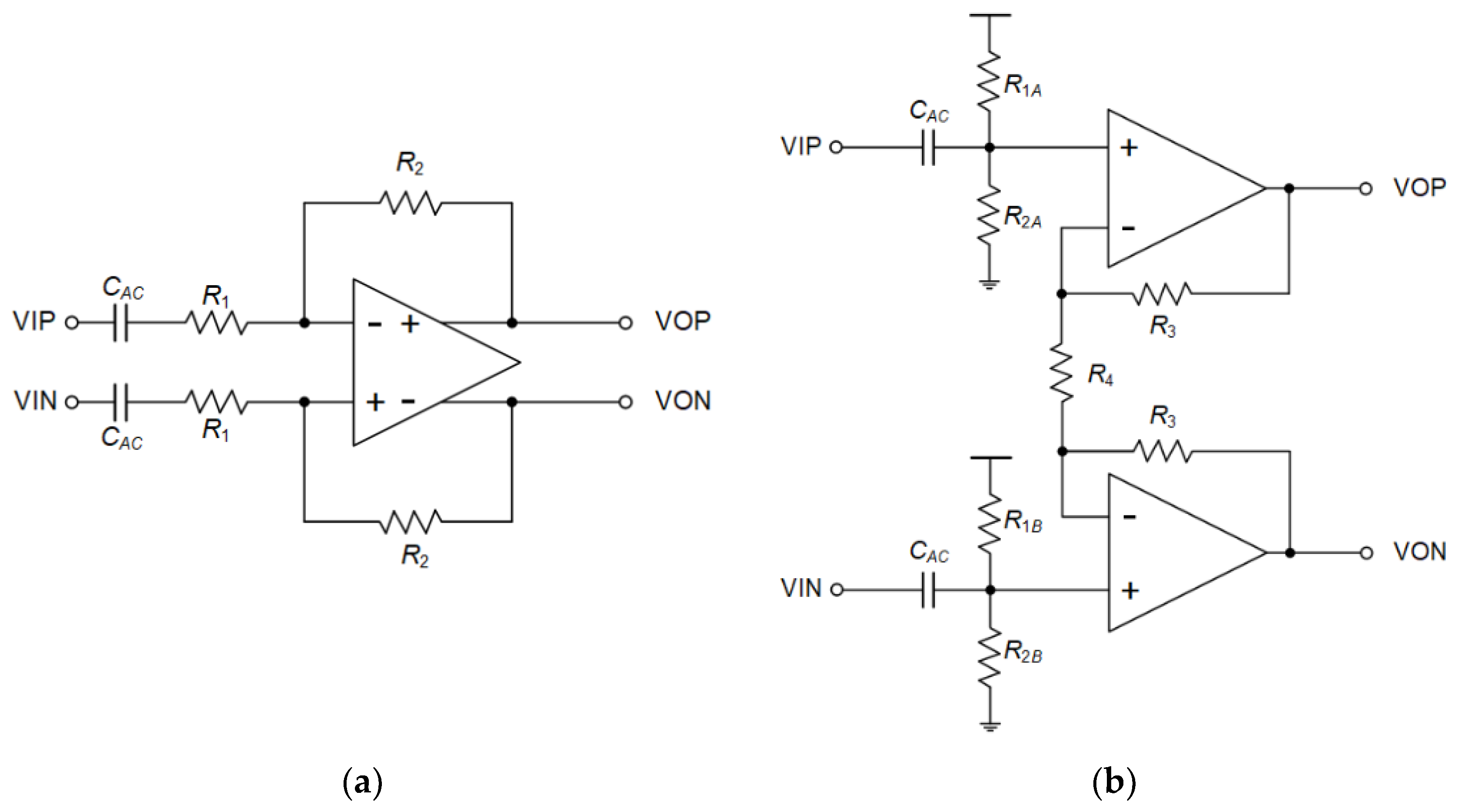

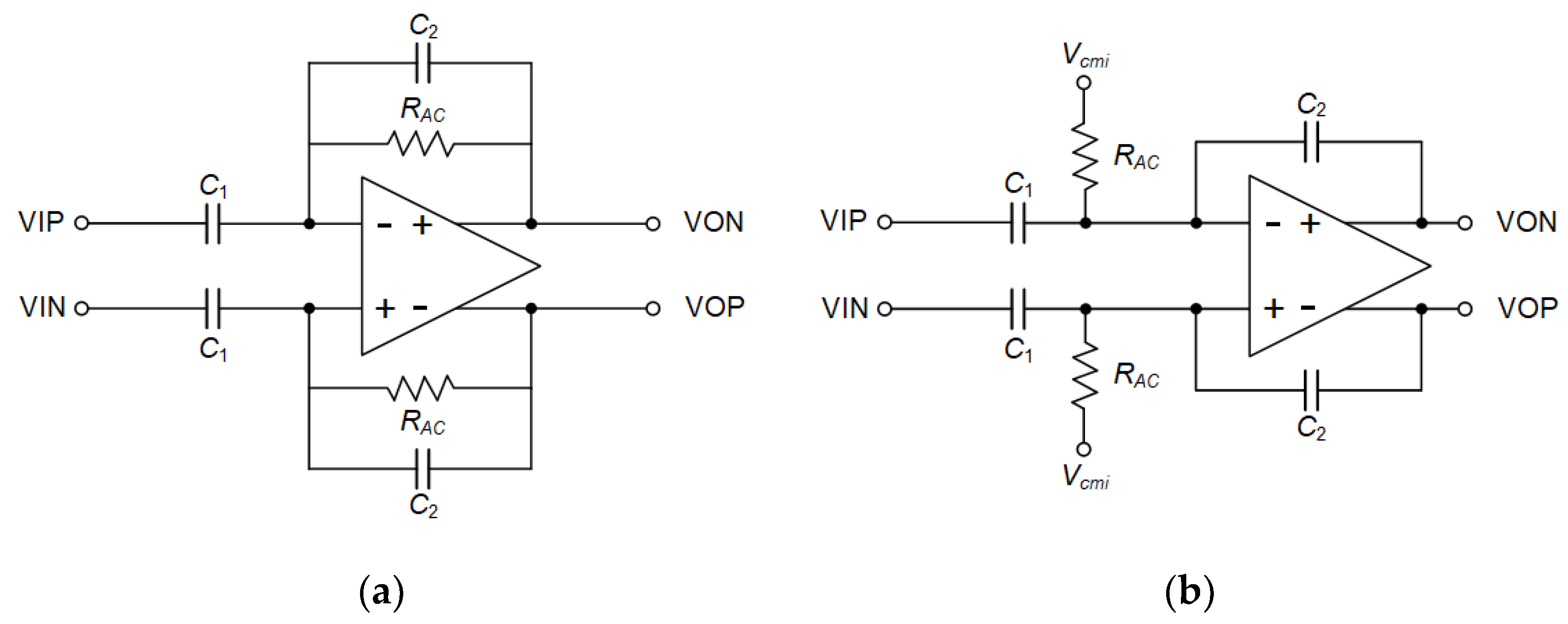

Microphones have non-zero output resistance, which is usually in the kilo-ohms range. This dictates that the preamplifier should have a large input impedance to avoid the reduction of the effective gain. There are a variety of preamplifier structures that aim for different performances, and each of them has different drawbacks. For example, inverting an amplifier with resistive feedback can achieve over 100 dB dynamic range (DR). However, the required noise level for the SNR limits the input impedance of the preamplifier, which leads to effective gain reduction [

3,

4,

5,

6]. Moreover, typical resistive feedback architectures require large off-chip ac-coupling capacitors to obtain a lower cut-off frequency of less than 20 Hz, which is undesirable in mobile applications requiring a very small footprint.

This paper presents a high performance programmable-gain microphone preamplifier with on-chip ac-coupling capacitors for driving an audio ADC. The preamplifier adopts an inverting architecture with capacitive feedback because of its large input impedance. Pseudo-resistors with very large resistance were employed to realize ac-coupling with on-chip capacitors of practical size. The proposed preamplifier was designed and fabricated in a 28 nm CMOS process. The designed preamplifier shows peak SNR of 107 dBA, peak SNDR of 95.5 dBA, DR of 107 dB, and the power consumption of 270 μW at 1.8 V supply voltage.

The rest of this paper is organized as follows: In

Section 2, the optimum preamplifier architecture for the mobile applications is selected after reviewing previously reported architectures, and the method to implement very large resistance needed for on-chip ac-coupling is proposed. In

Section 3, detailed circuit level descriptions along with simulation results are presented. The measurement results of the fabricated chips are reported in

Section 4 and the conclusions are given in

Section 5.

3. Circuit Level Design

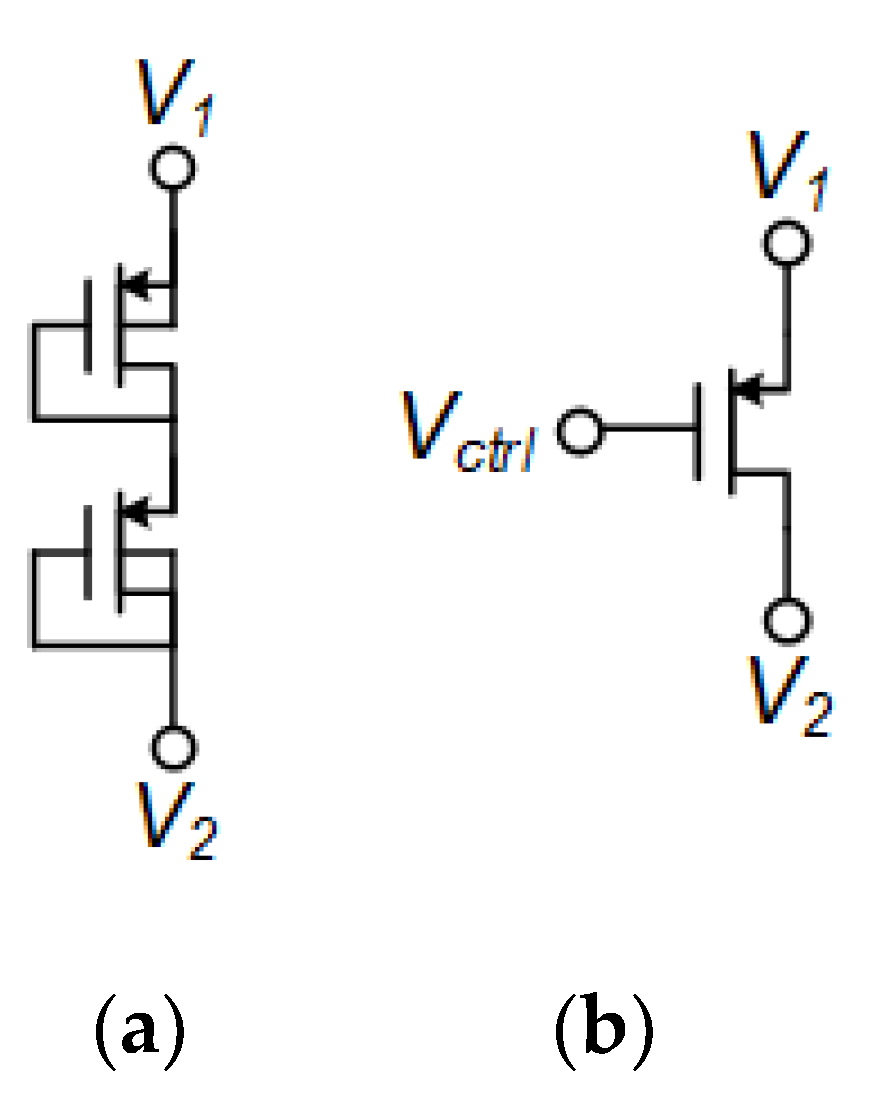

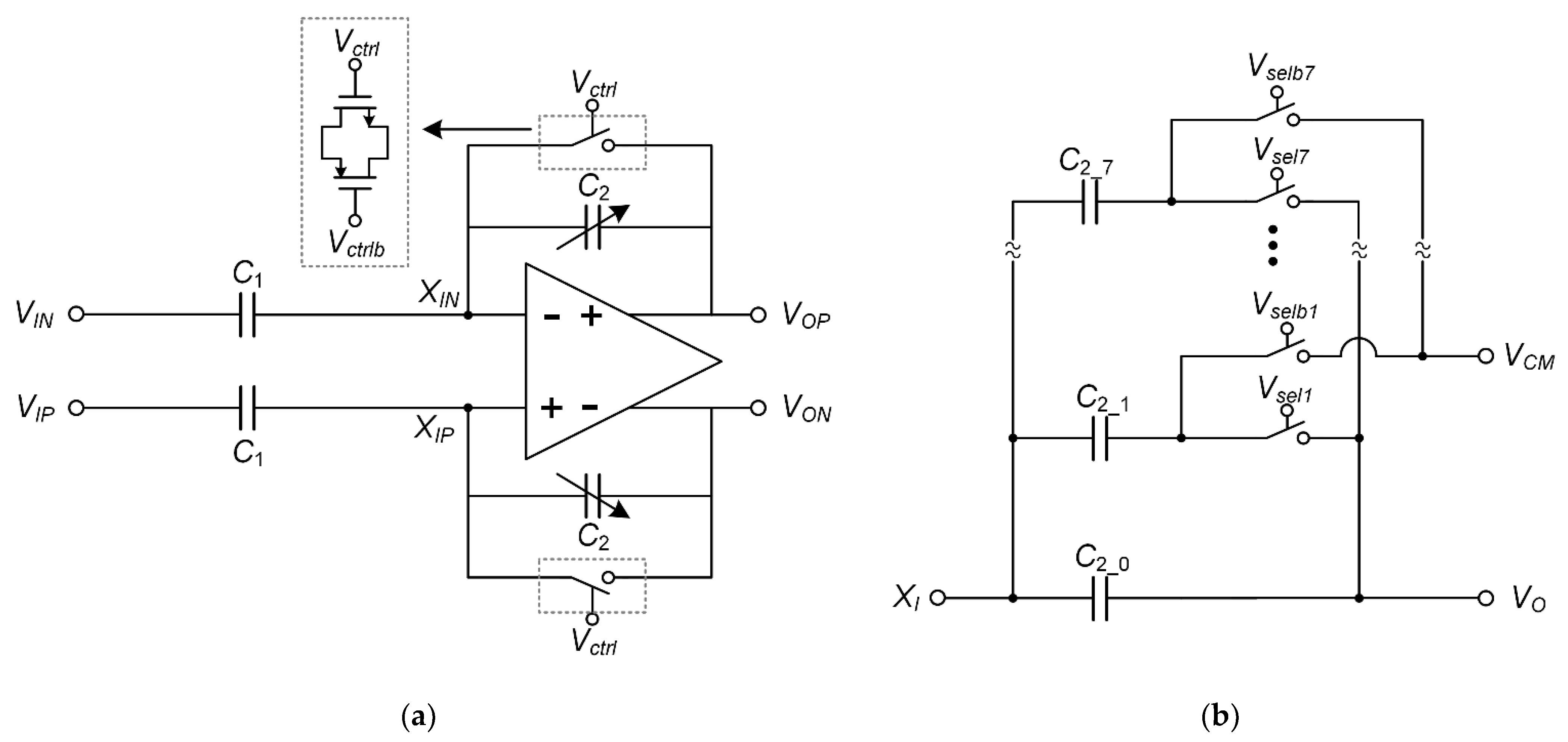

Figure 6a shows the architecture of the proposed microphone preamplifier. The switches are off during the normal operation of the preamplifier (

Vctrl = 0), and they are turned on for a short period of time during the start-up (

Vctrl =

VDD). To reduce the nonlinear characteristics of the switches, the switches are realized as CMOS transmission gates, where the NMOS and PMOS have same size of W/L = 0.25 μm/0.15 μm. It can also reduce the charge injection when the switches are being turned off.

In this preamplifier, the gain is determined by

C1/

C2.

Figure 6b shows the array of capacitors, out of which we select certain sub capacitors to get a desired

C2. When designing the switching of sub capacitors, we need to consider the preamplifier output change at the gain-switching moment. If the output voltage does not change instantaneously to the new value that is proper for the new gain, this will lead to an offset in the differential output. Although this offset is eventually removed by the charge flow through

RAC, it takes a very long time because of very large

RAC. In the proposed scheme shown in

Figure 6b, the top plates of the sub-capacitors (

C2i) are always connected to the virtual ground (i.e., OTA input), while the bottom plates are switched between the preamplifier output node and the common-mode voltage. When the preamplifier gain is increased, the bottom plates of the selected sub capacitors are switched from the output to the common-mode voltage. Then, the charge stored in those capacitors moves to the capacitors whose bottom plate is still connected to the output node. This increases the output voltage to the level which is proper for the new gain. When the gain is lowered, the bottom plates of the selected sub capacitors are switched from the common-mode voltage to the output voltage. Then, the charge redistribution between the sub capacitors instantaneously lowers the output voltage to the level proper for the new gain. Note that before the switching, the capacitor whose bottom plate is switched from the common-mode output to the output node was fully discharged.

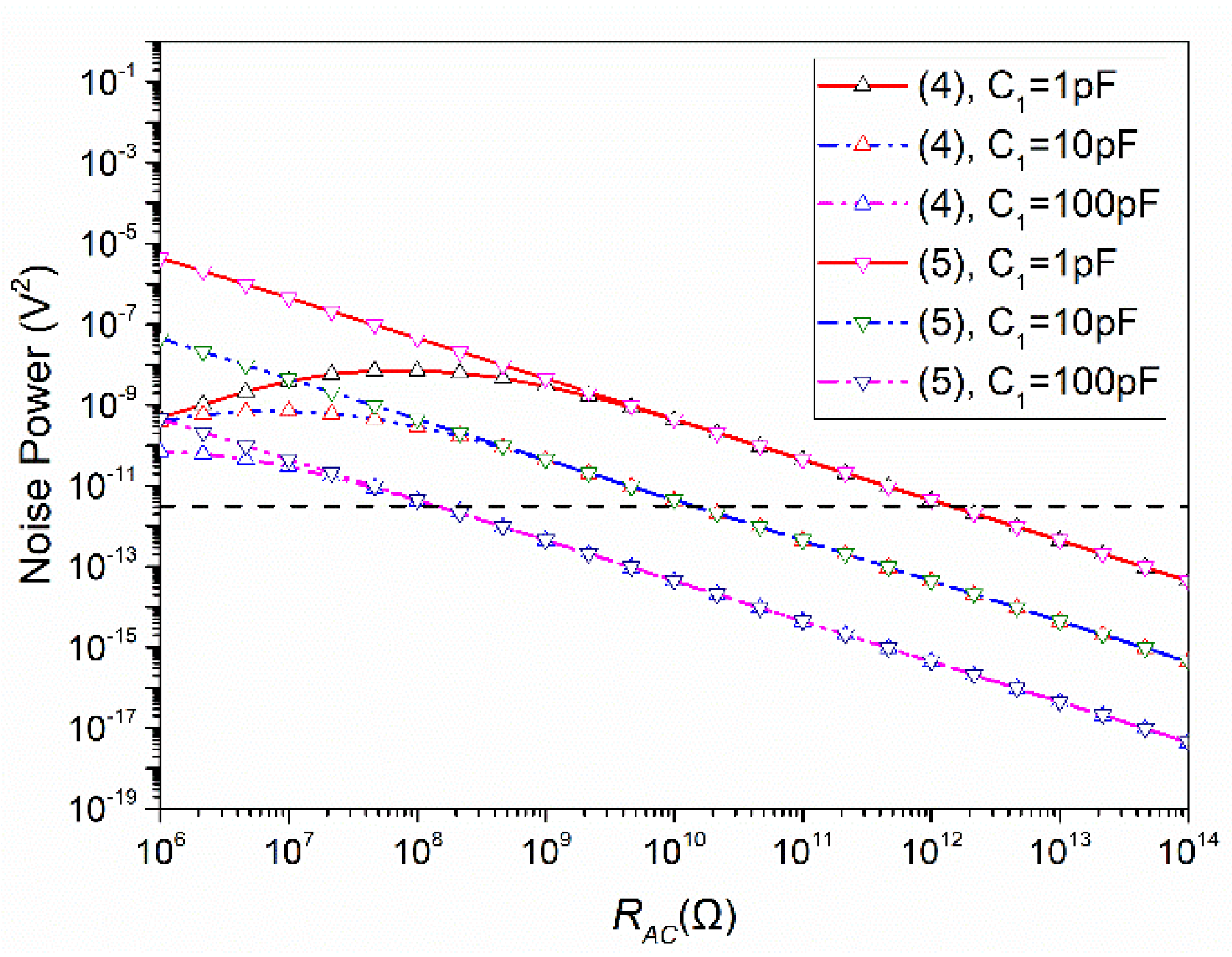

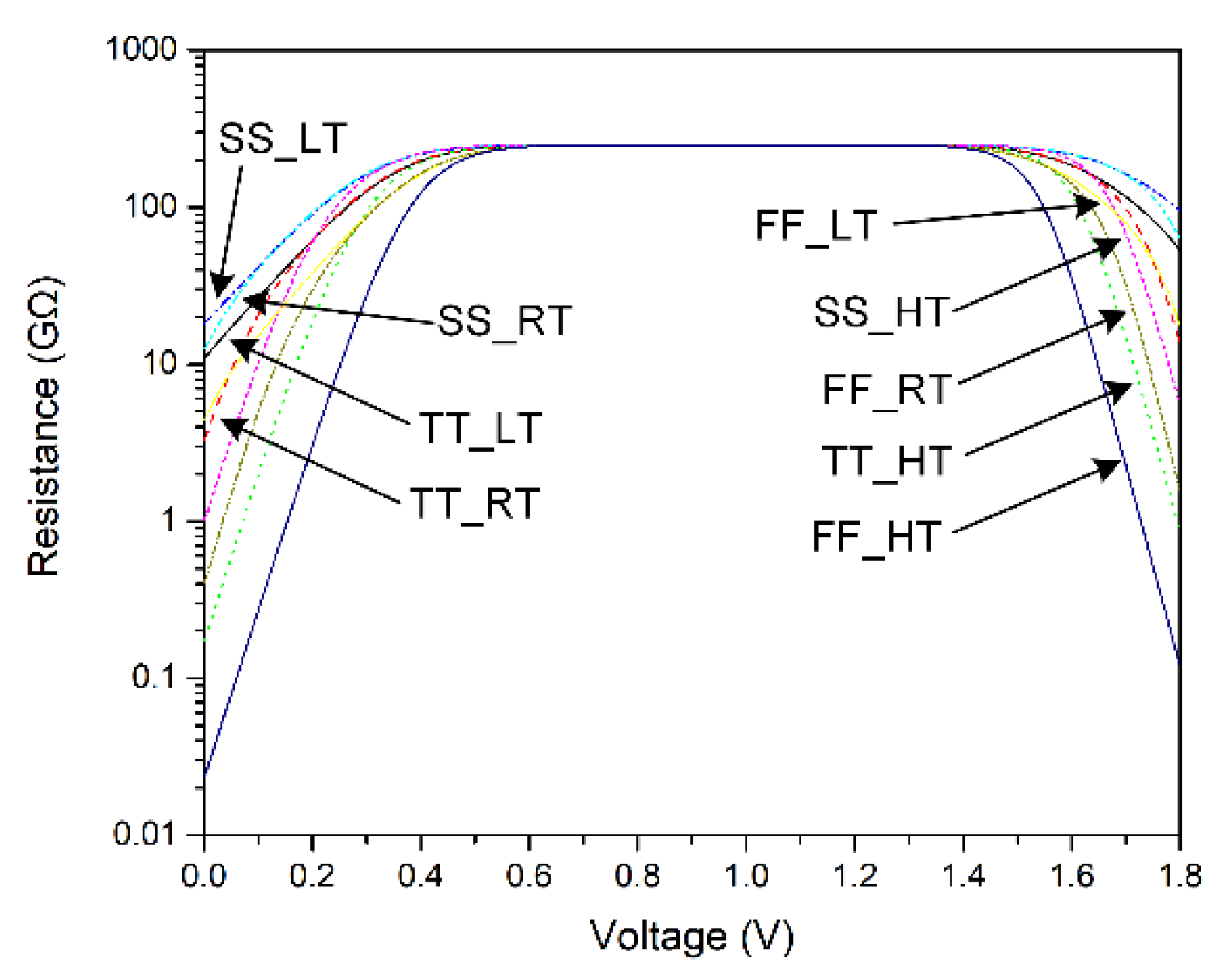

Figure 7 shows the simulated resistance of the pseudo-resistor. One of the terminals is connected to the common mode voltage of 0.9 V and the voltage of the other terminal is swept from 0 V to 1.8 V. A concern when using pseudo-resistors is the variation of the resistance. Therefore, we repeated simulations at three process corners (TT, FF, SS) and three temperatures (T = 25 °C, 27 °C, 85 °C). From

Figure 7, we observe that in the off-state the resistance is about 250 GΩ regardless of the corner condition or the temperature, while it is affected by the conditions in the on-state or the sub-threshold range. We attribute this to the limitation of the PDK. Having admitted the limitation, we can still confirm that the resistance stays larger than 10 GΩ for 0.3 V < V < 1.6 V. Note that in the region where we become concerned about low resistance of the pseudo-resistor, the simulation results correctly predict corner-condition-and-temperature dependency. As mentioned above, when the voltage is between 0.6 V and 1.4 V, the resistance is about 250 GΩ. From the noise power discussion in the previous section, we observed that this value of resistance along with

C1 = 10 pF could be used to limit the noise power to below

N1 = 3.2

10

−12 V

2, which is 10% of the total noise budget. However, we also note that 250 GΩ is not large enough to be used with

C1 = 1 pF to satisfy the same noise requirement.

The preamplifier gain is programmable from 0 dB to 21 dB with 3 dB steps. To keep the input impedance constant for all gain settings, C1 was fixed at 10 pF and C2 was made programmable by selecting the desired capacitor from capacitor arrays.

It is important to select a proper OTA architecture to achieve the desired performance. For example, a telescopic architecture can be selected when a high gain OTA is required. If the supply voltage is low, an OTA with current source level shifting technique [

16] or an OTA with an active load with cross-coupled bulk [

17] can be selected. In our work, we adopted a two-stage pseudo class-AB OTA to realize a power efficient low noise OTA.

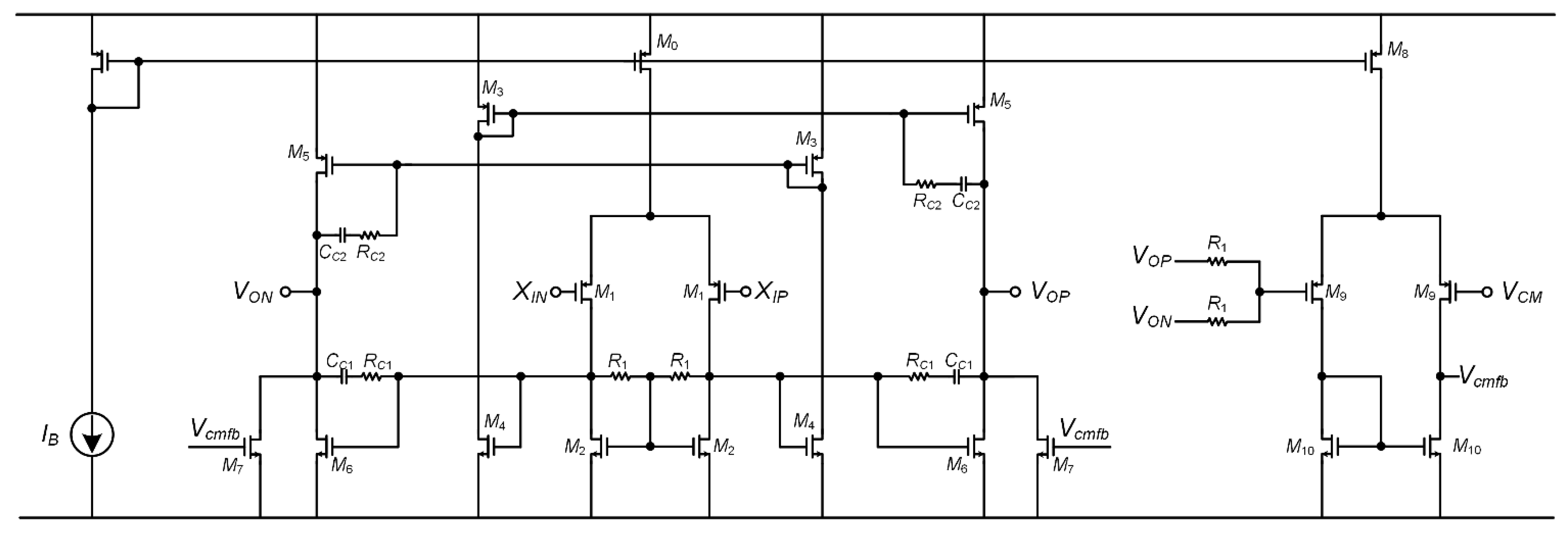

Figure 8 shows the schematic diagram of the OTA used in this work. The OCML of the first stage is stabilized by the resistor

R1. A large resistance of

R1 = 1 MΩ is used to prevent the open-loop gain reduction. The OCML of the OTA is stabilized by a common-mode feedback (CMFB) circuit employing a simple differential pair. The bias current

IB was copied from the reference current that was generated by a conventional constant-gm circuit.

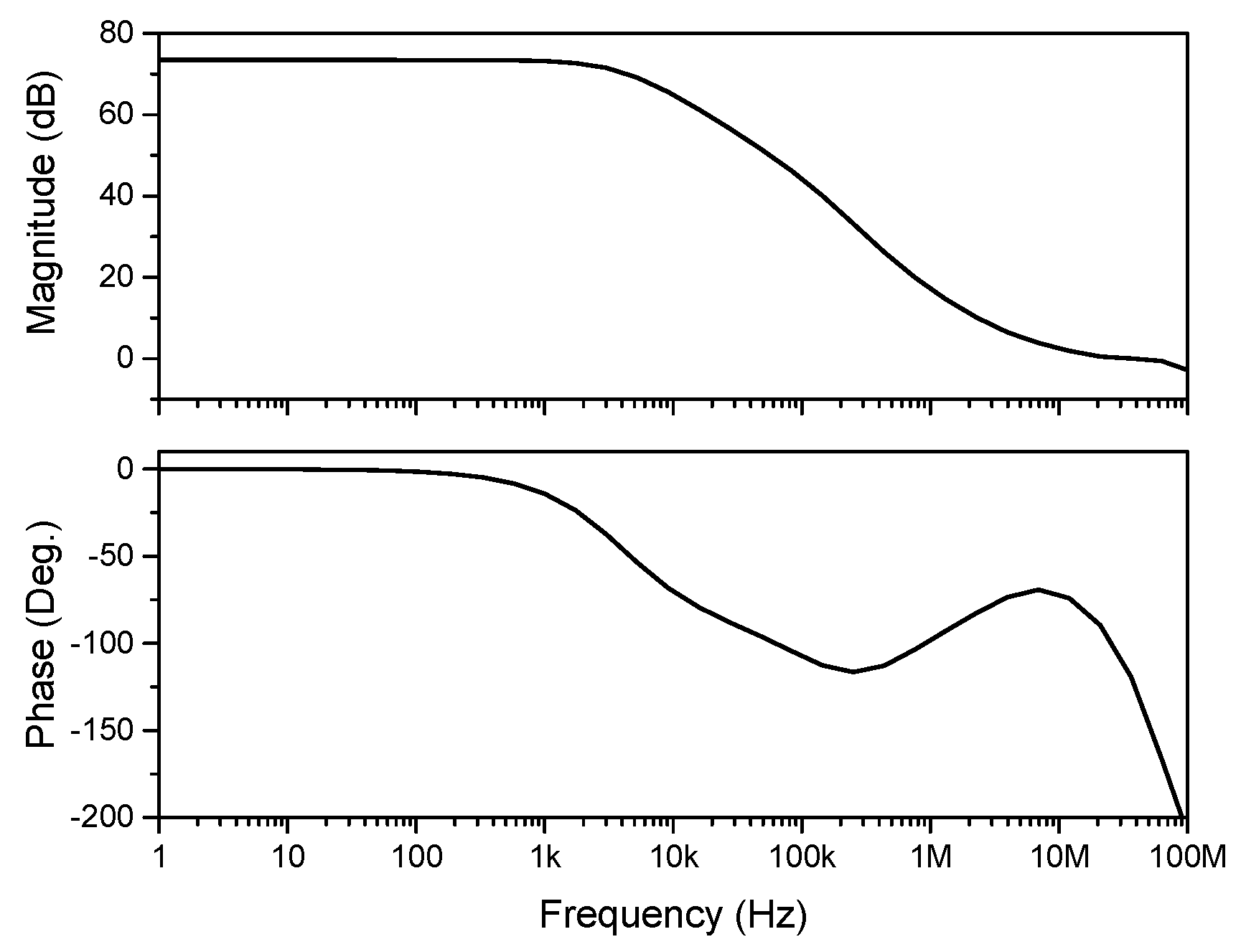

Figure 9 shows the AC simulation result of the OTA with the 10 kΩ load resistance. From the simulation, we observe that the loop gain and the phase margin are 73.4 dB and 61°, respectively. The size of the devices in the OTA is listed in

Table 2. To reduce the flicker noise, we used large input transistors (

W1/

L1 = 1664 μm/3 um) and to minimize the thermal noise,

gm2/

gm1 was made small. Note that the large

M1 and

M2 lower the bandwidth of the OTA due to its large parasitic capacitances at the output nodes of the first stage. However, the large trans-conductance of the OTA required for a good SNR already leads to a unity-gain bandwidth much larger than the 20-kHz bandwidth of a microphone amplifier. Therefore, the large parasitic capacitance does not become a problem in our design.

The simulated A-weighted input-referred noise of the OTA in the signal bandwidth of 20 Hz < f < 20 kHz was 1.3 10−12 V2, where the contribution by the thermal noise and the flicker noise were 40% and 60%, respectively. All transistors operate in the saturation region except for M1, which operates in the weak inversion region because of its large W/L ratio to obtain a large gm1.

The AC noise simulations of the pre-amplifier indicates that the total output noise is 2.2 × 10

−11 V

2 (A-weighted) when the preamplifier gain is 0 dB. Of the total noise, the thermal noise and flicker noise contribution are 1.2 × 10

−11 V

2 and 0.96 × 10

−12 V

2, respectively. This corresponds to an A-weighted SNR of 101.6 dB. The noise from the pseudo-resistor is less than 1% of the total noise.

Figure 10 shows the output spectrum obtained from the transient noise simulation of the proposed preamplifier with the gain of 0 dB with a 4.3 kHz, 800 mV

pk,diff balanced input signal. From the result, we obtain the SNR and SNDR of 101.4 dB (A-weighted) and 94.7 dB (A-weighted), respectively.

Figure 11 shows the results of the transient simulations of the preamplifier to observe the start-up behavior. The supply voltage is ramped up from 0 V to 1.8 V with a rising time of 1 μs at

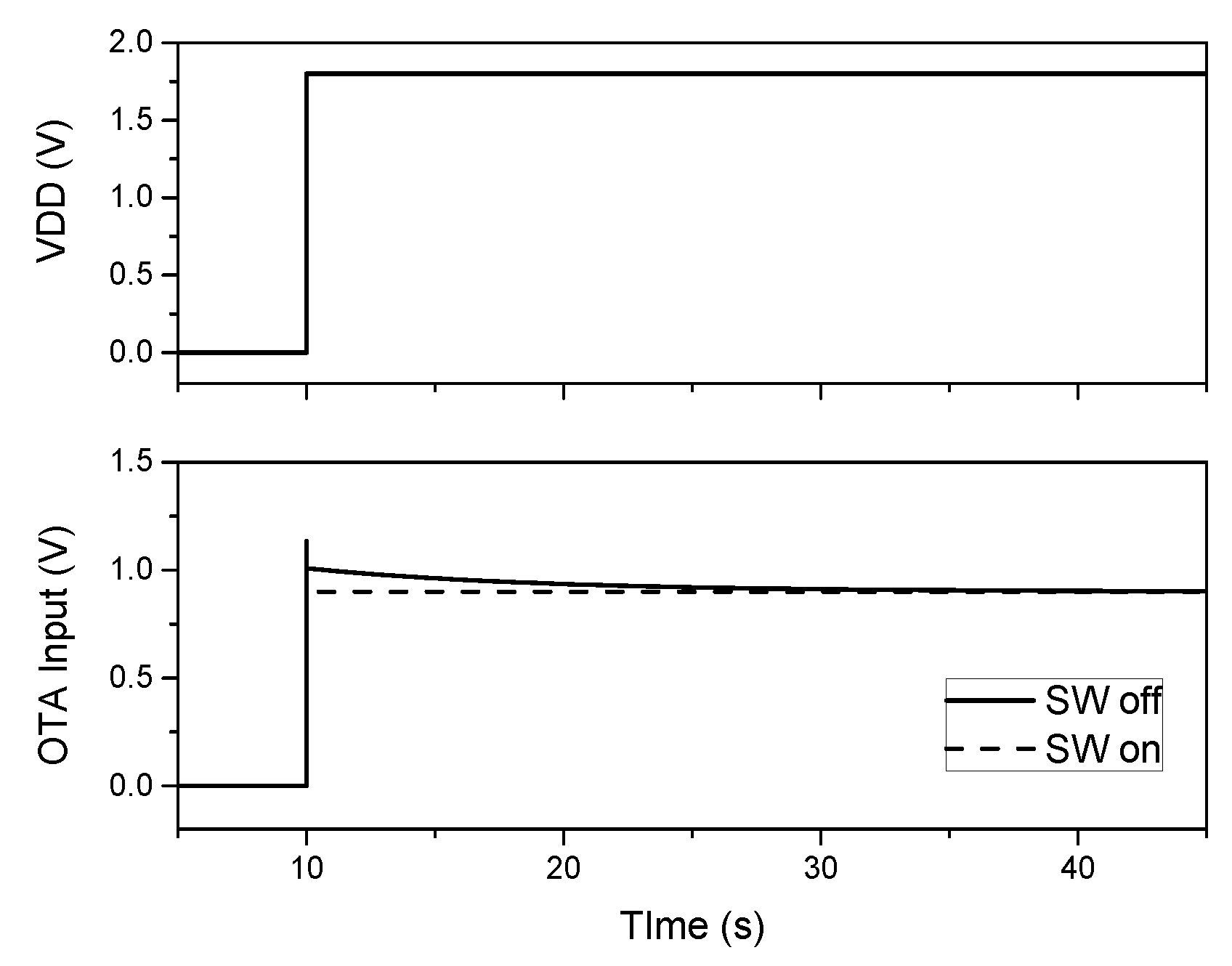

t = 10 s. When the switches stay off and behave as pseudo-resistors, the settling of the OTA input nodes is very slow, and the required settling time was tens of seconds. However, if the switch is turned on, the input node voltage of the OTA is stabilized very quickly with settling time of tens of microseconds.

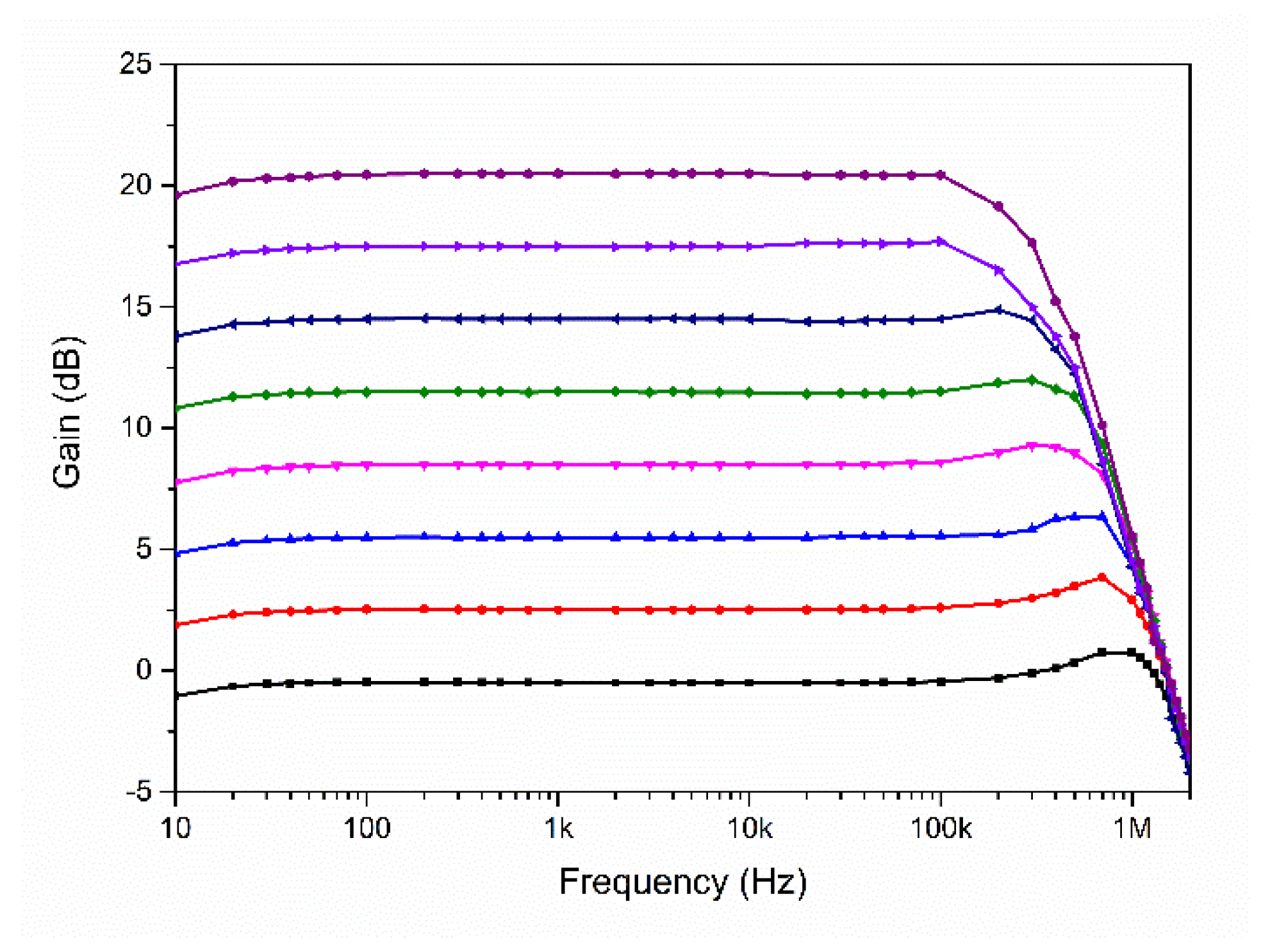

Figure 12 shows the frequency response of the preamplifier for all gain settings obtained from ac simulations. From the results, we observe that the lower cut-off frequency is lower than 1 Hz for all gain settings. In addition, we can observe flat frequency response over the audio bandwidth between 20 Hz and 20 kHz. In fact, the lower and upper 3 dB frequency of the frequency response is much lower than 20 Hz and higher than 20 kHz, respectively. The high upper 3 dB frequency is the result of a very large trans-conductance of the OTA, which is needed for a high SNR performance. When the upper 3 dB frequency is higher than necessary, a concern is that the noise in the extra bandwidth is aliased down to the signal band when sampled by a down-stream ADC and the SNR is degraded. However, in this work, we assumed an oversampling ADC with a large oversampling ratio, which is usually used for audio applications. In this case, the aliasing can be avoided and the noise in the extra bandwidth can be safely removed by a low-pass filtering decimation filter. The very low lower 3 dB frequency is the result of a very large

RAC. As explained in

Section 2.3, a large

RAC is actually beneficial because it reduces the total noise in the signal band. Because the large resistance could be obtained easily using pseudo-resistors, we did not try to increase the lower 3 dB frequency.

4. Measurement Results and Discussion

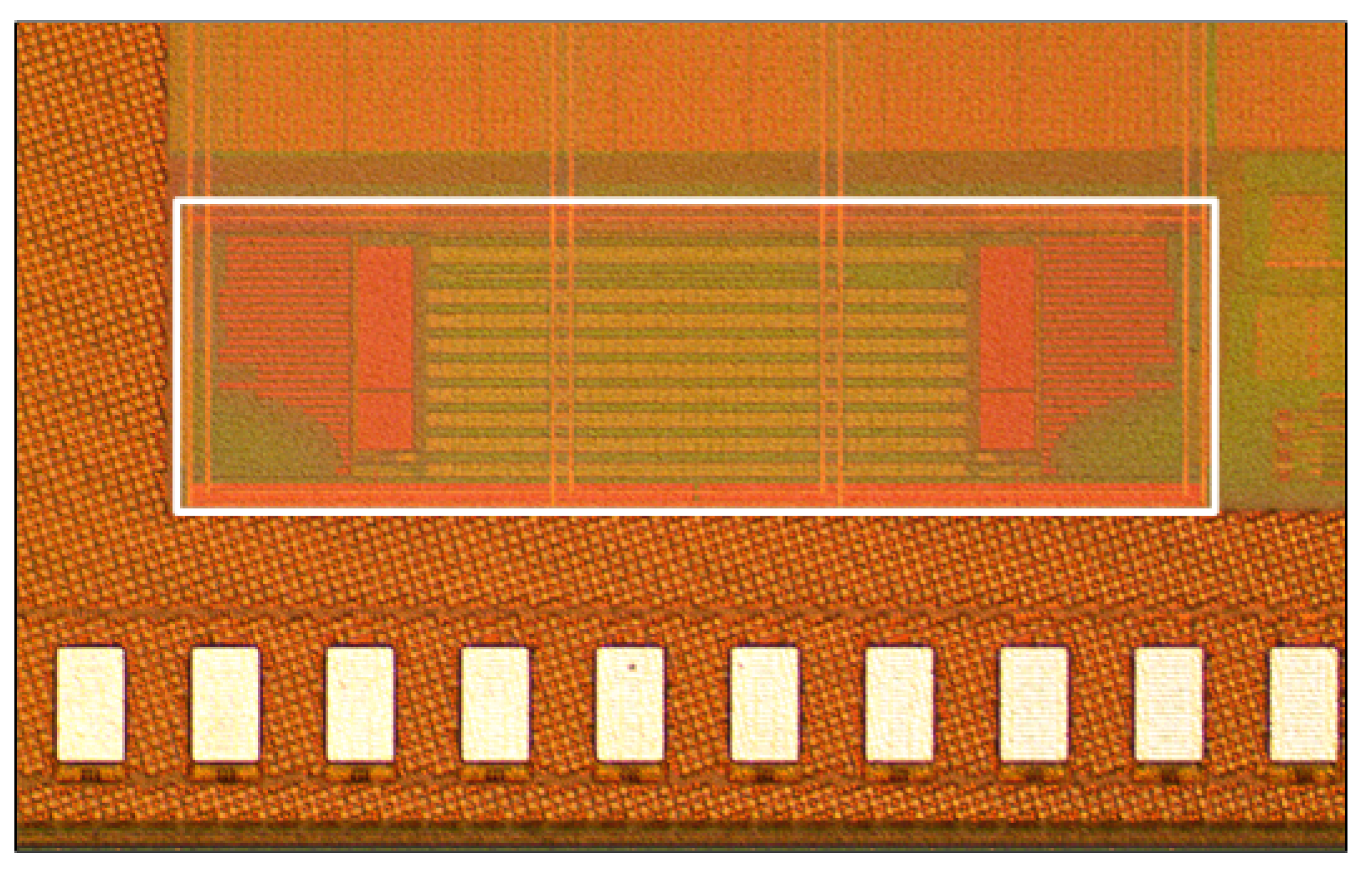

The proposed preamplifier was fabricated using a 28 nm CMOS technology.

Figure 13 shows the chip microphotograph of the fabricated circuit. The white rectangle in

Figure 13 indicates the preamplifier and the active area occupied by the preamplifier is 0.19 mm

2.

Figure 14 shows the frequency response with the balanced input signal with 1.8 V supply for all gain settings measured with an Agilent 81160A function generator and an Agilent MSO9104A oscilloscope. The measured data matches the simulation results of

Figure 12 well, and very flat frequency responses were obtained in the audio band. The small reduction of gain in the low frequency range is from the limit of the measurement system, and the slight peaking at around 1 MHz is from the interaction of the large input capacitance of the measurement system and the output impedance of the preamplifier.

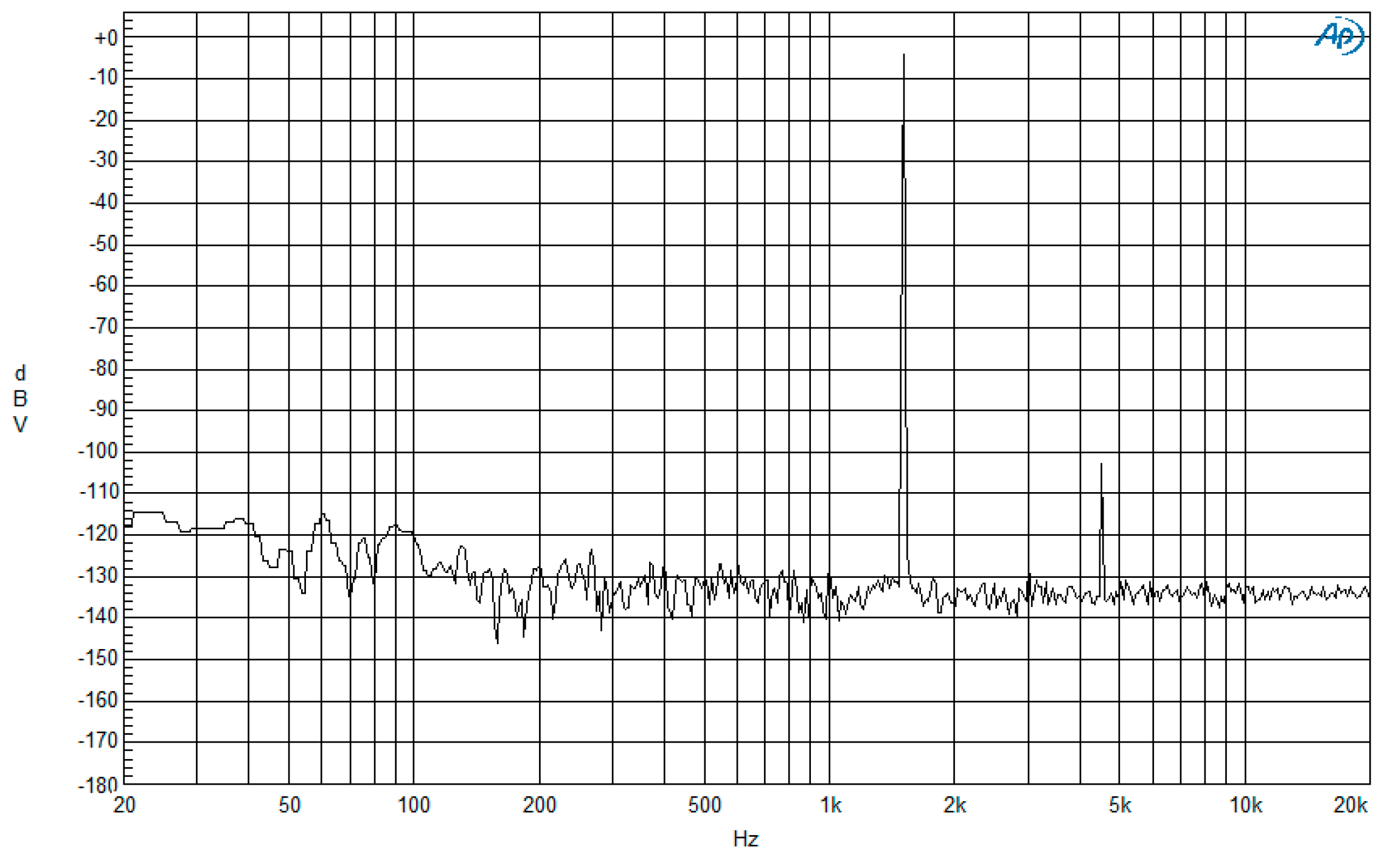

Figure 15 shows the output power spectrum of the preamplifier measured with the gain of 0 dB and 800 mV

pk, 1.5 kHz sinusoidal input supplied by an Audio Precision AP-2700. The single-ended output of AP-2700 was converted to a differential signal by a balun consisting of a center-tapped transformer before being applied to the preamplifier. The supply voltage was 1.8 V. From the results, we can observe that the corner frequency of flicker noise is about 200 Hz due to the OTA’s large input transistors. The third order distortion is the dominant distortion component whose power is about 100 dB lower than the signal power. The powers of other harmonic components are lower than the signal power by more than 120 dB and is buried in the noise.

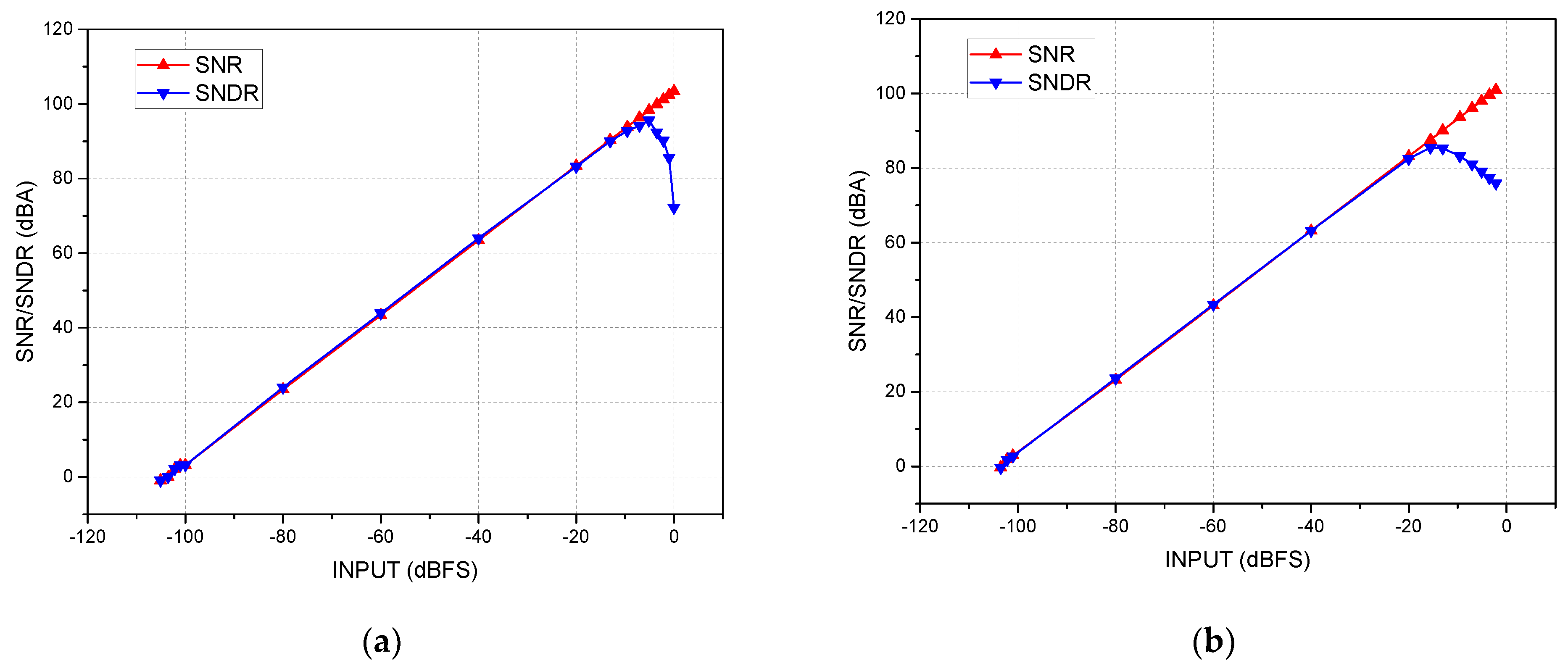

Figure 16 shows the measured A-weighted SNR and A-weighted SNDR versus input level when (a) the balanced signal was applied and (b) the single-ended signal was applied. The maximum A-weighted SNR and A-weighted SNDR with the balanced signal were 107 dBA and 95.5 dBA, respectively. The measured DR of the preamplifier is 107 dB. Maximum SNRs were obtained at the input signal level of 0 dBFS (=1.8 V

pk,diff), which produces the maximum output swing of 1.8 V

pk,diff. With a single-ended signal applied, the peak A-weighted SNDR was reduced to 85.6 dBA mainly due to even-order harmonics. However, the SNRs with a single-ended signal is almost identical to those with balanced input signal.

The measured power consumption with the supply voltage of 1.8 V was 270 μW.

Table 3 summarizes measurement results of the preamplifier. In the table, we present A-weighted and unweighted SNR, SNDR, and DR for balanced and single-ended input signals with the gain of 0 dB and 21 dB. Comparisons with previously published results are provided in

Table 4. The power-efficiency is compared by employing the figure of merit (FoM) factor, which is defined as FoM = DR + 10log

10(Bw(Hz)/Power(W)). Since the gain of [

5] is fixed at 20 dB, the SNR, SNDR, DR, and FoM of [

5] was adjusted by adding the 20 dB gain for fair comparisons. From

Table 4, we can observe that our design represents comparable performance with the state of the art designs. Ref. [

5] reports the highest FoM among the comparisons. However, the resistive architecture of [

5] limits the input impedance to 10 kΩ, and it employed external ac-coupling capacitor. Our work, as well as [

8], both report capacitive on-chip ac-coupling preamplifiers. A pseudo-resistor was employed in our work to realize an on-chip ac-coupling, while switched capacitor networks were adopted as biasing resistors in [

8].