Low-Power Two-Phase Clocking Adiabatic PUF Circuit

Abstract

1. Introduction

2. Fundamental Adiabatic PUF

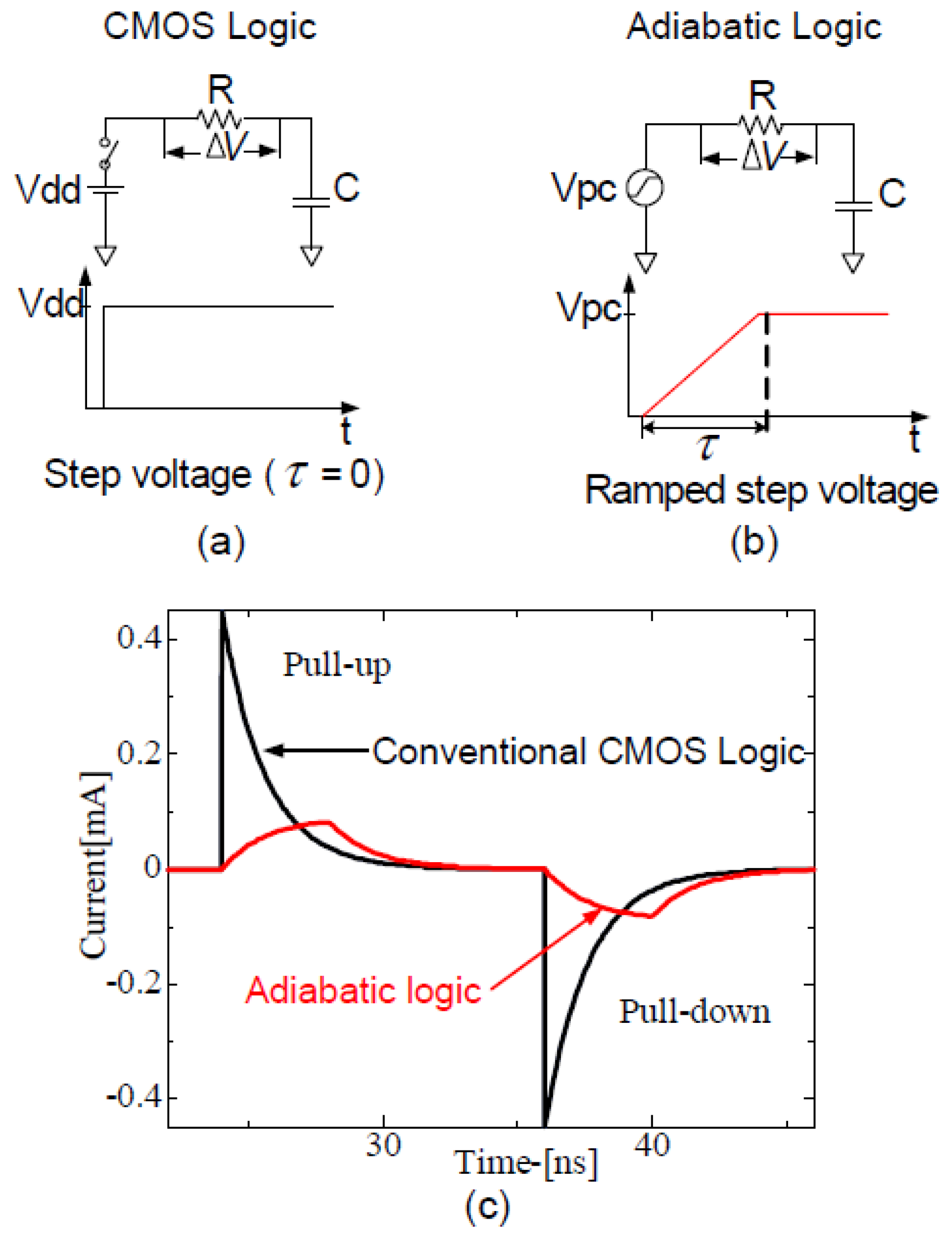

2.1. Principle of Adiabatic Switching

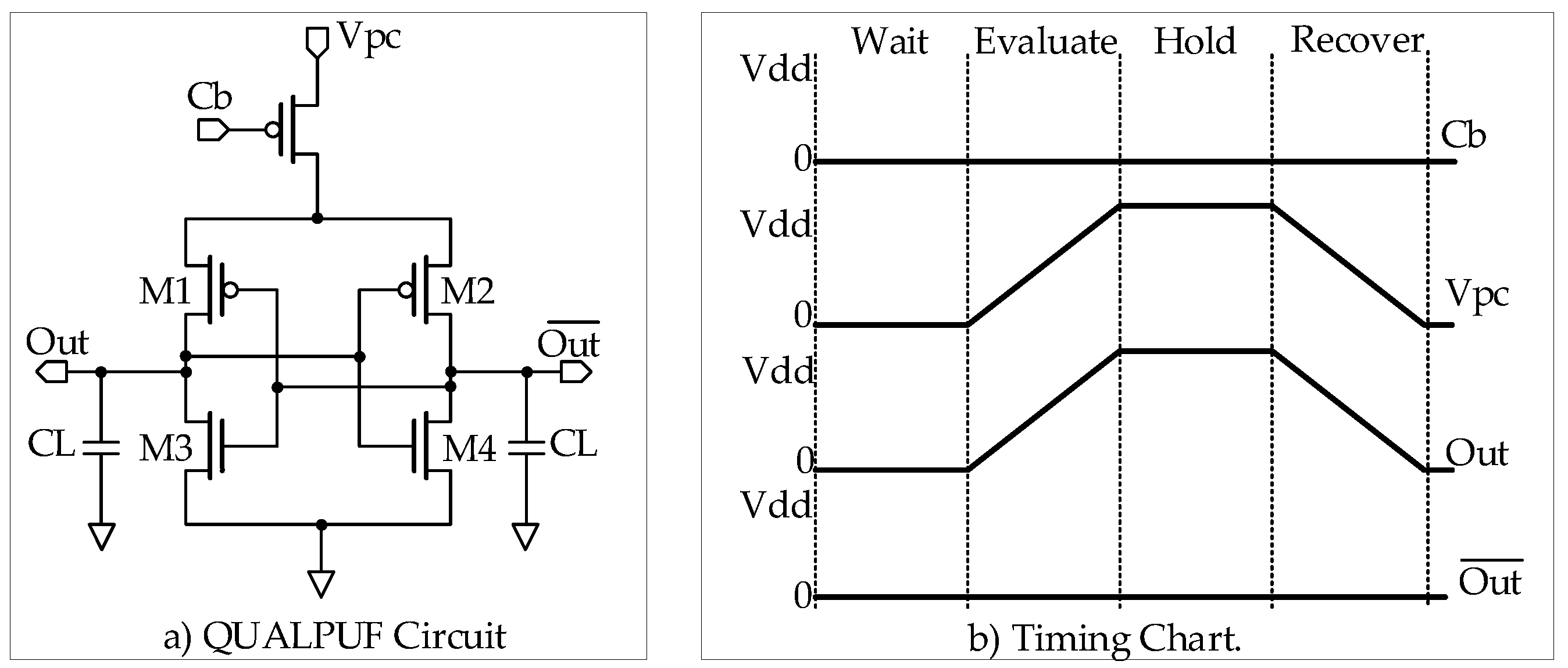

2.2. Conventional Adiabatic PUF

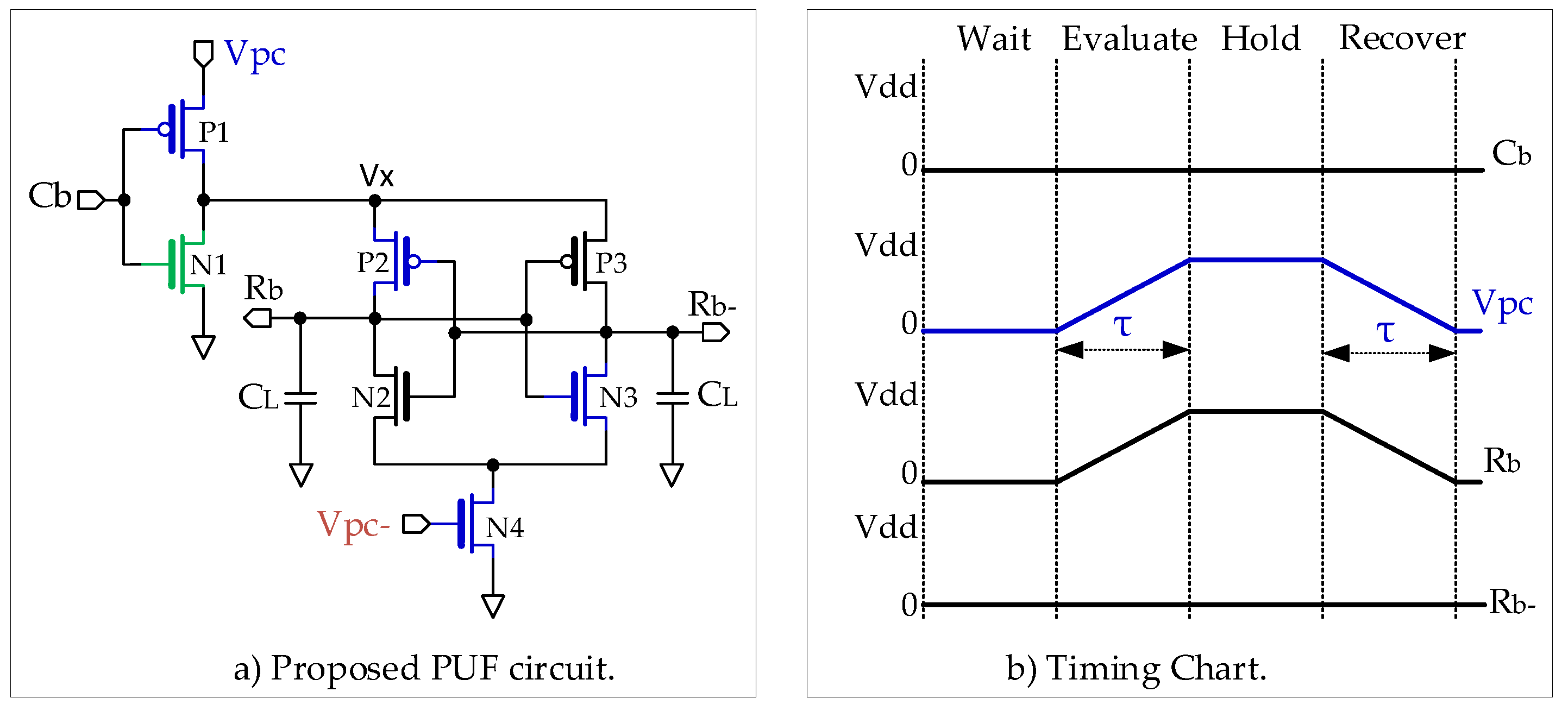

2.3. Proposed Adiabatic PUF

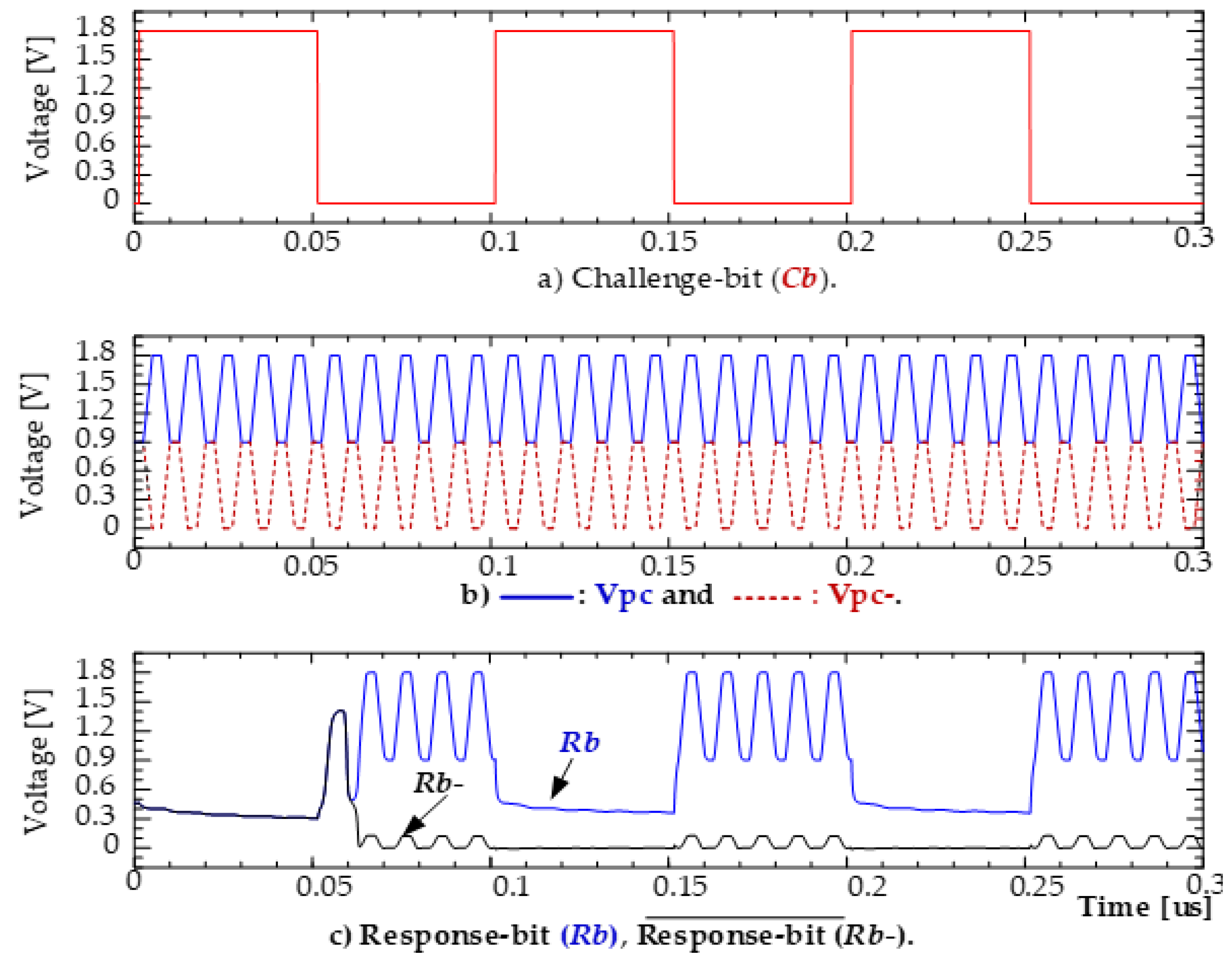

2.3.1. Operation of the Proposed Adiabatic PUF

- Wait Phase: During the wait phase, the power clock (Vpc) is at a constant level of 0.9 V. Therefore, the PUF cell will be in a waiting state during this phase.

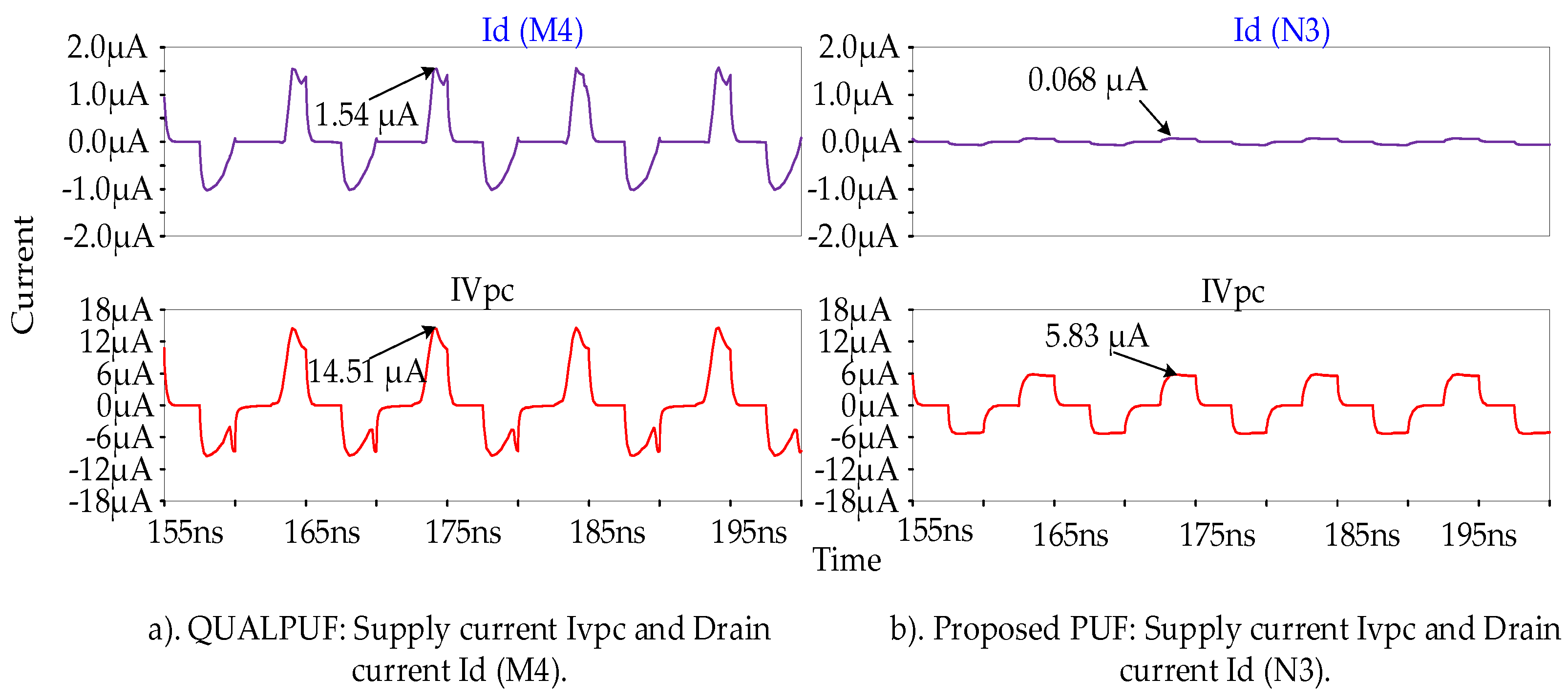

- Evaluate Phase: During the evaluate phase, Vpc slowly rises from 0.9 to 1.8 V (Vdd). Because Vpc is always greater than VTHP in our proposed Vpc signal, both P2 and P3 are turned ON. However, owing to the effect of different threshold voltages due to imperfections in the CMOS manufacturing process, one of the transistors (P2 and P3) with a lower threshold voltage will conduct first, thereby facilitating the corresponding load capacitor to quickly become charged. This will lead to a flip in the outputs where one of the outputs leads to logic “1” and the other to logic “0”. In this phase, the supply current IVpc flows through P1 and P2 to charge the Rb node capacitor, as shown in Figure 3a.

- Hold Phase: During the hold phase of the Vpc, the proposed adiabatic PUF generates a stable PUF response.

- Recover Phase: During the recovery phase of the Vpc, the time ramp voltage slowly decreases from Vdd to 0.9 V. During this phase, the charge stored in the load capacitor is slowly recovered back to the power clock supply through P1 and P2 transistors. Moreover, the response bits will remain stable because the low level of Vpc is 0.9 V, which is always higher than the VTH of both NMOS and PMOS transistors. Hence, the Rb node maintains logic “1”, which triggers transistor N3 to stay always ON and pull-down Rb- node to ground level through transistor N4 once Vpc- is higher than VTHN.

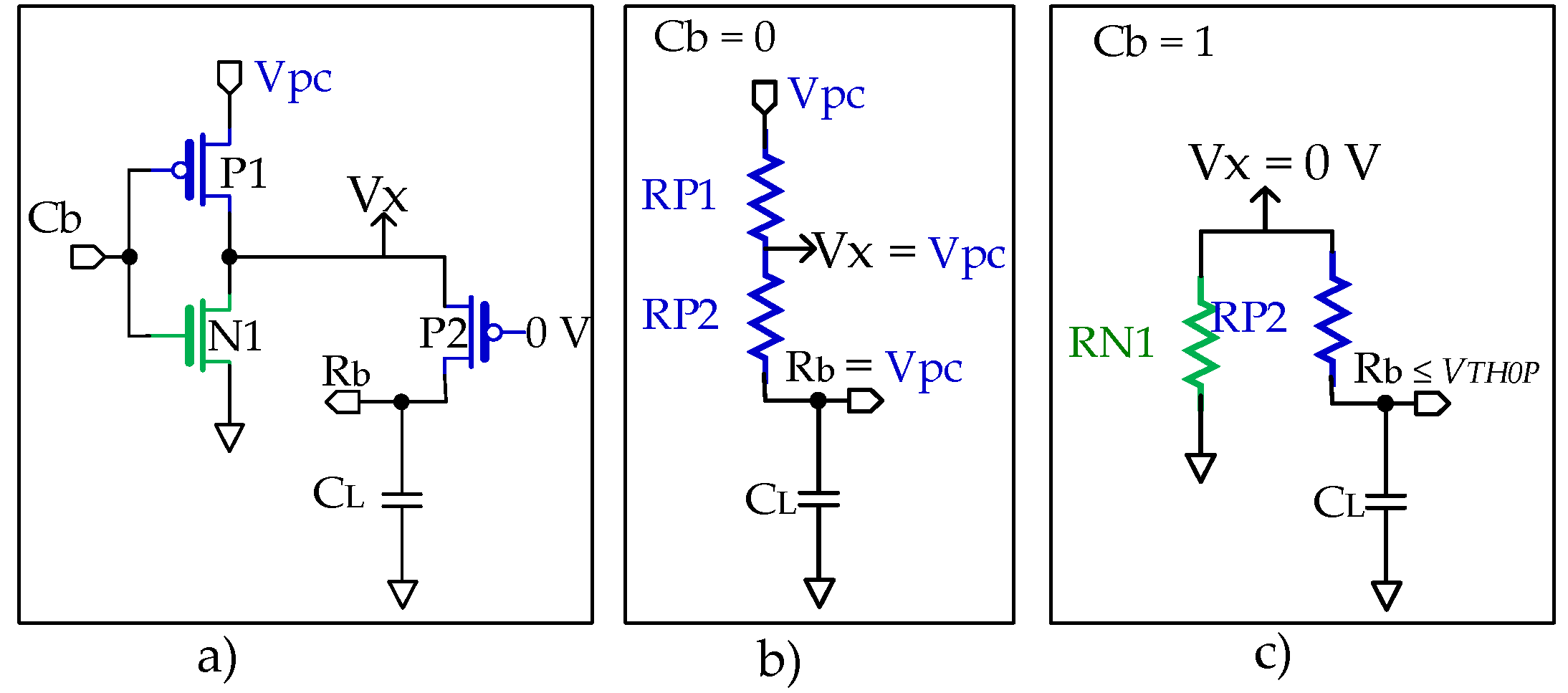

2.3.2. Theoretical Analysis of the Proposed Adiabatic PUF

3. Design of 4-Bits Adiabatic PUF

4. Simulation and Results

4.1. Simulation Condition

4.2. Simulation Result

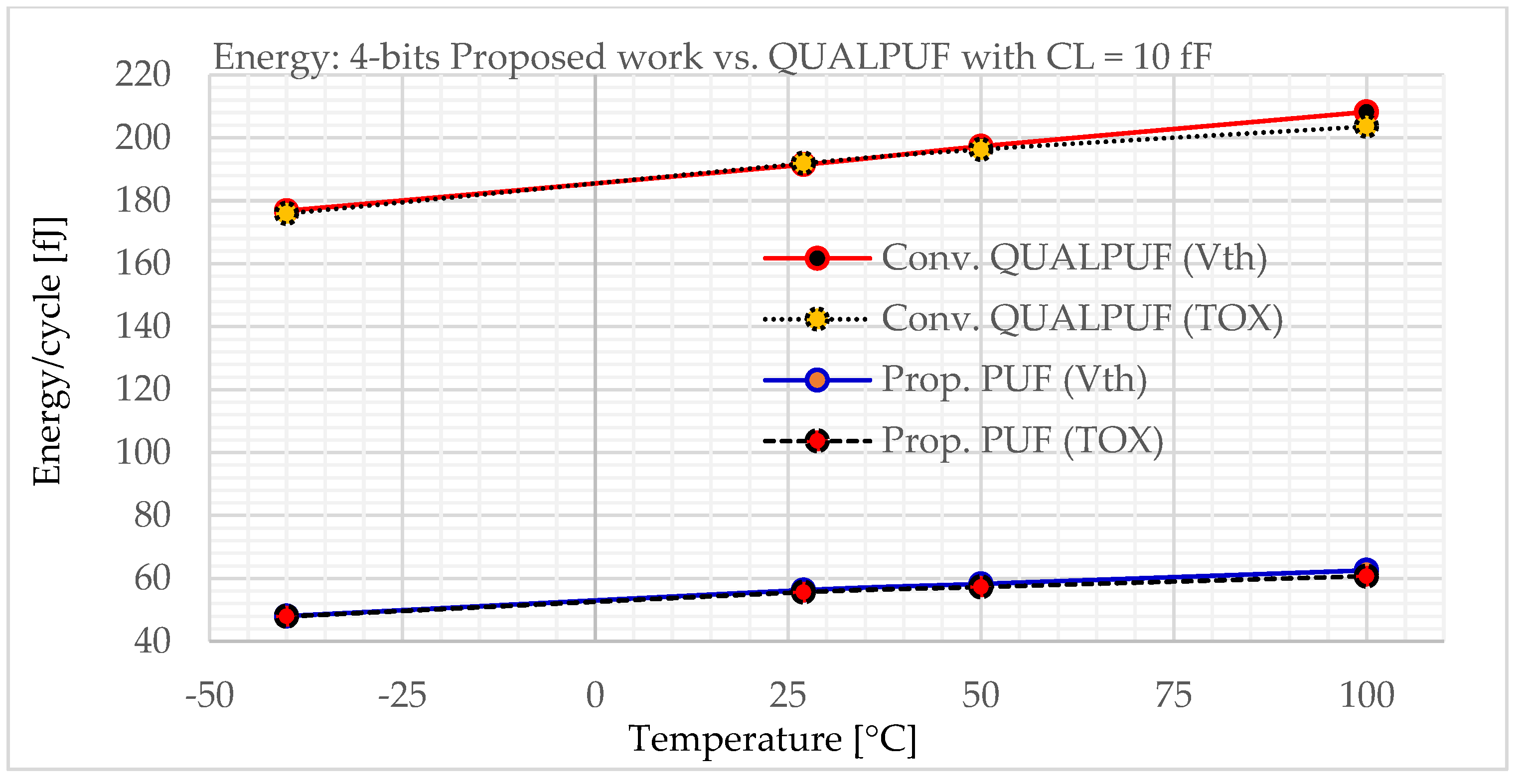

4.2.1. Energy Dissipation

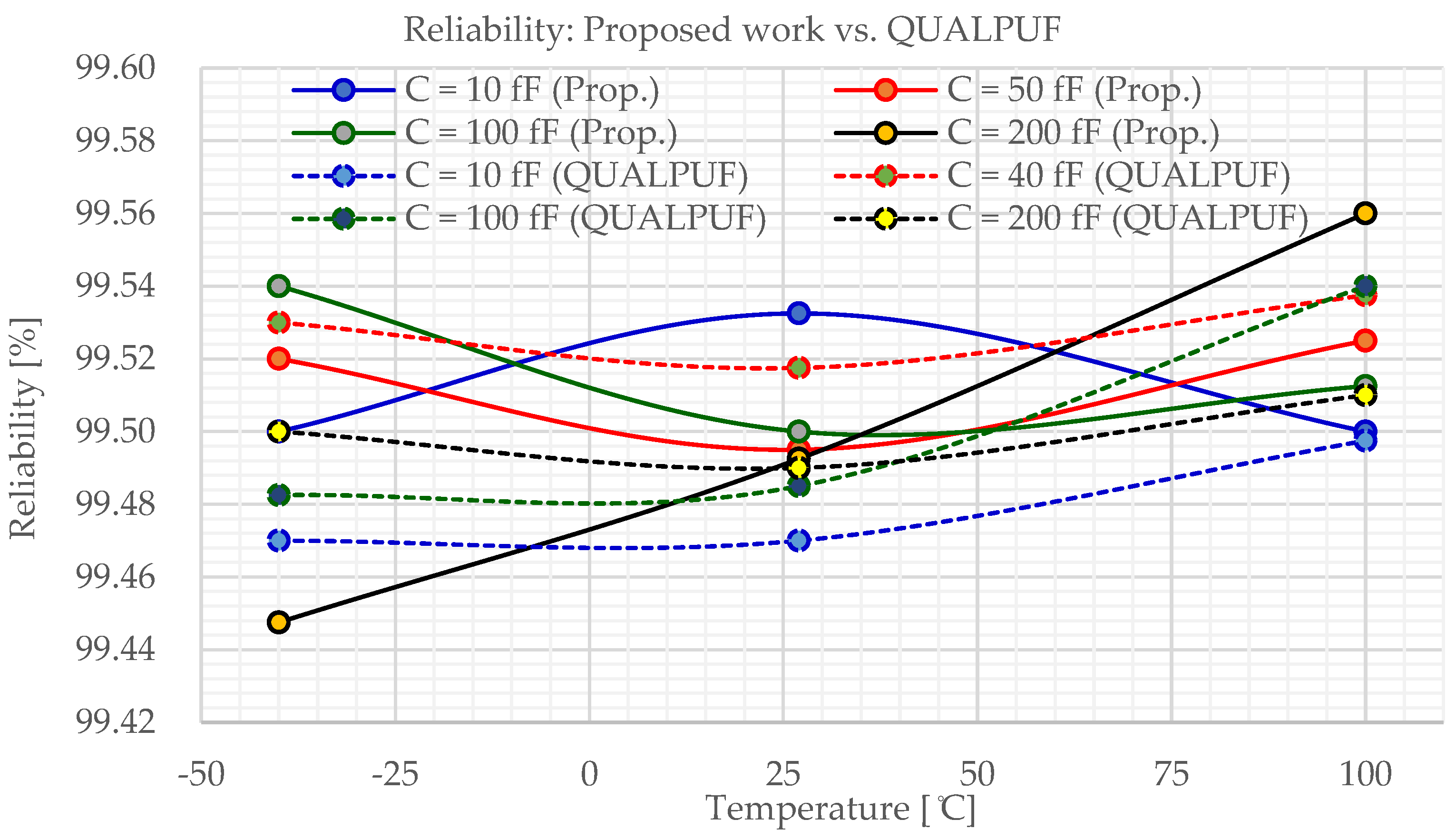

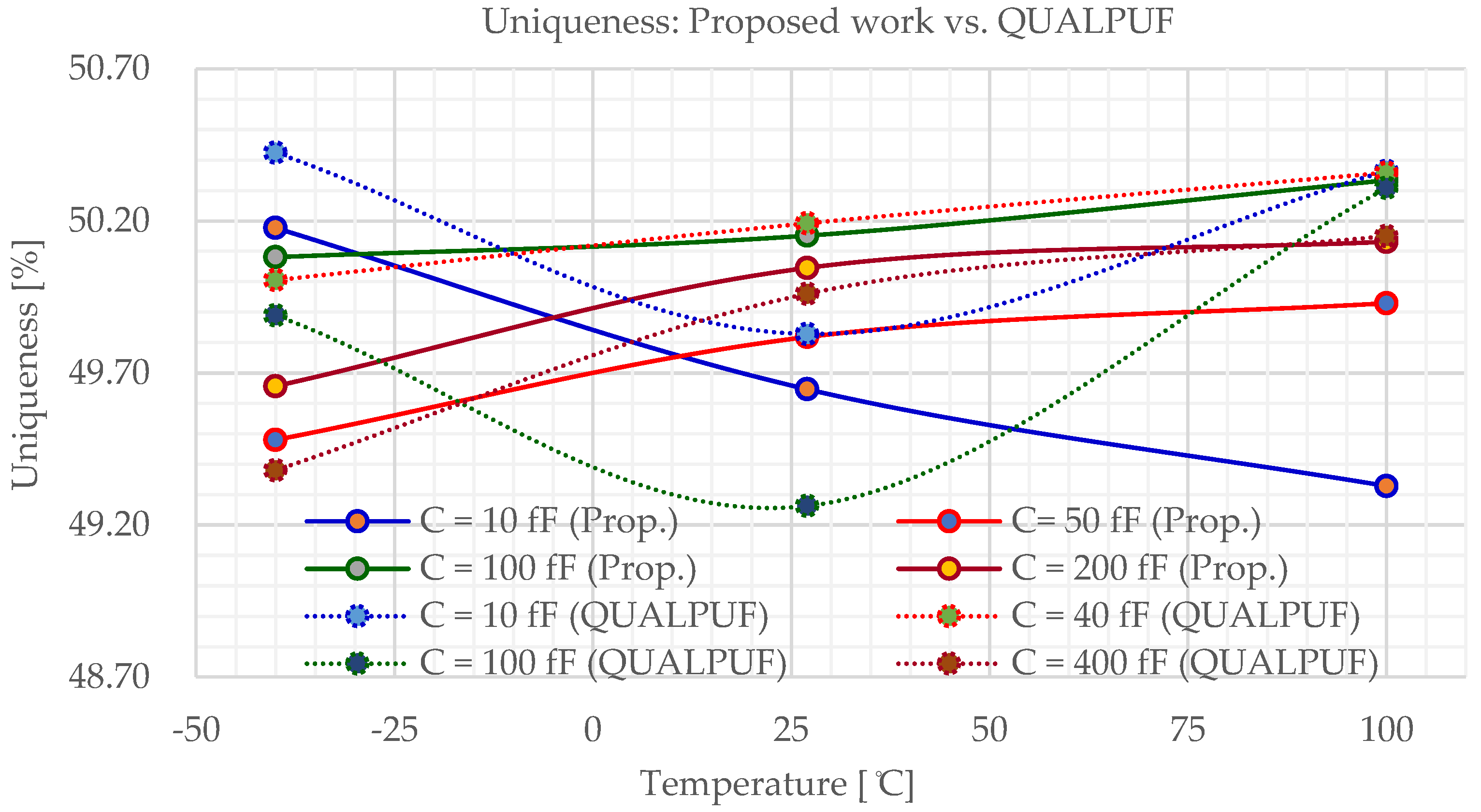

4.2.2. PUF Evaluation Metric

- Uniqueness is used to determine the ability of a PUF to distinguish a chip from other chips [29]. The ideal value of the uniqueness metric is 50%, indicating that a uniqueness result closer to 50% has a better performance (where the normalized value of uniqueness is 0 ≤ U ≤ 1). The uniqueness is expressed aswhere HD(Ri, Rj) represents the Hamming Distance of the two different PUF instances’ responses, with k number of chips and n-bit length.

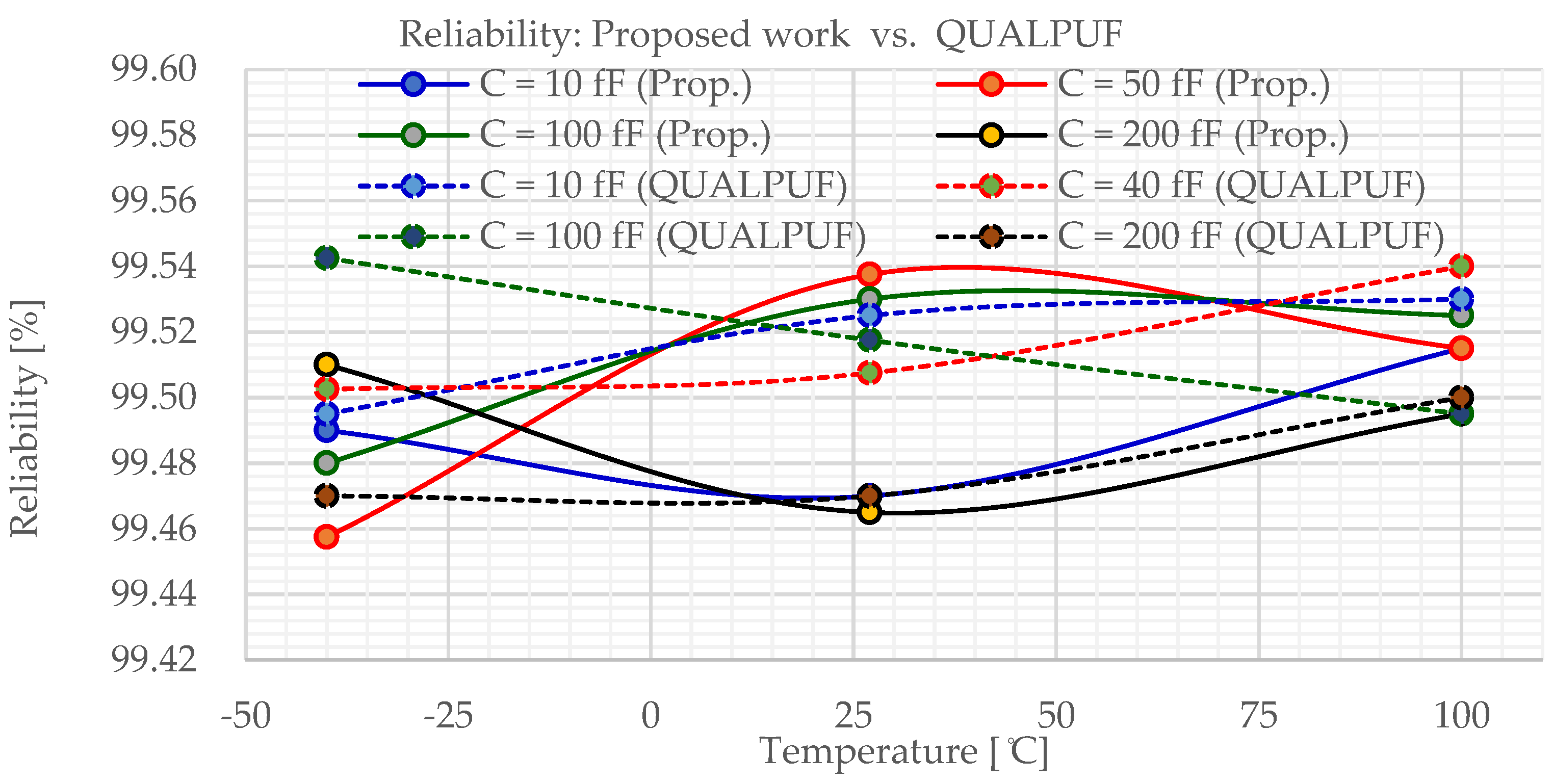

- Reliability measures how reproducibly the challenge-response pairs of a PUF instance with varying environmental conditions, such as temperature and CMOS process variations. The reliability is mathematically expressed as follows:where k represents the total number chips (k = 100 in this study), n is the number of PUF bits, and HD(Ri, Ri,j) is the Hamming Distance of j-th sampling of Ri. The ideal reliability value is 100%.

5. Discussion

6. Conclusions

- -

- it utilizes a trapezoidal power clock signal with a time-ramped voltage that can improve energy efficiency and facilitate reliable start-up PUF behavior;

- -

- static CMOS logic is employed to produce stable CRPs in the adiabatic mode;

- -

- an extra evaluation transistor enables the PUF cell to charge and discharge its output nodes with a constant supply current, while generating secure keys to counteract cyber-attacks;

- -

- by connecting the PMOS bulks to their respective sources, the proposed PUF cell can pull down the response node close to the ground during discharging. This method allows the PUF cell to produce a stable logic function for further cascading of the LSI circuits.

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Atzori, L.; Iera, A.; Morabito, G. The internet of things: A survey. Comput. Netw. 2010, 54, 2787–2805. [Google Scholar] [CrossRef]

- Bandyopadhyay, D.; Sen, J. Internet of things: Applications and challenges in technology and standardization. Wirel. Pers. Commun. 2011, 58, 49–69. [Google Scholar] [CrossRef]

- Keoh, S.L.; Kumar, S.S.; Tschofenig, H. Securing the internet of things: A standardization perspective. IEEE Internet Things J. 2014, 1, 265–275. [Google Scholar] [CrossRef]

- Helder, C.; Yu, M.-D.; Koushanfar, F.; Devadas, S. Physical Unclonable Functions and Applications: A Tutorial. Proc. IEEE 2014, 102, 1126–1141. [Google Scholar] [CrossRef]

- Mukhopadhyay, D. PUFs as promising tools for security in Internet of Things. IEEE Des. Test 2016, 33, 103–115. [Google Scholar] [CrossRef]

- McGrath, T.; Bagci, I.E.; Wang, Z.M.; Roedig, U.; Young, R.J. A PUF Taxonomy. Appl. Phys. Rev. 2019, 6, 011303. [Google Scholar] [CrossRef]

- Hori, Y.; Yoshida, T.; Katashita, T.; Satoh, A. Quantitative and statistical performance evaluation of arbiter physical unclonable functions on FPGAs. In Proceedings of the 2010 International Conference on IEEE Reconfigurable Computing and FPGAs, Cancun, Mexico, 13–15 December 2010; pp. 298–303. [Google Scholar] [CrossRef]

- Lee, J.W.; Lim, D.; Gassend, B.; Suh, G.E.; Dijk, M.v.; Devadas, S. A technique to build a secret key in integrated circuits for identification and authentication applications. In Proceedings of the 2004 Symposium on VLSI Circuits. Digest of Technical Papers (IEEE Cat. No.04CH37525), Honolulu, HI, USA, 17–19 June 2004; pp. 176–179. [Google Scholar] [CrossRef]

- Beckmann, N.; Potkonjak, M. Hardware-based public-key cryptography with public physically unclonable functions. In International Workshop on Information Hiding; Springer: Darmstadt, Germany, 2009; pp. 206–220. [Google Scholar] [CrossRef]

- Machida, T.; Yamamoto, D.; Iwamoto, M.; Sakiyama, K. Implementation of double arbiter PUF and its performance evaluation on FPGA. In Proceedings of the 20th Asia and South Pacific Design Automation Conference, Chiba, Japan, 19–22 January 2015; pp. 6–7. [Google Scholar] [CrossRef]

- Maiti, A.; Casarona, J.; McHale, L.; Schaumont, P. A large scale characterization of RO-PUF. In Proceedings of the 2010 IEEE International Symposium on Hardware-Oriented Security and Trust (HOST), Anaheim, CA, USA, 13–14 June 2010; pp. 94–99. [Google Scholar] [CrossRef]

- Gao, M.; Lai, K.; Qu, G. A highly flexible ring oscillator PUF. In Proceedings of the 51st Annual Design Automation Conference, San Francisco, CA, USA, 1–5 June 2014; ACM: New York, NY, USA, 2014; pp. 1–6. [Google Scholar] [CrossRef]

- Maiti, A.; Schaumont, P. Improving the quality of a physical unclonable function using configurable ring oscillators. In Proceedings of the International Conference on Field Programmable Logic and Applications, Prague, Czech Republic, 31 August–2 September 2009; pp. 703–707. [Google Scholar] [CrossRef]

- Gassend, B.; Clarke, D.; Dijk, M.v.; Devadas, S. Silicon physical random functions. In Proceedings of the 9th ACM Conference on Computer and Communications Security, Washington, DC, USA, 18–22 November 2002; pp. 148–160. [Google Scholar] [CrossRef]

- Cao, Y.; Zhang, L.; Chang, C.-H.; Chen, S. A Low-Power Hybrid RO PUF with Improved Thermal Stability for Lightweight Applications. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2015, 34, 1143–1147. [Google Scholar] [CrossRef]

- Günlü, O.; Kernetzky, T.; İşcan, O.; Sidorenko, V.; Kramer, G.; Schaefer, R.F. Secure and Reliable Key Agreement with Physical Unclonable Functions. Entropy 2018, 20, 340. [Google Scholar] [CrossRef] [PubMed]

- Chen, Q.; Csaba, G.; Lugli, P.; Schlichtmann, U.; Ruhmair, U. The bistable ring PUF: A new architecture for strong physical unclonable functions. In Proceedings of the IEEE International Symposium on Hardware-Oriented Security and Trust (HOST), San Diego, CA, USA, 5–6 June 2011; pp. 134–141. [Google Scholar] [CrossRef]

- Anderson, J.H. A PUF design for secure FPGA-based embedded systems. In Proceedings of the 15th Asia and South Pacific Design Automation Conference (ASP-DAC), Taipe, Taiwan, 18–21 January 2010; pp. 1–6. [Google Scholar] [CrossRef]

- Tehranipoor, F.; Karimian, N.; Xion, K.; Chandy, J.A. DRAM-based Intrinsic physical unclonable functions for system level security. In Proceedings of the 25th Edition on Great Lakes Symposium on VLSI, Pittsburgh, PA, USA, 20–22 May 2015; pp. 15–20. [Google Scholar] [CrossRef]

- Tehranipoor, F.; Karimian, N.; Yan, W.; Chandy, J.A. DRAM-based intrinsic physically unclonable functions for system-level security and authentication. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2017, 25, 1085–1097. [Google Scholar] [CrossRef]

- Guajardo, J.; Kumar, S.S.; Schrijen, G.-J.; Tuyls, P. FPGA intrinsic PUFs and their use for IP protection. In Proceedings of the 9th International Workshop on Cryptographic Hardware and Embedded Systems, Viennan, Austria, 10–13 September 2007; pp. 63–80. [Google Scholar] [CrossRef]

- Holcomb, D.E.; Burleson, W.P.; Fu, K. Power-Up SRAM State as an Identifying Fingerprint and Source of True Random Numbers. IEEE Trans. Comput. 2009, 58, 1198–1210. [Google Scholar] [CrossRef]

- Majzoobi, M.; Ghiaasi, G.; Koushanfar, F.; Nassif, S.R. Ultra-low power current-based PUF. In Proceedings of the 2011 IEEE International Symposium of Circuits and Systems (ISCAS), Rio de Janeiro, Brazil, 15–18 May 2011; pp. 2071–2074. [Google Scholar] [CrossRef]

- Golanbari, M.S.; Kiamehr, S.; Bishnoi, R.; Tahoori, M.B. Reliable memory PUF design for low-power applications. In Proceedings of the 19th International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, USA, 13–14 March 2018; pp. 207–213. [Google Scholar] [CrossRef]

- Athas, W.C.; Svensson, L.J.; Koller, J.G.; Tzartzanis, N.; Chou, E.Y.-C. Low-power digital systems based on adiabatic-switching principles. IEEE Trans. Very Large-Scale Integr. (VLSI) Syst. 1994, 2, 398–407. [Google Scholar] [CrossRef]

- Monteiro, C.; Takahashi, Y.; Sekine, T. Low-power secure S-box circuit using charge-sharing symmetric adiabatic logic for advanced encryption standard hardware design. IET Circuits Dev. Syst. 2015, 9, 362–369. [Google Scholar] [CrossRef]

- Avital, M.; Dagan, H.; Levi, I.; Keren, O.; Fish, A. DPA-Secured Quasi-Adiabatic Logic (SQAL) for Low-Power Passive RFID Tags Employing S-Boxes. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 149–156. [Google Scholar] [CrossRef]

- Kumar, S.D.; Thapliyal, H.; Mohammad, A. EE-SPFAL: A Novel Energy-Efficient Secure Positive Feedback Adiabatic Logic for DPA Resistant RFID and Smart Card. IEEE Trans. Emerg. Top. Comput. 2019, 7, 281–293. [Google Scholar] [CrossRef]

- Kumar, S.D.; Thapliyal, H. QUALPUF: A Novel Quasi-Adiabatic Logic based Physical Unclonable Function. In Proceedings of the 11th Annual Cyber and Information Security Research Conference, Oak Ridge, TN, USA, 5–7 April 2016. [Google Scholar] [CrossRef]

- Kumar, S.D.; Thapliyal, H. Design of Adiabatic Logic-Based Energy-Efficient and Reliable PUF for IoT Devices. J. Emerg. Technol. Comput. Syst. 2020, 16, 34. [Google Scholar] [CrossRef]

- Takahashi, Y.; Koyasu, H.; Kumar, S.D.; Thapliyal, H. Post-Layout Simulation of Quasi-Adiabatic Logic Based Physical Unclonable Function. In Proceedings of the 2019 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Miami, FL, USA, 15–17 July 2019; pp. 443–446. [Google Scholar] [CrossRef]

- Takahashi, Y.; Koyasu, H.; Kumar, S.D.; Thapliyal, H. Quasi-Adiabatic SRAM Based Silicon Physical Unclonable Function. SN Comput. Sci. 2020, 1, 237. [Google Scholar] [CrossRef]

- Razavi, B. Design of Analog CMOS Integrated Circuit; International Edition; McGRAM-HILL: New York, NY, USA, 2001; pp. 9–38. [Google Scholar]

- Muller, R.S.; Kamins, T.I. Device Electronics for Integrated Circuits, 2nd ed.; Wiley: New York, NY, USA, 1986. [Google Scholar]

- Cortez, M.; Hamdioui, S.; Kaichouhi, A.; Leest, V.v.d.; Maes, R.; Schrijen, G.-J. Intelligent Voltage Ramp-Up Time Adaptation for Temperature Noise Reduction on Memory-Based PUF Systems. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2015, 34, 1162–1175. [Google Scholar] [CrossRef]

| Power supply | Vpc: swing from 0.9–1.8 V trapezoidal clock, fVpc = 100 MH zVpc-: swing from 0–0.9 V trapezoidal power clock, fVpc- = 100 MHzCb voltage: 1.8 pulse signal, fCb = 10 MHz |

| Transistor parameter and ratio | Parameter: 0.18 µm ROHM standard CMOS process Ratio: W/L = 0.6 µm/0.18 µm for all NMOS and PMOS Transistors |

| PUF | Kumar [29] | Takahashi [32] | This Work |

|---|---|---|---|

| Year | 2016 | 2019 | 2021 |

| Topology | Adiabatic SRAM | Adiabatic SRAM | Adiabatic SRAM |

| Transistor-number/bit | 5 | 5 | 7 |

| Process (nm) | 180 | 180 | 180 |

| Start-Up power (µW) | 3.08 | 3.08 | 0.47 |

| Energy (fJ/bit/cycle) | 39.18 | 39.18 | 15.98 |

| Uniqueness (%) | 40.50 | 47.58 | 49.82 |

| Reliability (%) | 96.20 | 95.10 | 99.47 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Monteiro, C.; Takahashi, Y. Low-Power Two-Phase Clocking Adiabatic PUF Circuit. Electronics 2021, 10, 1258. https://doi.org/10.3390/electronics10111258

Monteiro C, Takahashi Y. Low-Power Two-Phase Clocking Adiabatic PUF Circuit. Electronics. 2021; 10(11):1258. https://doi.org/10.3390/electronics10111258

Chicago/Turabian StyleMonteiro, Câncio, and Yasuhiro Takahashi. 2021. "Low-Power Two-Phase Clocking Adiabatic PUF Circuit" Electronics 10, no. 11: 1258. https://doi.org/10.3390/electronics10111258

APA StyleMonteiro, C., & Takahashi, Y. (2021). Low-Power Two-Phase Clocking Adiabatic PUF Circuit. Electronics, 10(11), 1258. https://doi.org/10.3390/electronics10111258