Design of a Charge Pump Circuit and System with Input Impedance Modulation for a Flexible-Type Thermoelectric Generator with High-Output Impedance

Abstract

1. Introduction

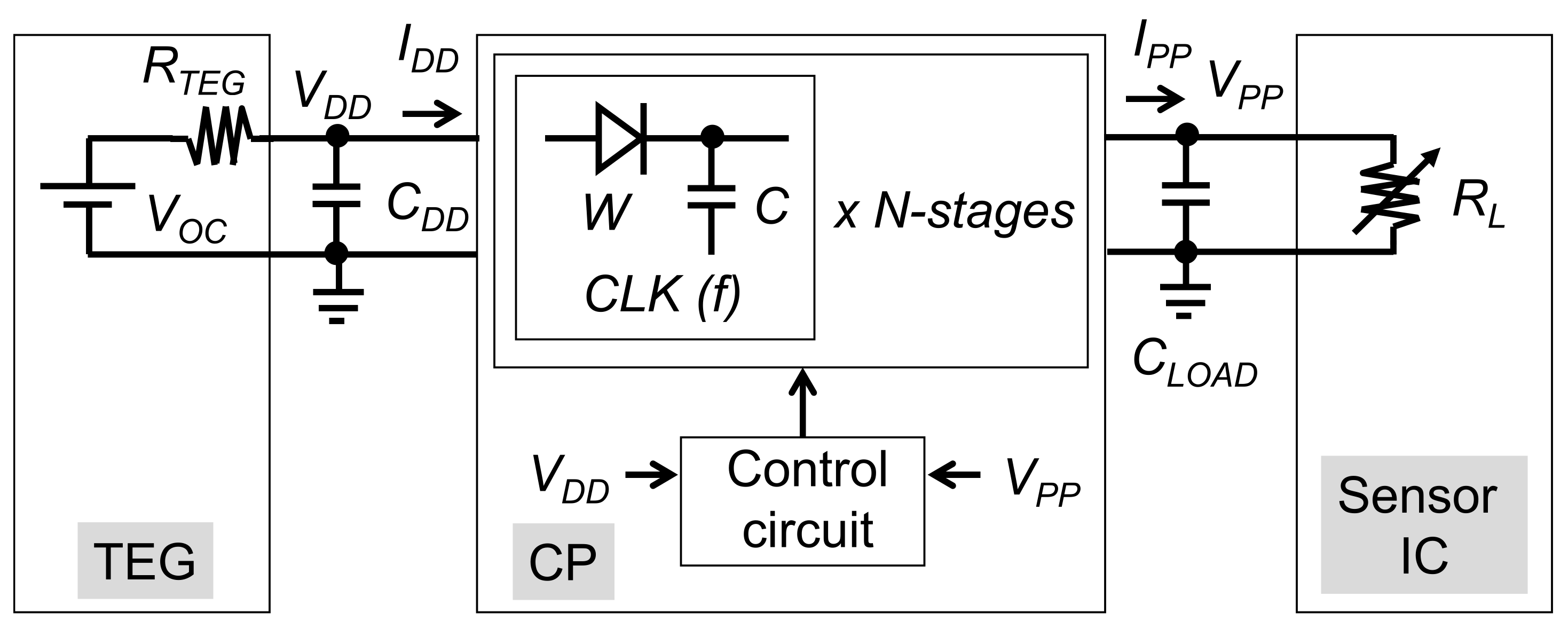

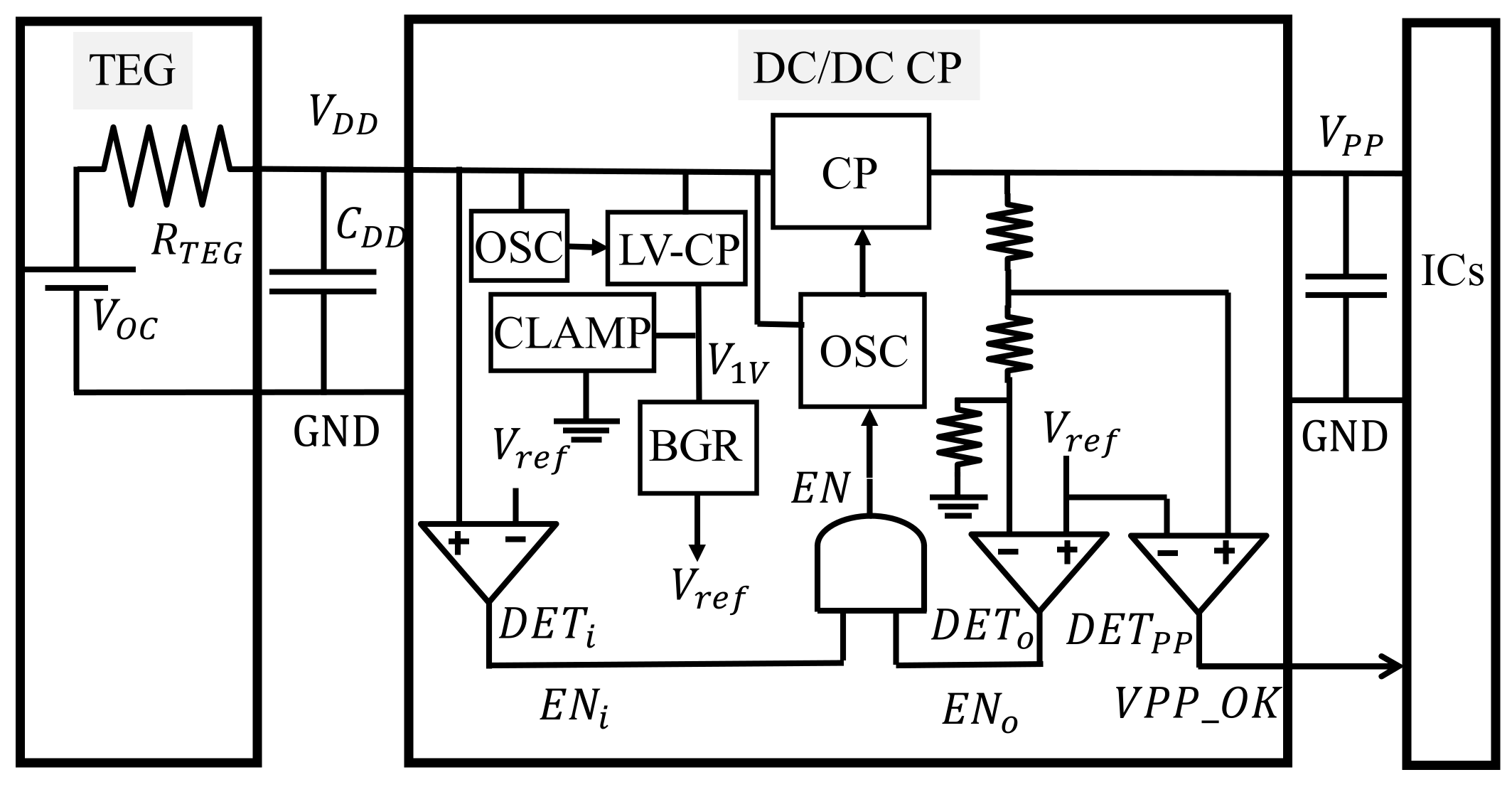

2. Circuit Design

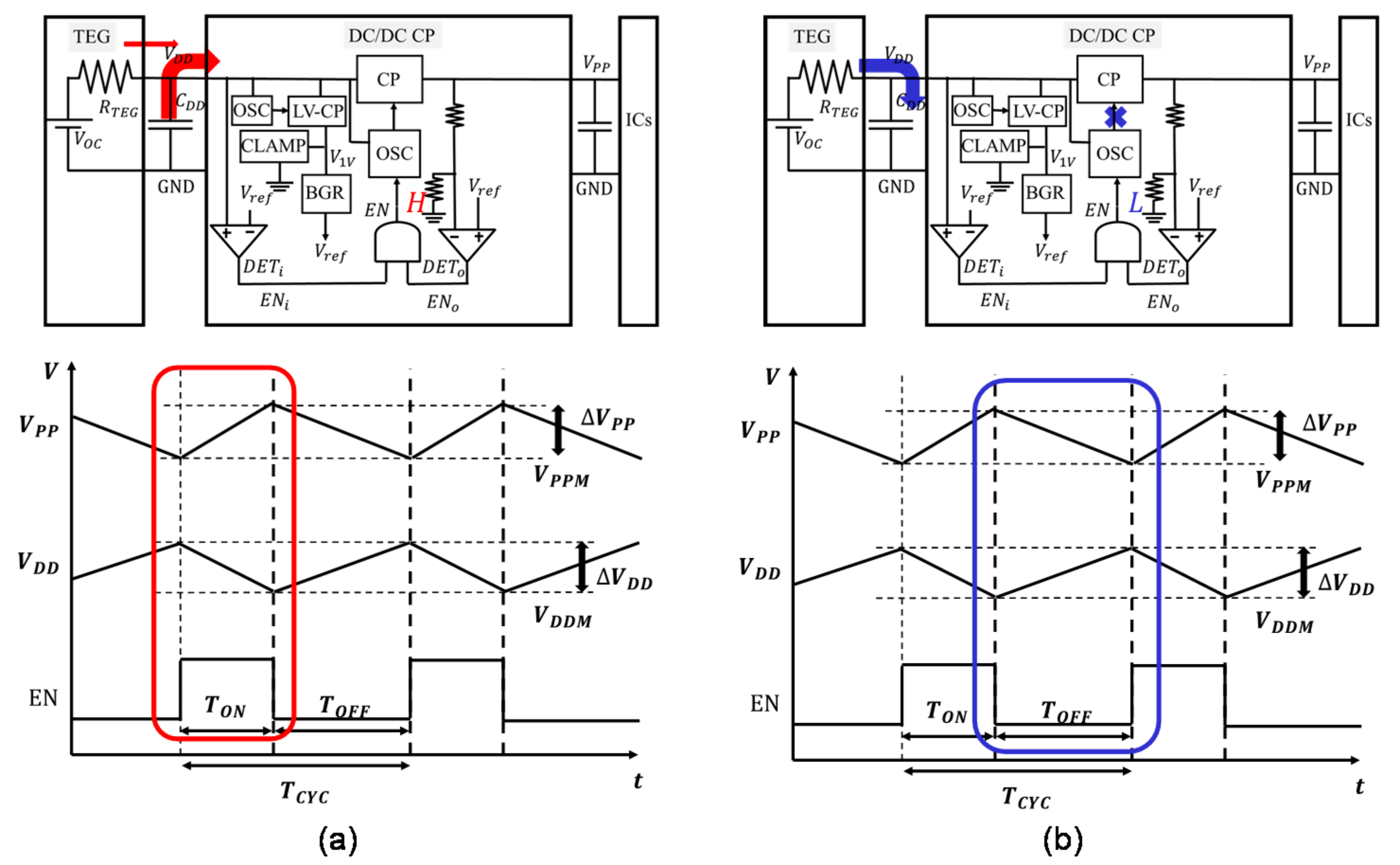

2.1. System Design

2.2. Building Blocks’ Design

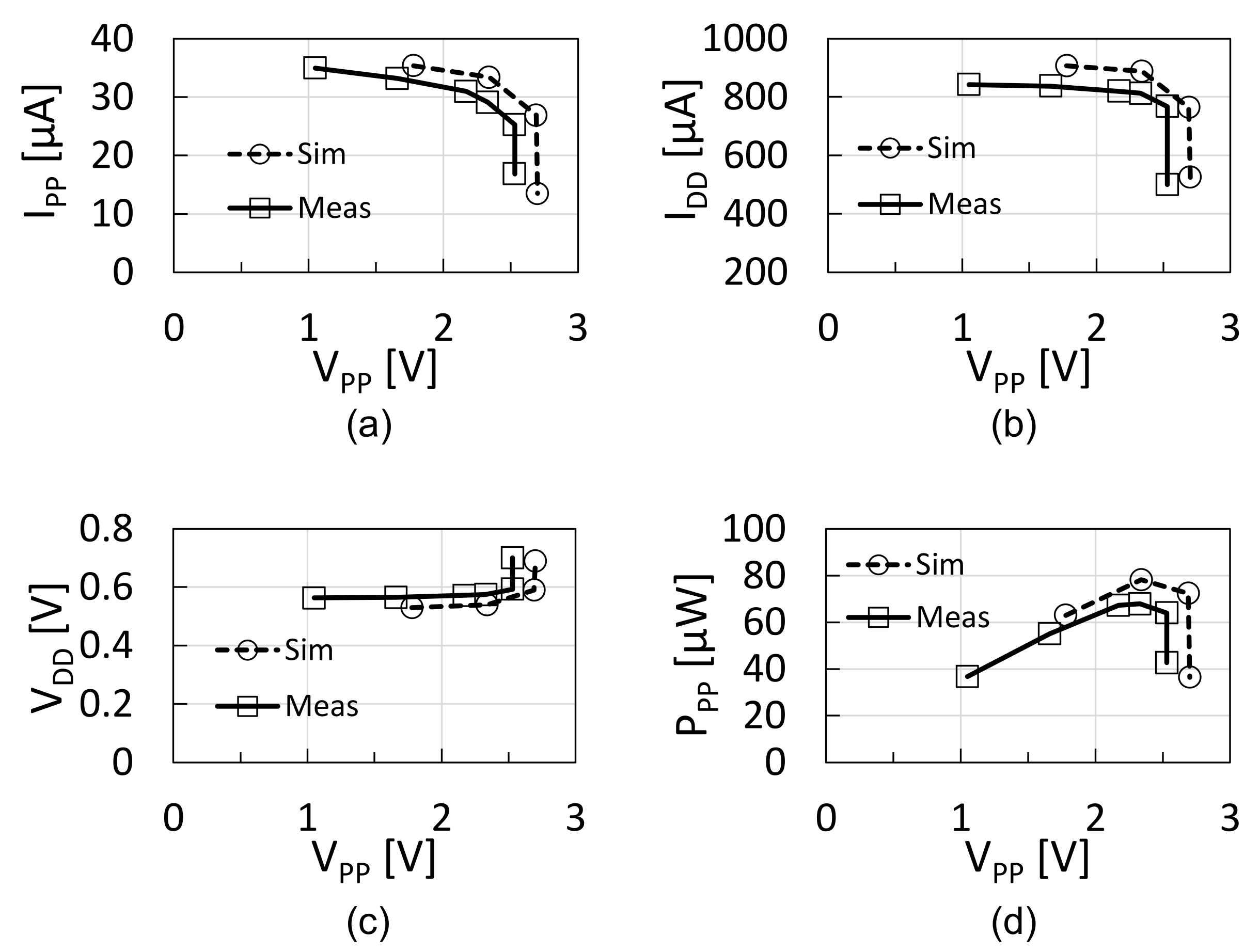

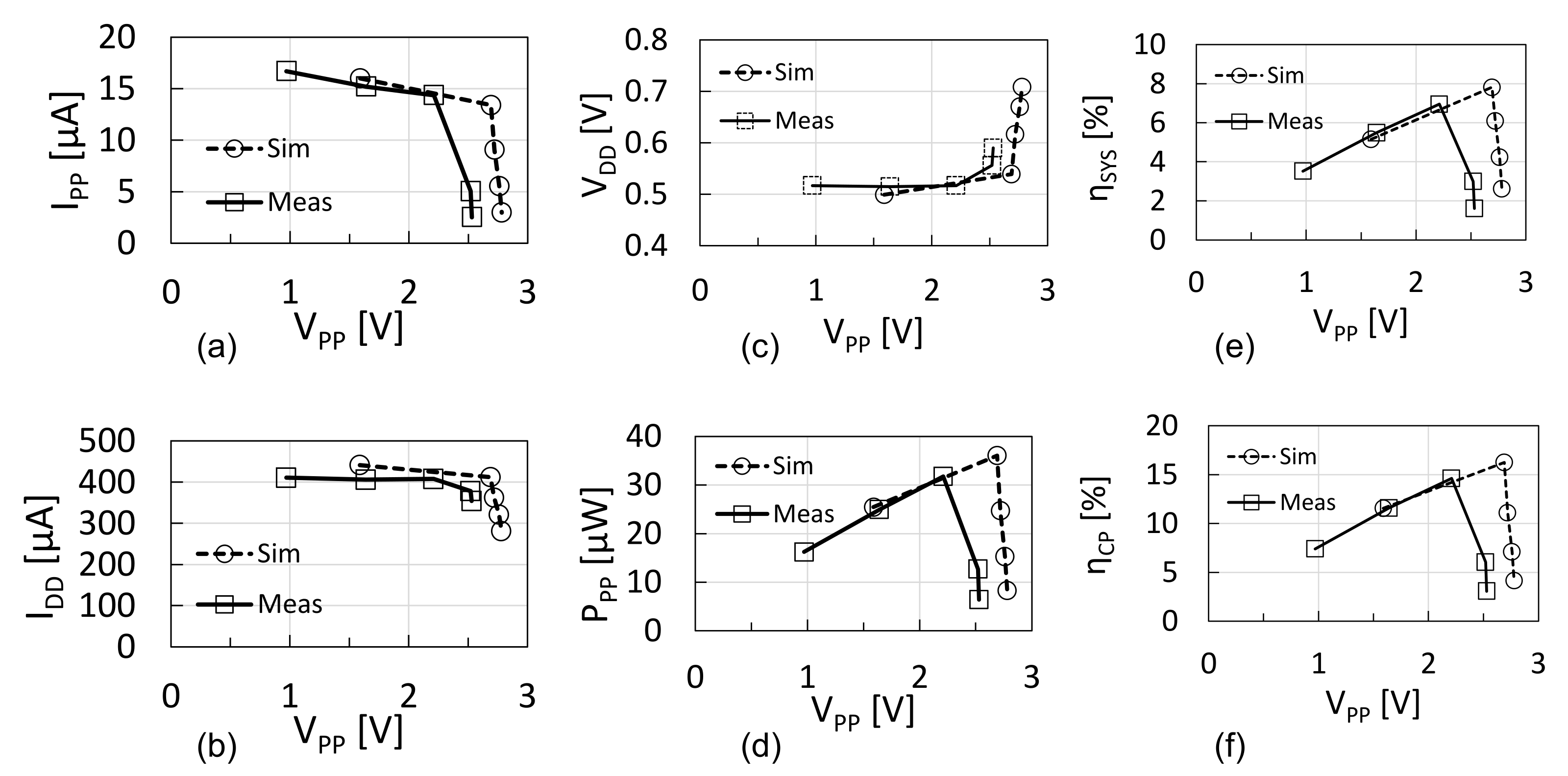

2.3. Experimental Results

3. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Nomenclature

| C | Capacitance per stage |

| CDD | Capacitor connected to VDD |

| CPP | Capacitor connected to VPP |

| f | Clock frequency |

| ICP | Input current of CP |

| ICTRL | Input current of control circuits |

| IDD | Operating current of the TEG and CP |

| ILOAD | Load current of the CP |

| ITEG | Output current of the TEG |

| N | Stage number of the CP |

| PDD | Input power of the CP |

| PPP | Output power of the CP |

| PTEG | Generated power of the TEG |

| αT | Ratio of top plate capacitance to C |

| αB | Ratio of bottom plate capacitance to C |

| RTEG | Output impedance of the TEG |

| T | Operation period, TON + TOFF |

| TOFF | Suspended period |

| TON | Resumed period |

| VDD | Input voltage of the CP |

| VDDT | Target input voltage of the CP to be controlled |

| VDDM | Minimum VDD in operation |

| ΔVDD | Ripple in VDD |

| VPP | Output voltage of the CP |

| VPPT | Target output voltage of the CP to be controlled |

| VPPM | Minimum VPP in operation |

| ΔVPP | Ripple in VPP |

| β | Ratio of ICTRL to IDD |

| γ | Operation duty; TON/T |

References

- Lu, C.; Raghunathan, V.; Roy, K. Efficient Design of Micro-Scale Energy Harvesting Systems. IEEE J. Emerg. Sel. Top. Circuits Syst. 2011, 1, 254–266. [Google Scholar] [CrossRef]

- Huesgen, T.; Woias, P.; Kockmann, N. Design and fabrication of MEMS thermoelectric generators with high temperature efficiency. Sens. Actuators A Phys. 2008, 145, 423–429. [Google Scholar] [CrossRef]

- Date Sheet of TGP-651, Micropelt. Available online: http://www.micropelt.com/ (accessed on 2 April 2021).

- Du, Y.; Xu, J.; Paul, B.; Eklund, P. Flexible thermoelectric materials and devices. Appl. Mater. Today 2018, 12, 366–388. [Google Scholar] [CrossRef]

- Priya, S.; Inman, D.J. Chapter 18: Energy Harvesting for Active RF Sensors and ID Tags. In Energy Harvesting Technologies; Springer: New York, NY, USA, 2009. [Google Scholar]

- Li, Y.; Buddharaju, K.; Singh, N.; Lo, G.Q.; Lee, S.J. Chip-Level Thermoelectric Power Generators Based on High-Density Silicon Nanowire Array Prepared with Top-Down CMOS Technology. IEEE Electron Device Lett. 2011, 32, 674–676. [Google Scholar] [CrossRef]

- Shrivastava, A.; Wentzloff, D.; Calhoun, B.H. A 10mV-input boost converter with inductor peak current control and zero detection for thermoelectric energy harvesting. In Proceedings of the IEEE 2014 Custom Integrated Circuits Conference, San Jose, CA, USA, 15–17 September 2014. [Google Scholar] [CrossRef]

- Remeli, M.F.; Kiatbodin, L.; Singh, B.; Verojporn, K.; Date, A.; Akbarzadeh, A. Power Generation from Waste Heat Using Heat Pipe and Thermoelectric Generator. Energy Procedia 2015, 75, 645–650. [Google Scholar] [CrossRef]

- Priya, S.; Inman, D.J. Chapter 11: Thermoelectric Energy Harvesting. In Energy Harvesting Technologies; Springer: New York, NY, USA, 2009. [Google Scholar]

- Tokuda, S.; Tanzawa, T. Toward a Minimum-Operating-Voltage Design of DC-DC Charge Pump Circuits for Energy Harvesting. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Koketsu, K.; Tanzawa, T. An Optimum Design of Thermal Energy Transducers and Power Converters for Small Form-Factor Thermoelectric Energy Harvester. In Proceedings of the IEICE General Conference, Tokyo, Japan, 19–22 March 2019; Available online: http://hdl.handle.net/10297/00026345 (accessed on 27 March 2019).

- Lu, C.; Park, S.P.; Raghunathan, V.; Roy, K. Analysis and Design of Ultra Low Power Thermoelectric Energy Harvesting Systems. In Proceedings of the 16th ACM/IEEE International Symposium on Low-Power Electronics and Design, Austin, TX, USA, 11 October 2010; pp. 183–188. [Google Scholar] [CrossRef]

- Tanzawa, T. Design of DC-DC Switched-Capacitor Voltage Multiplier driven by DC Energy Transducer. In Proceedings of the 2014 21st IEEE International Conference on Electronics Circuits and Systems, Marseille, France, 7–10 December 2014; pp. 327–330. [Google Scholar] [CrossRef]

- Koketsu, K.; Tanzawa, T. A Design of Cold Start Charge Pump for Flexible Thermoelectric Generator with High Output Impedance. In Proceedings of the 2020 27th IEEE International Conference on Electronics, Circuits and Systems, Glasgow, UK, 23–25 November 2020. [Google Scholar] [CrossRef]

- Tanzawa, T. An Optimum Design for Integrated Switched-Capacitor Dickson Charge Pump Multipliers with Area Power Balance. IEEE Trans. Power Electron. 2014, 29, 534–538. [Google Scholar] [CrossRef]

- Haddad, P.-A.; Gosset, G.; Raskin, J.-P.; Flandre, D. Automated Design of a 13.56 MHz 19 µW Passive Rectifier With 72% Efficiency Under 10 µA load. IEEE J. Solid-State Circuits 2016, 51, 1290–1301. [Google Scholar] [CrossRef]

- Banba, H.; Shiga, H.; Umezawa, A.; Miyaba, T.; Tanzawa, T.; Atsumi, S.; Sakui, K. A CMOS bandgap reference circuit with sub-1-V operation. IEEE J. Solid-State Circuits 1999, 34, 670–674. [Google Scholar] [CrossRef]

- Suemori, K.; Hoshino, S.; Kamata, T. Flexible and lightweight thermoelectric generators composed of carbon nanotube—Polystyrene composites printed on film substrate. Appl. Phys. Lett. 2013, 103, 153902. [Google Scholar] [CrossRef]

| Optimum Design Target | Given Design Parameters | Parameter to Be Optimized | Parameters to Be Determined | |

|---|---|---|---|---|

| Tokuda [10] | CP | VPP, IPP, VDD, f | Area of the CP to be minimized and the PCE to be maximized | |

| Koketsu [11] | TEG + CP | VPP, IPP, f | Area of the TEG and CP to be minimized | VOC, RTEG, N, C |

| Lu [12] | VOC, RTEG, N, C | PPP to be maximized | W, f | |

| Tanzawa [13] | VOC, RTEG, VPP, f | IPP @ VPP to be maximized | ||

| This work | VOC, RTEG, VPPVDDMIN |

| VPP < VPPT | VPP > VPPT | |

|---|---|---|

| VDD > VDDT | Resume | Suspend |

| VDD < VDDT | Suspend | Suspend |

| VDDMIN | VDDT | VTHEFF | VPPT | RTEG | VOCMIN | f | αT | αB | β | γ |

|---|---|---|---|---|---|---|---|---|---|---|

| 0.45 V | 0.5 V | 0.25 V | 2.5 V | 400 Ω | 0.6 V | 10 MHz | 0.1 | 0.2 | 0.2 | 0.33 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Koketsu, K.; Tanzawa, T. Design of a Charge Pump Circuit and System with Input Impedance Modulation for a Flexible-Type Thermoelectric Generator with High-Output Impedance. Electronics 2021, 10, 1212. https://doi.org/10.3390/electronics10101212

Koketsu K, Tanzawa T. Design of a Charge Pump Circuit and System with Input Impedance Modulation for a Flexible-Type Thermoelectric Generator with High-Output Impedance. Electronics. 2021; 10(10):1212. https://doi.org/10.3390/electronics10101212

Chicago/Turabian StyleKoketsu, Kazuma, and Toru Tanzawa. 2021. "Design of a Charge Pump Circuit and System with Input Impedance Modulation for a Flexible-Type Thermoelectric Generator with High-Output Impedance" Electronics 10, no. 10: 1212. https://doi.org/10.3390/electronics10101212

APA StyleKoketsu, K., & Tanzawa, T. (2021). Design of a Charge Pump Circuit and System with Input Impedance Modulation for a Flexible-Type Thermoelectric Generator with High-Output Impedance. Electronics, 10(10), 1212. https://doi.org/10.3390/electronics10101212