Mechanism Analysis of Dynamic On-State Resistance Degradation for a Commercial GaN HEMT Using Double Pulse Test

Abstract

1. Introduction

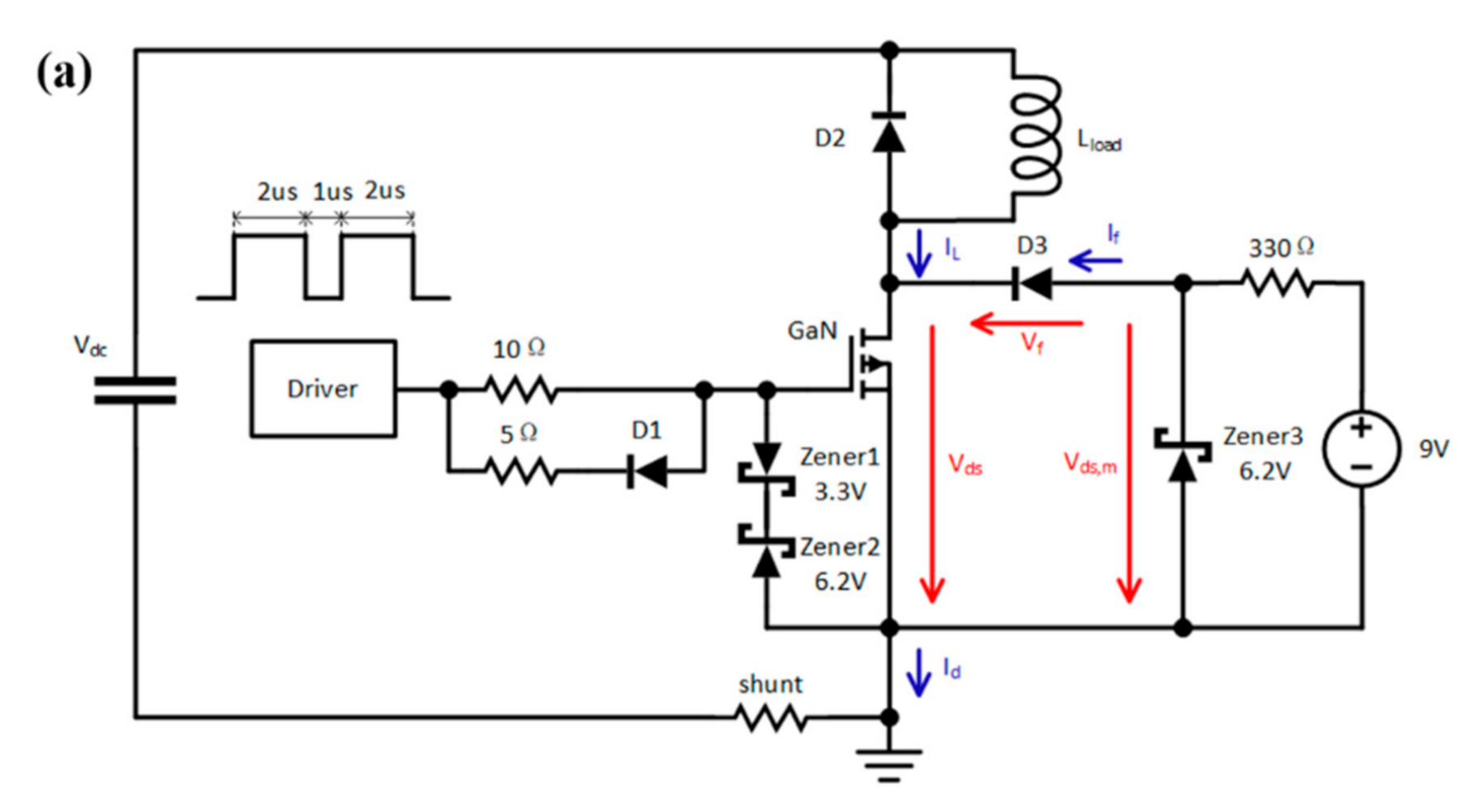

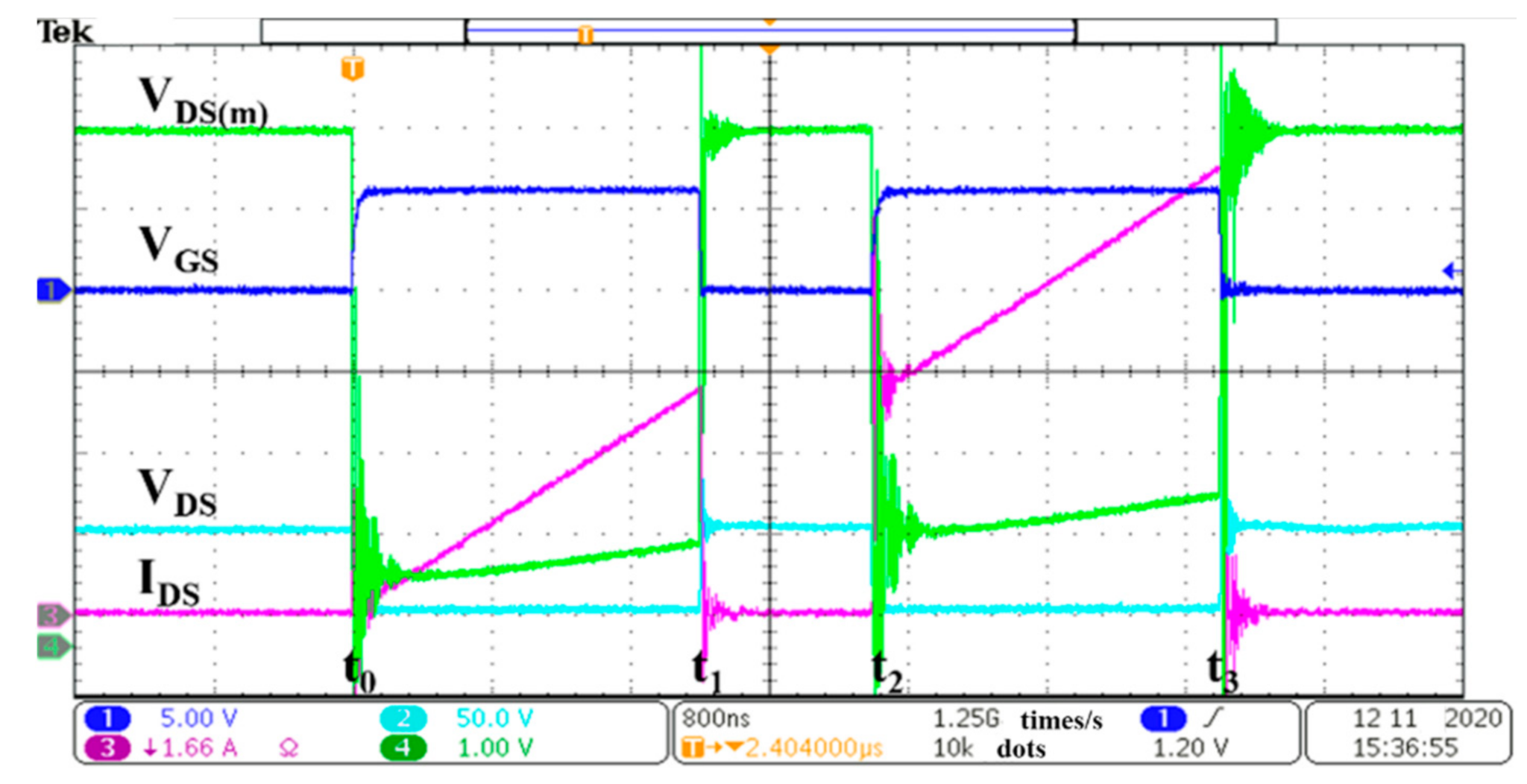

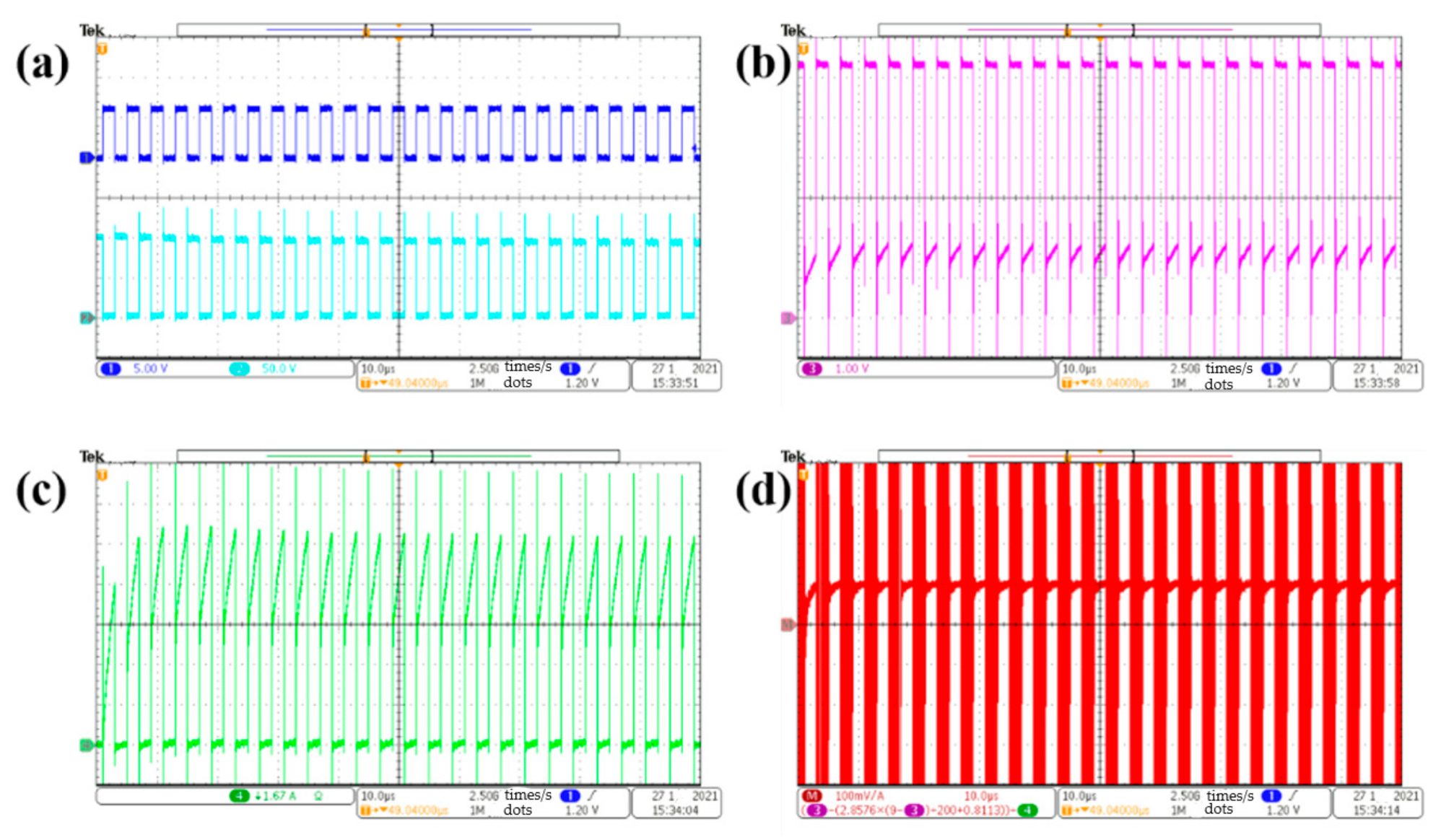

2. Experimental Details

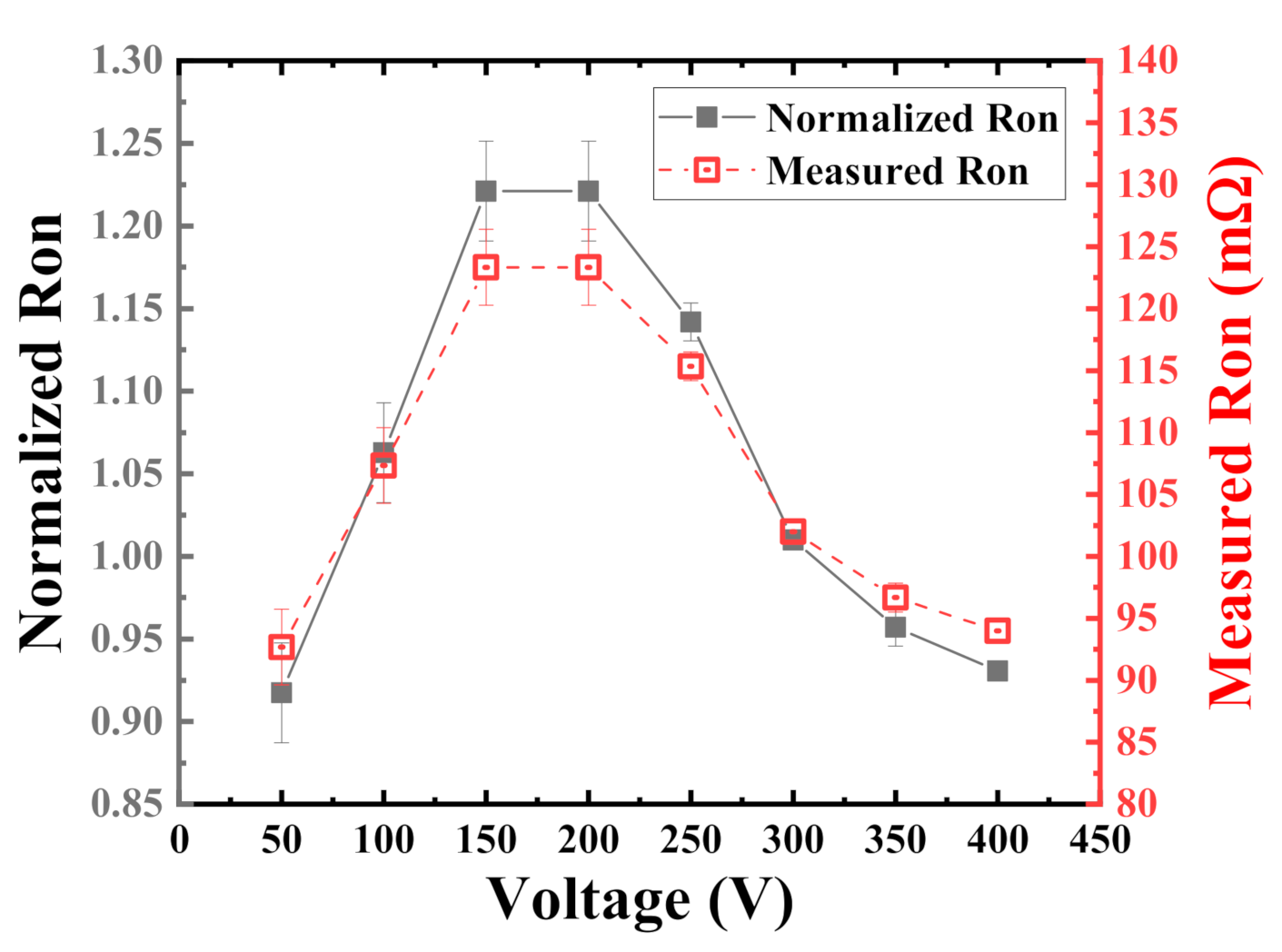

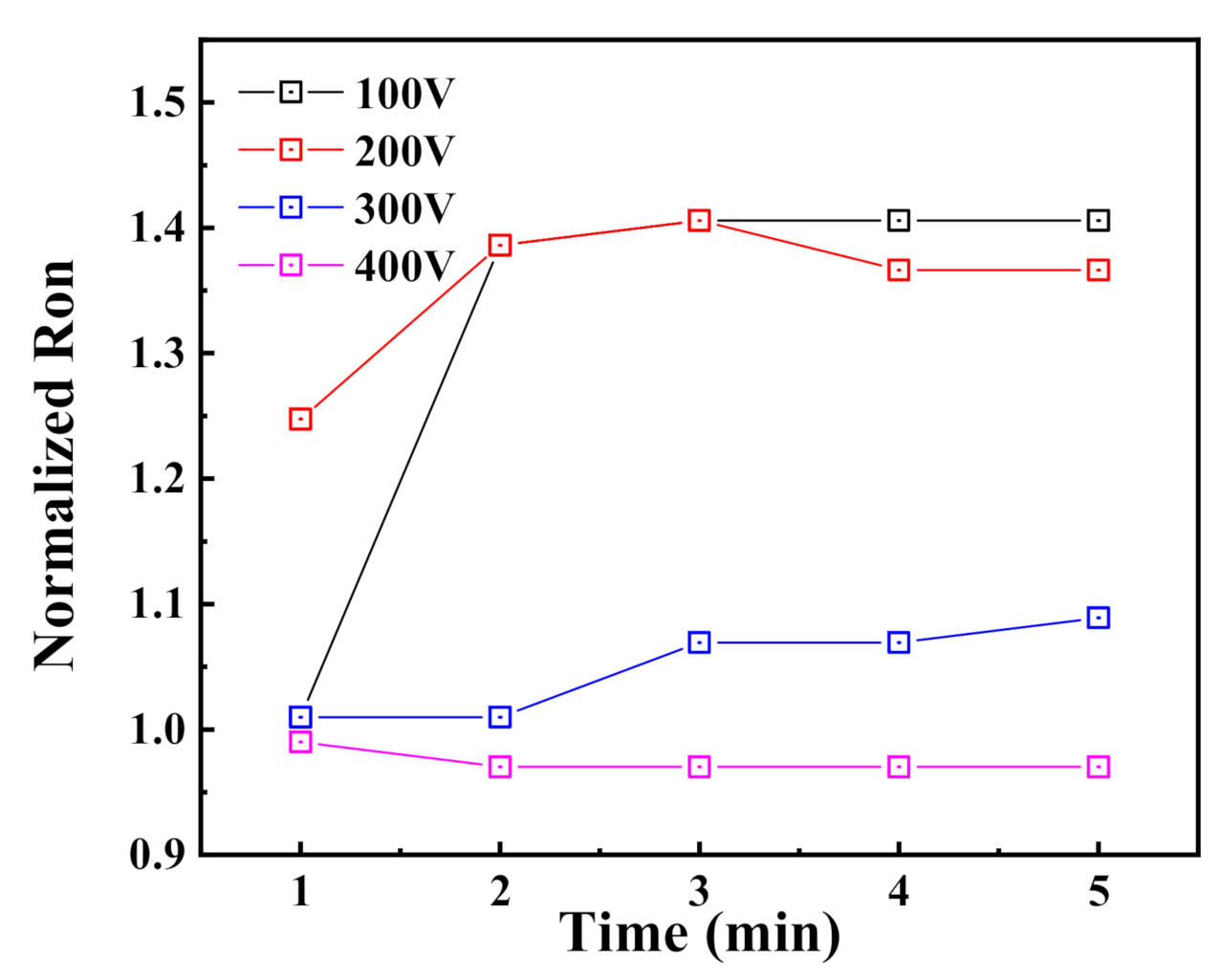

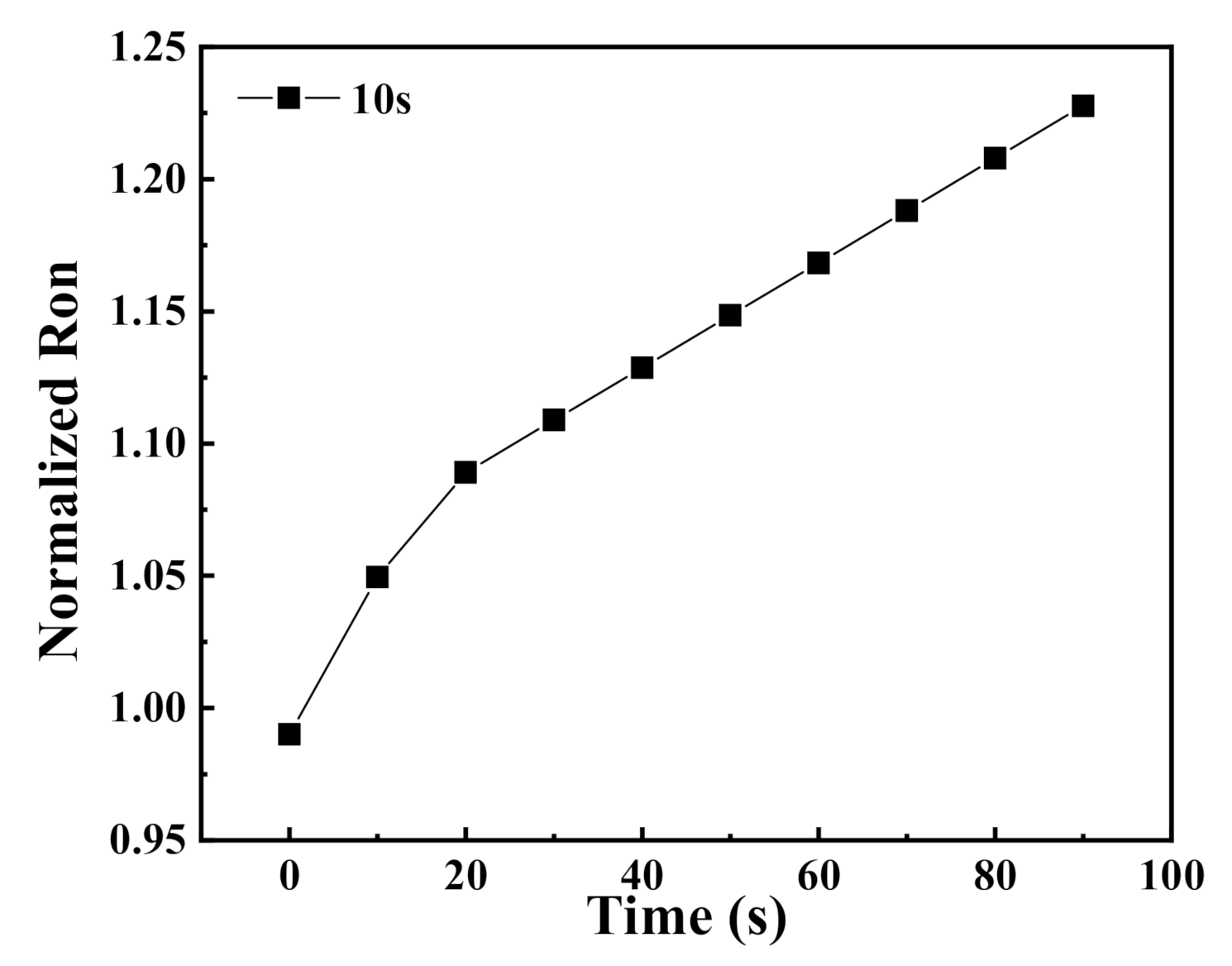

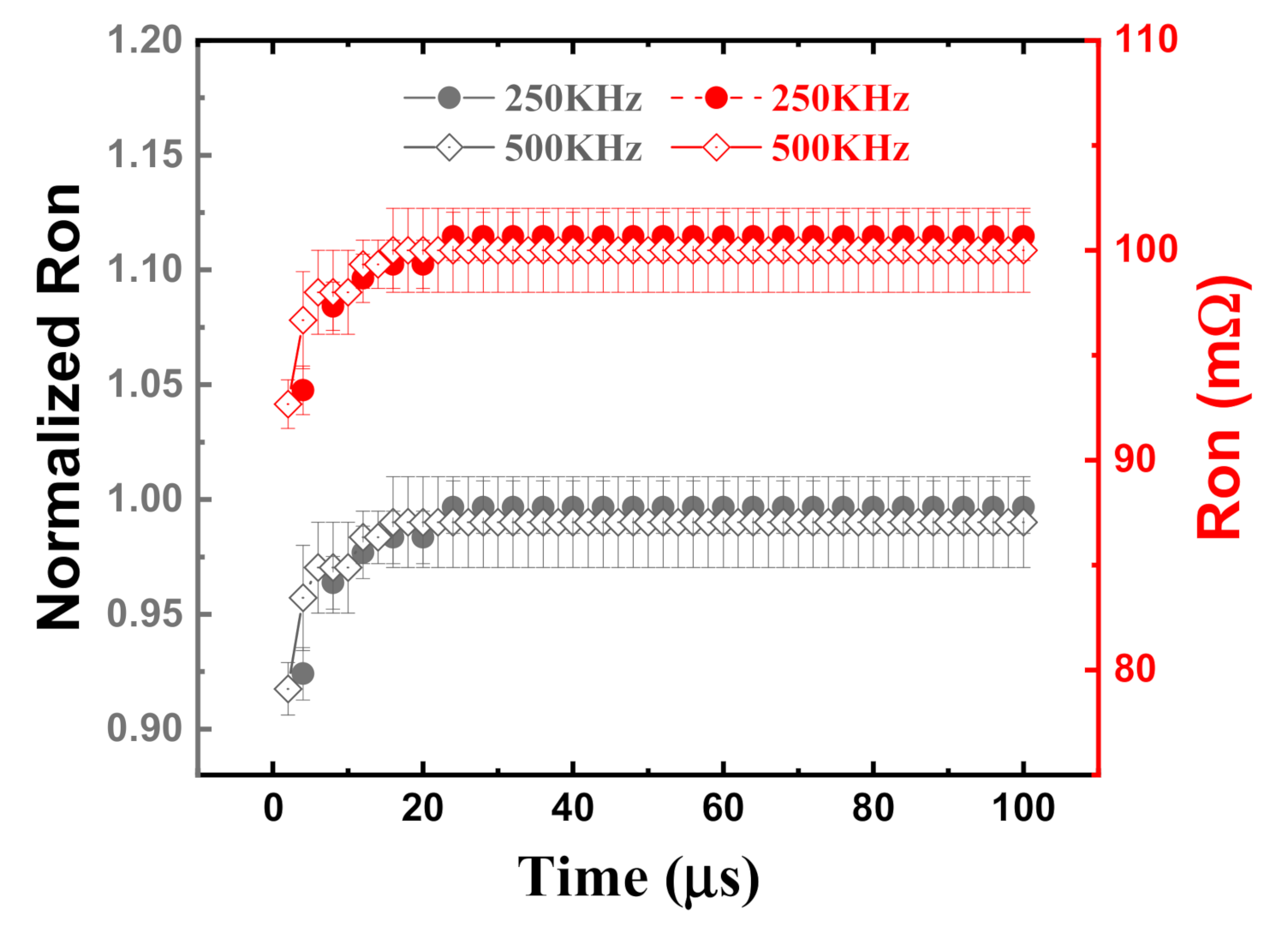

3. Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Moens, P.; Banerjee, A.; Coppens, P.; Declercq, F.; Tack, M. AlGaN/GaN power device technology for high current (100+A) and high voltage (1.2 kV). In Proceedings of the 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Prague, Czech Republic, 12–16 June 2016; pp. 455–458. [Google Scholar] [CrossRef]

- Vetury, R.; Zhang, N.Q.; Keller, S.; Mishra, U.K. The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs. IEEE Trans. Electron. Devices 2001, 48, 560–566. [Google Scholar] [CrossRef]

- Meneghini, M.; Zanoni, E.; Meneghesso, G. Gallium nitride based HEMTs for power applications: High field trapping issues. In Proceedings of the 2014 12th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Guilin, China, 28–31 October 2014; pp. 1–4. [Google Scholar] [CrossRef]

- Hwang, I.; Kim, J.; Chong, S.; Choi, H.-S.; Hwang, S.-K.; Oh, J.; Shin, J.K.; Chung, U. Impact of Channel Hot Electrons on Current Collapse in AlGaN/GaN HEMTs. IEEE Electron. Device Lett. 2013, 34, 1494–1496. [Google Scholar] [CrossRef]

- Rossetto, I.; Meneghini, M.; Tajalli, A.; Dalcanale, S.; De Santi, C.; Moens, P.; Banerjee, A.; Zanoni, E.; Meneghesso, G. Evidence of Hot-Electron Effects During Hard Switching of AlGaN/GaN HEMTs. IEEE Trans. Electron. Devices 2017, 64, 3734–3739. [Google Scholar] [CrossRef]

- Jones, E.A.; Wang, F.F.; Costinett, D. Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 707–719. [Google Scholar] [CrossRef]

- Hilt, O.; Bahat-Treidel, E.; Cho, E.; Singwald, S.; Wurfl, J. Impact of buffer composition on the dynamic on-state resistance of high-voltage AlGaN/GaN HFETs. In Proceedings of the 2012 24th International Symposium on Power Semiconductor Devices and ICs, Bruges, Belgium, 3–7 June 2012; pp. 345–348. [Google Scholar] [CrossRef]

- Zhang, W.; Xu, Z.; Zhang, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J. Evaluation of 600 V cascode GaN HEMT in device characterization and all-GaN-based LLC resonant converter. In Proceedings of the 2013 IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 15–19 September 2013; pp. 15–19. [Google Scholar] [CrossRef]

- Josifovic, I.; Popovic-Gerber, J.; Ferreira, J.A. Improving SiC JFET Switching Behavior under Influence of Circuit Parasitics. IEEE Trans. Power Electron. 2012, 27, 3843–3854. [Google Scholar] [CrossRef]

- Badawi, N.; Hilt, O.; Bahat-Treidel, E.; Bocker, J.; Wurfl, J.; Dieckerhoff, S. Investigation of the Dynamic On-State Resistance of 600 V Normally-Off and Normally-On GaN HEMTs. IEEE Trans. Ind. Appl. 2016, 52, 4955–4964. [Google Scholar] [CrossRef]

- Cai, Y.; Forsyth, A.J.; Todd, R. Impact of GaN HEMT dynamic on-state resistance on converter performance. IEEE Appl. Power Electron. Conf. Expo. (APEC) 2017, 1689–1694. [Google Scholar] [CrossRef]

- Jones, E.A.; Pozo, A. Hard-Switching Dynamic Rds,on Characterization of a GaN FET with an Active GaN-Based Clamping Circuit. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 2757–2763. [Google Scholar] [CrossRef]

- Burgos, R.; Zheng, C.; Boroyevich, D.; Wang, F. Design considerations of a fast 0-Ω gate-drive circuit for 1.2 kV SiC JFET devices in phase-leg configuration. In Proceedings of the 2009 IEEE Energy Conversion Congress and Exposition, San Jose, CA, USA, 20–24 September 2009; pp. 2293–2300. [Google Scholar] [CrossRef]

- Yao, T.; Ayyanar, R. A Multifunctional Double Pulse Tester for Cascode GaN Devices. IEEE Trans. Ind. Electron. 2017, 64, 9023–9031. [Google Scholar] [CrossRef]

- Wang, H.; Wei, J.; Xie, R.; Liu, C.; Tang, G.; Chen, K.J. Maximizing the Performance of 650-V p-GaN Gate HEMTs: Dynamic RON Characterization and Circuit Design Considerations. IEEE Trans. Power Electron. 2017, 32, 5539–5549. [Google Scholar] [CrossRef]

- Lu, B.; Palacios, T.; Risbud, D.; Bahl, S.; Anderson, D.I. Extraction of Dynamic On-Resistance in GaN Transistors: Under Soft- and Hard-Switching Conditions. In Proceedings of the 2011 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Waikoloa, HI, USA, 16–19 October 2011; pp. 1–4. [Google Scholar] [CrossRef]

- Li, R.; Wu, X.; Yang, S.; Sheng, K. Dynamic On-state Resistance Test and Evaluation of GaN Power Devices under Hard and Soft Switching Conditions by Double and Multiple Pulses. IEEE Trans. Power Electron. 2019, 34, 1044–1053. [Google Scholar] [CrossRef]

- GS66504B-650V Enhancement Mode GaN Transistor. Available online: https://gansystems.com/gan-transistors/gs66504b/ (accessed on 13 May 2021).

- Badawi, N.; Dieckerhoff, S. A new method for dynamic Ron extraction of GaN power HEMTs. In Proceedings of the PCIM Europe 2015; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management (PCIM), Nuremberg, Germany, 19–21 May 2015; pp. 1–6. [Google Scholar]

- Uren, M.J.; Karboyan, S.; Chatterjee, I.; Pooth, A.; Moens, P.; Banerjee, A.; Kuball, M. “Leaky Dielectric” Model for the Suppression of Dynamic RON in Carbon-Doped AlGaN/GaN HEMTs. IEEE Trans. Electron. Devices 2017, 64, 2826–2834. [Google Scholar] [CrossRef]

- Kaneko, S.; Kuroda, M.; Yanagihara, M.; Ikoshi, A.; Okita, H.; Morita, T.; Takana, K.; Hikita, M.; Uemoto, Y.; Takahashi, S.; et al. Current-collapse-free operations up to 850 V by GaN-GIT utilizing hole injection from drain. In Proceedings of the 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Hong Kong, China, 10–14 May 2015; pp. 41–44. [Google Scholar] [CrossRef]

- Cornigli, D.; Reggiani, S.; Gnani, E.; Gnudi, A.; Baccarani, G.; Moens, P.; Vanmeerbeek, P.; Banerjee, A.; Meneghesso, G. Numerical investigation of the lateral and vertical leakage currents and breakdown regimes in GaN-on-Silicon vertical structures. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 109–112. [Google Scholar] [CrossRef]

- Zhou, C.; Jiang, Q.; Huang, S.; Chen, K.J. Vertical Leakage/Breakdown Mechanisms in AlGaN/GaN-on-Si Devices. IEEE Electron. Device Lett. 2012, 33, 1132–1134. [Google Scholar] [CrossRef]

- Chatterjee, I.; Uren, M.J.; Karboyan, S.; Pooth, A.; Moens, P.; Banerjee, A.; Kuball, M. Lateral Charge Transport in the Carbon-Doped Buffer in AlGaN/GaN-on-Si HEMTs. IEEE Trans. Electron. Devices 2017, 64, 977–983. [Google Scholar] [CrossRef]

- Moens, P.; Liu, C.; Banerjee, A.; Vanmeerbeek, P.; Coppens, P.; Ziad, H.; Constant, A.; Li, Z.; Vleeschouwer, H.D.; RoigGuitart, J.; et al. An industrial process for 650V rated GaN-on-Si power devices using in-situ SiN as a gate dielectric. In Proceedings of the 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; pp. 374–377. [Google Scholar] [CrossRef]

- Meneghini, M.; Stocco, A.; Silvestri, R.; Ronchi, N.; Meneghesso, G.; Zanoni, E. Impact of hot electrons on the reliability of AlGaN/GaN High Electron Mobility Transistors. In Proceedings of the 2012 IEEE International Reliability Physics Symposium (IRPS), Anaheim, CA, USA, 15–19 April 2012; pp. 2C.2.1–2C.2.5. [Google Scholar] [CrossRef]

| VDC (V) | 50 | 100 | 150 | 200 | 250 | 300 | 400 |

| Inductor (μH) | 20 | 40 | 60 | 80 | 100 | 120 | 160 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, W.; Liang, Y.; Zhang, M.; Lin, F.; Wen, F.; Wang, H. Mechanism Analysis of Dynamic On-State Resistance Degradation for a Commercial GaN HEMT Using Double Pulse Test. Electronics 2021, 10, 1202. https://doi.org/10.3390/electronics10101202

Wang W, Liang Y, Zhang M, Lin F, Wen F, Wang H. Mechanism Analysis of Dynamic On-State Resistance Degradation for a Commercial GaN HEMT Using Double Pulse Test. Electronics. 2021; 10(10):1202. https://doi.org/10.3390/electronics10101202

Chicago/Turabian StyleWang, Wei, Yan Liang, Minghui Zhang, Fang Lin, Feng Wen, and Hongxing Wang. 2021. "Mechanism Analysis of Dynamic On-State Resistance Degradation for a Commercial GaN HEMT Using Double Pulse Test" Electronics 10, no. 10: 1202. https://doi.org/10.3390/electronics10101202

APA StyleWang, W., Liang, Y., Zhang, M., Lin, F., Wen, F., & Wang, H. (2021). Mechanism Analysis of Dynamic On-State Resistance Degradation for a Commercial GaN HEMT Using Double Pulse Test. Electronics, 10(10), 1202. https://doi.org/10.3390/electronics10101202