A New Type of DC-DC Buck Converter with Soft Start Function and Reduced Voltage Stress

Abstract

1. Introduction

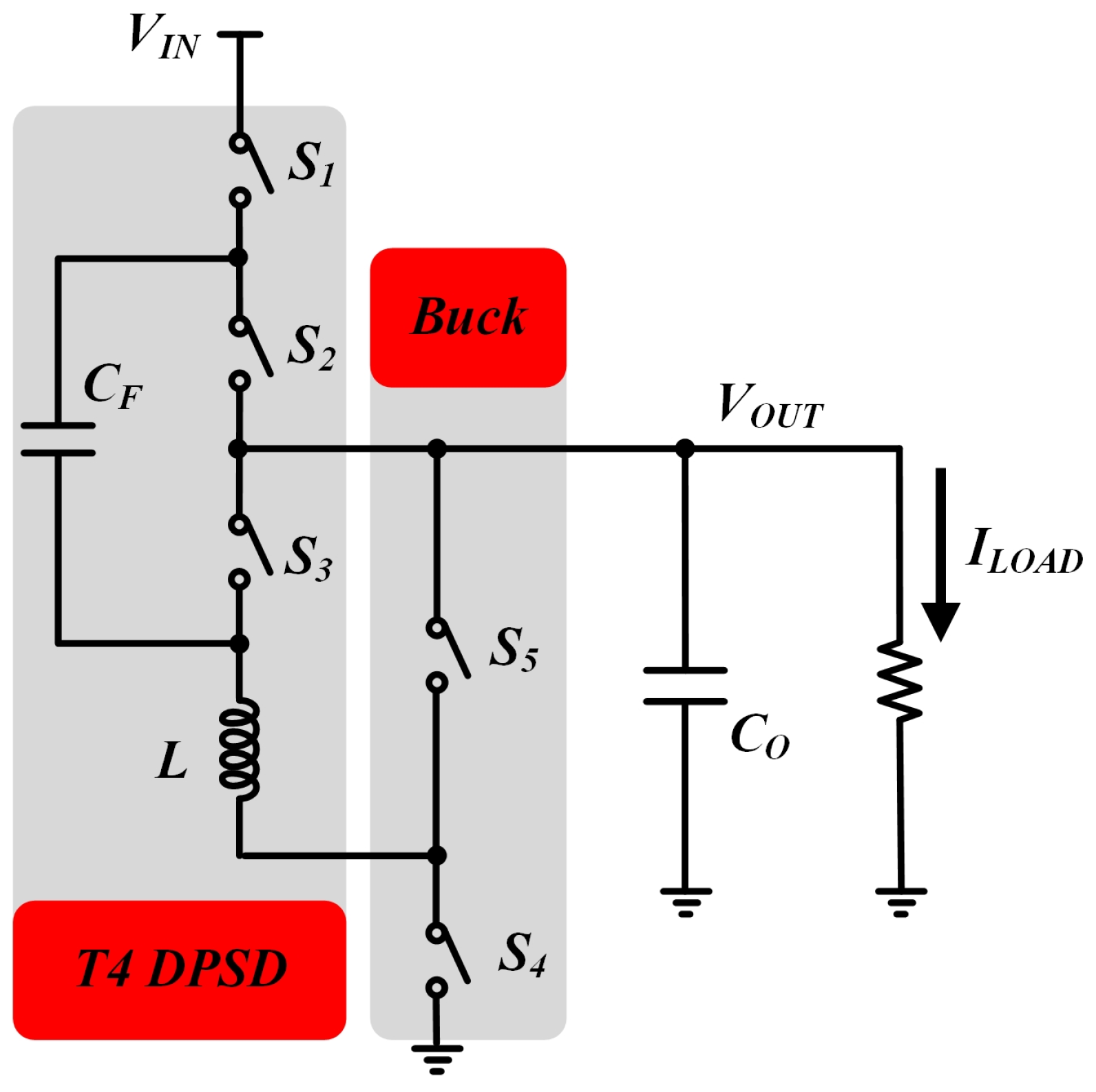

2. The Proposed Topology

2.1. Topology Transformation

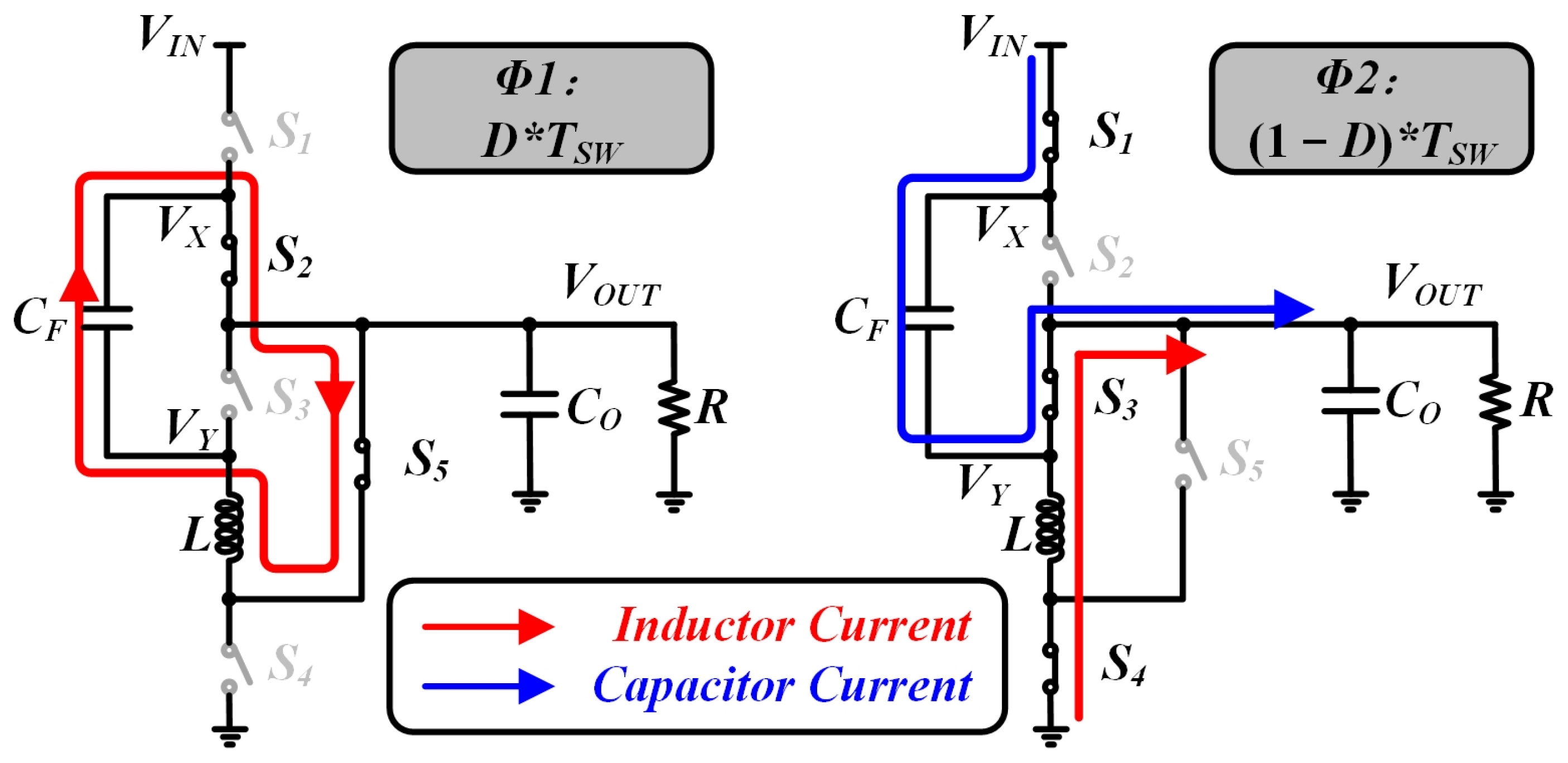

2.2. Operation of the Proposed Topology

2.3. Step-Down Conversion Ratios

2.4. Switch Voltage Stress Reduction

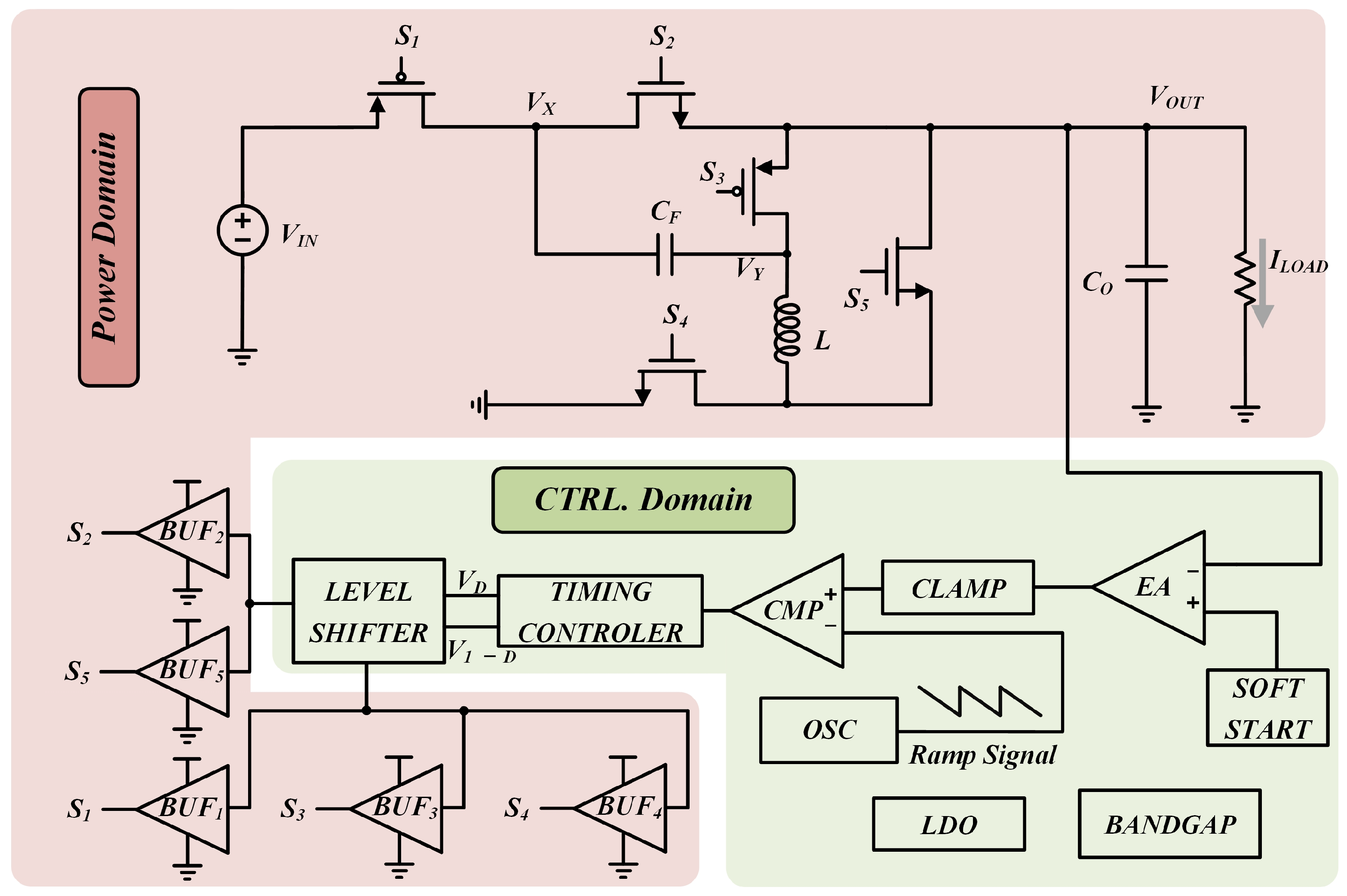

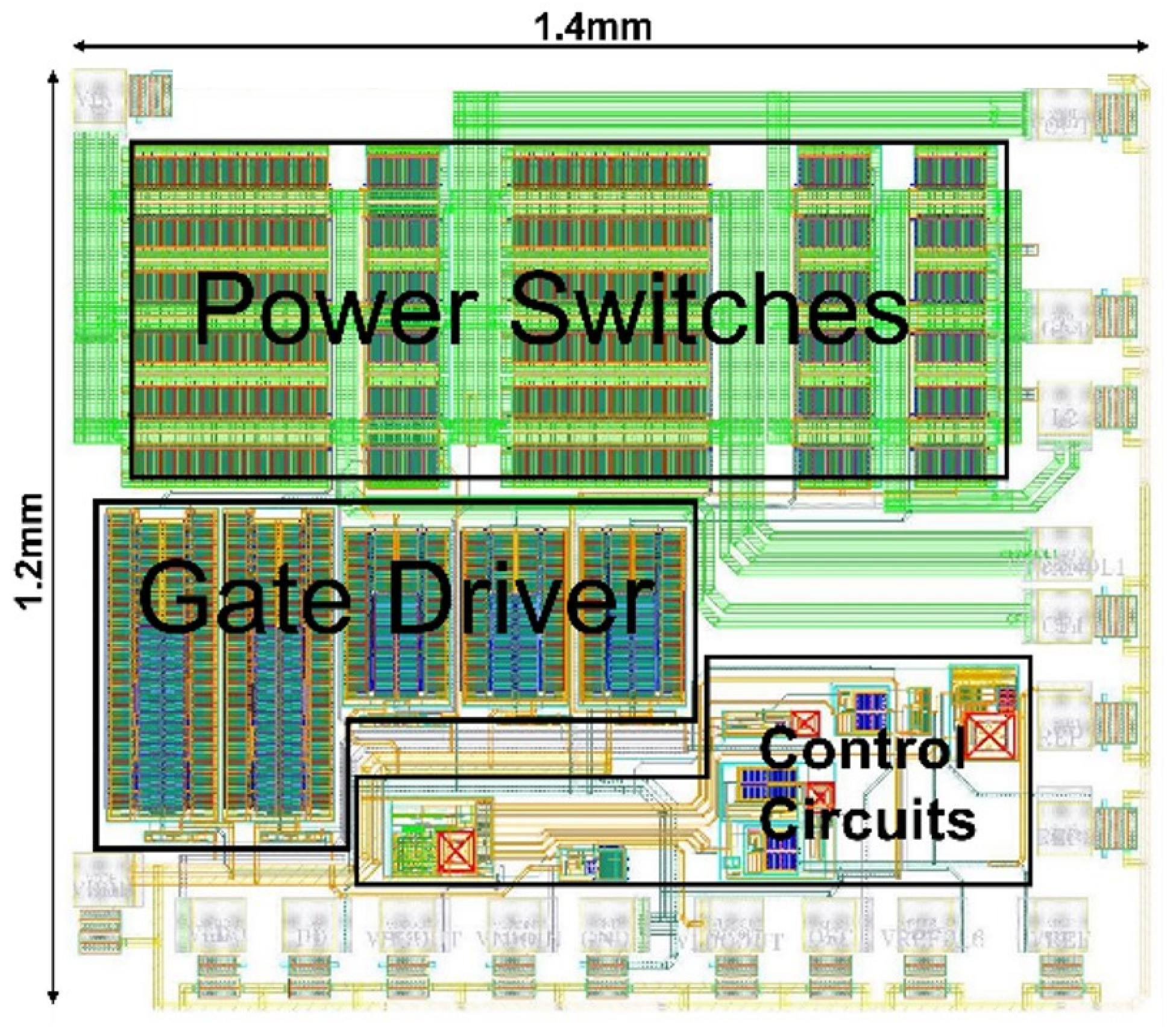

3. Circuit Implementation

3.1. Control Circuit

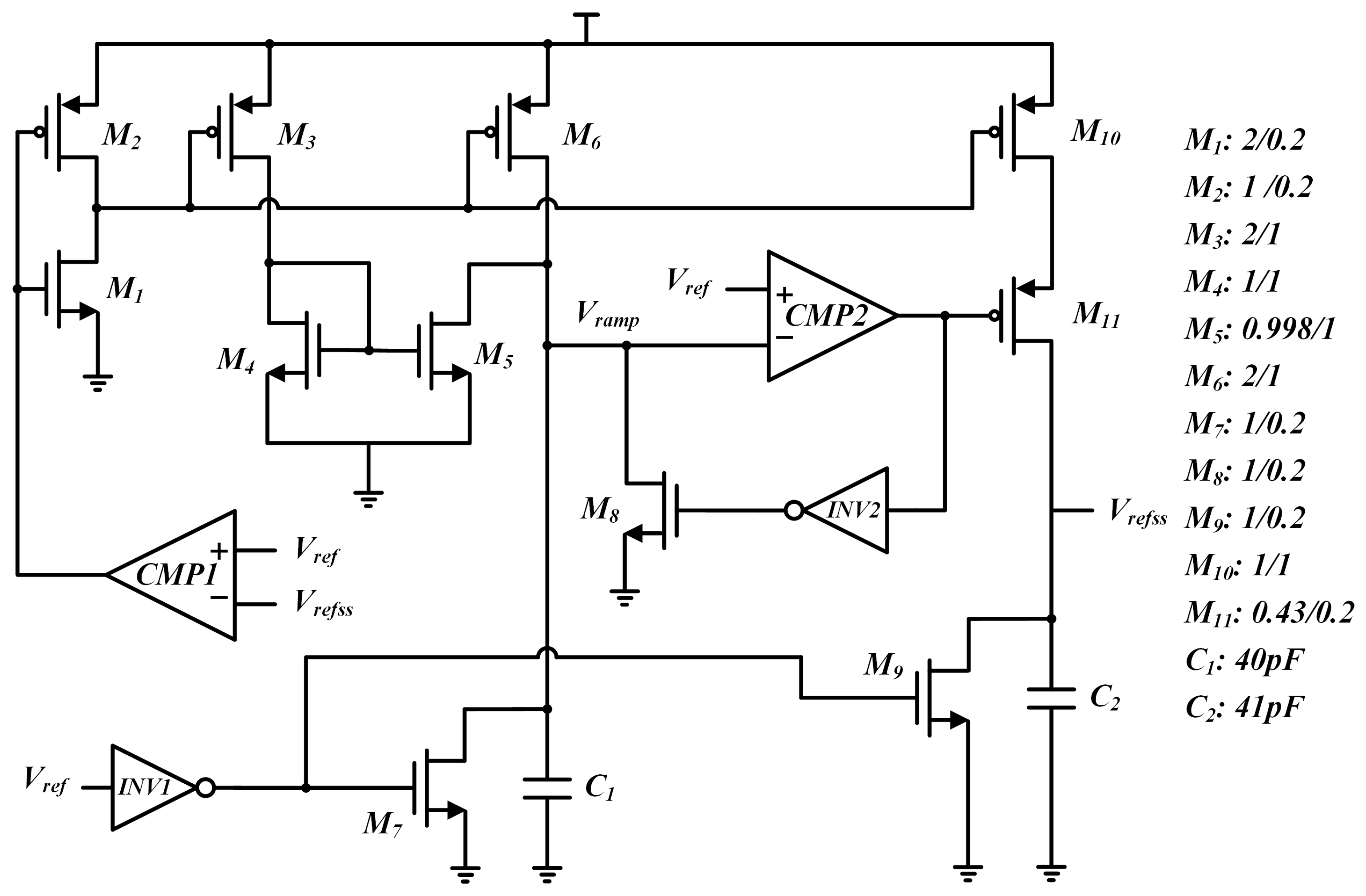

3.2. Soft-Start Circuit

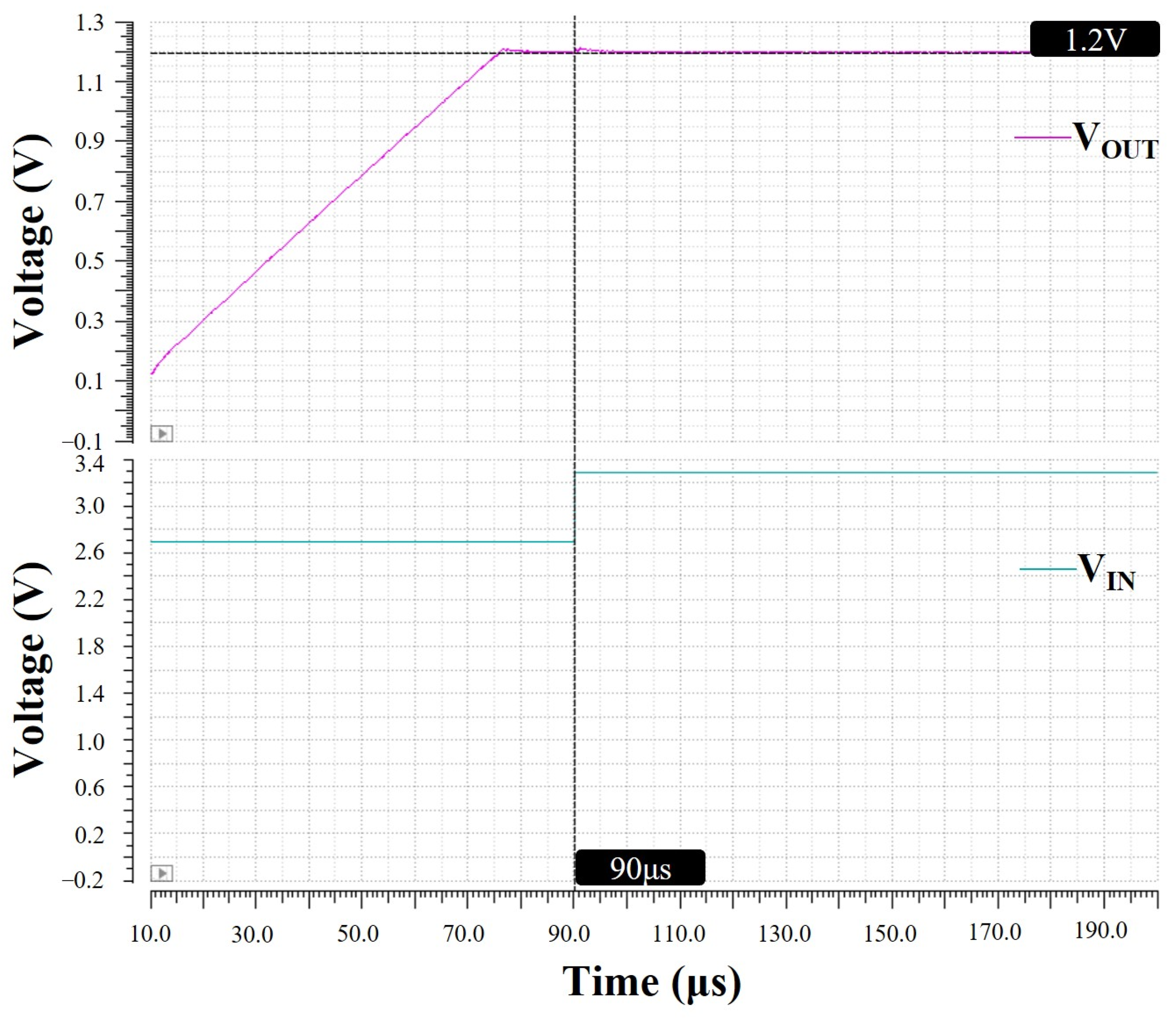

4. Simulation Result and Discussions

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Ahsanuzzaman, S.M.; Prodić, A.; Johns, D.A. An Integrated High-Density Power Management Solution for Portable Applications Based on a Multioutput Switched-Capacitor Circuit. IEEE Trans. Power Electron. 2016, 31, 4305–4323. [Google Scholar] [CrossRef]

- Renz, P.; Kaufmann, M.; Lueders, M.; Wicht, B. Switch Stacking in Power Management ICs. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 3735–3743. [Google Scholar] [CrossRef]

- Shi, C.; Walker, B.C.; Zeisel, E.; Hu, B.; McAllister, G.H. A Highly Integrated Power Management IC for Advanced Mobile Applications. IEEE J. Solid-State Circuits 2007, 42, 1723–1731. [Google Scholar]

- Meng, F.; Disney, D.; Liu, B.; Volkan, Y.B.; Zhou, A.; Liang, Z.; Yi, X.; Selvaraj, S.L.; Peng, L.; Ma, K.; et al. Heterogeneous Integration of GaN and BCD Technologies and Its Applications to High Conversion-Ratio DC-DC Boost Converter IC. IEEE Trans. Power Electron. 2019, 34, 1993–1996. [Google Scholar] [CrossRef]

- Disney, D.; Shen, Z.J. Review of Silicon Power Semiconductor Technologies for Power Supply on Chip and Power Supply in Package Applications. IEEE Trans. Power Electron. 2013, 28, 4168–4181. [Google Scholar] [CrossRef]

- Wu, P.Y.; Tsui, S.Y.S.; Mok, P.K.T. Area- and Power-Efficient Monolithic Buck Converters with Pseudo-Type III Compensation. IEEE J. Solid-State Circuits 2010, 45, 1446–1455. [Google Scholar] [CrossRef]

- Li, Z.; Lin, Z.; Meng, F. A Single Active Phase Hybrid Buck Converter with Reduced Voltage Stress and Wide Voltage Conversion Ratios for Integrated Terahertz Systems. In Proceedings of the 5th China and International Young Scientist Terahertz Conference, Chengdu, China, 22–24 March 2024; Chang, C., Zhang, Y., Zhao, Z., Zhu, Y., Eds.; Springer Science and Business Media, LLC: Singapore, 2024; Volume 2, pp. 200–204. [Google Scholar]

- Du, M.; Lee, H.; Liu, J. A 5MHz 91% Peak-Power-Efficiency Buck Regulator with Auto-Selectable Peak and Valley-Current Control. IEEE J. Solid-State Circuits 2011, 46, 1928–1939. [Google Scholar] [CrossRef]

- Son, H.S.; Kim, J.K.; Lee, J.B.; Moon, S.S.; Park, J.H.; Lee, S.H. A New Buck–Boost Converter with Low-Voltage Stress and Reduced Conducting Components. IEEE Trans. Ind. Electron. 2017, 64, 7030–7038. [Google Scholar] [CrossRef]

- Pan, C.T.; Chuang, C.F.; Chu, C.C. A Novel Transformerless Interleaved High Step-Down Conversion Ratio DC-DC Converter with Low Switch Voltage Stress. IEEE Trans. Ind. Electron. 2014, 61, 5290–5299. [Google Scholar] [CrossRef]

- Kozak, J.P.; Song, Q.; Zhang, R.; Ma, Y.; Liu, J.; Li, Q.; Saito, W.; Zhang, Y. Degradation and Recovery of GaN HEMTs in Overvoltage Hard Switching Near Breakdown Voltage. IEEE Trans. Power Electron. 2023, 38, 435–446. [Google Scholar] [CrossRef]

- Hata, K.; Yamauchi, Y.; Sai, T.; Sakurai, T.; Takamiya, M. 48V-to-12V Dual-Path Hybrid DC-DC Converter. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020; pp. 2279–2284. [Google Scholar]

- Zhen, S.; Yang, R.; Wu, D.; Cheng, Y.; Luo, P.; Zhang, B. Design of Hybrid Dual-Path DC-DC Converter with Wide Input Voltage Efficiency Improvement. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Republic of Korea, 22–28 May 2021; pp. 1–5. [Google Scholar]

- Cai, G.; Lu, Y.; Martins, R.P. An SC-Parallel-Inductor Hybrid Buck Converter with Reduced Inductor Voltage and Current. IEEE J. Solid-State Circuits 2023, 58, 1758–1768. [Google Scholar] [CrossRef]

- Zhang, D.; Sha, D.; Gao, C.; Liu, X.; Long, H.; Tang, G.; Zhao, Y.; Gao, Y. A Closed-Loop Soft Start up Strategy to Suppress Inrush Current for Full-Bridge Modular Multilevel Converters. IEEE Trans. Power Electron. 2024, 39, 14787–14799. [Google Scholar] [CrossRef]

- Al-Shyoukh, M.; Lee, H. A Compact Fully-Integrated Extremum-Selector-Based Soft-Start Circuit for Voltage Regulators in Bulk CMOS Technologies. IEEE Trans. Circuits Syst. II Express Briefs 2010, 57, 818–822. [Google Scholar] [CrossRef]

- Goyal, S.; Wadhwa, S.K.; Tripathi, D. An RC charging based Soft-Start circuit for Voltage Regulators. In Proceedings of the 2022 IEEE Region 10 Symposium (TENSYMP), Mumbai, India, 1–3 July 2022; pp. 1–4. [Google Scholar]

- Al-Shyoukh, M.; Lee, H. A Compact Ramp-Based Soft-Start Circuit for Voltage Regulators. IEEE Trans. Circuits Syst. II Express Briefs 2009, 56, 535–539. [Google Scholar] [CrossRef]

- Liu, P.J.; Hsu, Y.C.; Chang, Y.H. A Current-Mode Buck Converter with a Pulse-skipping Soft-start Circuit. In Proceedings of the 2013 IEEE 10th International Conference on Power Electronics and Drive Systems (PEDS), Kitakyushu, Japan, 22–25 April 2013; pp. 262–265. [Google Scholar]

- Jing, X.; Mok, P.K.T. Soft-Start Circuit with Duty Ratio Controlled Voltage Clamping and Adaptive Sizing Technique for Integrated DC-DC Converters. In Proceedings of the 2010 IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), Hong Kong, China, 15–17 December 2010; pp. 1–4. [Google Scholar]

- Liu, P.J.; Hsu, C.Y.; Chang, Y.H. Techniques of Dual-Path Error Amplifier and Capacitor Multiplier for On-Chip Compensation and Soft-Start Function. IEEE Trans. Power Electron. 2015, 30, 1403–1410. [Google Scholar] [CrossRef]

- Tiwari, A.A.; Mishra, D.K. A DC-DC Boost Converter with Soft Start Function and DPEA Technique Using 180nm Technology. In Proceedings of the 2017 International Conference on Information, Communication, Instrumentation and Control (ICICIC), Indore, India, 17–19 August 2017; pp. 1–6. [Google Scholar]

- Magni, G.; Melillo, P.; Bertolini, A.; Leoncini, M.; Ghioni, M. A 10-MHz Three-Level Buck Converter with Dual-Loop Time-Based Control and Flying Capacitor Voltage-Balance for Fast DVS. In Proceedings of the 2024 19th Conference on Ph.D Research in Microelectronics and Electronics (PRIME), Larnaca, Cyprus, 9–12 June 2024; pp. 1–4. [Google Scholar]

- Li, W.S.; Zhou, D.C.; Yan, H.; Zhang, J.F.; Ma, H.H.; Chen, C.; Huang, J.B.; Liu, X.M.; Li, W.P.; Wu, M.; et al. Dynamic Rdson and Vth Free 15 V E-mode GaN HEMT Delivering Low sFOM of 13.1 mΩ•nC and over 90% Efficiency at 10 MHz for Buck Converter. In Proceedings of the 2022 IEEE 34th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vancouver, BC, Canada, 22–25 May 2022; pp. 161–164. [Google Scholar]

- Agarwal, S.; Maity, A. A 10-MHz Current-Mode Fixed-Frequency Hysteretic Controlled DC-DC Converter with Fast Transient Response. In Proceedings of the 2019 IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS), Dallas, TX, USA, 4–7 August 2019; pp. 945–948. [Google Scholar]

- Crupi, G.; Schreurs, D.M.M.-P.; Caddemi, A. Effects of Gate-Length Scaling on Microwave MOSFET Performance. Electronics 2017, 6, 62. [Google Scholar] [CrossRef]

- Zhu, Q.; Zhang, T.; Wang, J.; Cheng, Y. Design and Layout realization of Power MOSFET in Switching Power Supply. In Proceedings of the 2023 5th International Conference on Electronic Engineering and Informatics (EEI), Wuhan, China, 30 June–2 July 2023; pp. 99–103. [Google Scholar]

| Parameter | Value |

|---|---|

| Output capacitor, Co | 5 µF |

| Inductor, L | 380 nH |

| Flying capacitor, CF | 80 nF |

| NMOS power switch | 35 × 600 µm/0.5 um |

| PMOS power switch | 70 × 600 µm/0.5 um |

| Output voltage, VOUT | 1.2 V |

| Expected load current | 200 mA |

| This Work * | [8] JSSC 2011 # | [12] APEC 2020 # | [13] ISCAS 2021 * | [14] JSSC 2022 # | |

|---|---|---|---|---|---|

| Process | 65 nm CMOS | 0.35 µm CMOS | PCB | 0.18 µm BCD | 65 nm CMOS |

| Topology | DPSD with Auxiliary Switches | Buck | DPSD | DPSD | CPL-Buck |

| Frequency | 10 MHz | 5 MHz | 100 kHz | 1 MHz | 2 MHz |

| Peak Efficiency | 90.6% | 91% | 97.1% | 95.6% | 92.9% |

| Input Voltage [V] | 2.7–4 | 2.7–4.2 | 48 | 2.7–5 | 3.0–4.2 |

| Output Voltage [V] | 1.2 | N/A | 12 | 1.2 | 0.6–1.0 |

| Number of Power Switches | 5 | 2 | 3 | 3 | 6 |

| Main Switch Voltage Stress [V] | VIN–VOUT, VOUT | VIN | VIN–VOUT | VIN–VOUT | VIN–VOUT, VOUT |

| Topology VCRs | D | D | D/(1 + D) | D/(1 + D) | D/(1 + 2D) or D/(1 + D) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, X.; Li, Z.; Lin, Z.; Meng, F. A New Type of DC-DC Buck Converter with Soft Start Function and Reduced Voltage Stress. J. Low Power Electron. Appl. 2025, 15, 29. https://doi.org/10.3390/jlpea15020029

Wang X, Li Z, Lin Z, Meng F. A New Type of DC-DC Buck Converter with Soft Start Function and Reduced Voltage Stress. Journal of Low Power Electronics and Applications. 2025; 15(2):29. https://doi.org/10.3390/jlpea15020029

Chicago/Turabian StyleWang, Xin, Zishuo Li, Zhen Lin, and Fanyi Meng. 2025. "A New Type of DC-DC Buck Converter with Soft Start Function and Reduced Voltage Stress" Journal of Low Power Electronics and Applications 15, no. 2: 29. https://doi.org/10.3390/jlpea15020029

APA StyleWang, X., Li, Z., Lin, Z., & Meng, F. (2025). A New Type of DC-DC Buck Converter with Soft Start Function and Reduced Voltage Stress. Journal of Low Power Electronics and Applications, 15(2), 29. https://doi.org/10.3390/jlpea15020029