A 0.15-to-0.5 V Body-Driven Dynamic Comparator with Rail-to-Rail ICMR

Abstract

1. Introduction

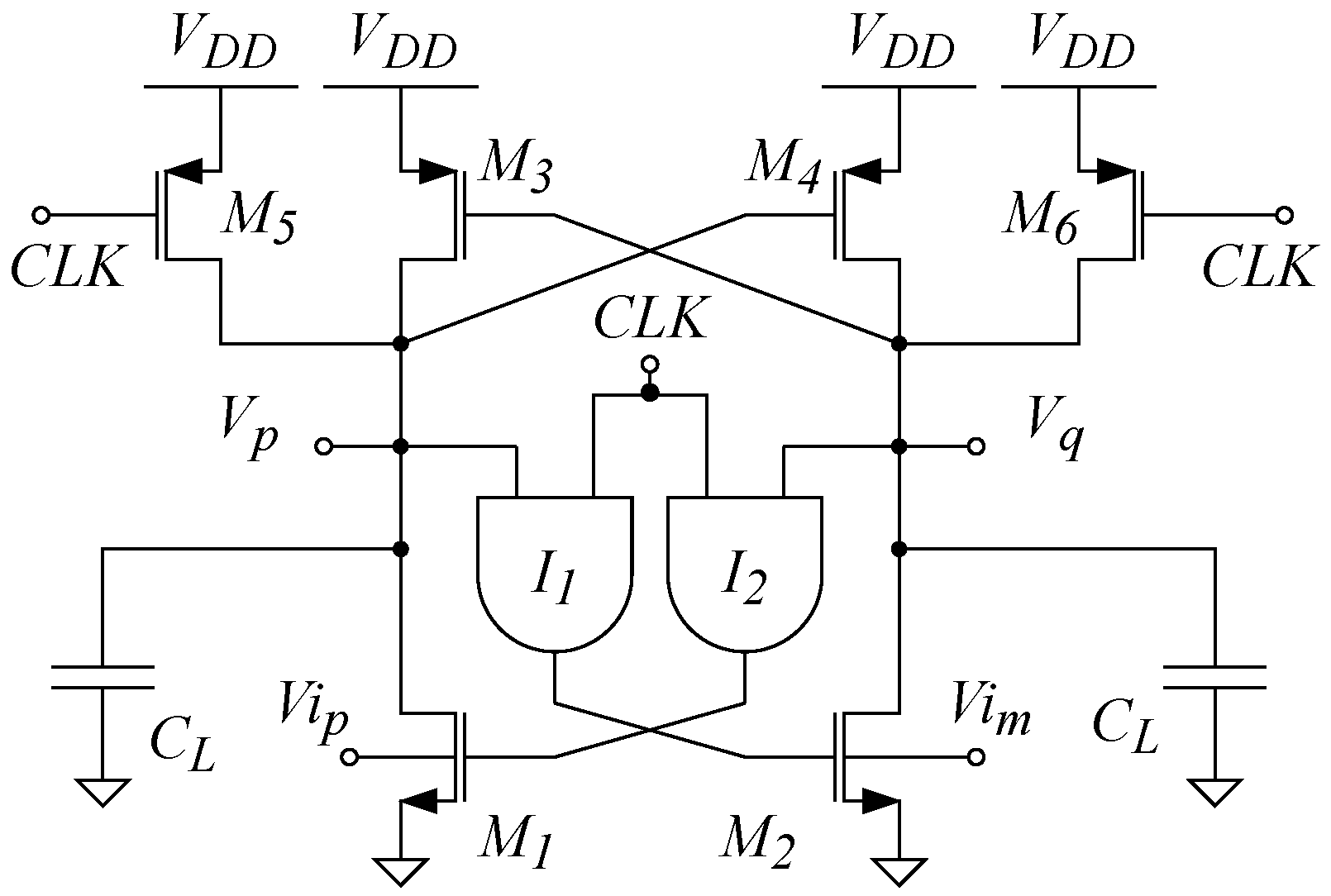

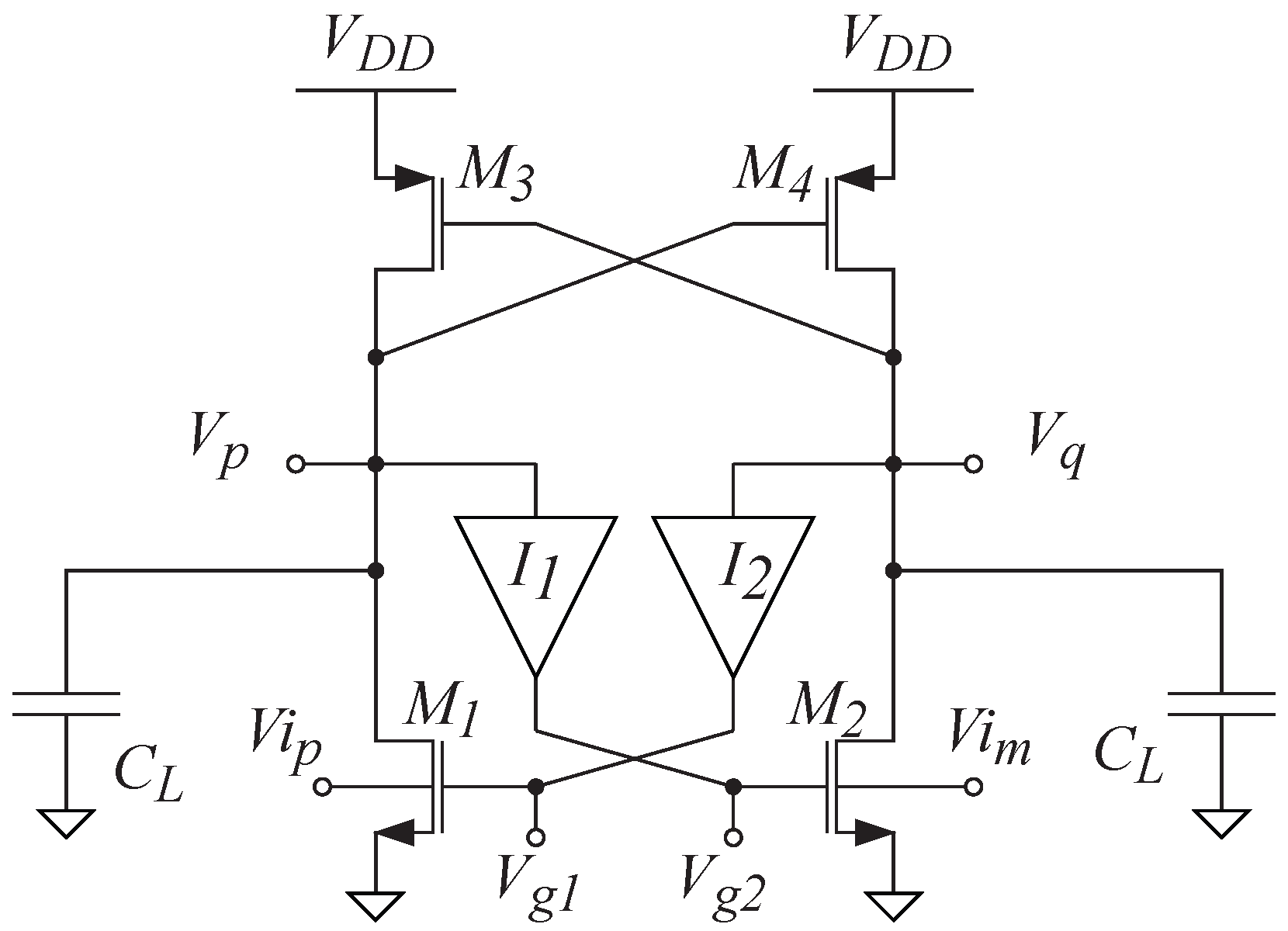

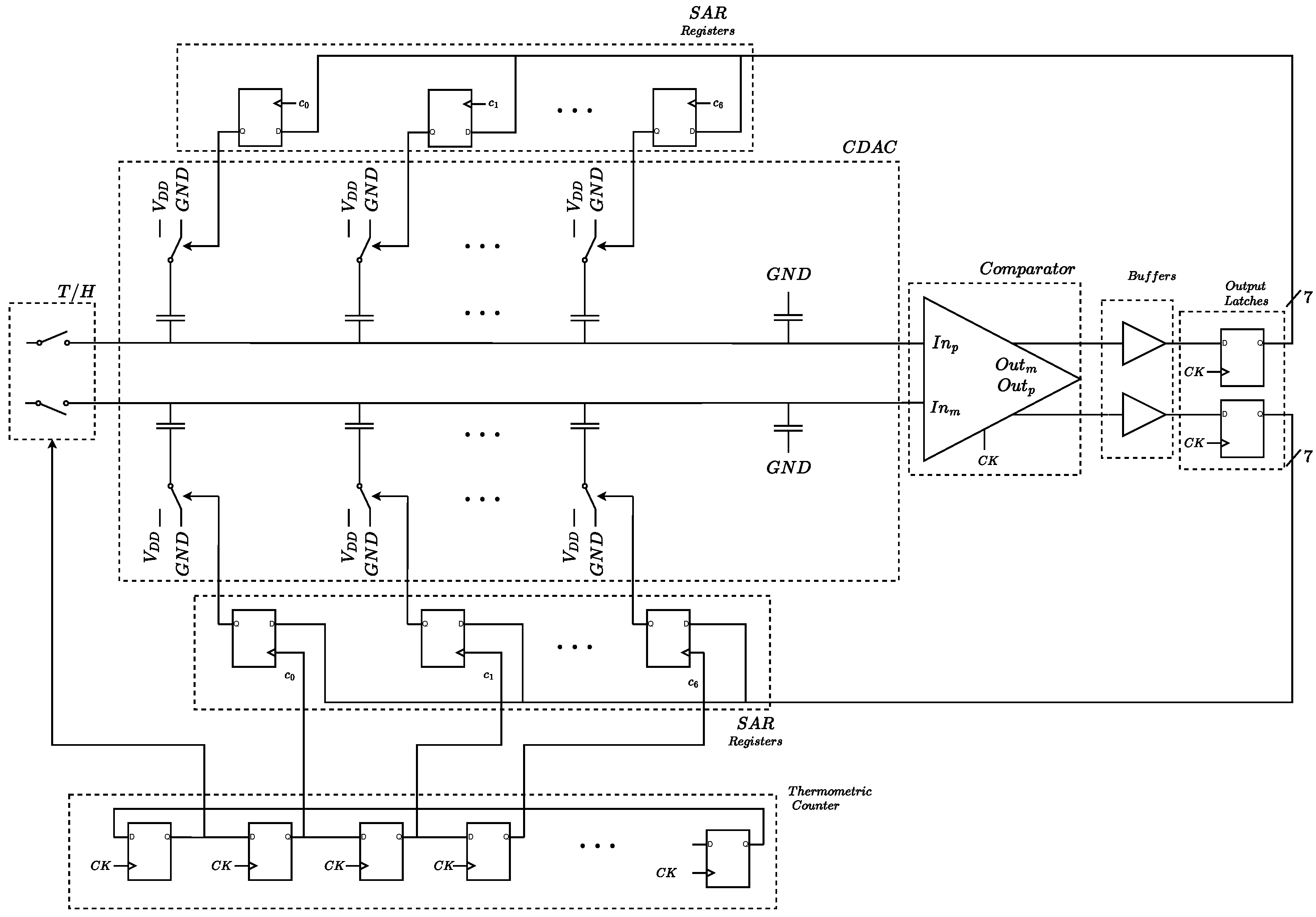

2. Proposed Comparator Topology

- Reset Phase: in the reset phase, the clock is low; hence the two NMOS are turned off, whereas the two PMOS pump current in the output nodes , charging the output parasitic capacitances to . In this phase, the PMOS-driven SR-latch holds the previous data due to the positive feedback of .

- Evaluation Phase: in the evaluation phase, the two NMOS are turned on, whereas the PMOS are turned off. In this phase, given the difference between the two body voltages of , a differential current is generated, and the positive feedback forced by sets the outputs to and ground according to the sign of the input differential signal. In this condition, the feedback through the AND gates turns off one of the input devices, , thus, avoiding static power consumption. The SR-latch senses the differential output voltage and unbalances the outputs accordingly.

3. Analysis of the Delay

3.1. Preamplification

3.2. Regeneration

- The first term on the left side of Equation (14) shows that the initial difference will be regenerated exponentially until the outputs are saturated. The second term, instead, vanishes as and is, thus, negligible.

- It is easy to verify that if the AND gates were not used, the regeneration time constant would be , which is greater than . This confirms that not only the addition of the AND gate improves power consumption by cutting the conductive path between and ground, but it also provides an advantage in terms of delay because it speeds up regeneration. The improvement with respect to the version without AND gates depends on the ratio : the smaller is compared to , the larger the reduction in delay that is obtained by adding the AND gates. This is in accordance with intuition because the advantage derived from the AND gates becomes larger as their delay decreases.

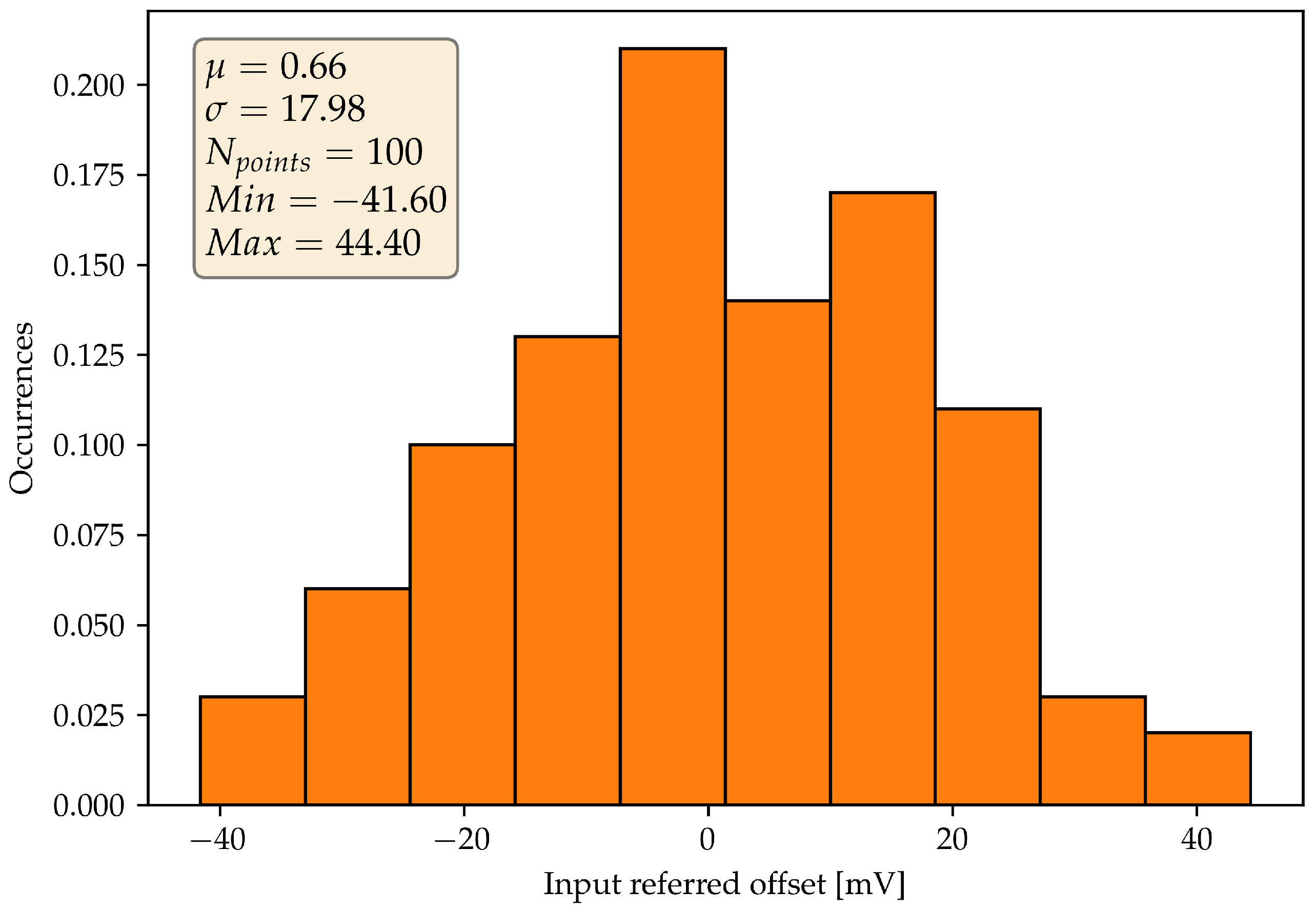

3.3. Analysis of the Input Referred Offset vs. Mismatch Variations

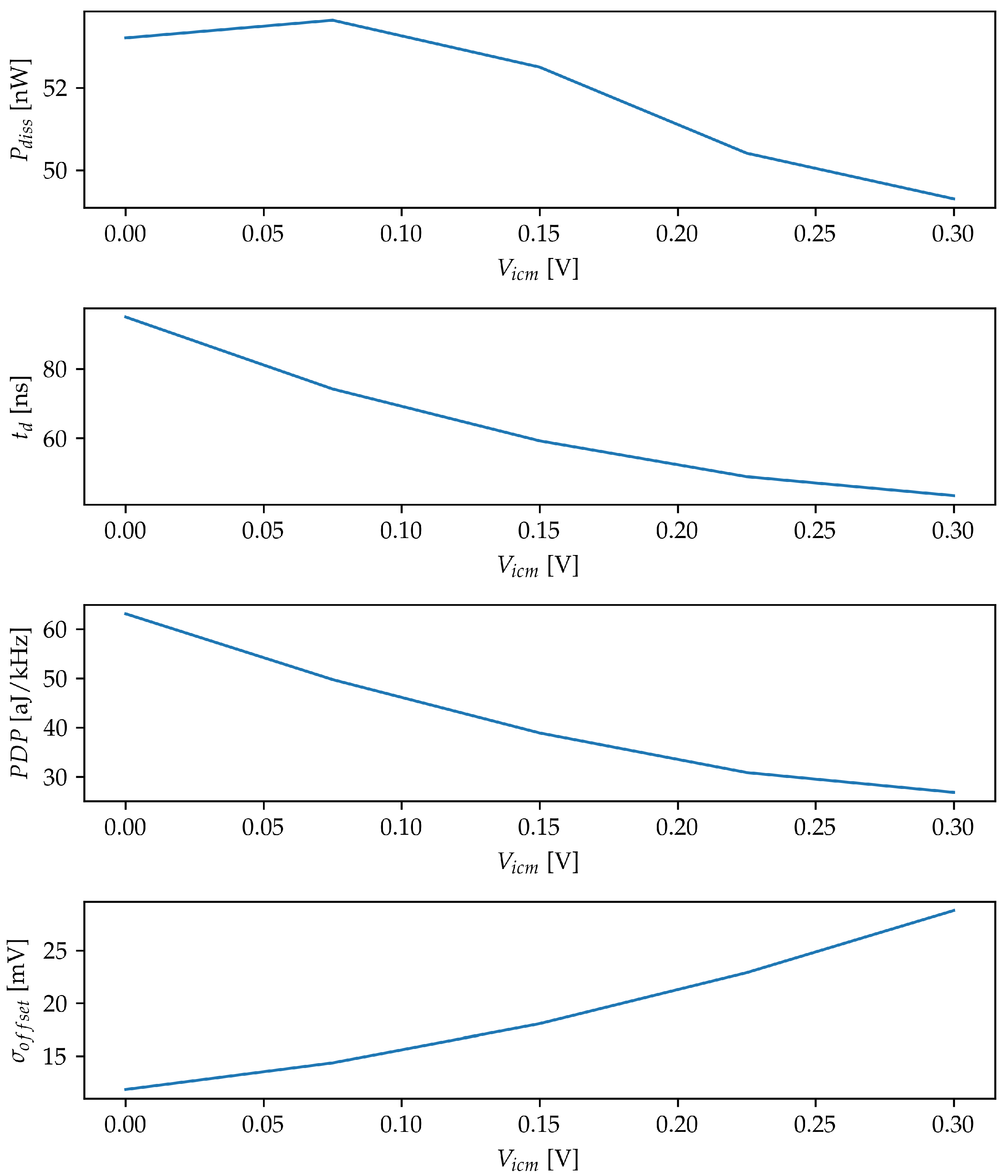

4. Simulation Results

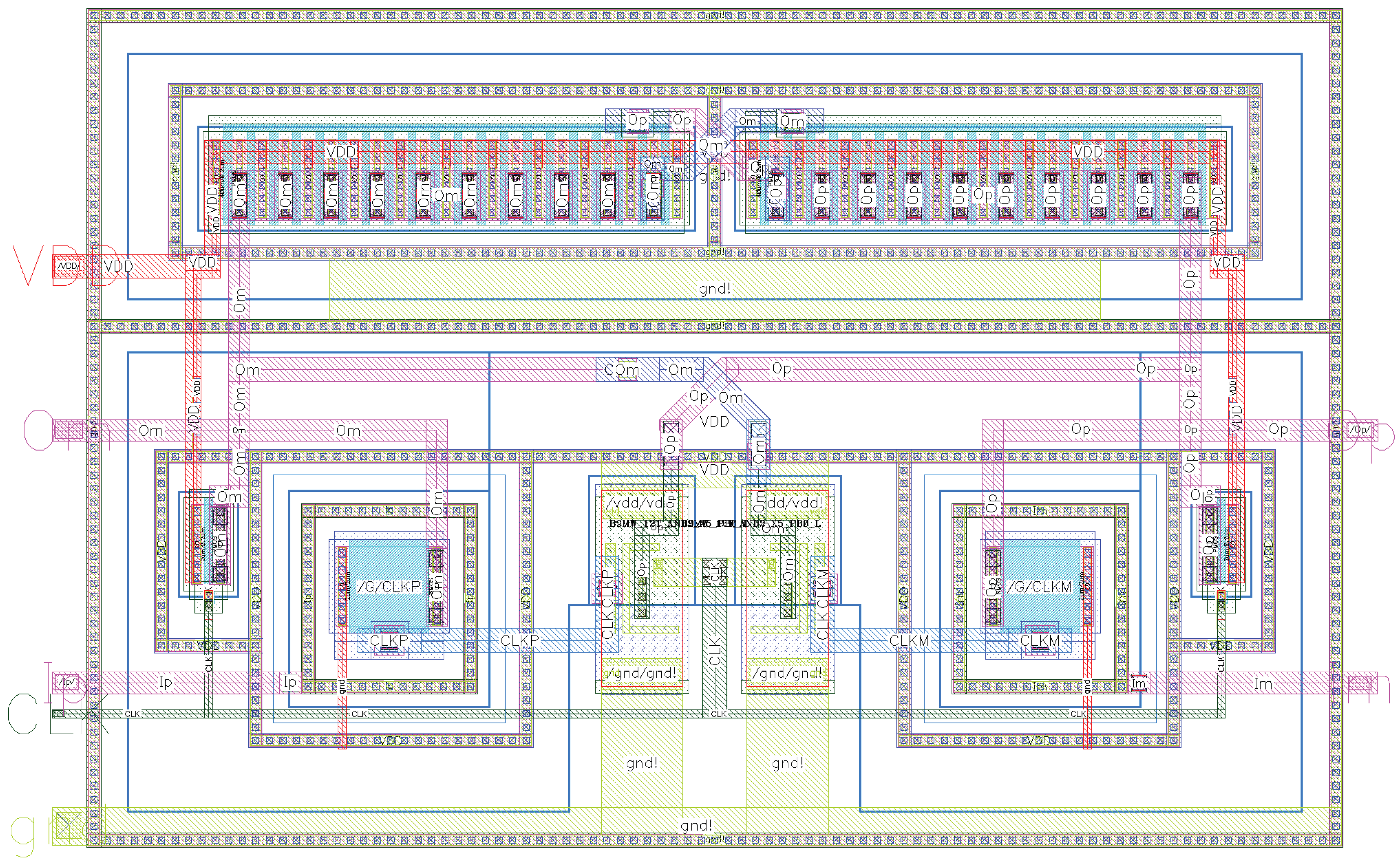

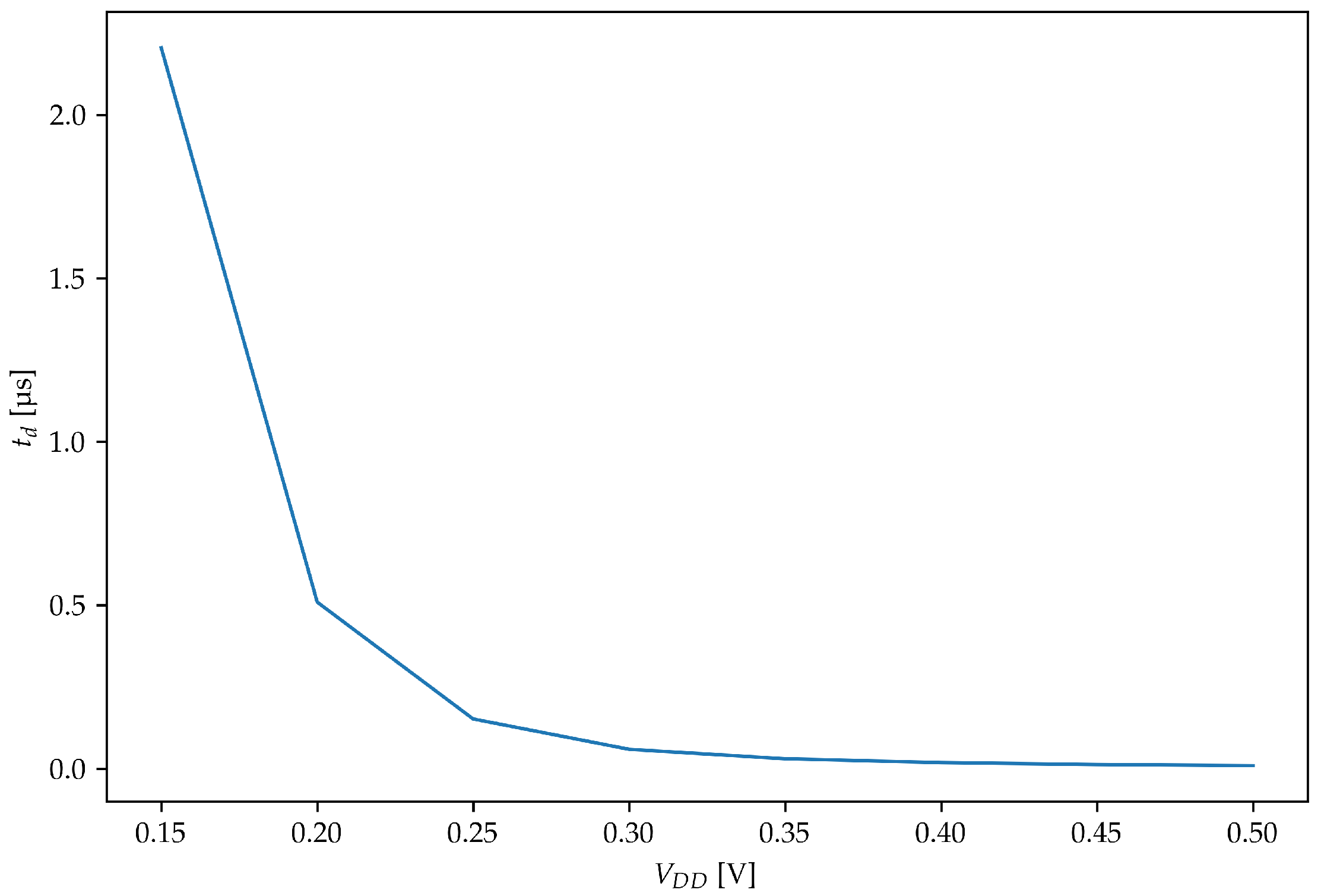

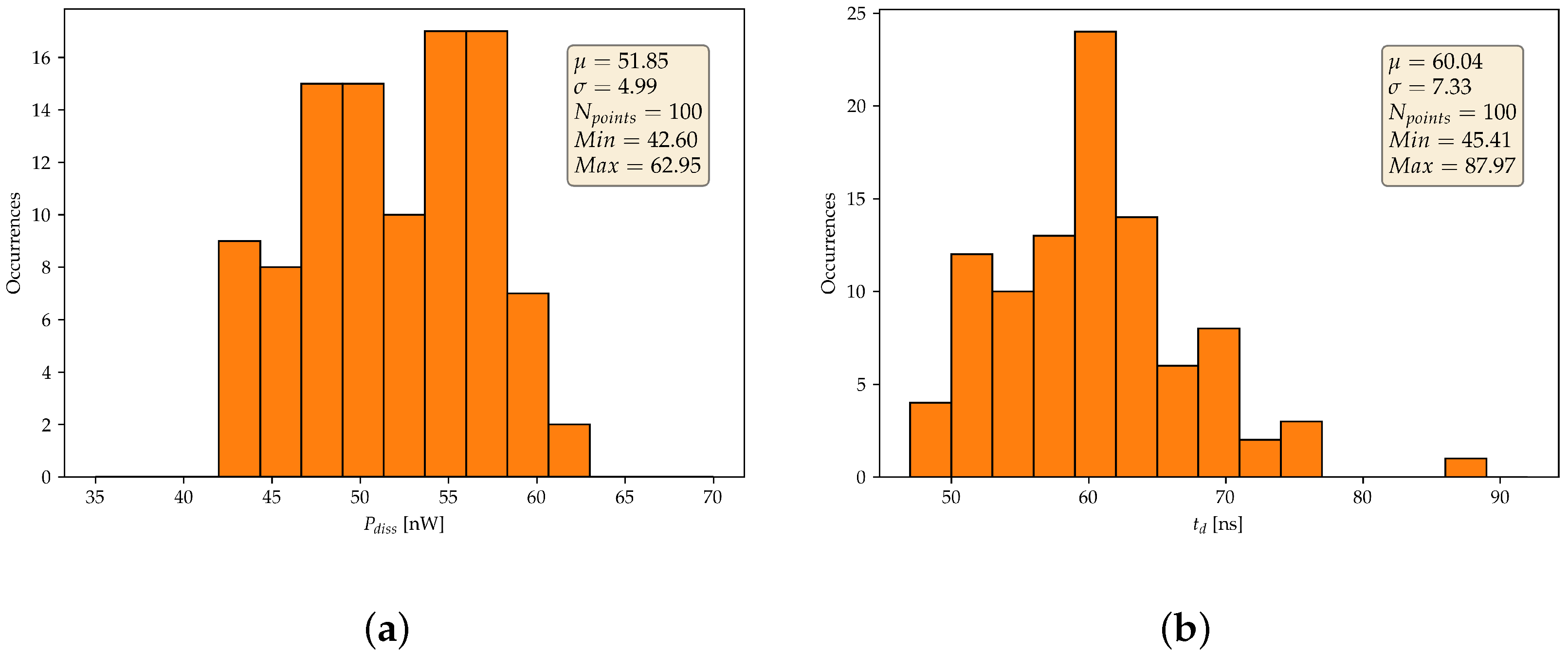

4.1. Comparator

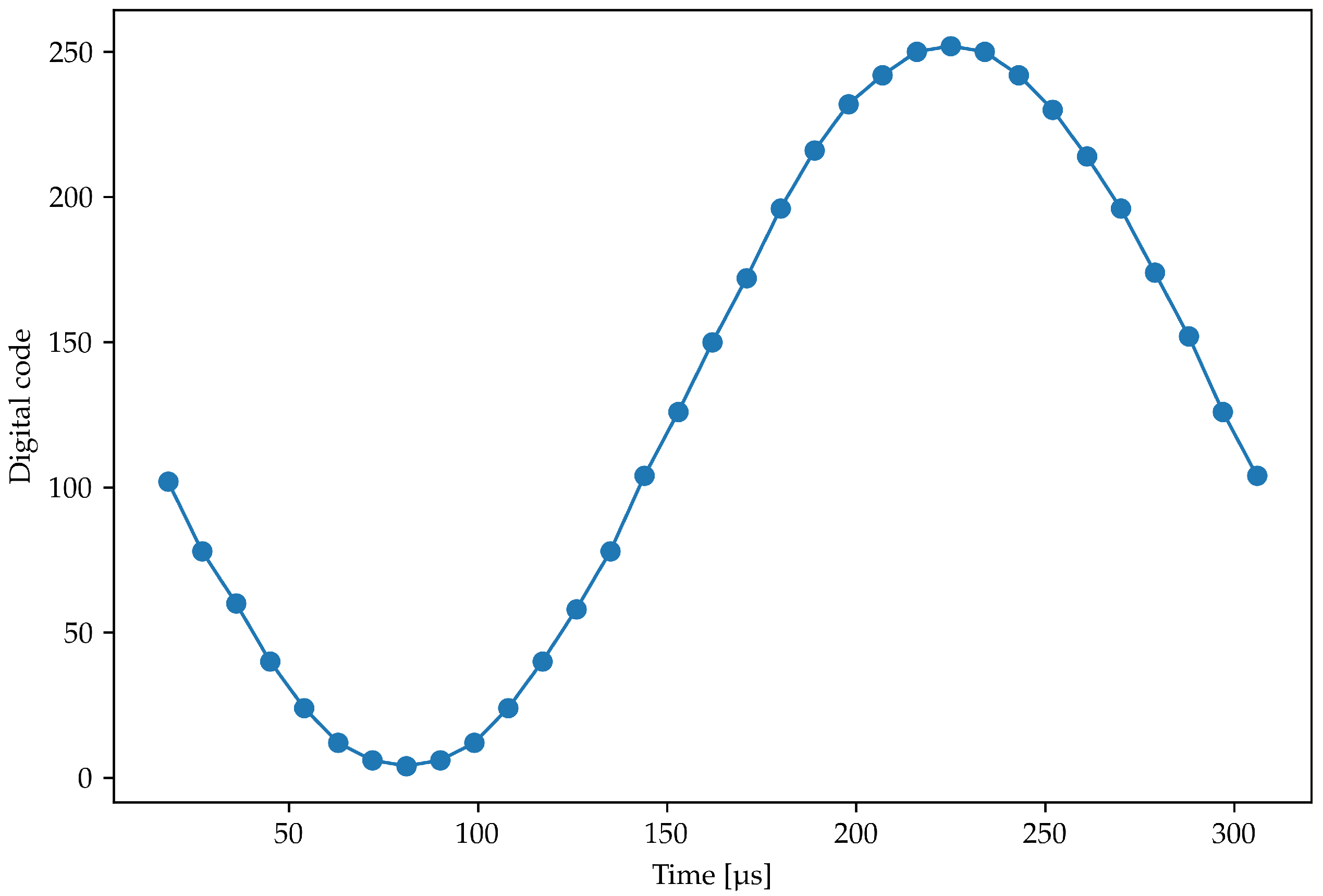

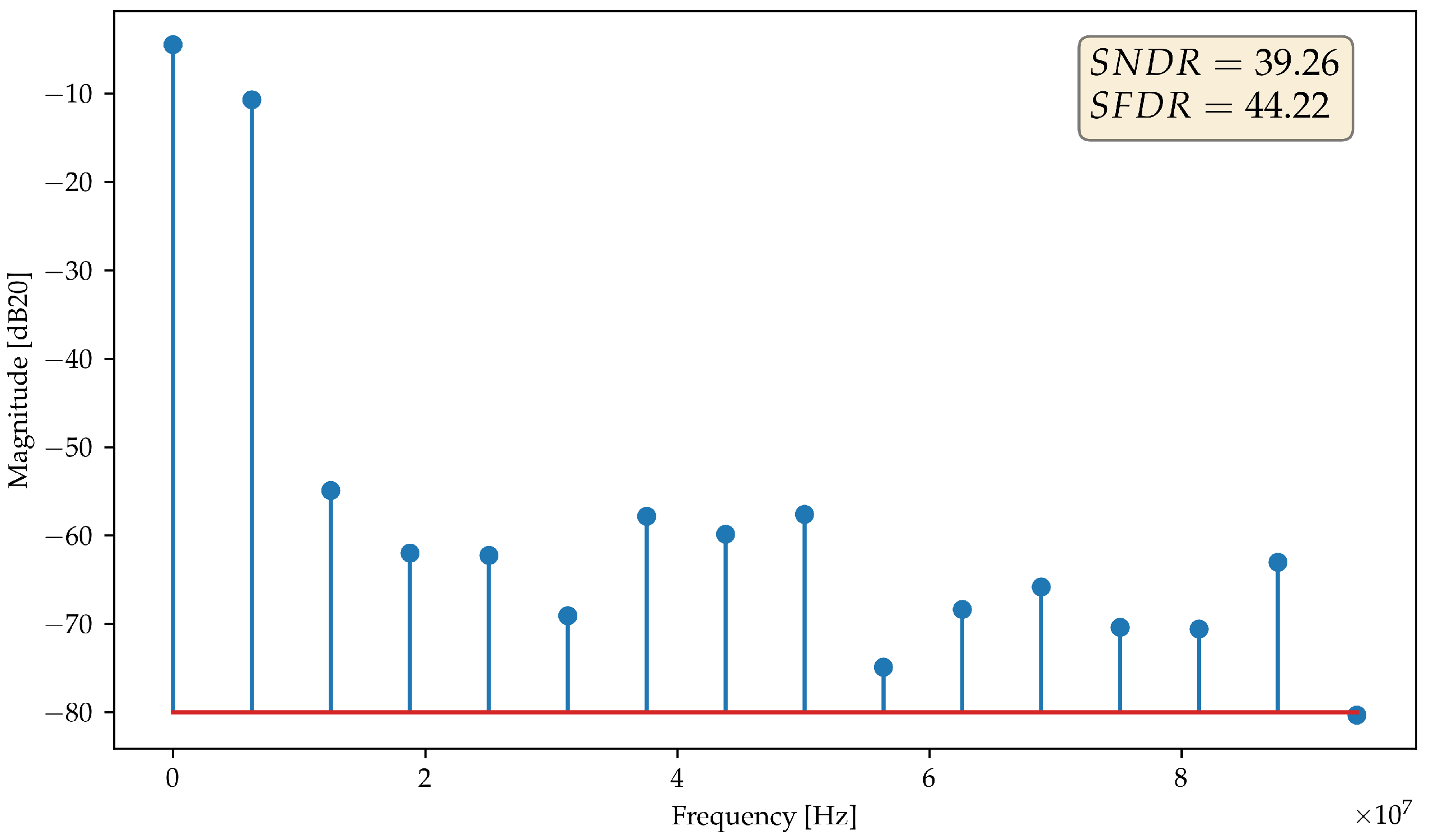

4.2. Application: Design of a SAR ADC

5. Comparison

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Wardlaw, J.L.; Karaman, I.; Karsilayan, A.İ. Low-power circuits and energy harvesting for structural health monitoring of bridges. IEEE Sens. J. 2013, 13, 709–722. [Google Scholar] [CrossRef]

- Lazaro, A.; Villarino, R.; Girbau, D. A survey of NFC sensors based on energy harvesting for IoT applications. Sensors 2018, 18, 3746. [Google Scholar] [CrossRef] [PubMed]

- Della Sala, R.; Centurelli, F.; Scotti, G.; Tommasino, P.; Trifiletti, A. A differential-to-single-ended converter based on enhanced body-driven current mirrors targeting ultra-low-voltage OTAs. Electronics 2022, 11, 3838. [Google Scholar] [CrossRef]

- Della Sala, R.; Centurelli, F.; Monsurró, P.; Scotti, G.; Trifiletti, A. A 0.3V rail-to-rail three-stage OTA with high DC gain and improved robustness to PVT variations. IEEE Access 2023, 11, 19635–19644. [Google Scholar] [CrossRef]

- Huang, G.Y.; Chang, S.J.; Liu, C.C.; Lin, Y.Z. A 1-µW 10-bit 200-kS/s SAR ADC with a bypass window for biomedical applications. IEEE J. Solid-State Circuits 2012, 47, 2783–2795. [Google Scholar] [CrossRef]

- Ng, K.A.; Xu, Y.P. A low-power, high CMRR neural amplifier system employing CMOS inverter-based OTAs with CMFB through supply rails. IEEE J. Solid-State Circuits 2016, 51, 724–737. [Google Scholar] [CrossRef]

- Goncalves, S.B.; Palha, J.M.; Fernandes, H.C.; Souto, M.R.; Pimenta, S.; Dong, T.; Yang, Z.; Ribeiro, J.F.; Correia, J.H. LED Optrode with Integrated Temperature Sensing for Optogenetics. Micromachines 2018, 9, 473. [Google Scholar] [CrossRef]

- Swaroop, K.N.; Chandu, K.; Gorrepotu, R.; Deb, S. A health monitoring system for vital signs using IoT. Internet Things 2019, 5, 116–129. [Google Scholar] [CrossRef]

- Della Sala, R.; Monsurró, P.; Scotti, G.; Trifiletti, A. Area-efficient low-power bandpass Gm-C filter for epileptic seizure detection in 130nm CMOS. In Proceedings of the 2019 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Genoa, Italy, 27–29 November 2019; pp. 298–301. [Google Scholar] [CrossRef]

- Zhou, Z. A front-end amplifier with current compensation feedback input impedance booster for neural signal applications. IEEE Access 2020, 8, 178055–178062. [Google Scholar] [CrossRef]

- Della Sala, R.; Centurelli, F.; Monsurró, P.; Scotti, G. Sub-μW front-end low noise amplifier for neural recording applications. In Proceedings of the 2022 17th Conference on Ph.D Research in Microelectronics and Electronics (PRIME), Villasimius, Italy, 12–15 June 2022; pp. 305–308. [Google Scholar] [CrossRef]

- Salam, M.T.; Sawan, M.; Nguyen, D.K. A novel low-power-implantable epileptic seizure-onset detector. IEEE Trans. Biomed. Circuits Syst. 2011, 5, 568–578. [Google Scholar] [CrossRef]

- Lin, C.Y.; Chen, W.L.; Ker, M.D. Implantable stimulator for epileptic seizure suppression with loading impedance adaptability. IEEE Trans. Biomed. Circuits Syst. 2013, 7, 196–203. [Google Scholar] [CrossRef] [PubMed]

- Shoffstall, A.J.; Paiz, J.E.; Miller, D.M.; Rial, G.M.; Willis, M.T.; Menendez, D.M.; Hostler, S.R.; Capadona, J.R. Potential for thermal damage to the blood–brain barrier during craniotomy: Implications for intracortical recording microelectrodes. J. Neural Eng. 2018, 15, 034001. [Google Scholar] [CrossRef] [PubMed]

- Lundstrom, B.N.; Lin, C.; Starnes, D.K.; Middlebrooks, E.H.; Tatum, W.; Grewal, S.S.; Crepeau, A.Z.; Gregg, N.M.; Miller, K.J.; Van Gompel, J.J.; et al. Safety and management of implanted epilepsy devices for imaging and surgery. Mayo Clin. Proc. 2022, 97, 2123–2138. [Google Scholar] [CrossRef] [PubMed]

- Zhou, X.; Li, Q. A 160 mV 670 nW 8-bit SAR ADC in 0.13 μm CMOS. In Proceedings of the CICC 2012 IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 9–12 September 2012; pp. 1–4. [Google Scholar] [CrossRef]

- Lin, J.Y.; Hsieh, C.C. A 0.3 V 10-bit 1.17 f SAR ADC with merge and split switching in 90 nm CMOS. IEEE Trans. Circ. Syst. I 2015, 62, 70–79. [Google Scholar] [CrossRef]

- Rabuske, T.; Rabuske, F.; Fernandes, J.; Rodrigues, C. An 8-bit 0.35-V 5.04-fJ/conversion-step SAR ADC with background self-calibration of comparator offset. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2015, 23, 1301–1307. [Google Scholar] [CrossRef]

- Harikumar, P.; Wikner, J.J.; Alvandpour, A. A 0.4-V subnanowatt 8-bit 1-kS/s SAR ADC in 65-nm CMOS for wireless sensor applications. IEEE Trans. Circuits Syst. II 2016, 63, 743–747. [Google Scholar] [CrossRef]

- Lee, P.C.; Lin, J.Y.; Hsieh, C.C. A 0.4 V 1.94 fJ/conversion-step 10 bit 750 kS/s SAR ADC with input-range-adaptive switching. IEEE Trans. Circ. Syst. I 2016, 63, 2149–2157. [Google Scholar] [CrossRef]

- Lin, J.Y.; Hsieh, C.C. A 0.3 V 10-bit SAR ADC with first 2-bit guess in 90-nm CMOS. IEEE Trans. Circ. Syst. I 2017, 64, 562–572. [Google Scholar] [CrossRef]

- Guo, W.; Zhu, Z. A 0.3 V 8-bit 8.9fJ/con.-step SAR ADC with sub-DAC merged switching for bio-sensors. Microelectron. J. 2017, 68, 44–54. [Google Scholar] [CrossRef]

- Xin, X.; Cai, J.P.; Chen, T.T.; Yang, Q.D. A 0.4-V 10-bit 10-kS/s SAR ADC in 0.18 μm CMOS for low energy wireless sensor network chip. Microelectron. J. 2019, 83, 104–116. [Google Scholar] [CrossRef]

- Hong, H.C.; Lin, L.Y.; Chiu, Y. Design of a 0.20–0.25-V, sub-nW, rail-to-rail, 10-bit SAR ADC for self-sustainable IoT applications. IEEE Trans. Circ. Syst. I 2019, 66, 1840–1852. [Google Scholar] [CrossRef]

- Luo, J.; Liu, Y.; Li, J.; Ning, N.; Wu, K.; Liu, Z.; Yu, Q. A low voltage and low power 10-bit non-binary 2b/cycle time and voltage based SAR ADC. IEEE Trans. Circ. Syst. I 2019, 67, 1136–1148. [Google Scholar] [CrossRef]

- Kim, J.E.; Yoo, T.; Jung, D.K.; Yoon, D.H.; Seong, K.; Kim, T.T.H.; Baek, K.H. A 0.5 V 8–12 Bit 300 kSps SAR ADC with adaptive conversion time detection-and-control for high immunity to PVT variations. IEEE Access 2020, 8, 101359–101368. [Google Scholar] [CrossRef]

- Wang, S.H.; Hung, C.C. A 0.3 V 10b 3 MS/s SAR ADC with comparator calibration and kickback noise reduction for biomedical applications. IEEE Trans. Biomed. Circuits Syst. 2020, 14, 558–569. [Google Scholar] [CrossRef]

- Hu, B.; Zhang, S.; Pan, X.; Zhao, X.; Ding, Z.; Zhou, X.; Yang, S.; Li, Q. Sampling and comparator speed-enhancement techniques for near-threshold SAR ADCs. IEEE Open J. Circuits Syst. 2021, 2, 304–310. [Google Scholar] [CrossRef]

- Wang, S.; Li, K.; Chan, C.H.; Zhu, Y.; Martins, R.P. A 0.3V 762nW-only binary-search phase ADC with current-reused RO-based comparator. In Proceedings of the 2022 IEEE Asian Solid-State Circuits Conference (A-SSCC), Taipei, Taiwan, 6–9 November 2022; pp. 18–20. [Google Scholar] [CrossRef]

- Michel, F.; Steyaert, M.S.J. A 250 mV 7.5 μW 61 dB SNDR SC ΔΣ modulator using near-threshold-voltage-biased inverter amplifiers in 130 nm CMOS. IEEE J. Solid-State Circuits 2012, 47, 709–721. [Google Scholar] [CrossRef]

- Park, J.E.; Hwang, Y.H.; Jeong, D.K. A 0.4-to-1 V voltage scalable ΔΣ ADC with two-step hybrid integrator for IoT sensor applications in 65-nm LP CMOS. IEEE Trans. Circuits Syst. II 2017, 64, 1417–1421. [Google Scholar] [CrossRef]

- Kulej, T.; Khateb, F.; Ferreira, L.H.C. A 0.3-V 37-nW 53-dB SNDR asynchronous Delta–Sigma Modulator in 0.18-μm CMOS. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2019, 27, 316–325. [Google Scholar] [CrossRef]

- Catania, A.; Ria, A.; Manfredini, G.; Dei, M.; Piotto, M.; Bruschi, P. A 150 mV, Sub-1 nW, 0.75%-full-scale INL Delta-Sigma ADC for power-autonomous sensor nodes. In Proceedings of the ESSCIRC 2022—IEEE 48th European Solid State Circuits Conference (ESSCIRC), Milan, Italy, 19–22 September 2022; pp. 257–260. [Google Scholar] [CrossRef]

- Lee, S.; Park, S.; Kim, Y.; Kim, Y.; Lee, J.; Lee, J.; Chae, Y. A 0.6-V 86.5-dB DR 40-kHz BW inverter-based continuous-time Delta–Sigma Modulator with PVT-robust body-biasing. IEEE Solid-State Circuits Lett. 2021, 4, 178–181. [Google Scholar] [CrossRef]

- Wu, H.J.; Li, B.; Huang, W.C.; Li, Z.P.; Zou, M.H.; Wang, Y.P. A 1.2 V 8-bit 1 MS/s SAR ADC with Res–Cap segment DAC for temperature sensor in LTE. Analog Integr. Circ. Sig. Process. 2012, 73, 225–232. [Google Scholar] [CrossRef]

- Park, J.E.; Hwang, Y.H.; Jeong, D.K. A 0.5-V fully synthesizable SAR ADC for on-chip distributed waveform monitors. IEEE Access 2019, 7, 63686–63697. [Google Scholar] [CrossRef]

- Liu, C.C.; Chang, S.J.; Huang, G.Y.; Lin, Y.Z. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits 2010, 45, 731–740. [Google Scholar] [CrossRef]

- Kandala, M.; Wang, H. A 0.5 V high-speed comparator with rail-to-rail input range. Analog Integr. Circ. Sig. Process. 2012, 73, 415–421. [Google Scholar] [CrossRef]

- Hoseini, S.Z.; Abdekhoda, J.; Lee, K.S. An ultra low voltage low power self biased latched comparator with wide input common mode range for biomedical applications. J. Circuits Syst. Comp. 2015, 24, 1550134. [Google Scholar] [CrossRef]

- Qiu, L.; Meng, T.; Yao, B.; Du, Z.; Yuan, X. A high-speed low-noise comparator with auxiliary-inverter-based common mode-self-regulation for low-supply-voltage SAR ADCs. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2023, 31, 152–156. [Google Scholar] [CrossRef]

- Hwang, Y.H.; Jeong, D.K. Ultra-low-voltage low-power dynamic comparator with forward body bias scheme for SAR ADC. Electron. Lett. 2018, 54, 1370–1372. [Google Scholar] [CrossRef]

- Canal, B.; Klimach, H.D.; Bampi, S.; Balen, T.R. Low-voltage dynamic comparator using positive feedback bulk effect on a floating inverter amplifier. Analog Integr. Circ. Sig. Process. 2021, 108, 511–524. [Google Scholar] [CrossRef]

- Goll, B.; Zimmermann, H. Low-power 600 MHz comparator for 0.5 V supply voltage in 0.12 −m CMOS. Electron. Lett. 2007, 43, 388–390. [Google Scholar] [CrossRef]

- Yang, B.D. 250-mV supply subthreshold CMOS voltage reference using a low-voltage comparator and a charge-pump circuit. IEEE Trans. Circuits Syst. II 2014, 61, 850–854. [Google Scholar] [CrossRef]

- Mohammadi Khanghah, M.; Sadeghipour, K.D. A 0.5 V offset cancelled latch comparator in standard 0.18 μm CMOS process. Analog Integr. Circ. Sig. Process. 2014, 79, 161–169. [Google Scholar] [CrossRef]

- Babayan-Mashhadi, S.; Sarvaghad-Moghaddam, M. Analysis and design of dynamic comparators in ultra-low supply voltages. In Proceedings of the 2014 22nd Iranian Conference on Electrical Engineering (ICEE), Tehran, Iran, 20–22 May 2014; pp. 255–258. [Google Scholar] [CrossRef]

- Li, Y.; Mao, W.; Zhang, Z.; Lian, Y. An ultra-low voltage comparator with improved comparison time and reduced offset voltage. In Proceedings of the 2014 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Ishigaki, Japan, 17–20 November 2014; pp. 407–410. [Google Scholar] [CrossRef]

- Akbari, M.; Maymandi-Nejad, M.; Mirbozorgi, S.A. A new rail-to-rail ultra low voltage high speed comparator. In Proceedings of the 2013 21st Iranian Conference on Electrical Engineering (ICEE), Mashhad, Iran, 14–16 May 2013; pp. 1–6. [Google Scholar] [CrossRef]

- Xin, X.; Cai, J.; Xie, R.; Wang, P. Ultra-low power comparator with dynamic offset cancellation for SAR ADC. Electron. Lett. 2017, 53, 1572–1574. [Google Scholar] [CrossRef]

- Della Sala, R.; Centurelli, F.; Scotti, G. A high performance 0.3 V standard-cell-based OTA suitable for automatic layout flow. Appl. Sci. 2023, 13, 5517. [Google Scholar] [CrossRef]

- Deng, W.; Yang, D.; Ueno, T.; Siriburanon, T.; Kondo, S.; Okada, K.; Matsuzawa, A. A fully synthesizable all-digital PLL with interpolative phase coupled oscillator, current-output DAC, and fine-resolution digital varactor using gated edge injection technique. IEEE J. Solid-State Circuits 2015, 50, 68–80. [Google Scholar] [CrossRef]

- Fahmy, A.; Liu, J.; Kim, T.; Maghari, N. An all-digital scalable and reconfigurable wide-input range stochastic ADC using only standard cells. IEEE Trans. Circuits Syst. II 2015, 62, 731–735. [Google Scholar] [CrossRef]

- Liu, J.; Park, B.; Guzman, M.; Fahmy, A.; Kim, T.; Maghari, N. A fully synthesized 77-dB SFDR reprogrammable SRMC filter using digital standard cells. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2018, 26, 1126–1138. [Google Scholar] [CrossRef]

- Centurelli, F.; Della Sala, R.; Scotti, G. A standard-cell-based CMFB for fully synthesizable OTAs. J. Low Power Electron. Appl. 2022, 12, 27. [Google Scholar] [CrossRef]

- Della Sala, R.; Centurelli, F.; Scotti, G. A novel differential to single-ended converter for ultra-low-voltage inverter-based OTAs. IEEE Access 2022, 10, 98179–98190. [Google Scholar] [CrossRef]

- Della Sala, R.; Centurelli, F.; Scotti, G. Enabling ULV fully synthesizable analog circuits: The BA cell, a standard-cell-based building block for analog design. IEEE Trans. Circuits Syst. II 2022, 69, 4689–4693. [Google Scholar] [CrossRef]

- Weaver, S.; Hershberg, B.; Moon, U.K. Digitally synthesized stochastic flash ADC using only standard digital cells. IEEE Trans. Circ. Syst. I 2014, 61, 84–91. [Google Scholar] [CrossRef]

- Aiello, O.; Crovetti, P.; Toledo, P.; Alioto, M. Rail-to-rail dynamic voltage comparator scalable down to pW-range power and 0.15-V supply. IEEE Trans. Circuits Syst. II 2021, 68, 2675–2679. [Google Scholar] [CrossRef]

- Zhou, T.; Li, X.; Ji, Y.; Li, Y. A 0.25–1.0 V fully synthesizable three-stage dynamic voltage comparator based XOR&XNOR&NAND&NOR logic. Analog Integr. Circ. Sig. Process. 2021, 108, 221–228. [Google Scholar] [CrossRef]

- Sood, L.; Agarwal, A. A CMOS standard-cell based fully-synthesizable low-dropout regulator for ultra-low power applications. AEU Int. J. Electron. Commun. 2021, 141, 153958. [Google Scholar] [CrossRef]

- Li, X.; Zhou, T.; Ji, Y.; Li, Y. A 0.35 V-to-1.0 V synthesizable rail-to-rail dynamic voltage comparator based OAI&AOI logic. Analog Integr. Circ. Sig. Process. 2020, 104, 351–357. [Google Scholar] [CrossRef]

- Akbari, M.; Hashemipour, O.; Moradi, F. Input offset estimation of CMOS integrated circuits in weak inversion. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2018, 26, 1812–1816. [Google Scholar] [CrossRef]

- Sheikholeslami, A. Process variation and Pelgrom’s law [Circuit Intuitions]. IEEE Solid-State Circuits Mag. 2015, 7, 8–9. [Google Scholar] [CrossRef]

- Orguc, S.; Khurana, H.S.; Lee, H.S.; Chandrakasan, A.P. 0.3 V ultra-low power sensor interface for EMG. In Proceedings of the ESSCIRC 2017—43rd IEEE European Solid State Circuits Conference, Leuven, Belgium, 11–14 September 2017; pp. 219–222. [Google Scholar] [CrossRef]

- Yoshioka, K.; Shikata, A.; Sekimoto, R.; Kuroda, T.; Ishikuro, H. An 8 bit 0.3–0.8 V 0.2–40 MS/s 2-bit/Step SAR ADC with successively activated threshold configuring comparators in 40 nm CMOS. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2015, 23, 356–368. [Google Scholar] [CrossRef]

- Chiu, P.F.; Zimmer, B.; Nikoliç, B. A double-tail sense amplifier for low-voltage SRAM in 28nm technology. In Proceedings of the 2016 IEEE Asian Solid-State Circuits Conference (A-SSCC), Toyama, Japan, 7–9 November 2016; pp. 181–184. [Google Scholar] [CrossRef]

| Device | W | L |

|---|---|---|

| m] | m] | |

| 2 | 2 | |

| 40 | 0.2 | |

| 2 | 0.2 | |

| 5 | 1 | |

| 1 | 1 |

| V [V] | 0.15 | 0.3 | 0.5 |

|---|---|---|---|

| [MHz] | 0.08 | 2 | 16 |

| [ns] | 2200 | 59.27 | 9.26 |

| [nW] | 0.856 | 52.50 | 12.96 |

| PDP [fJ] | 1.88 | 3.11 | 12.96 |

| EDP [aJ/kHz] | 23.584 | 1.556 | 0.810 |

| Performance | Nominal | Vddmin | Vddmax | Tmin | Tmax | SS | FF | SF | FS |

|---|---|---|---|---|---|---|---|---|---|

| [ns] | 59.27 | 97.94 | 39.4 | 74.09 | 44.85 | 81.78 | 44.38 | 79.97 | 49.08 |

| [nW] | 52.5 | 42.35 | 65.62 | 41.84 | 71.6 | 48.9 | 57.72 | 51.63 | 53.71 |

| PDP [fJ] | 3.11 | 4.15 | 2.59 | 3.10 | 3.21 | 4.00 | 2.56 | 4.13 | 2.64 |

| EDP [aJ/kHz] | 1.56 | 2.07 | 1.29 | 1.55 | 1.61 | 2.00 | 1.28 | 2.06 | 1.32 |

| This Work | [58] | [58] | [48] | [61] | [46] | [41] | [66] | [48] | [45] | [46] | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Topology | BD-SA | STD-CELL | STD-CELL | BD-SA | STD-CELL | BD-SA | DT | DT | BD-SA | SA | BD-SA | ||

| [V] | 0.15 | 0.3 | 0.5 | 0.15 | 0.3 | 0.3 | 0.35 | 0.35 | 0.4 | 0.4 | 0.5 | 0.5 | 0.5 |

| Technology [nm] | 130 | 130 | 130 | 180 | 180 | 180 | 45 | 90 | 180 | 28 | 180 | 180 | 90 |

| Type | BD | GD | GD | BD | GD | BD | BD | GD | BD | GD | BD | ||

| Area [m] | 670 | 670 | 670 | 900 | 900 | - | 59 | - | - | - | - | - | - |

| ICMR [mV] | 150 | 300 | 500 | 135 | 275 | 300 | 350 | - | 200 | 200 | 500 | - | 500 |

| ICMR-rail-to-rail | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✗ | ✗ | ✓ | ✗ | ✓ |

| Max. [ns] | 2200 | 59.27 | 9.26 | 442,000 | 34,700 | 980 | 2100 | 2.22 | 594 | 1330 | 16.4 | 5.77 | 0.5 |

| [mV] | 1 | 1 | 1 | 10 | 10 | 0.5 | 10 | - | 0.1 | 0.1 | 0.5 | 2 | 1 |

| [kHz] | 80 | 2000 | 16,000 | 10 | 10 | 62.5 | 10 | 50 | 100 | 100 | 5000 | 200,000 | 333,000 |

| Offset () [mV] | 18.74 | 17.98 | 18.14 | 31 | 8 | - | 4.73 | - | 13.7 | 15.3 | - | 0.29 | 5.1 |

| [%] | 12.49 | 5.99 | 3.63 | 20.67 | 2.67 | - | 1.35 | - | 3.42 | 3.82 | - | 0.06 | 1.02 |

| [nW] | 0.856 | 52.5 | 1400 | 0.027 | 0.024 | 0.1 | - | 184 | 4.48 | 14.6 | 20.2 | 34,000 | 2300 |

| PDP [aJ] | 1883.86 | 3111.67 | 12,964 | 11,934 | 3088.3 | 98 | - | 408.48 | 2661.12 | 19418 | 331.28 | 196,180 | 1145.4 |

| EDP [aJ/kHz] | 23.55 | 1.55 | 0.81 | 1193.4 | 308.83 | 1.57 | - | 8.17 | 26.61 | 194.18 | 0.07 | 0.98 | 0.003 |

| FOM [pJ/kHz] | 23.55 | 1.55 | 0.81 | 1326 | 336.9 | 1.57 | - | - | 53.22 | 388.36 | 0.07 | - | 0.003 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Della Sala, R.; Spinogatti, V.; Bocciarelli, C.; Centurelli, F.; Trifiletti, A. A 0.15-to-0.5 V Body-Driven Dynamic Comparator with Rail-to-Rail ICMR. J. Low Power Electron. Appl. 2023, 13, 35. https://doi.org/10.3390/jlpea13020035

Della Sala R, Spinogatti V, Bocciarelli C, Centurelli F, Trifiletti A. A 0.15-to-0.5 V Body-Driven Dynamic Comparator with Rail-to-Rail ICMR. Journal of Low Power Electronics and Applications. 2023; 13(2):35. https://doi.org/10.3390/jlpea13020035

Chicago/Turabian StyleDella Sala, Riccardo, Valerio Spinogatti, Cristian Bocciarelli, Francesco Centurelli, and Alessandro Trifiletti. 2023. "A 0.15-to-0.5 V Body-Driven Dynamic Comparator with Rail-to-Rail ICMR" Journal of Low Power Electronics and Applications 13, no. 2: 35. https://doi.org/10.3390/jlpea13020035

APA StyleDella Sala, R., Spinogatti, V., Bocciarelli, C., Centurelli, F., & Trifiletti, A. (2023). A 0.15-to-0.5 V Body-Driven Dynamic Comparator with Rail-to-Rail ICMR. Journal of Low Power Electronics and Applications, 13(2), 35. https://doi.org/10.3390/jlpea13020035