An Acoustic Vehicle Detector and Classifier Using a Reconfigurable Analog/Mixed-Signal Platform

Abstract

1. Introduction

1.1. Wireless Sensor Networks and Acoustic Techniques

1.2. Proposal, Novelty, and Overview

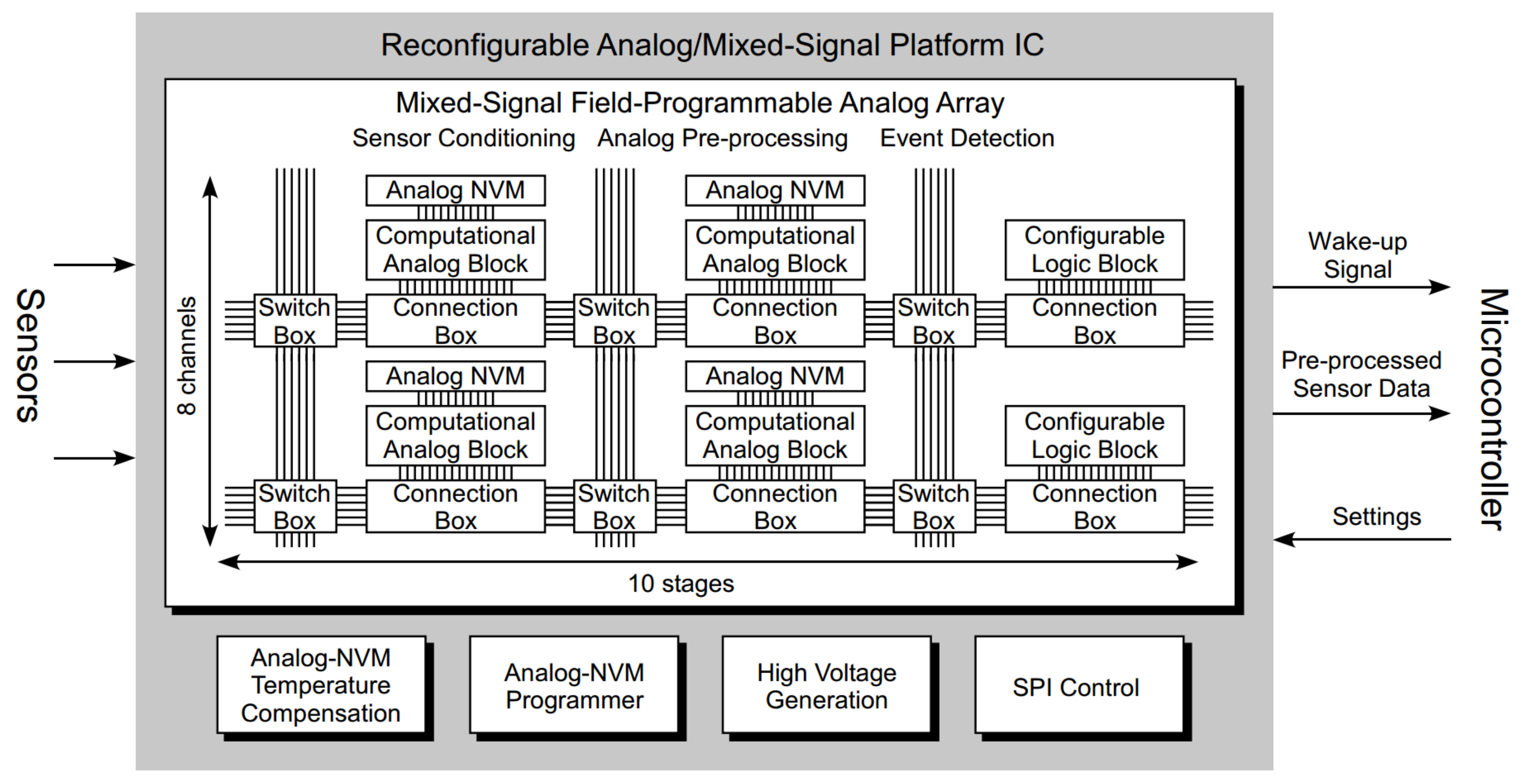

2. System Architecture

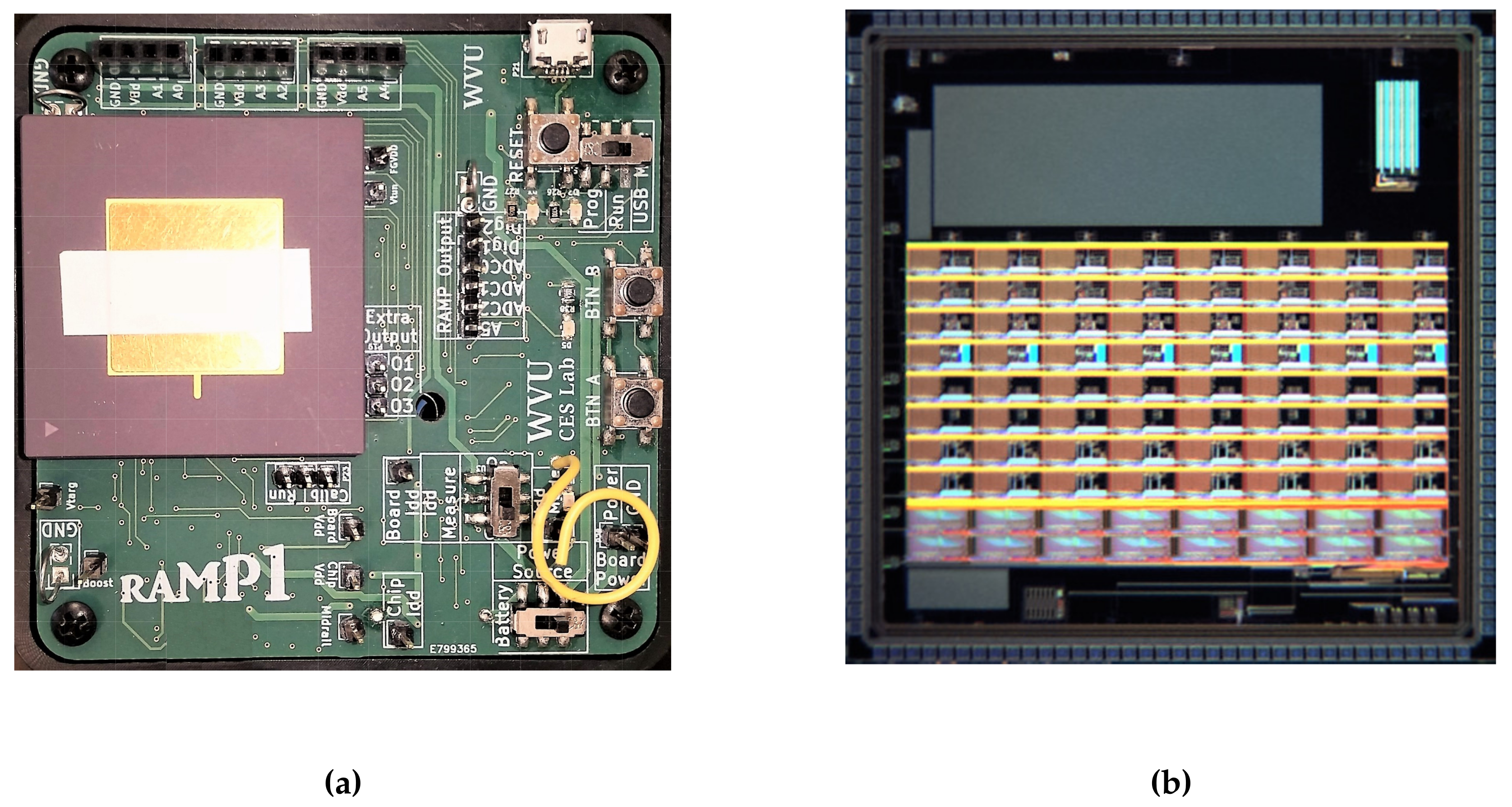

2.1. Reconfigurable Platform

2.2. Programming Infrastructure

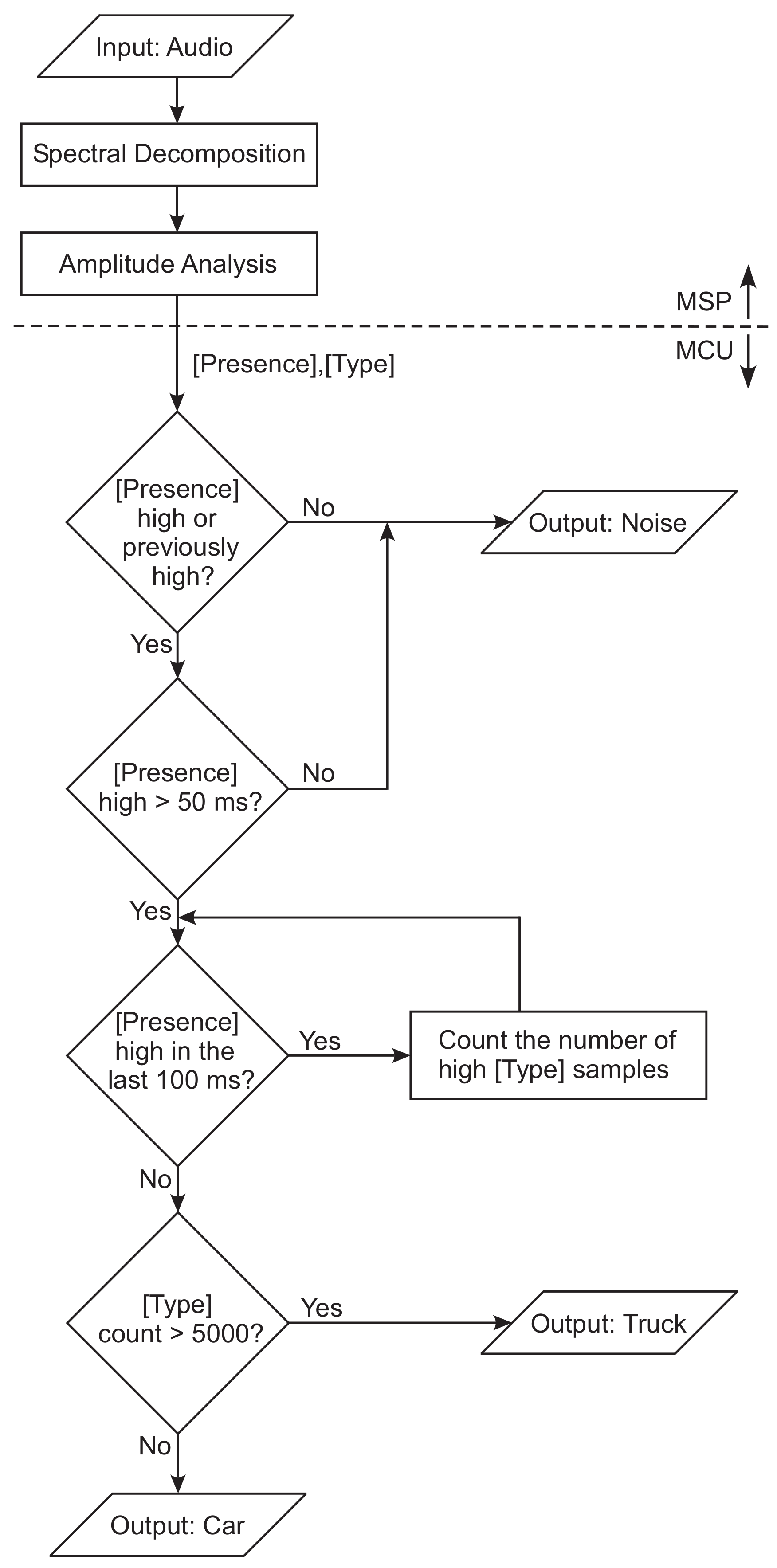

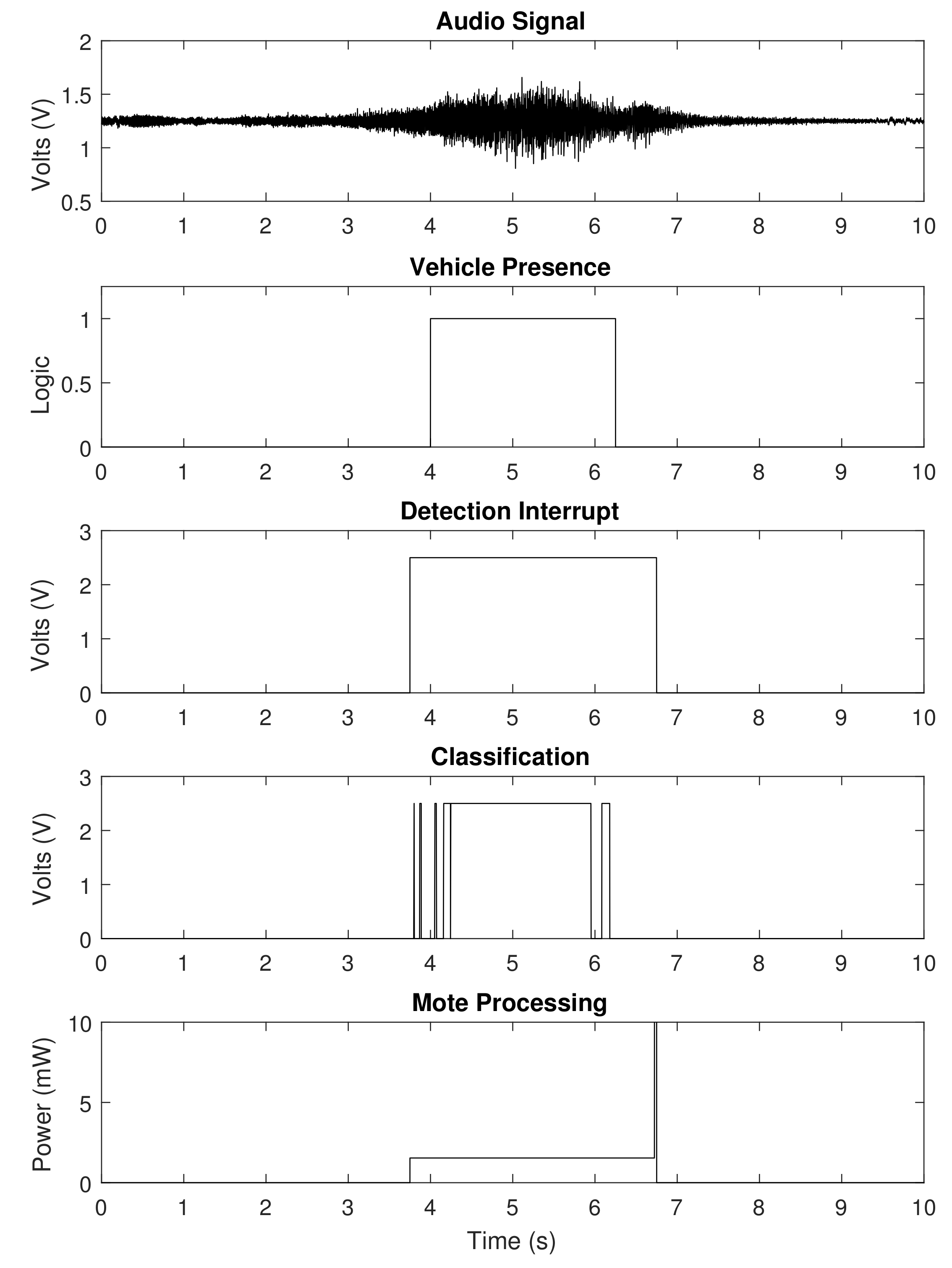

3. Vehicle Detector Configuration

- Spectral decomposition using a filterbank of bandpass filters (BPFs)

- RMS envelope estimation using a bank of root-mean-square (RMS) detectors cascaded with a bank of ripple-smoothing, adaptive-time-constant (adaptive-) lowpass filters

- Digitization using a bank of comparators

- Digital “debouncing” using a starved inverter

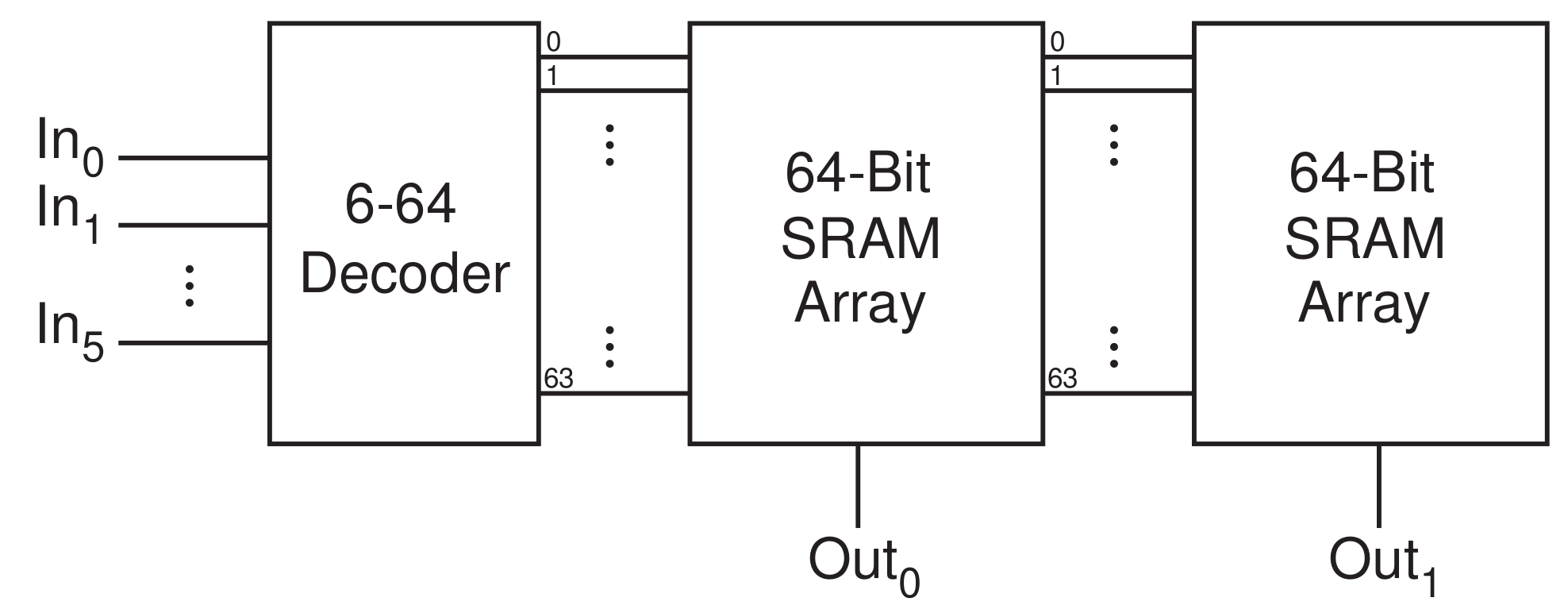

- Template matching using a LUT

- Final decision transmission using a panStamp MCU

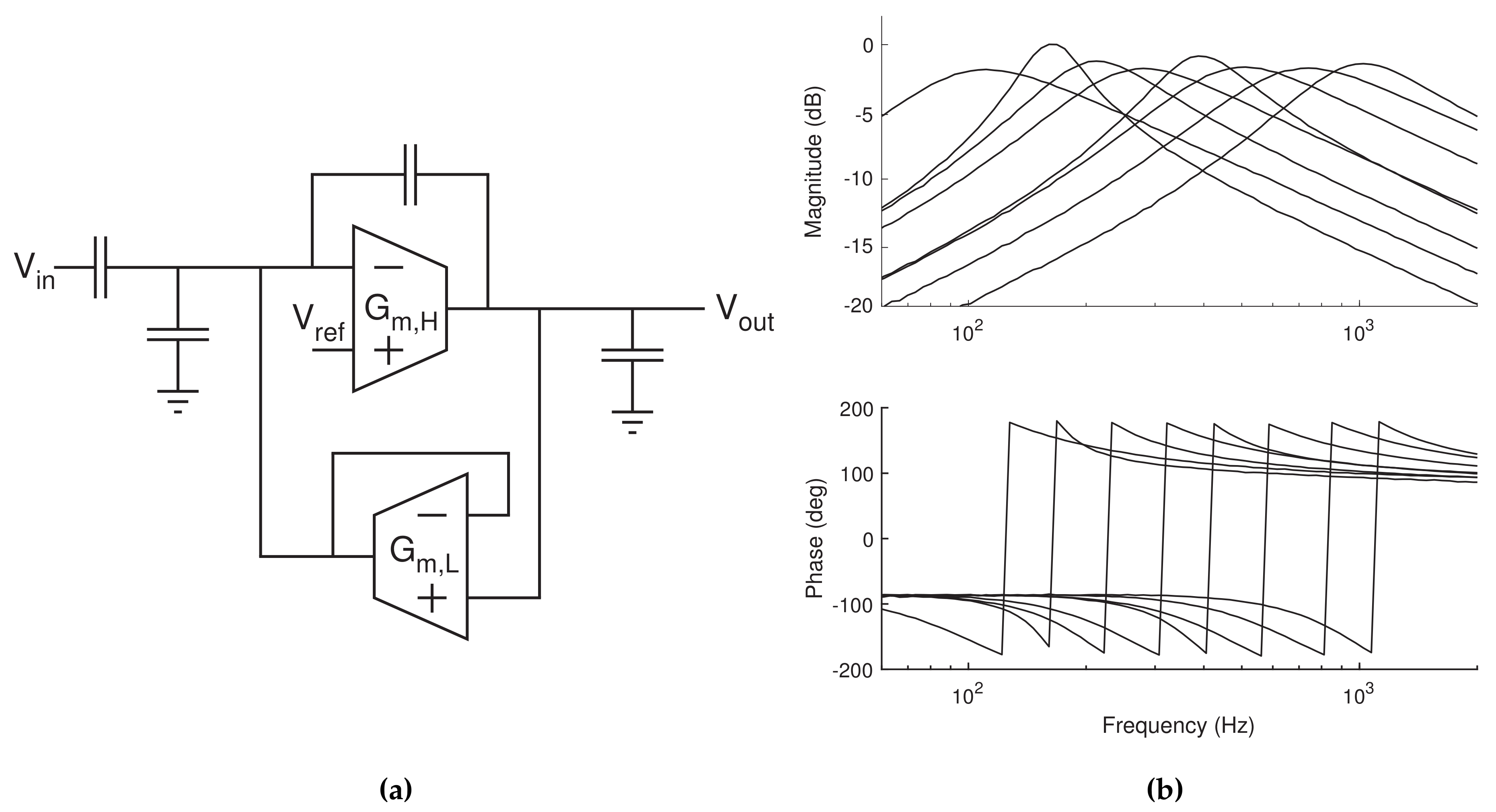

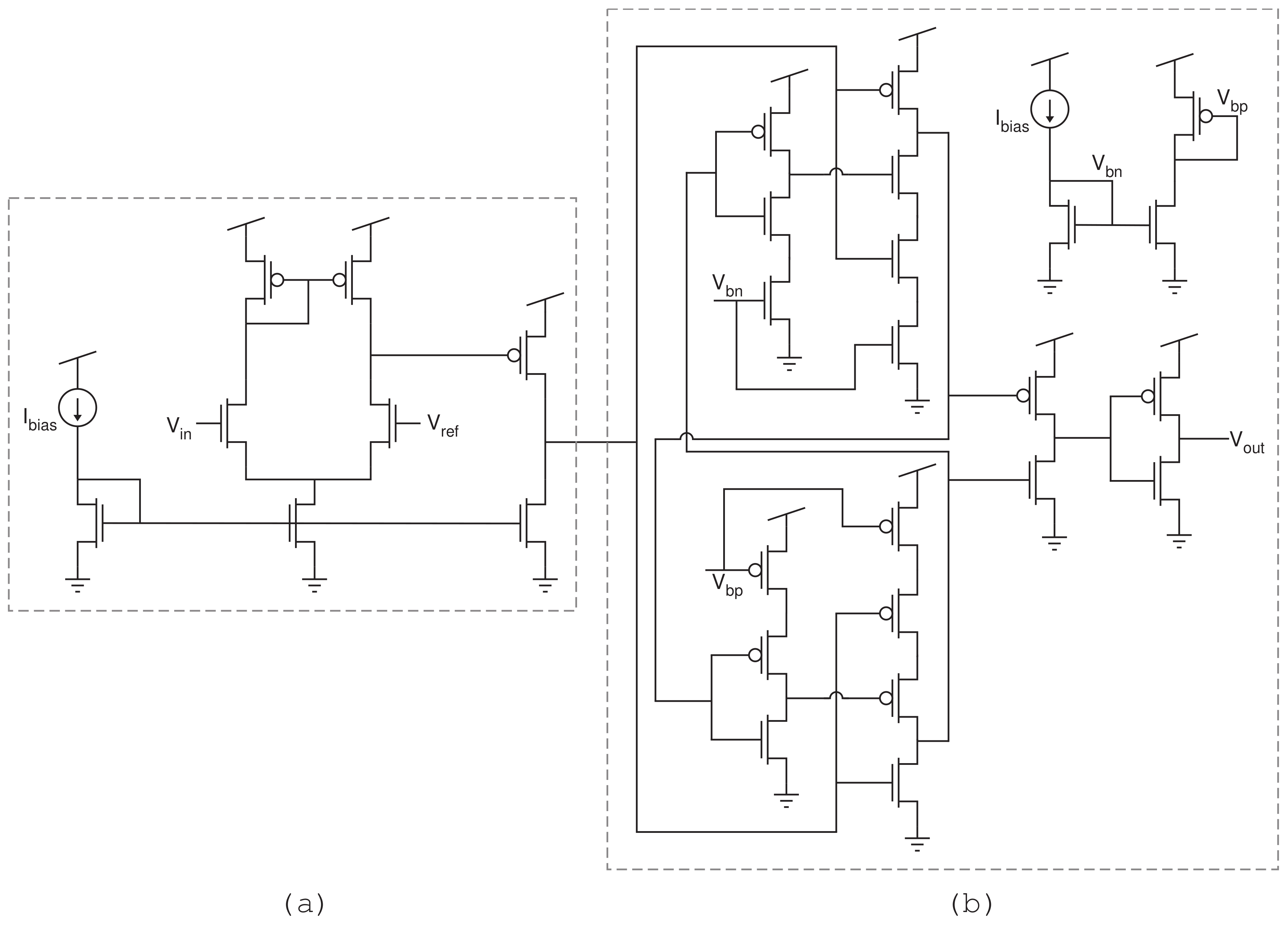

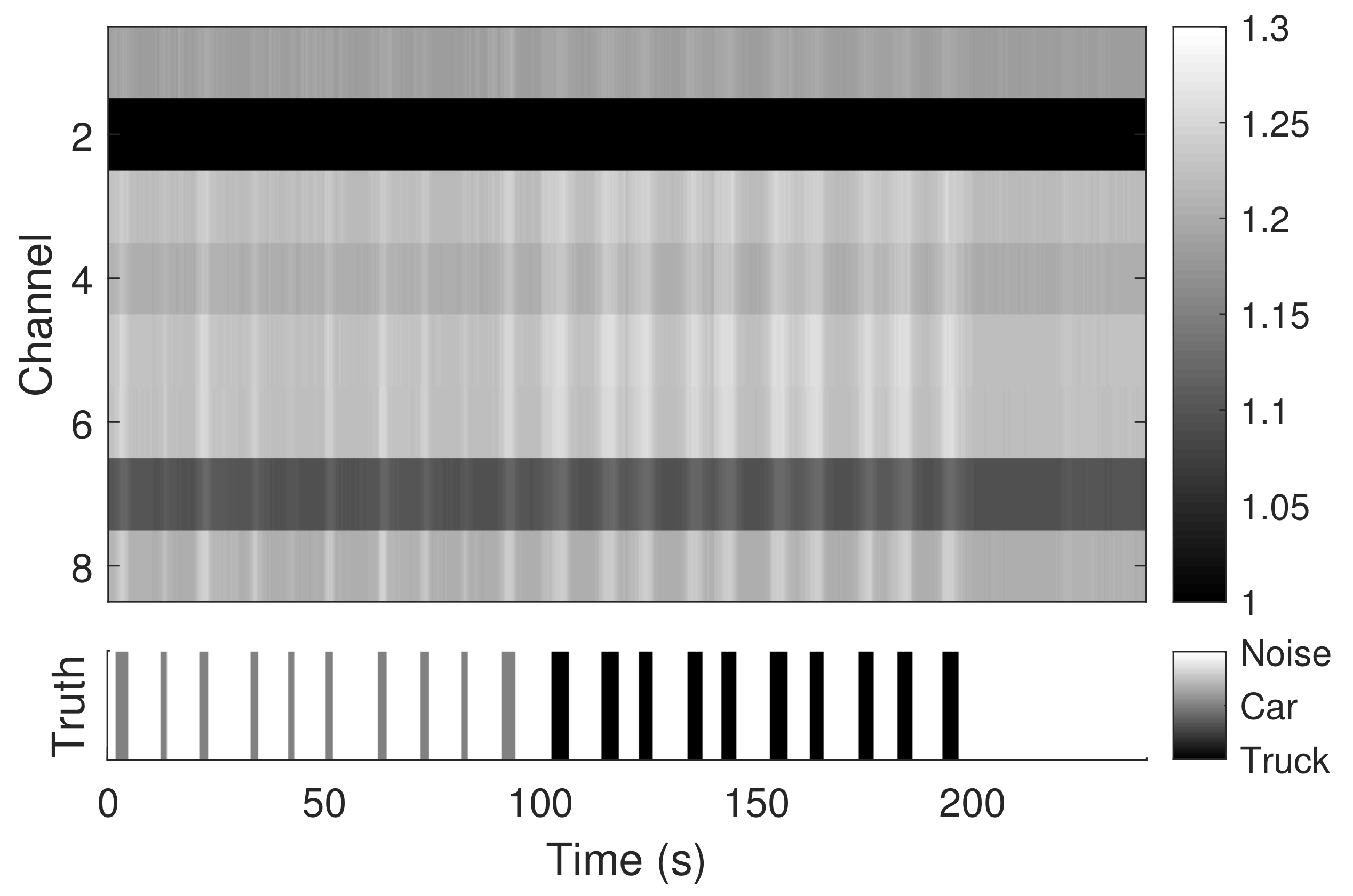

3.1. Spectral Decomposition

3.2. RMS Envelope Estimation

3.3. Digitization

3.4. Digital Debouncing

3.5. Template Matching

3.6. Final Decision Transmission

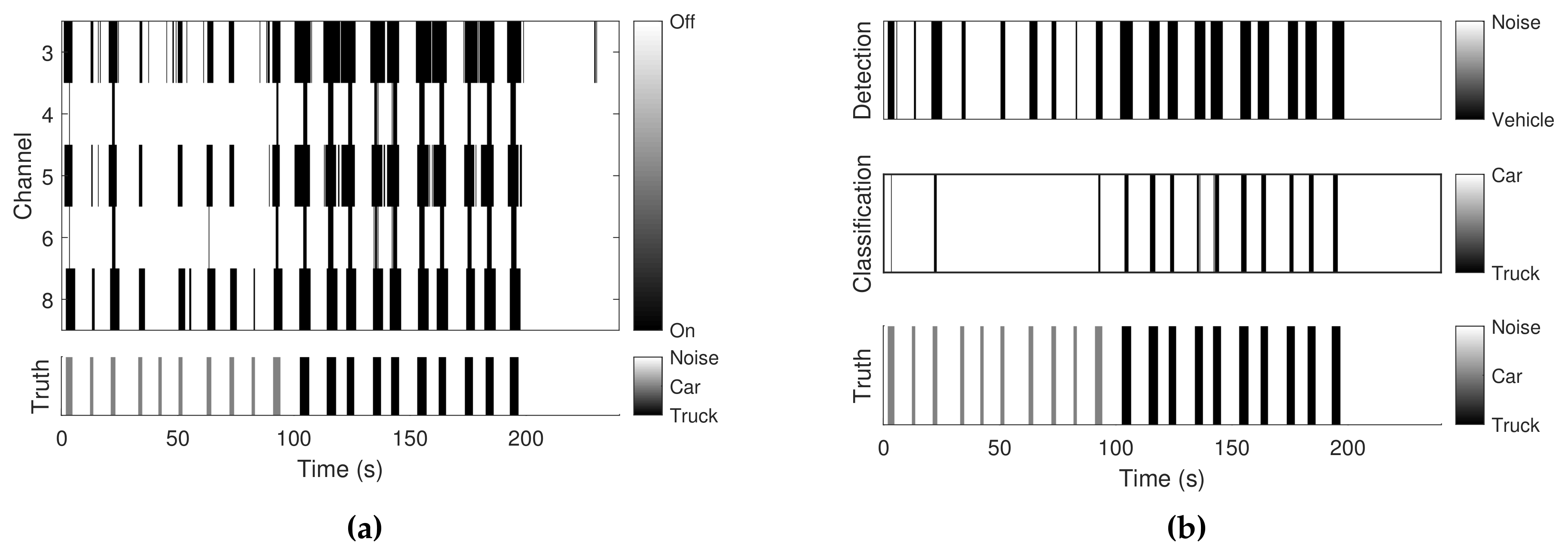

4. Classifier Training

4.1. Data Preparation

4.2. Comparator Threshold Optimization

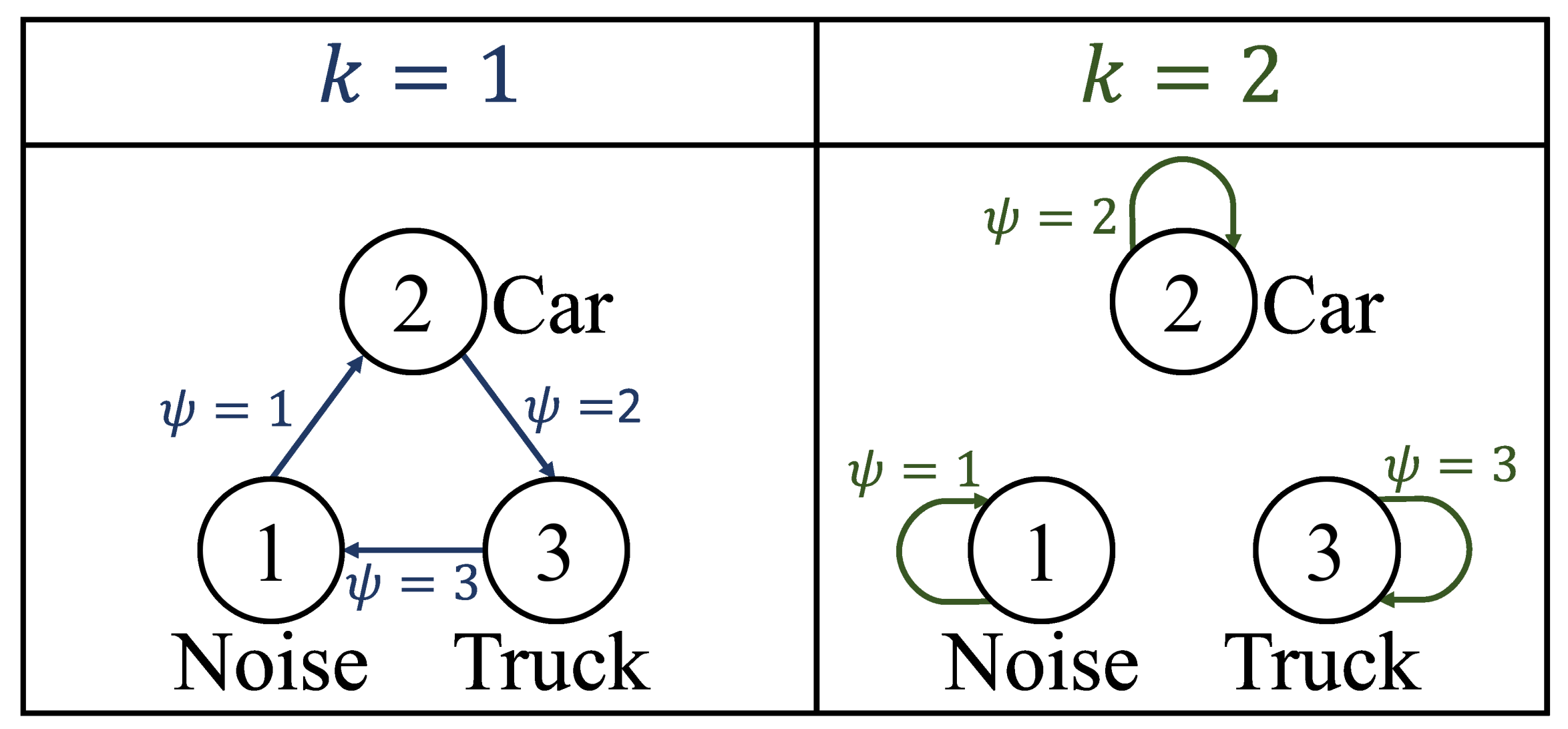

4.3. Lookup Table Configuration

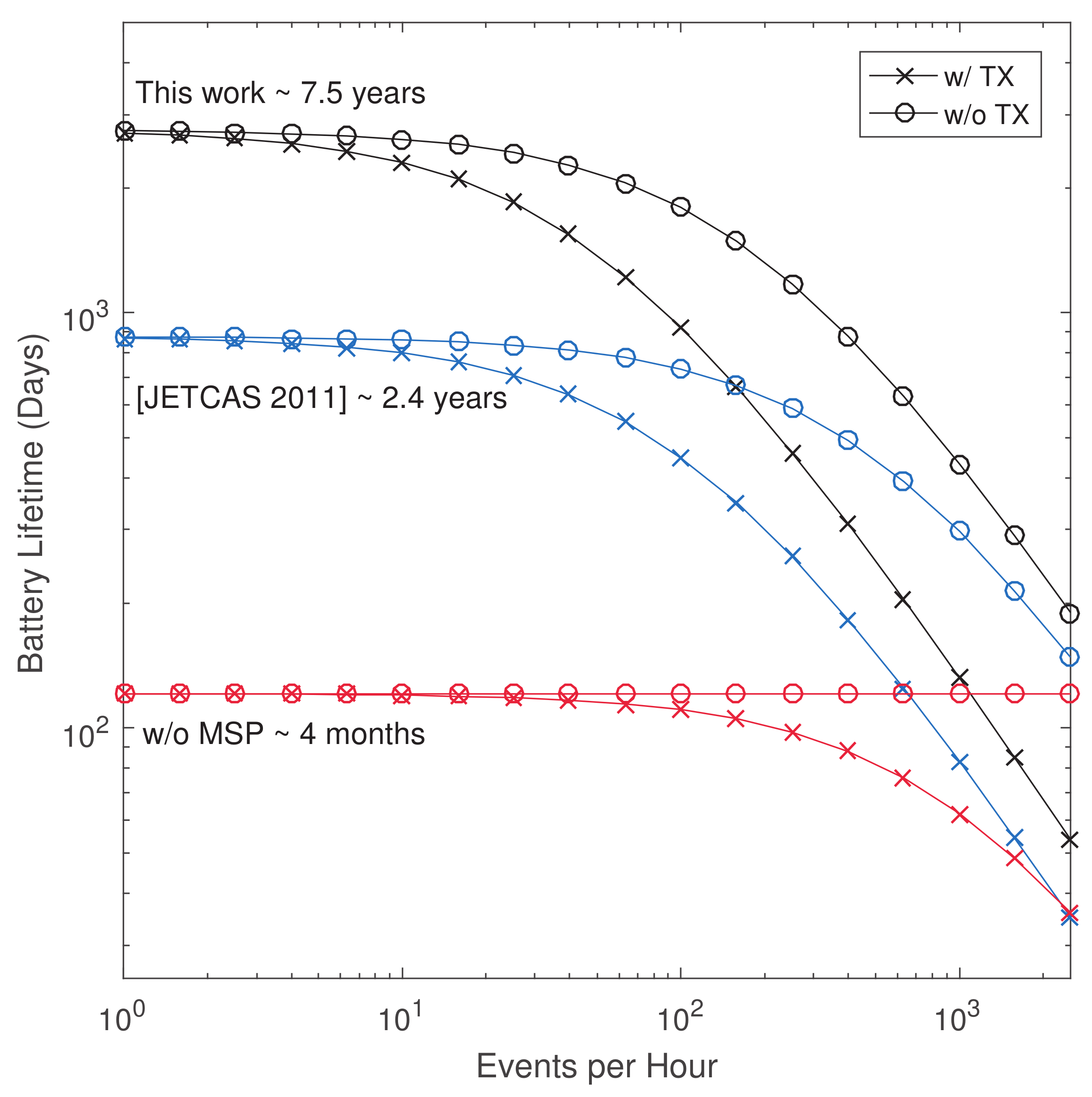

5. Results

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviations

| ASIC | application-specific integrated circuit |

| ASP | analog signal processor |

| AVDC | acoustic vehicle detection and classification |

| BPF | bandpass filter |

| CAB | computational analog block |

| CLB | computational logic block |

| DSP | digital signal-processor |

| FG | floating-gate (transistors) |

| FPAA | field-programmable analog array |

| FPGA | field-programmable gate array |

| IC | integrated circuit |

| IoT | Internet of Things |

| LUT | lookup table |

| MCU | microcontroller unit |

| MSP | mixed-signal processor |

| OTA | operational transconductance amplifier |

| PCB | printed circuit board |

| RAMP | Reconfigurable Analog/Mixed-Signal Platform |

| RMS | root-mean-square |

| SPI | serial-peripheral interface |

| WSN | wireless sensor network |

References

- Rumberg, B.; Graham, D.W.; Kulathumani, V. A low-power, programmable analog event detector for resource-constrained sensing systems. In Proceedings of the 55th IEEE International Midwest Symposium on Circuits and Systems, Boise, ID, USA, 5–8 August 2012; pp. 338–341. [Google Scholar]

- Arora, A.; Dutta, P.; Bapat, S.; Kulathumani, V.; Zhang, H.; Naik, V.; Mittal, V.; Cao, H.; Demirbas, M.; Gouda, M.; et al. A Line in the Sand: A Wireless Sensor Network for Target Detection, Classification, and Tracking. Comput. Netw. 2004, 46, 605–634. [Google Scholar] [CrossRef]

- Raghunathan, V.; Schurgers, C.; Park, S.; Srivastava, M.B. Energy-Aware Wireless Microsensor Networks. IEEE Signal Process. Mag. 2002, 19, 40–50. [Google Scholar] [CrossRef]

- Gu, C.; Rice, J.A.; Li, C. A wireless smart sensor network based on multi-function interferometric radar sensors for structural health monitoring. In Proceedings of the 2012 IEEE Topical Conference on Wireless Sensors and Sensor Networks, Santa Clara, CA, USA, 15–18 January 2012; pp. 33–36. [Google Scholar]

- Arora, A.; Ramnath, R.; Ertin, E.; Sinha, P.; Bapat, S.; Naik, V.; Kulathumani, V.; Zhang, H.; Cao, H.; Sridharan, M.; et al. ExScal: Elements of an extreme scale wireless sensor network. In Proceedings of the 11th IEEE International Conference on Embedded and Real-Time Computing Systems and Applications, Hong Kong, China, 17–19 August 2005; pp. 102–108. [Google Scholar]

- Rumberg, B.; Graham, D.W.; Kulathumani, V.; Fernandez, R. Hibernets: Energy-Efficient Sensor Networks Using Analog Signal Processing. IEEE J. Emerg. Sel. Top. Circuits Syst. 2011, 1, 321–334. [Google Scholar] [CrossRef]

- Malhotra, B.; Nikolaidis, I.; Harms, J. Distributed Classification of Acoustic Targets in Wireless Audio-Sensor Networks. Comput. Netw. 2008, 52, 2582–2593. [Google Scholar] [CrossRef]

- Uttarakumari, M.; Koushik, A.S.; Raghavendra, A.S.; Adiga, A.R.; Harshita, P. Vehicle detection using acoustic signatures. In Proceedings of the International Conference on Computing, Communication and Automation, Greater Noida, India, 5–6 May 2017; pp. 1173–1177. [Google Scholar]

- Malinowski, M.; Moskwa, M.; Feldmeier, M.; Laibowitz, M.; Paradiso, J. CargoNet: A low-cost micropower sensor node exploiting quasi-passive wakeup for adaptive asychronous monitoring of exceptional events. In Proceedings of the 5th International Conference on Embedded Networked Sensor Systems, Sydney, Australia, 6–9 November 2007; ACM: New York, NY, USA, 2007; pp. 145–159. [Google Scholar]

- Jevtic, S.; Kotowsky, M.; Dick, R.; Dinda, P.; Dowding, C. Lucid Dreaming: Reliable analog event detection for energy-constrained applications. In Proceedings of the 6th International Conference on Information Processing in Sensor Networks, Cambridge, MA, USA, 25–27 April 2007; ACM: New York, NY, USA, 2007; pp. 350–359. [Google Scholar]

- Ding, J.; Cheung, S.Y.; Tan, C.W.; Varaiya, P. Signal processing of sensor node data for vehicle detection. In Proceedings of the IEEE Conference on Intelligent Transportation Systems, Washington, WA, USA, 3–6 October 2004; IEEE: Piscataway, NJ, USA, 2004; pp. 70–75. [Google Scholar]

- Gutierrez, E.; Perez, C.; Hernandez, F.; Hernandez, L. VCO-based feature extraction architecture for low power speech recognition applications. In Proceedings of the IEEE 62nd International Midwest Symposium on Circuits and Systems, Dallas, TX, USA, 4–7 August 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 1175–1178. [Google Scholar]

- Mishra, B.; Thakkar, S.; Jain, N. Ultra-Low Power Digital Front-End for Single Lead ECG Acquisition Integrated with a Time-to-Digital Converter. IET Comput. Digit. Tech. 2019, 13, 453–460. [Google Scholar] [CrossRef]

- Hall, T.S.; Twigg, C.M.; Hasler, P.; Anderson, D.V. Application performance of elements in a floating-gate FPAA. In Proceedings of the IEEE International Symposium on Circuits and Systems, Vancouver, BC, Canada, 23–26 May 2004; IEEE: Piscataway, NJ, USA, 2014; Volume 2, p. II-589. [Google Scholar]

- Lee, S. Techniques for Low-Power High-Performance ADCs. Ph.D. Thesis, Massachusetts Institute of Technology, Cambridge, MA, USA, February 2014. [Google Scholar]

- Frigo, J.; Kulathumani, V.; Brennan, S.; Rosten, E.; Raby, E. Sensor network based vehicle classification and license plate identification system. In Proceedings of the 2009 Sixth International Conference on Networked Sensing Systems, Pittsburgh, PA, USA, 17–19 June 2009; IEEE: Piscataway, NJ, USA, 2009; pp. 1–4. [Google Scholar]

- Sarpeshkar, R. Analog Versus Digital: Extrapolating from Electronics to Neurobiology. Neural Comput. 1998, 10, 1601–1638. [Google Scholar] [CrossRef]

- Hasler, P.; Smith, P.; Graham, D.; Ellis, R.; Anderson, D. Analog floating-gate, on-chip auditory sensing system interfaces. IEEE Sens. J. 2005, 5, 1027–1034. [Google Scholar] [CrossRef]

- Park, J.; Hwang, Y.; Oh, J.; Song, Y.; Park, J.; Jeong, D. A compact self-capacitance sensing analog front-end for a touch detection in low-power mode. In Proceedings of the 2019 IEEE/ACM International Symposium on Low Power Electronics and Design, Lausanne, Switzerland, 29–31 July 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 1–6. [Google Scholar]

- Jeong, J.; An, J.; Jung, S.; Hong, S.; Kwon, O. A Low-Power Analog Delay Line Using a Current-Splitting Method for 3-D Ultrasound Imaging Systems. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 829–833. [Google Scholar] [CrossRef]

- Groza, R.; Farago, P. Low power current-mode analog front-end for biomedical applications. In Proceedings of the 2018 IEEE International Conference on Automation, Quality and Testing, Robotics, Cluj-Napoca, Romania, 24–26 May 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 1–5. [Google Scholar]

- Morshedlou, F.; Ravanshad, N.; Rezaee-Dehsorkh, H. A low-power current-mode analog QRS-detection circuit for wearable ECG sensors. In Proceedings of the 2018 25th National and 3rd International Iranian Conference on Biomedical Engineering, Qom, Iran, 29–30 November 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 1–6. [Google Scholar]

- Kim, J.; Kim, C.; Kim, K.; Yoo, H. An ultra-low-power analog-digital hybrid CNN face recognition processor integrated with a CIS for always-on mobile devices. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems, Sapporo, Japan, 26–29 May 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 1–5. [Google Scholar]

- Uetake, N.; Zhang, R.; Nakada, T.; Nakashima, Y. A programmable analog calculation unit for vector computations. In Proceedings of the 2018 IEEE Symposium in Low-Power and High-Speed Chips, Yokohama, Japan, 18–20 April 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 1–3. [Google Scholar]

- Rumberg, B.; Graham, D.W.; Kulathumani, V. Hibernets: Energy-efficient sensor networks using analog signal processing. In Proceedings of the 9th ACM/IEEE International Conference on Information Processing in Sensor Networks; ACM: New York, NY, USA, 2010; pp. 129–139. [Google Scholar]

- Rumberg, B.; Graham, D.W.; Clites, S.; Kelly, B.; Navidi, M.; Dilello, A.; Kulathumani, V. RAMP: Accelerating wireless sensor hardware design with a reconfigurable analog/mixed-signal platform. In Proceedings of the ACM/IEEE Conference on Information Processing in Sensor Networks, Seattle, WA, USA, 14–16 April 2015; ACM: New York, NY, USA, 2015; pp. 47–58. [Google Scholar]

- Basu, A.; Brink, S.; Schlottmann, C.; Ramakrishnan, S.; Petre, C.; Koziol, S.; Baskaya, F.; Twigg, C.M.; Hasler, P. A Floating-Gate-Based Field-Programmable Analog Array. IEEE J. Solid-State Circuits 2010, 45, 1781–1794. [Google Scholar] [CrossRef]

- Lee, E.K.F.; Gulak, P.G. A CMOS Field-Programmable Analog Array. IEEE J. Solid-State Circuits 1991, 26, 1860–1867. [Google Scholar] [CrossRef]

- Becker, J.; Henrici, F.; Trendelenburg, S.; Ortmanns, M.; Manoli, Y. A continuous-time hexagonal field-programmable analog array in 0.13 μm CMOS with 186 MHz GBW. In In Proceedings of the 2008 IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 3–7 February 2008; IEEE: Piscataway, NJ, USA, 2008; pp. 70–596. [Google Scholar]

- Hall, T.; Twigg, C.; Gray, J.; Hasler, P.; Anderson, D. Large-Scale Field-Programmable Analog Arrays for Analog Signal Processing. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 2298–2307. [Google Scholar] [CrossRef]

- Rumberg, B.; Graham, D.W. A floating-gate memory cell for continuous-time programming. In Proceedings of the IEEE International Midwest Symposium on Circuits and Systems, Boise, ID, USA, 5–8 August 2012; IEEE: Piscataway, NJ, USA, 2012; pp. 214–217. [Google Scholar]

- Aarts, E.; Korst, J.; Michiels, W. Simulated Annealing. In Search Methodologies: Introductory Tutorials in Optimization and Decision Support Techniques; Springer: Boston, MA, USA, 2014; pp. 265–285. [Google Scholar]

- Rumberg, B.; Graham, D.W. A Low-Power and High-Precision Programmable Analog Filter Bank. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 234–238. [Google Scholar] [CrossRef]

- Rumberg, B.; Graham, D.W. A Low-Power Magnitude Detector for Analysis of Transient-Rich Signals. IEEE J. Solid-State Circuits 2012, 47, 676–685. [Google Scholar] [CrossRef]

- Rumberg, B.; Graham, D.W.; Navidi, M.M. A Regulated Charge Pump for Tunneling Floating-Gate Transistors. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 516–527. [Google Scholar] [CrossRef]

- panStamp NRG 2. Technical Details. Available online: https://github.com/panStamp/panstamp/wiki/panStamp-NRG-2.-Technical-details (accessed on 20 December 2019).

- Zykina, A.V. A Lexicographic Optimization Algorithm. Autom. Remote Control 2004, 65, 363–368. [Google Scholar] [CrossRef]

- Miettinen, K. Nonlinear Multiobjective Optimization; International Series in Operations Research and Management Science; Springer: Boston, MA, USA, 1999. [Google Scholar]

- Allwein, E.L.; Schapire, R.E.; Singer, Y. Reducing Multiclass to Binary: A Unifying Approach for Margin Classifiers. J. Mach. Learn. Res. 2001, 1, 113–141. [Google Scholar]

- Badami, K.M.H.; Lauwereins, S.; Meert, W.; Verhelst, M. A 90 nm CMOS, 6μW Power-Proportional Acoustic Sensing Frontend for Voice Activity Detection. IEEE J. Solid-State Circuits 2016, 51, 291–302. [Google Scholar]

- Yang, M.; Yeh, C.; Zhou, Y.; Cerqueira, J.P.; Lazar, A.A.; Seok, M. Design of an Always-On Deep Neural Network-based 1-μ W Voice Activity Detector Aided With a Customized Software Model for Analog Feature Extraction. IEEE J. Solid-State Circuits 2019, 54, 1764–1777. [Google Scholar] [CrossRef]

- Price, M.; Glass, J.; Chandrakasan, A.P. A Low-Power Speech Recognizer and Voice Activity Detector Using Deep Neural Networks. IEEE J. Solid-State Circuits 2018, 53, 66–75. [Google Scholar] [CrossRef]

- Jeong, S.; Chen, Y.; Jang, T.; Tsai, J.M.; Blaauw, D.; Kim, H.; Sylvester, D. Always-On 12 nW Acoustic Sensing and Object Recognition Microsystem for Unattended Ground Sensor Nodes. IEEE J. Solid-State Circuits 2018, 53, 261–274. [Google Scholar] [CrossRef]

- Yang, M.; Chien, C.; Delbruck, T.; Liu, S. A 0.5 V 55 μW 64 × 2 Channel Binaural Silicon Cochlea for Event-Driven Stereo-Audio Sensing. IEEE J. Solid-State Circuits 2016, 51, 2554–2569. [Google Scholar] [CrossRef]

- Mayer, P.; Magno, M.; Benini, L. Self-Sustaining Acoustic Sensor With Programmable Pattern Recognition for Underwater Monitoring. IEEE Trans. Instrum. Meas. 2019, 68, 2346–2355. [Google Scholar] [CrossRef]

| LUT Output | Codeword Template | Vehicle Class | ||

|---|---|---|---|---|

| Noise | Car | Truck | ||

| Vehicle Presence | 4.1% | 68% | 97% | |

| Vehicle Type | 0.0% | 11% | 50% | |

| Device | Power | |

|---|---|---|

| MSP Circuitry (Always On) | RAMP | 43.0 W |

| “Sleep Mode” LUT Monitoring | ||

| “Wake Mode” LUT Monitoring | ||

| “Radio Mode” MCU Broadcast |

| Ground Truth | ||||

|---|---|---|---|---|

| Car (10 Samples) | Truck (10 Samples) | Noise (40 s) | ||

| Rumberg [6] | Car | 80% | 0% | 2 false alarms |

| Truck | 0% | 100% | 2 false alarms | |

| Noise | 20% | 0% | ||

| This Work | Car | 90% | 0% | 0 false alarms |

| Truck | 10% | 100% | 0 false alarms | |

| Noise | 0% | 0% | ||

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bhattacharyya, S.; Andryzcik, S.; Graham, D.W. An Acoustic Vehicle Detector and Classifier Using a Reconfigurable Analog/Mixed-Signal Platform. J. Low Power Electron. Appl. 2020, 10, 6. https://doi.org/10.3390/jlpea10010006

Bhattacharyya S, Andryzcik S, Graham DW. An Acoustic Vehicle Detector and Classifier Using a Reconfigurable Analog/Mixed-Signal Platform. Journal of Low Power Electronics and Applications. 2020; 10(1):6. https://doi.org/10.3390/jlpea10010006

Chicago/Turabian StyleBhattacharyya, Swagat, Steven Andryzcik, and David W. Graham. 2020. "An Acoustic Vehicle Detector and Classifier Using a Reconfigurable Analog/Mixed-Signal Platform" Journal of Low Power Electronics and Applications 10, no. 1: 6. https://doi.org/10.3390/jlpea10010006

APA StyleBhattacharyya, S., Andryzcik, S., & Graham, D. W. (2020). An Acoustic Vehicle Detector and Classifier Using a Reconfigurable Analog/Mixed-Signal Platform. Journal of Low Power Electronics and Applications, 10(1), 6. https://doi.org/10.3390/jlpea10010006