Quartz Resonator Based, 0.12 μW, 32768 Hz Oscillator with ±100 ppm Frequency Accuracy

Abstract

:1. Introduction

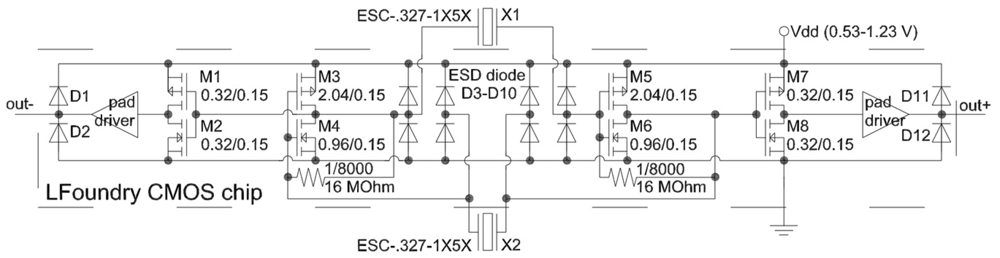

2. Proposed Circuit of the Low-Power Quartz Oscillator

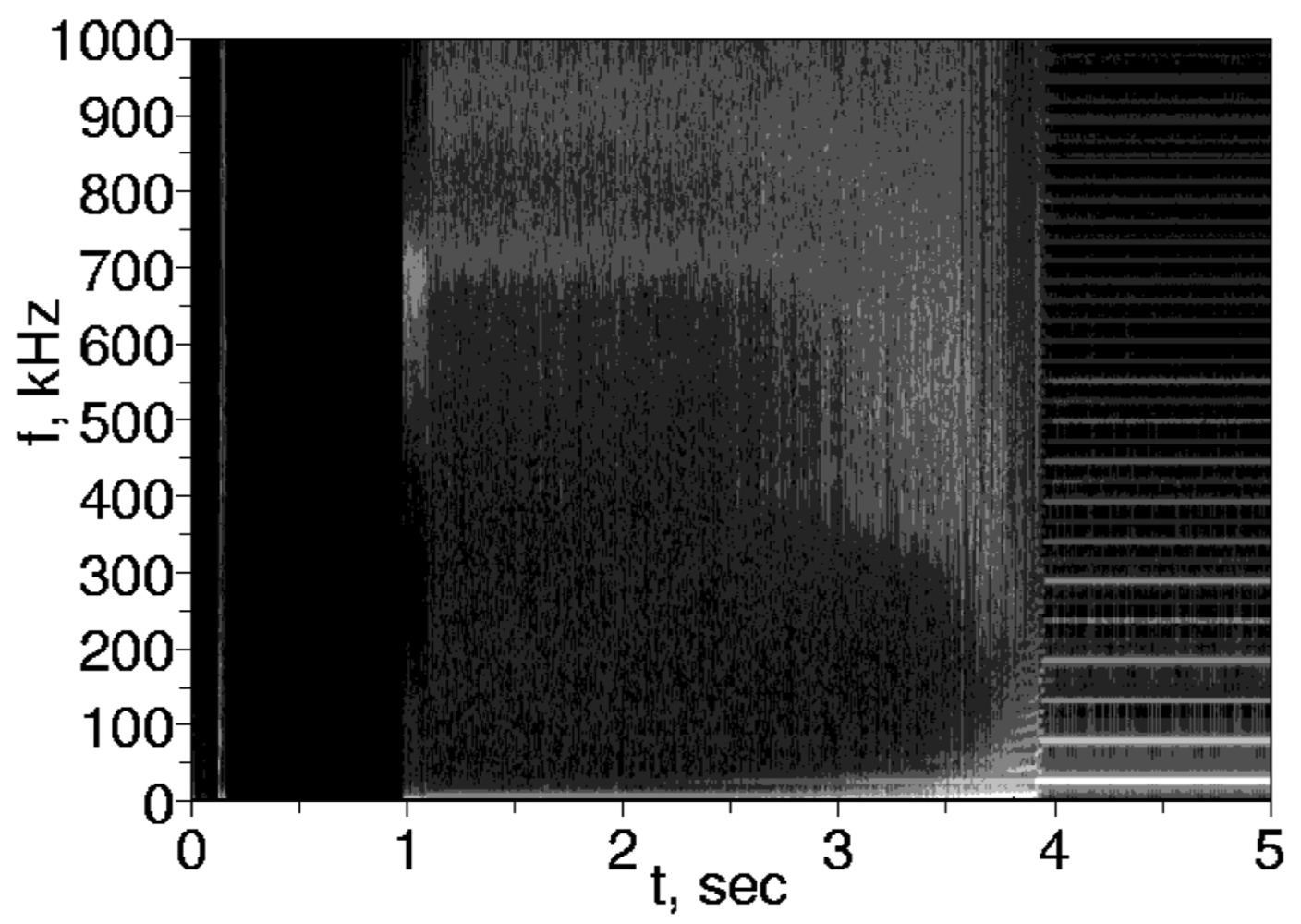

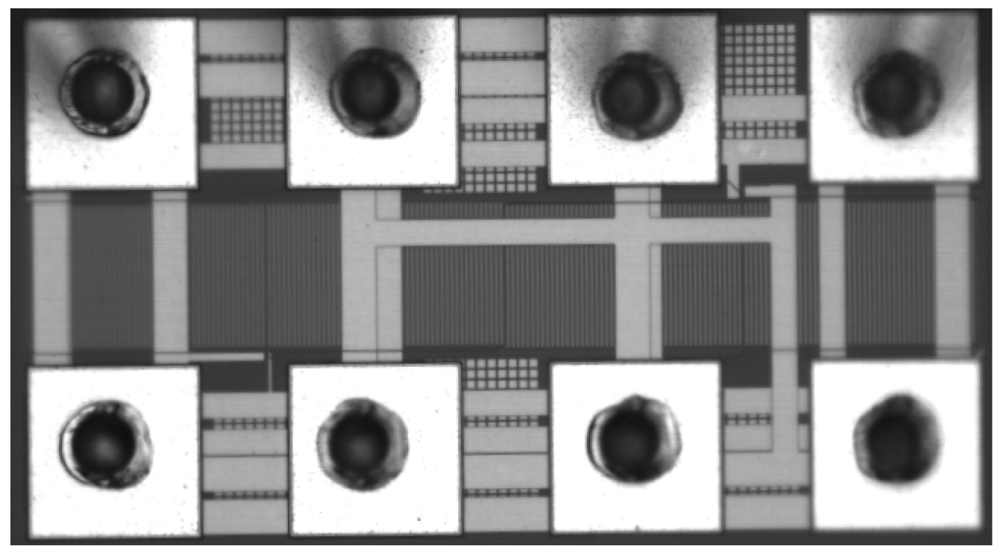

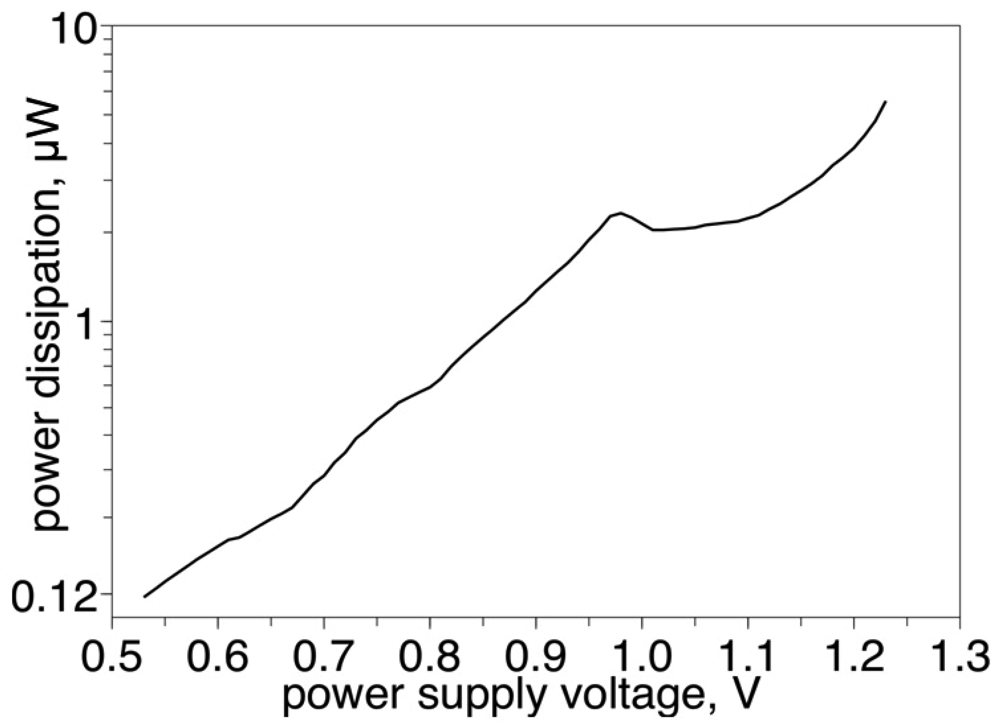

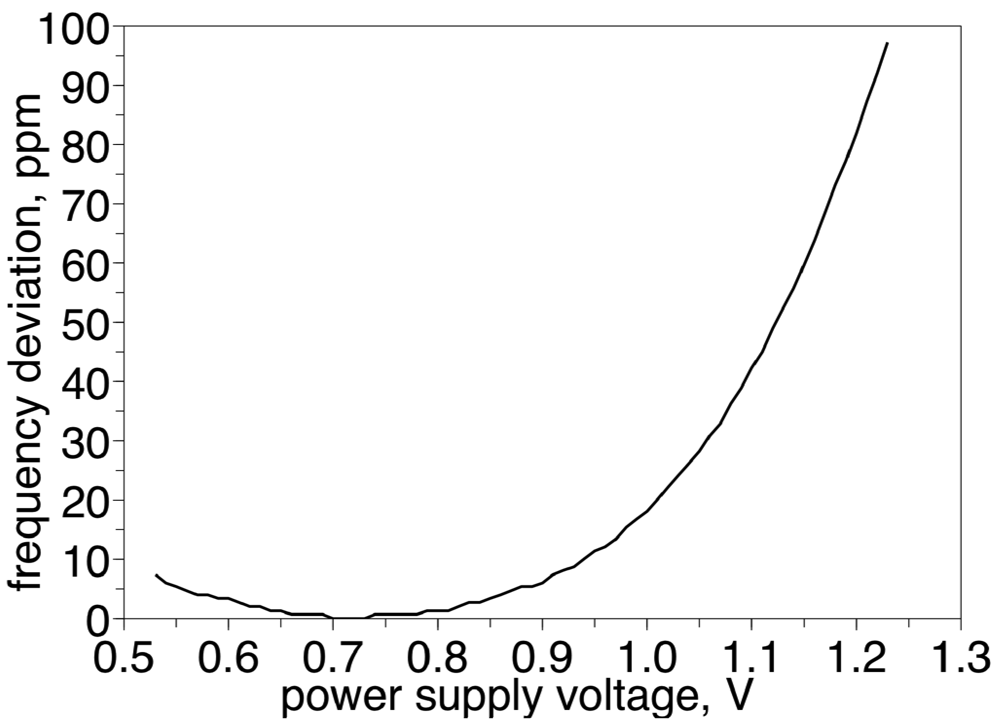

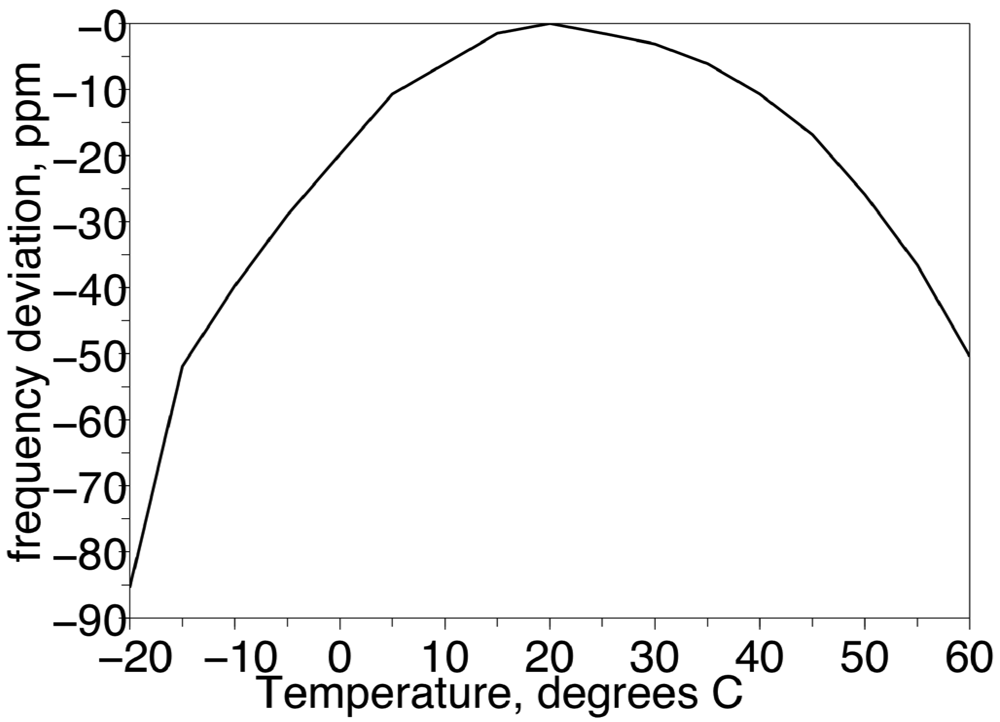

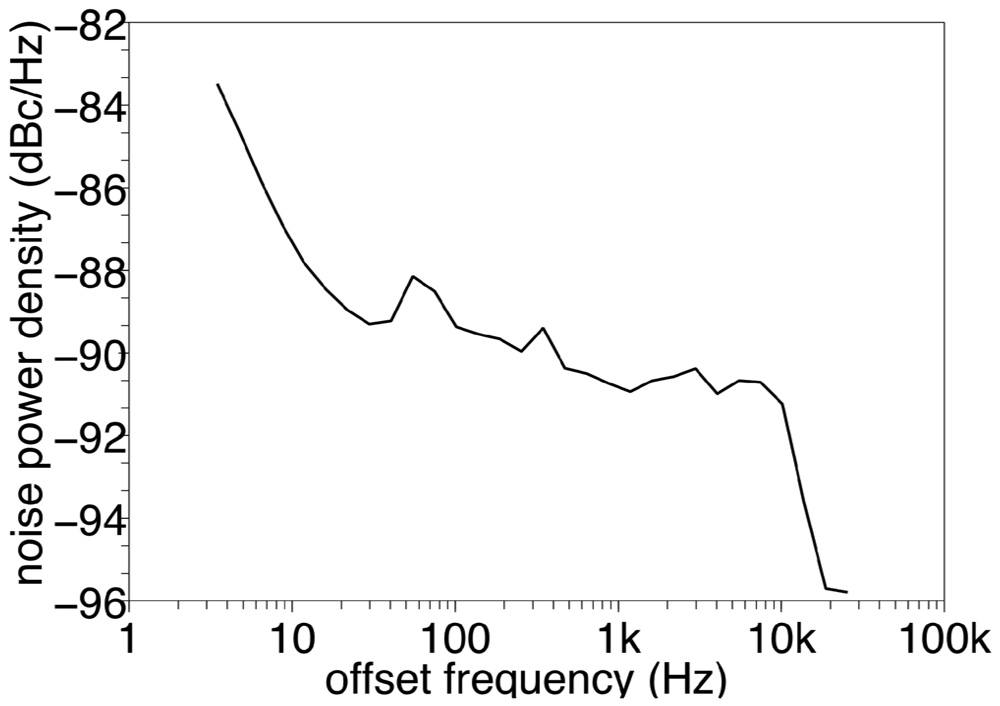

3. Experimental Results

4. Conclusion

| Reference | Power | F, MHz | Accuracy, ppm | Phase Noise, dBc | Technology |

|---|---|---|---|---|---|

| [1] | 3.0 μW | 0.032768 | 5 | −82@15 Hz offset | On-chip piezoelectric |

| [5] | 2.8 μW | 0.032768 | 50 | Not measured | Quartz resonator—parallel |

| [6] | 1.3 μW | 0.016384 * | 0.3 | Not measured | Quartz resonator—parallel |

| This work | 0.12 μW | 0.032768 | 100 | −83@3 Hz offset | Quartz resonator—serial |

Acknowledgments

References

- Ruffieux, D.; Pliska, A.; Krummenacher, F. Silicon-resonator-based, 3 μA Real-time Clock with 5ppm Frequency Accuracy. Proceedings of the International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 8–12 February 2009; pp. 209–211.

- Roessig, T.A.; Howe, R.T.; Pisano, A.P. Nonlinear Mixing in Surface-micromachined Tuning Fork Oscillators. Proceedings of the 1997 IEEE International Frequency Control Symposium; Institute of Electrical & Electronics Engineers: New York, NY, USA, 1998; pp. 778–782. [Google Scholar]

- Tuantranont, A.; Wisitsora-at, A.; Sritongkham, P.; Jaruwongrungsee, K. A review of monolithic multichannel quartz crystal microbalance: A review. Anal. Chim. Acta 2011, 687, 114–128. [Google Scholar]

- Pantalei, S.; Zampetti, E.; Macagnano, A.; Bearzotti, A.; Venditti, I.; Russo, M.V. Enhanced Sensory properties of a multichannel quartz crystal microbalance coated with polymeric nanobeads. Sensors 2007, 7, 2920–2928. [Google Scholar]

- Epson Toyocom SG-3040LC/JC Quartz Oscillator Datasheet. Available online: http://www.epsontoyocom.co.jp/product/OSC/set01/sg3040lc_jc/index.html (accessed on 10 May 2011).

- Aebischer, D.; Oguey, H.J.; von Kaenel, V.R. A 2.1-MHz crystal oscillator time base with a current consumption under 500 nA. IEEE J. Solid-State Circuits 1997, 32, 999–1005. [Google Scholar]

- Karthaus, U. A differential two-pin crystal oscillator—concept, analysis, and implementation. IEEE Trans. Circuits Syst. 2006, 53, 1073–1077. [Google Scholar]

- Thommen, W. An Improved Low Power Crystal Oscillator. Proceedings of the 25th European Solid-State Circuits Conference (ESSCIRC '99), Duisburg, Germany, 21–23 September 1999; pp. 146–149.

© 2011 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).

Share and Cite

Nizhnik, O.; Higuchi, K.; Maenaka, K. Quartz Resonator Based, 0.12 μW, 32768 Hz Oscillator with ±100 ppm Frequency Accuracy. J. Low Power Electron. Appl. 2011, 1, 327-333. https://doi.org/10.3390/jlpea1020327

Nizhnik O, Higuchi K, Maenaka K. Quartz Resonator Based, 0.12 μW, 32768 Hz Oscillator with ±100 ppm Frequency Accuracy. Journal of Low Power Electronics and Applications. 2011; 1(2):327-333. https://doi.org/10.3390/jlpea1020327

Chicago/Turabian StyleNizhnik, Oleg, Kohei Higuchi, and Kazusuke Maenaka. 2011. "Quartz Resonator Based, 0.12 μW, 32768 Hz Oscillator with ±100 ppm Frequency Accuracy" Journal of Low Power Electronics and Applications 1, no. 2: 327-333. https://doi.org/10.3390/jlpea1020327

APA StyleNizhnik, O., Higuchi, K., & Maenaka, K. (2011). Quartz Resonator Based, 0.12 μW, 32768 Hz Oscillator with ±100 ppm Frequency Accuracy. Journal of Low Power Electronics and Applications, 1(2), 327-333. https://doi.org/10.3390/jlpea1020327