Abstract

Field deployment is critical to developing numerous sensitive impedance transducers. Precise, cost-effective, and real-time readout units are being sought to interface these sensitive impedance transducers for various clinical or environmental applications. This paper presents a general readout method with a detailed design procedure for interfacing impedance transducers that generate small fractional changes in the impedance characteristics after detection. The emphasis of the design is obtaining a target response resolution considering the accuracy in real-time. An entire readout unit with amplification/filtering and real-time data acquisition and processing using a single microcontroller is proposed. Most important design parameters, such as the signal-to-noise ratio (SNR), common-mode-to-differential conversion, digitization configuration/speed, and the data processing method are discussed here. The studied process can be used as a general guideline to design custom readout units to interface with various developed transducers in the laboratory and verify the performance for field deployment and commercialization. A single frequency readout unit with a target 8-bit resolution to interface differentially placed transducers (e.g., bridge configuration) is designed and implemented. A single MCU is programmed for real-time data acquisition and sine fitting. The 8-bit resolution is achieved even at low SNR levels of roughly 7 dB by setting the component values and fitting algorithm parameters with the given methods.

1. Introduction

Recently, real-time sensing and detection are revolutionizing many services such as healthcare, home automation, transportation, etc. Moreover, there is a push to develop more field-deployable biosensors for medical diagnostics and environmental monitoring applications. Motivated by this, there has been a surge in the development of new transducers targeting a wide range of biosensing applications for detecting proteins, ions, temperature, etc.

Label-free impedance biosensors are famous prototypes for point-of-care real-time applications such as toxins, viruses, whole-cell, bacteria, nucleic acids, detection, or tissue impedance modeling [1,2,3,4,5,6]. Two-, three-, or four-electrode transductions are used for various impedance measurements. In general, the ratio between the voltage across the reference electrode (RE) and the working electrode (WE) and the current flowing between the working electrode and the counter electrode (CE) yields the impedance of a specific interface (solution electrode) [1,7] or tissue [8], cell culture [9], etc. The variable impedance of the transducer is generally estimated by AC electrochemical impedance spectroscopy (EIS) [1]. The EIS method measures the medium or interface’s impedance at multiple frequencies [10,11]. Next, proper fitting techniques estimate the impedance model from the spectrum [12]. However, for the development of a simple real-time, field-deployable readout interface, a single frequency AC excitation [1,3] is generally a good alternative for applications where the model of the interface or tissue is known a priori and the quantification of a specific analyte or change in the impedance due to bio-recognition is desired. One method to quantify the transducer impedance change is measuring the amplitude and phase of the response signal (current or voltage) with respect to a reference signal in real-time [13].

However, one challenge in the design of readout interfaces for label-free real-time single-frequency measurements is that the total change in the impedance of the transducers is often only a few percent over the entire full range of detection. For example, capacitive transducers for measuring certain hepatotoxins in water have been presented in [2], where the total electrode–solution interfacial capacitance changes by only 1% over the entire range of concentrations. A similar issue is associated with the developed label-free transducers for detecting Cholera toxins in [14] and Cryptosporidium at lower concentrations [15]. The impedance phase change at sub-Hz frequency is employed to detect human interleukin-8 in serum with sub-pg/mL sensitivity [16]. The results indicate a phase change of only over a baseline impedance phase of , at the minimum detection level and an overall sensitivity of 220.4 m°/decade (approximately 0.25%). The resistance of the ultra-sensitive interdigitated electrodes designed in [17] changes by roughly a couple of percent over the full range of PfHRP2—a malaria biomarker—concentrations in human saliva. The non-faradaic EIS biosensor for detecting C-reactive protein in a complex medium, such as human blood, reports a fractional impedance change of approximately 2.5% at the minimum detection limit [18]. The capacitance of the developed DNA sensors changes by roughly 3% for the reported concentrations [19]. To complicate matters, avoiding physical damage to the functional layer and nonlinear distortion effect on the response require that the magnitude of the applied AC excitation remain small (typically <50 mV) [1,3,7]. The result is that the absolute value of the transducer output voltage is small, leading to a full-scale change in the voltage in the order of hundreds of microvolts. Moreover, suppose we assume that the transducer’s output voltage will be detected with a modest resolution of 8-bits. In that case, the sensor must be able to detect changes in the transducer’s output voltage that are less than 1 μV.

The readout process for the abovementioned sensitive transducers is straightforward, using laboratory-grade bench-top test equipment for characterization, but very sensitive instrumentation is required for large-scale deployment. As a solution, differential sensing with a bridge circuit that acts similar to intermediate secondary transduction and a sensitivity booster is proposed in [20]. Two capacitive transducer chips, each with a pair of electrodes (functionalized WE and chemically non-functional CE providing the electrical signal path in the solution), are placed in the opposite bridge legs and generate a differential sensing response. Although with the differential capacitive bridge designed in [20], the effects of common-mode noise, drift, and temperature variation can be further decreased and sensitivity enhanced, there is still a need for small, inexpensive, and low-power readout to reach a particular required resolution and make the commercialization of the developed transducers in this structure feasible [8,9].

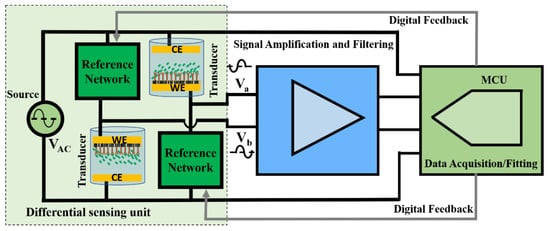

Figure 1 shows the block diagram of the differential sensing unit utilized in [20] interfaced with high-level generic blocks of a readout system, amplification, filtering, and digitization. The transducers are designed to sense the change in the transducer impedance due to bio-recognition with respect to the reference networks differentially. Amplification/filtering is typically required with the expected weak and noisy sensor response. For real-time and low-cost operation, an MCU performs both the task of data acquisition and processing (fitting) and any extra required digital adjustments. The MCU acquires the response and excitation source signals and measures the amplified response signal magnitude and differential phase (with respect to the excitation source) in real-time.

Figure 1.

General block diagram of a differential bio-sensing unit interfaced with signal amplification and filtering unit and a microcontroller (MCU) for low-cost real-time operation and field deployment. The transducers are designed to sense the change in the transducer impedance due to bio-recognition with respect to the reference networks differentially. Amplification/filtering is typically required with the expected weak and noisy sensor response. For real-time and low-cost operation, an MCU performs both the task of data acquisition and processing (fitting) and any extra required digital adjustments.

Some factors limit the performance of the generic sensor interface units shown in Figure 1 if implemented with discrete commercially available components. Typical precision opamps that would be used in this application have input referred noise voltages that are on the order of tens of . Therefore, to maintain a practical input signal-to-noise ratio (SNR) greater than 1, with microvolt-level transducer output voltages, the effective noise bandwidth of the sensor interface circuit could be limited to only a few tens of hertz. Moreover, approximately 60–80 dB voltage gains will be required to effectively use an ADC for data acquisition. Extreme amplification and filtering require highly accurate component matching, extensive shielding, and careful circuit design. Data acquisition and the specific algorithm implemented in the MCU for data processing in Figure 1 should be performed simultaneously with no need to transmit or store the raw data in external memory. Therefore, the algorithm processing speed and the ADC sampling rate should be carefully adjusted. Lower complexity, power consumption, and overall cost are other design goals to avoid limiting the potential of the sensor.

This paper proposes a comprehensive, fully differential readout interface design suitable for tiny sensor response signals generated differently. A study of the design tradeoffs between overall sensor system complexity and performance at low cost, particularly with small fractional detection impedance change (<1%), is given. Each readout interface block shown in Figure 1 was analyzed and designed based on the required resolution, overall gain, SNR, etc. It is shown here that extreme amplification and filtering requirements can be met with the careful design of a two-channel digital acquisition and processing (sine fitting) utilizing a single microcontroller. A theoretical design procedure and a practical discrete implementation example are presented here, targeting mainly real-time, low-cost operation for less than full-scale change in the transducer’s output voltage, and an 8-bit characteristic change resolution. In Section 2, design methods considering the most important performance parameters, such as overall gain, bandwidth, SNR, common-mode rejection ratio (CMRR), sampling rate, signal fitting algorithm, and real-time implementation for each of the readout blocks; amplification, filtering, and data acquisition/processing are explained in detail. The implementation results, board characterization, and real-time operation and sensitivity verification are presented in Section 3.

2. Materials and Methods

A reasonable assumption for the differential sensing unit shown in Figure 1 is that less than a 1% full-scale response change with the bio-recognition event is expected before any amplification. The change in the transducer’s impedance () has a linear relationship with the change in the medium’s concentration. Thus, the differential output voltage of the sensing unit is linearly related to the transducer fractional impedance change, and the source voltage (1) shows this linear relationship.

where is the differential output voltage of the sensing unit, is a proportionality constant, is the transducer fractional impedance change, and is the AC excitation source voltage.

Before discussing the amplification stage, it is mandatory to examine some typical values for the expected differential voltage. Let us consider a typical excitation signal (VAC) with an AC amplitude of 1–100 mV. Assuming the case with , and the maximum change in the amplitude of the bridge output will be less than . If the target resolution for the sensor is set to the typical 8-bits, then the expected least-significant bit (LSB) of the response will be several microvolts. With the minimum response signal level knowledge, the proceeding amplification and filtering stages can be designed, and parameters such as required gain, matching, bandwidth, etc., can be decided. However, dealing with such small signals requires the careful consideration of parasitic, noise, and any unwanted interfering signals and trying to minimize such effects and achieve the dynamic target range; these design considerations are discussed in the following.

2.1. Amplification and Filtering Analysis

Two critical design parameters for the amplification and filtering unit will impact the accuracy and precision of a fully differential readout circuit for detecting tiny fractional changes at the output: common-mode-induced differential conversion and noise. The common mode rejection ratio (CMRR) criteria here is the amplification and filtering interface’s ability to reject the common mode output voltage (for example, an equal DC signal required to bias the differential transducers) and amplify the differential output voltage change due to the transducer impedance change with detection. Failing to reject the common mode at the output, considering the high required differential gain, will lead to an unpleasant common mode to differential conversion that not only gives rise to a false detection signal but also limits the dynamic range. Noise will affect the lower detection limit and shrink the dynamic range. Various sources causing common-mode to differential conversion and SNR degradation at the interface’s output before ADC are analyzed in the following section. Based on this analysis, parameters such as the gain of each stage for a cascaded design, effective noise bandwidth (ENB) of the filter, and the required matching sensitivity can be determined and based on the best achievable SNR at the board output, a potential suitable fitting algorithm in the data acquisition unit can be picked and designed.

2.1.1. Common Mode to Differential Conversion

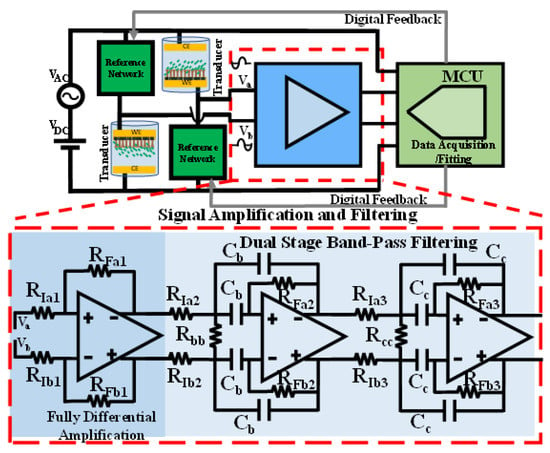

With the typical available full-scale voltage of the ADCs,, on the order of (1–5 V), a three-stage amplification and filtering interface is proposed here, as shown in Figure 2. One stage of amplification and two identical bandpass filtering stages are responsible for providing a total differential gain that amplifies the initial full-scale differentially sensed output of roughly to match the full-scale range of the ADC. A multiple feedback bandpass topology is chosen for the fully differential filters [21]. The filter’s gain, center frequency, and bandwidth can be flexibly tuned with the multiple feedback topology. Therefore, a total differential gain in the order of 70–80 dB is approximately required. To estimate the amount of needed common mode rejection, consider the case with in (1). With equal to tens of millivolts (based on the excitation source amplitude ) and the differential LSB change at the sensing unit output, , will only be several microvolts.

Figure 2.

The three-stage amplification and filtering unit, proceeding the differential sensing unit and succeeding the data acquisition and fitting unit. A fully differential amplification followed by a cascaded two-stage bandpass filter provides the differential gain and filters the unwanted noise for certain minimum SNR. It is critical to maintain good matching in the feedback ratios of the peripheral components, as shown in (3), to achieve the overall target CMRR.

and will be amplified by the common mode to differential gain and differential gain, respectively. To maintain the desired resolution, criteria (2) should be satisfied so that the differentially amplified sensing signal at the LSB level is at least twice the interference caused by the common mode to differential conversion:

where , is the common mode-induced differential gain, , is the differential gain. and are the minimum differential voltage and the common mode voltage at the output of the sensing unit, respectively. The abovementioned criteria (2) sets the minimum for the , to around which, with of around 70–80 dB, requires the to be at least to . If the required minimum is not reached, the target resolution will not be achieved.

- Effect of component matching and tolerance

Ideally, the CMRR of a fully differential circuit would be infinite. However, in reality, the CMRR is limited by the CMRR of each stage in the circuit and by matching the peripheral components. Typical fully differential amplifiers for precision measurements provide relatively high CMRR values of around . However, when configured as a fully differential amplification stage, as shown in Figure 2, the CMRR of each stage is determined not only by the CMRR of the Opamp but also by the matching between the two symmetrical feedback ratios and . If and , therefore, and . The stage CMRR is derived in [22]:

where is the effective CMRR of each stage, is the typical CMRR of any given Opamp, and is the feedback matching ratio. Therefore, inevitable degradation in is expected with the worse matching ratio of the feedback networks.

For a given stage with a differential voltage gain, , , the resistance, ’s tolerance , is included as . Feedback ratio matching is related to the component tolerance using the following derivations:

For ,

where is the percent tolerance of a resistance. Based on (6), a lower component tolerance is required to maintain a given feedback-matching ratio for a higher differential gain of a stage. For the design and implementation of a multistage fully differential amplification unit, as shown in Figure 2; (3), and (5) determine the required degree of component matching tolerance based on the known differential gain distribution and total .

- Effect of cascaded stages

The abovementioned design criteria are regarding singular stages; now, given that several stages participate in the amplification and filtering before the data acquisition, it is helpful to understand each stage’s contribution to the total CMRR. In [23], the contribution of each stage, on the total CMRR, of a cascade of 3 differential stages is investigated, and an approximate formula, (6), is derived.

where, , is the total effective CMRR of the cascaded stages, is the CMRR contribution of the individual amplification stage, , and are the differential to differential and common mode to common mode gains of each of the 3 stages, respectively. If the output common-mode voltage,, of the fully differential amplifiers before ADC, are set externally at , to cover the full ADC dynamic range equally, then the for all stages would be 1. Thus, if the two filtering stages are identical, with the same gains, based on the (6) effect of the CMRR of the first stage on the is dominant compared to higher stages. Therefore, component matching in the first amplification stage significantly affects the total CMRR and common mode to differential conversion, and this is specifically important for implementation and debugging.

2.1.2. Noise Analysis

In addition to the common-mode-to-differential conversion, noise is also a primary limitation on the performance of the sensor readout circuitry. The presence of thermal noise, if the noise floor is greater than the detection signal around the lower detection limit, will decrease the dynamic range. Two primary sources of noise are involved in the general block diagram of the biosensor in Figure 1.; the total noise generated by the electrodes and differential sensing unit and noise generated by the amplification block. Quantization noise and sampling clock jitter are also issues, but the quantization noise effect is negligible if the utilized ADC resolution is higher than the required response target resolution. The clock jitter gains more importance at high sampling rates (hundreds of MS/s or GS/s) for higher frequency excitations; this effect will be considered and discussed separately in sub-Section 2.2.2.

Given the small magnitude of the electrode response on the order of several microvolts at LSB of detection, the noise of proceeding stages plays a vital role in determining the minimum expected SNR. The typical input referred voltage noise density for differential precision amplifiers is several . If a gain of 70–80 dB is targeted utilizing the multistage amplification, the total output noise voltage density contributed by the amplifiers will be on the order of several . Moreover, the noise associated with the peripheral resistors and noise from the transducer itself will add to the total output noise density. Therefore, considering wide-band amplification stages without filtering, the minimum SNR value before ADC could obtain even less than . However, the amount of in-band noise can be significantly reduced if bandpass filtering is performed. The quantitative analysis of the expected noise level presented in the following determines the method to calculate the required reduction in noise and effective noise bandwidth (ENB) of the filter.

The noise model of the electrodes and the equivalent circuitry with noise sources for the differential sensing unit and amplification stage are required for the noise analysis. The differential bridge model utilizing capacitive transducers presented in [20] is adopted here as the differential sensing unit. The noise model for the differential sensing unit with the noise sources included for noise analysis is shown in Figure 3a.

Figure 3.

Utilized noise models for the two primary noise contributing blocks; (a) the bridge as the differential sensing unit, with the series RC model for the capacitive transducers and balancing networks, all the noise sources in the bridge are thermal type (b) differential amplification stage with the associated thermal noise sources for the peripheral resistors, and input-referred current and voltage noise sources of the Opamp.

In Figure 3a, and are the RC-balancing networks made with arrays of digitally controlled capacitors and resistors to balance the bridge for the AC signal path. resistors are DC-balancing resistive paths that provide a stable DC bias to the working electrodes and equal DC voltage at and . The solution–electrode interface in this study is modeled with series RC, the resistive parts ( and ) are modeling solution resistance and the capacitive parts ( and ) are the interface capacitance. Gesteland et al. show in [24] that the noise of a metal microelectrode can be modeled as the thermal noise of a resistance in a narrow band of frequency, where the corresponding resistance is the real part of the electrode–solution interface impedance. Therefore, the associated noise sources with the electrodes and balancing resistors in the differential sensing unit is in series with the corresponding resistances in Figure 3a and are all representing thermal noise model for the resistance, i.e., with units of . is the Boltzmann’s constant, is the absolute temperature and is the corresponding resistance. For a perfectly matched and balanced bridge case, with , , the noise contribution of the differential sensing unit can be derived based on the model in Figure 3a as follows:

where is the output referred noise power density of the bridge, and , is the angular frequency of the operation. The electrodes makeup and solution conductivity for capacitive transducers are set so that at the frequency of operation, the reactive part of the interface impedance is dominant, [1]. The value of the DC-balancing resistors, , are much larger than the magnitude of the transducer impedance not to load the functional electrode impedance and decrease sensitivity, therefore, knowing that leads to [20].

Based on the abovementioned considerations, (7) can be simplified as follows:

The noise model for a fully differential Opamp with the associated feedback resistors [25,26] is shown in Figure 3b. Again, the resistors have the thermal noise voltage model in series, and , and are the Opamp input referred voltage and current noise sources, respectively. The power density of the Opamp noise sources have the units of and are defined as; , . and , are the opamp input referred voltage and current white noise powers. and , are the voltage and current noise power density corner frequencies. The output referred noise power density of each amplification and filtering stage is , For the case of a noiseless excitation source, the total root mean square (rms) noise voltage at the output of the amplification and filtering board is obtained from (9).

where is the total rms noise voltage at the board output. Here, it is also assumed that the output common mode voltage is set externally and adequately filtered. The output referred noise power density of the bridge, , and the output referred noise power density of each amplification and filtering stage, , is multiplied by the square of the noise gain, of the proceeding stages, then summed and integrated over the bandwidth of the interface (lower, , to higher, , cut off frequency). The output referred noise power density of each differential amplification and filtering stage is obtained from (10).

where , and . Assuming , , and , yields (11). For a 4th-order bandpass filter (consisting of two stages in this design) [25,27] Note that if and , the effect of flicker noise must be included, as well. Based on (11), the ENB of the required overall filtering to obtain 8-bit resolution at a given expected SNR can be determined using the typical application values for the bridge components.

Thus, the minimum expected SNR is computed by knowing the minimum expected rms differentially sensed and amplified signal with a defined resolution and the total rms noise signal after filtering. The required ENB can be adjusted accordingly.

where is the minimum expected rms differentially sensed and amplified signal for a given resolution. In practice, however, for low-frequency () measurements, the effect of flicker noise cannot be neglected entirely, and other sources of non-ideality, such as the transducer functional layer instability and environmental noise, may also add to the estimated total output referred rms noise, and even lower ENB might be required. There are also practical limitations on realizing filter bandwidth on the order of 10s of hertz. The minimal bandwidth leads to a longer response settling time for step-type input variations. Sometimes the dynamics of analyte binding are fast, and the readout interface should be able to follow the relatively fast variations in the response signal. Therefore, the bandwidth should be set considering the amount of allowable noise and the fast settling requirement. Although a higher filter bandwidth leads to worse SNR, proper further digital signal processing techniques with suitable sine-fitting algorithms can effectively act as an additional filter and even extract the signal information buried in the noise, and this is described next.

2.2. Real-Time Digitization and Fitting

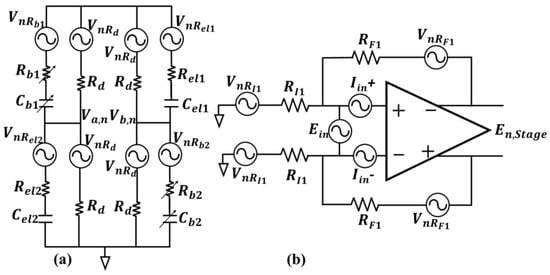

For any biosensor’s deployment, the transducer’s characteristic change should ultimately be quantified. In general, the response is an electric DC or AC signal that needs to be acquired in real-time for field deployment. The complex impedance of the solution–electrode interface can be measured in real-time by extracting the amplitude and phase data from the amplified transducer’s response signal. While amplitude information can be obtained using the response signal, the phase should be measured differentially with respect to some reference signal. In the two-channel data acquisition system, shown in Figure 4, the ADC alternatively samples the excitation voltage (i.e., the source signal) as a reference for differential phase measurement and the output of the amplification/filtering block (i.e., the response signal). To automate this, the digital system must be able to extract the amplitude and differential phase quantities from the digitized signal using a specific algorithm and in real-time for field deployment. Simultaneous data acquisition and real-time processing become feasible using ring buffers without sacrificing memory. The ADC samples the source and response signals and writes the data into the designated ring buffer. A sine fitting algorithm implemented within the microcontroller reads the samples consecutively and applies the fitting algorithm to a specific number of samples as a batch.

Figure 4.

A single microcontroller is utilized to both digitize the source and response signals. The built-in ADC samples the source and response signals alternatively. The samples are stored in ring buffers, and MCU computes the amplitude and differential phase information. The results are stored in a ring buffer for external communication.

The fitting results containing the amplitude and differential phase information are written in another ring buffer. The MCU uses the results for balancing-related computations or external communication via UART. The key parameters for the data acquisition and fitting unit design are the ring buffer length, ADC sampling rate, type of the sine fitting algorithm, and the number of samples required for each round of fitting, considering the expected signal and noise levels. Additionally, as the processing occurs in real-time using a single MCU, it requires a computationally efficient code and algorithm. The design process is explained in the following.

Sine-fitting algorithms are traditionally seen in ADC testing and characterization [28] and impedance/frequency response measurements [29].

Researchers have recently recognized the utility of sine-fitting algorithms for the real-time processing of the transducer output voltage [29,30]. There are many different approaches to sine-fitting, each with varying degrees of suitability in low-cost, real-time sensing applications. To design an accurate real-time sine fitting, the designer must set many parameters such as sampling rate, SNR, ADC resolution, record length, etc. Unfortunately, there is no general study of important factors for sine fitting of biosensor response in real-time; thus, the designer must study these tradeoffs for each design. This section will present a detailed analysis of the various tradeoffs for the abovementioned design parameters concerning sensing requirements. The results will help the designer pick the proper sine fitting algorithm based on the available budget, expected noise floor, required dynamic range, and accuracy with specific DSP hardware capabilities.

In general, sine-fitting algorithms can be classified as either iterative or non-iterative. Although providing better accuracy in some applications, iterative algorithms, such as the IEEE standard 4-parameter sine fitting [28], are not the best candidates for real-time implementation. By nature, the convergence of these algorithms might require multiple iterations, and data storage requires additional memory usage. Non-iterative algorithms, on the other hand, offer better real-time solutions, considering their relatively more straightforward implementation. However, the accuracy of a non-iterative approach with small and noisy signals and compatibility with low-cost general-purpose microcontroller implementation needs to be considered for real-time and field deployable applications.

The non-iterative sine parameter extraction algorithm, IEEE standard 3-parameter sine fit (3PSF) [31], is reviewed for the design requirements in this paper.

The 3-parameter sine parameter extraction is based on the assumption that the excitation source frequency () is known, and only the amplitude, initial phase, and DC offset of each singular channel are estimated. A brief theoretical review of the 3PSF is available in [31,32,33]. The real-time implementation of 3PSF in a low-cost microcontroller can be greatly simplified by using coherent sampling; therefore, simplified 3PSF with coherent sampling is considered for performance comparison here. Consider a sequence of samples of a sine wave represented as follows:

where is the sampling rate for both channels (source and response), sine wave frequency , amplitude , initial phase and offset . The source and response signals are derived from the same generator; therefore, they share the same frequency . If the ratio of is known, the 3 parameters , , and can be estimated for each channel, in the least squares sense, using 3PFS, as shown in [31]. The real-time implementation of 3PSF in a low-cost microcontroller can be significantly simplified by using coherent sampling; therefore, simplified 3PSF with coherent sampling is considered for performance comparison here.

If the estimated signal, is expressed as follows:

With some simple algebra using the coefficients and for each channel, the amplitude and phase of are estimated as in [31].

where and are the estimated amplitude and initial phase. Coherent sampling is achieved when , where and are relatively prime integers and represent the total number of input periods in the record and the total record length, respectively. Under the assumption of coherent sampling, , and are defined as follows:

For a known input frequency, the given ratio of and the ratio of remains fixed. Hence, a lookup table rather than a function can be used to compute the sinusoidal values, ) and , dramatically reducing the required processing time. A primary concern, however, remains the effect of uncertainty in the ratio, as well as jitter in the sampling clock, in the presence of very low SNR signals. Therefore, the effects of the oversampling ratio of the ADC and the SNR of the signal, as well as clock jitter and computational resource requirements, will be studied before algorithm implementation. The principal investigated performance metrics in the analysis and comparisons are the estimated percent amplitude error (), and percent differential phase ( = ) error ().

2.2.1. Additive White Gaussian Noise

To see the effect of noise on the resolution of the sensor, let us assume the noise, , is additive white Gaussian noise. For a noisy, coherently sampled signal,

the estimation parameters in (17) are independent and unbiased in the presence of white Gaussian noise. In this case, the expected values of the estimation parameters are: , , and . The covariance matrix, , of the 3PSF with coherent sampling is [32]:

where is the variance in the additive white Gaussian noise. The estimated amplitude parameters, and , in the presence of noise, are statistically analyzed and defined in [32,33], with their expected values and , and equal variance . The amplitude and initial phase and , are functions of the statistically defined random variables and . The mean and variance of a function of two random variables , can be approximately derived based on a Taylor series expansion of the function about the expected values of the associated random variables , as shown in [32,34]:

where and are the mean and variance of the function . Using (19)–(21), the mean and variance of the estimated amplitude and initial phase can be derived as a function of SNR:

where , and , are the mean and variance of the estimated amplitude and initial phase, respectively. Based on (22), the amplitude estimation is biased with noise present. When alternate sampling is used, as shown in Figure 4, the initial phase of the response signal is measured with reference to the source signal, therefore:

where is the variance of the differential phase, and are the variance of the initial phase estimation of response and source signals, respectively. When the source and response signals are corrupted by additive noise, the initial phase estimations are independent (i.e., = 0). From (23) and (24), if the same record length is assumed for both channels (N), the variance of the differential phase can be derived as:

The 3PSF algorithm can effectively reduce the effect of noise on the acquired data based on (22)–(25). If the ratio of is chosen considering the actual SNR at the lower limits of detection, better resolution can be achieved.

2.2.2. Sampling Clock Jitter

Sampling clock jitter causes uncertainty in 3PFS estimation results. The uncertainty caused by sampling clock jitter can be modeled as a normally distributed random variable with zero mean and standard deviation equal to [35]. A coherently sampled signal with jitter is modeled as follows:

where is a normally distributed random variable with zero mean and standard deviation . In the presence of jitter, the 3PSF is no longer an unbiased estimator for and , the expected values for the three parameters are as follows:

If the initial phase, , is assumed to be constant, the covariance matrix of the estimator in the presence of jitter, , is derived in (30). The approximate mean and variance of the amplitude and initial phase estimation with jitter present, using (27) and (28), are as follows:

In the presence of jitter, the estimations for the source and output initial phases are independent, i.e., . The differential phase variance is derived using (24) and (33):

If we examine the mean error in the estimated amplitude using (31) from above:

where is the amplitude estimation relative error. Although it is seen in (35) that the amplitude mean error will never reach zero even with the largest number of samples for 3PSF, which is also claimed in [35], with an optimized large record length 8-bit detection resolution for both amplitude and phase is achievable even at non-realistically high jitter standard deviation of around π radians.

Based on the obtained results, 3PSF can maintain the target 8-bit resolution at jitter standard deviations, even close to 2π radians, by controlling the record length.

It is worth mentioning that the obtained result for this analysis depends on the source and sampling frequency. The maximum allowable jitter using an ADC with a resolution of bits, and a sine wave input with an amplitude equal to the ADC full-scale and a frequency of , to have a jitter-induced error of less than half LSB is inversely proportional to ( [36]. The maximum allowable jitter, therefore, grows smaller if the sine wave has an amplitude smaller than full-scale, higher frequency, and with higher resolution for the ADC. For example, jitter considerations gain more importance for sensors with hundreds of MHz or GHz level excitation frequencies or when the response signal is not sufficiently amplified to the ADC’s full-scale range at lower detection limits.

2.2.3. Non-Coherency

A fundamental assumption while simplifying the implementation of the real-time 3PSF algorithm is that the data belong to a coherently sampled sine wave. However, depending on the source sine wave generator’s accuracy level, the desired source frequency may deviate from its actual value. The result will be that the record will not contain exactly cycles of the input signal, and the readily hard-coded lookup table for computing the sinusoidal values, ) and . will no longer represent correct samples, leading to errors in the estimated amplitude and initial phase. The effect of a shift in the source frequency, , can be modeled by assuming a shift in the such that [32]:

where is the integer part, and is the fractional part of the residue. The result is a shift in the number of periods being sampled. Now, if the cycles in the presence of shift in , are , the actual waveform, can be expressed as follows:

where are the samples of the waveform, including a frequency deviation. Using (15) and (17), the amplitude is estimated as follows:

which can be further simplified as a function of to be:

The initial phase estimation, as a function of , can be derived using (16) and (17):

which can be further simplified and written as a function of frequency deviation, :

With the realistic assumption that the shift in the input frequency is much smaller than the sampling frequency (), (39) reveals that the amplitude estimation accuracy is highly dependent on the record length . The larger the record length, the greater the amplitude estimation error for a given On the other hand, if , (41) simplifies as follows:

(42) indicates that, with a shift in the input frequency, regardless of the size of the sample record, there will be a linear phase error associated with the phase estimation. This error can be effectively mitigated if the output signal phase is measured with respect to a signal that shares the same frequency generator with the response.

2.2.4. Real-Time Microcontroller Implementation Considerations

For real-time implementation, any algorithm must perform mathematical operations with the individually taken samples from each channel, store the results in specific variables, and regularly update them with each incoming sample. The implementation cost is, therefore, the number of mathematical operations, functions, lookup tables, and the number of memory positions to hold the variables per fixed amount of data within each recording. One can estimate the execution time based on the number of clock cycles required by a specific MCU for each math operation. For the simplified 3PSF with a known excitation frequency, the values of and can be pre-computed using a singular lookup table. For comparison, the non-iterative ellipse fit algorithm [37] requires additional matrix operations other than the trigonometric functions and square root calculations that could be implemented with lookup tables. The real-time 3PSF is efficiently implemented within an MCU, with the computational cost as low as six variables, four multiplications, six additions, and one lookup table.

3. Results

Provided the theoretical analysis of the critical factors limiting the performance of a fully differential amplification/filtering and data acquisition/processing board, a readout interface is designed, fabricated, and tested for target 8-bit impedance sensing resolution. Board implementation and performance verification procedures are discussed in this section.

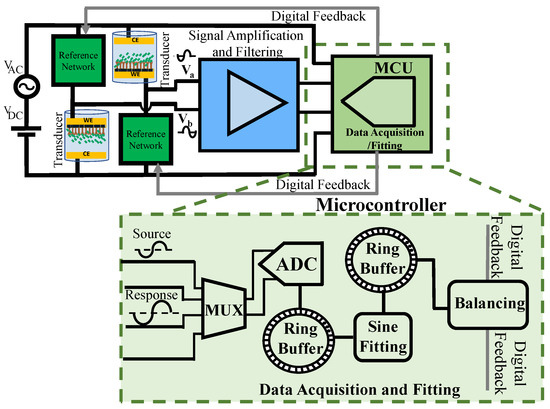

3.1. Differential Amplification and Filtering Implementation

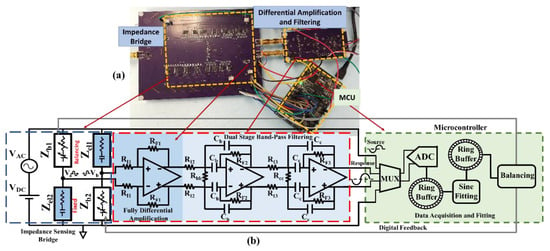

The Block diagram and the implemented boards of the amplification and filtering units interfacing a differential impedance sensing bridge are shown in Figure 5. A custom differential impedance sensing bridge with fixed series RC impedances ( and ) mimicking the electrode–solution interface impedance and balancing networks ( and ) composed of a digitally tunable resistor and capacitor array [20] is interfaced with the designed readout for performance verification. The DC biasing resistors () are not shown on the schematic for simplicity but are included on the board, as shown in Figure 3a. The first fully differential amplification stage is fabricated on the same board as the differential sensing unit to minimize the interferences caused by wiring and external connections. Details about the part selection and component values using the proposed design methodology are explained in the next section.

Figure 5.

(a) The implemented amplification and filtering board interfaced with the differential impedance sensing unit: (b) The block diagram of the differential impedance sensing unit and the developed readout. The first amplification stage is placed on the same board as the sensing unit to avoid interferences with the small sensing response signal caused by external connections.

3.1.1. Effect of Component Matching and Tolerances

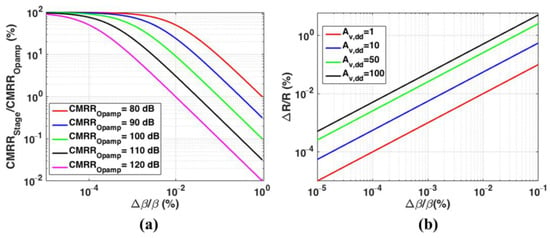

The three-stage amplification is configured to provide a total differential gain of 70 dB, to amplify the sensing unit’s full-scale output to of the ADC. The differential precision amplifier, Analog Devices Inc., Wilmington, MA, USA, LTC6363 is picked as the critical component of the amplification and filtering unit. The typical , for LTC6363 is . To maintain a total of around for the readout, a common mode-induced differential gain of around is required based on (2). Figure 6a shows the percent degradation in for various , versus the percent feedback matching ratio obtained from (3). Given a typical value of , feedback matching ratios better than are required to obtain a of . A stable common-mode voltage is provided for each differential difference amplifier using an on-board voltage regulator, Analog Devices Inc. LT3021, and the voltage amount is equal to half of the ADC full-scale reference voltage (0.6 ). Therefore, considering (6), adjusting the feedback matching ratio of the first amplification stage plays a critical role in the total readout .

Figure 6.

(a) Percent degradation in the ratio of the CMRR of a fully differential stage () and Opamp typical CMRR () for various versus percent change in matching ratios of peripheral resistors constructing the feedback network (); (b) Percent resistance tolerance () for various differential stage gain, , versus percent feedback ratio mismatch ().

The plots of the required percent component tolerance for various stage gain, , versus percent feedback ratio mismatch using (5), are shown in Figure 6b. Stages with higher allocated differential gain are less sensitive to component tolerances to obtain a given feedback matching ratio.

The peripheral surface-mount resistors and the capacitors of the differential amplification and filtering circuit were measured one by one in every purchased batch (containing at least 10 with 1% tolerance), and the ones with the closest values to obtain the matching ratio of better than 0.001% were mounted on the boards. The values of the resistors in the amplification and filtering stages to achieve a gain distribution of are; .

3.1.2. Noise Considerations and Filtering Unit

The input referred noise voltage, and current of the LTC6363 are 2.9 and 0.55 , respectively. With the known gain distribution and resistance values of the amplification and filtering stages and typical values for the electrode impedance models, using (8) the output referred noise of the readout board before ADC is . For an 8-bit resolution and 1% change in the impedance and the LSB of the differentially amplified sensing signal with the gain of , is . Considering the fast response settling requirements, by picking an ENB of , the expected SNR at the minimum response level obtained from (9) is 7~9 dB. A bandwidth of 265 Hz is chosen for the bandpass filter, and with the available commercial component’s values for the capacitors , the center frequency of the filter is expected to be approximately .

3.2. Real-Time Signal Acquisition and Sine Fitting

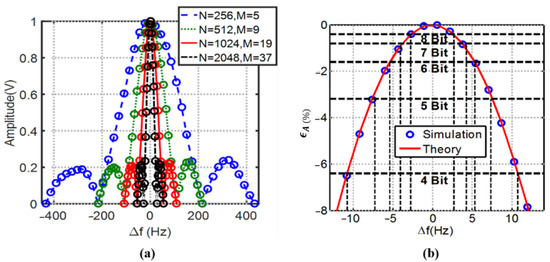

With the derived expressions in Section 2.2, the amplitude and phase estimation errors are good indicators of better noise immunity with various sample record lengths and specific accuracy requirements. To evaluate the reasonably achievable dynamic range for the sensor with the expected level of noise, jitter, and frequency accuracy, an optimized record length for a known is required. Thus, theoretical derivations are verified with numerical MATLAB simulations. For the subsequent analysis, we assume two sine signals (source and response) with an equal frequency of , amplitude of , the relative phase difference of 45°, and equal DC offset of 0.6 V, that are generated using MATLAB. The sampling rate, , and input frequency, , are constant and equal to and , respectively. The values and , are changed for multiple simulations, providing record lengths of 256, 512, and 1024 samples with 5, 9, and 19 cycles, respectively, to maintain the fixed ratio.

The ultimate metric of interest for a biosensor is to achieve a particular resolution. Therefore, the pointed non-idealities and their effect on 3PSF estimation are also examined here under the resolution (8-bit) context. The resolution of the sensor output is defined, considering a full-scale voltage at the input of the ADC, , and the full-scale target phase difference, . One performance criterion given a target of 8-bit resolution is the estimation mean error and standard deviation remaining within the and range. The estimation errors (mean and standard deviation) and resolution lines are normalized to full-scale values to demonstrate a more generic reference plot. For each non-ideality effect, the normalized estimation parameters of interest with their percent mean error and percent standard deviation are shown, and normalized resolution lines are also drawn on the plots as an indicator of the best achievable resolution with different levels of additive noise, jitter, and shift in the excitation frequency.

3.2.1. Additive Noise

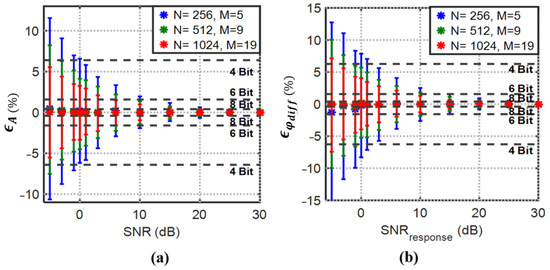

The expected minimum SNR value at the output of the implemented amplification and filtering board is 7~9. The analysis in Section 2.2.1 confirmed that an optimized record length for 3PSF improves both amplitude and differential phase estimation accuracy. To optimize the record length with the expected SNR, the estimation mean and standard deviation normalized percent errors obtained from the theoretical derivations (22)–(25) are simulated using MATLAB. Figure 7 shows the normalized mean amplitude and differential phase estimation error and the associated standard deviation for response SNR ranging from to and 1000 simulations at each point. The SNR at the source is fixed and set to 30 dB for the simulations. Apparently, with a larger record length, lower uncertainty in the estimation is achievable, even for SNR values less than .

Figure 7.

3PSF (a) percent mean amplitude and (b) percent mean differential phase estimation errors with their normalized standard deviations (error bars) vs. SNR. Normalized to full-scale resolution lines demonstrate the best achievable resolution by considering the standard deviation (error bars) with the degrading SNR and increasing record length (N).

The results in Figure 7 show that the 8-bit target resolution with SNR values even less than is achievable with .

- Oversampling

Numerical analysis with varying sampling rates and low SNRs is also carried out for 3PSF to confirm if a higher sample rate leads to better estimation performance in a noisy environment. For the numerical simulations, the oversampling ratios range from 4 to 256, and the input SNR is assumed to range from −5 to 35 dB. The simulations for the 3PSF produce an average percent error within 1% both for the amplitude ratio and the differential phase for the 256 samples in the record. The produced estimation results show that with a lower sampling-to-excitation frequency ratio, 3PSF can deliver reliable results at very low SNRs, with even four samples taken per period.

Although the greater number of samples within a record generates more accurate results with worse SNR levels, this might limit how fast the results could be produced at very low (sub-Hz) excitation frequencies. In [38], it is shown that utilizing 3PSF for a sub-Hz sensor response can produce an impedance estimation variance of 1% while the record covers only 11% of the whole period. Therefore, 3PSF is flexible for various excitation frequencies and signal-to-noise ratios. Consequently, it is concluded that at low SNRs, 3PSF with coherent sampling provides accurate results without oversampling. Therefore, the only limiting factor on the sampling rate is set by the real-time processing requirements.

3.2.2. Jitter

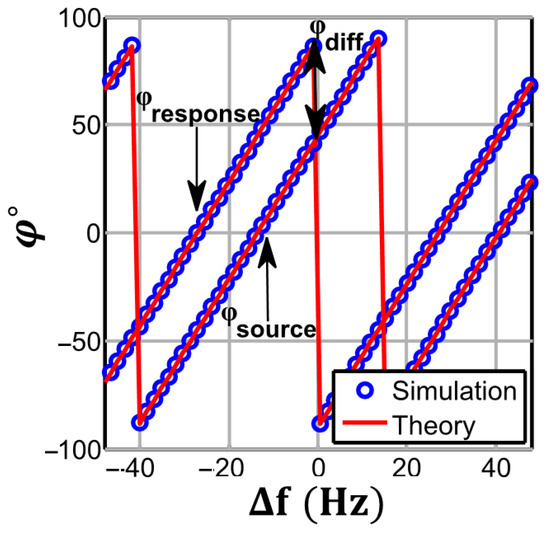

Based on derivations (31)–(34) for 3PSF in the presence of jitter and numerical simulations, the mean of the amplitude and differential phase errors with their normalized standard deviations for 1000 simulations at each point is plotted in Figure 8. The jitter standard deviation () varies from 0 to 2 for all the simulations.

Figure 8.

3PSF (a) percent mean amplitude and (b) percent mean differential phase estimation errors with their normalized standard deviations (error bars) vs. jitter standard deviation (). 3PFS can maintain 8-bit resolution with even unrealistic jitter standard deviations close to by record length control at 55 kS/s sampling rate.

Although it is seen in (35) that the amplitude mean error will never reach zero for 3PSF [35], with a record length of 1024, the 8-bit detection resolution for both amplitude and phase is achievable even at non-realistically high jitter standard deviation of around π radians.

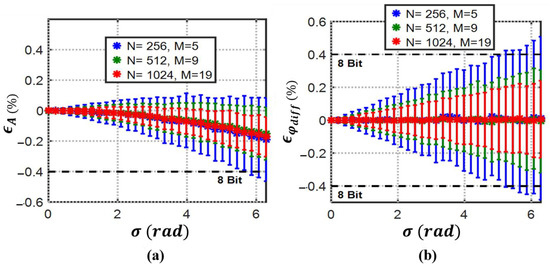

3.2.3. Shift in Excitation Frequency

Figure 9a shows the normalized amplitude estimation versus the deviation in the source frequency at various numbers of acquired cycles (and ) both for the theoretical derivation (39) and numerical simulation, with and . For a higher numbers of samples, with approximately equal input frequencies and a constant sampling rate, the fitting accuracy becomes much more sensitive to uncertainty in the ratio of . Figure 9b shows the zoomed-in plot of the amplitude error with non-coherency for . For 8-bit detection resolution, a frequency deviation of approximately can be tolerated, while if the resolution is relaxed to 4-bit, the safe frequency deviation is raised to . However, with the typical accuracy level of on-chip sine wave generators utilizing phase-locked loops (PLL) or direct digital synthesis (DDS) for discrete implementation, at range, this amount of non-coherency is not a concern for amplitude estimation.

Figure 9.

3PSF (a) amplitude estimation for a various number of samples within a record (b) zoomed-in Mean amplitude percent error for N = 1024, M = 19, and normalized percent detection resolutions vs. source frequency deviation. The plots also validate that the theoretical derivations for the non-coherency effect follow the numerical simulations accordingly.

However, at the or range, the accuracy of the generated sine wave is more of a limiting factor while picking the record length.

The theoretical (41) and numerically simulated initial phase estimation of the source and response with non-coherency are shown in Figure 10. A deviation in the source frequency will result in a linear increase in the initial phase, but the slope of this change, as derived in (41), is equal for both source and response signals, as they share the same frequency from a mutual source. Therefore, the resultant differential phase estimation for the alternate sampling scheme will not be affected by frequency deviation for any record length.

Figure 10.

3PSF initial phase estimation vs. source frequency deviation for . The plots obtained for N = 1024, M = 19. When the frequency of the source and response signals is generated from a mutual source, the linear phase estimation error for both has the same slope.

It should be clarified that, as seen in Figure 9a, the estimated amplitude will reach zero when the shift in the frequency leads to an integer number of acquired cycles difference (i.e., or when , see (39)), causing a discontinuity in the initial phase estimation at the same points.

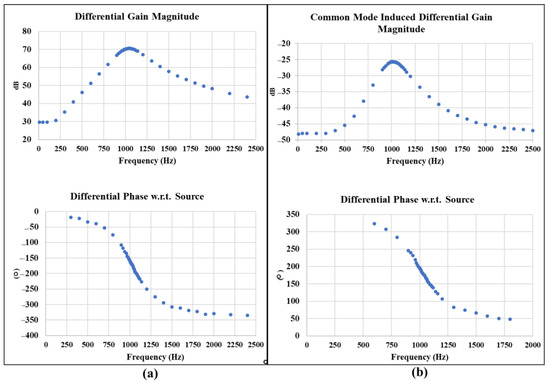

3.3. Board Characterization

The fabricated amplification and filtering board is characterized by measuring the total differential gain and common-mode-induced differential gain to verify the expected board total CMRR. For the differential gain measurement, the Audio Precision 2272 instrument is used to provide a very small differential sinusoidal input signal with a amplitude. The magnitude of the differential voltage at the output of the filtering board is measured using a digital multimeter. The differential phase of the board output with reference to the source signal is measured by an oscilloscope. The gain magnitude and differential phase are measured and recorded for multiple frequency points at a range from to Common-mode-induced differential gain is characterized with the same method, except for a voltage applied to the inputs of the board.

The measurement characterization graphs in Figure 11a show that the interface board can achieve a center frequency at , a maximum differential gain of corresponding to , and a bandwidth of . The maximum common mode induced differential gain shown in the measurement graph of Figure 11b is −, which yields a total CMRR of .

Figure 11.

The amplification and filtering board characterization for differential gain magnitude and differential phase verifies a center frequency of 1.02 kHz, bandwidth of 265 Hz, and a differential gain magnitude of

corresponding to ; (a). Maximum common mode induced differential gain magnitude is verified at −, which yields a total CMRR of (b).

3.4. Performance Verification

The amplification and filtering board is connected to the Texas Instruments Inc. MSP-EXP432P401R launchpad shown in Figure 5a for real-time data acquisition and sine fitting. The utilized key features of the single microcontroller are master clock rate, 14-bit, differential (two channel) ADC. Considering the acquisition of 1024 samples for each sine fitting operation satisfies 8-bit detection resolution requirements with 7~9 dB expected minimum SNR. The sampling rate is adjusted at to accommodate the needed real-time processing time. For the real-time fitting operation, each sample is multiplied by the corresponding and from a lookup table and results consecutively added to produce the and for each sine fitting.

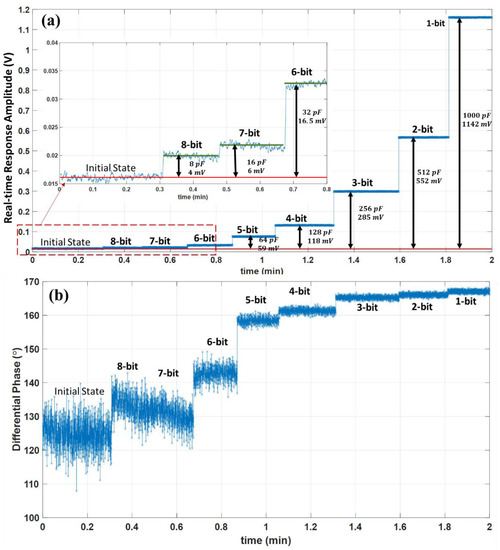

Real-Time Operation and Sensitivity

The readout sensitivity is tested using the same block diagram of Figure 5b. The test’s target is to detect a total 1% fractional capacitance change on one of the bridge impedances with an 8-bit resolution. A symmetrical bridge is configured by replacing and with the two fixed equal series RC impedances of and . After balancing the differential bridge using digitally tunable and networks, the 8-bit sensitivity is tested by additively changing the capacitance of the with and values. The test mimics an 8-bit detection resolution for a total 1% () fractional change of the capacitance in the symmetrical differential bridge. The real-time response amplitude and differential phase with reference to the source signal are demonstrated in Figure 12.

Figure 12.

Sensitivity to 1% capacitance change with 8-bit resolution and real-time processing verification for the implementation of the readout board. The obtained amplitude from the real-time 3PSF for and capacitance change at a symmetrical impedance bridge with a fixed capacitance of (a). the obtained real-time differential phase and the corresponding amplitude can be used to compute actual capacitance change for a known bridge impedance model (b).

The results show a distinct amplitude change at each consecutive capacitance change step compared to the initial balanced state amplitude. The change of amplitude values compared to the initial state at each binary weighted capacitance change is and correspondingly from the 8-bit to a 1-bit resolution. The 8-bit, 7-bit, and 6-bit amplitude levels are shown in an inset zoomed-in plot of Figure 12a after a 10-point moving average. The real-time differential phase is shown in Figure 12b, together with the corresponding amplitude, can be used to algebraically compute the exact values of the capacitance change with the known bridge impedance model [20]. The obtained results in Figure 12 reveal that the readout is sensitive to a capacitance change with an 8-bit resolution. Moreover, the results confirm that the developed interface can produce the processed response successfully in real time. The developed readout board could be interfaced with various custom-designed differential impedance sensing units with known impedance models, and the given design procedure could be employed for various precision-demanding applications.

4. Discussion

At the lower limits of detection for impedance biosensors, differential sensing and single frequency measurement with sufficient amplification and filtering are promising methods for real-time and field deployable implementation. However, when the response is still small and comparable to the noise level even after amplification, the resolution of the biosensor is significantly affected by the noise level. Moreover, the clock jitter will induce additional noise and degrade the SNR. Real-time digitization and processing with 3PSF, in expected low SNRs (even SNR < 0 dB), can lead to a higher resolution and better noise-immune operation. The algorithm can be implemented within a single MCU to process the digitized data in real time with an optimized number of samples per fitting to achieve a specific target resolution. With the assumption of a known operation frequency for the implementation of 3PSF, it is proven that a non-ideal shift in the source frequency and sampling clock jitter will affect the estimated response amplitude at any detection resolution. However, with typical accuracy levels of sine generation and the fact that both sampling clock and source signals are driven by a single sinusoidal source in most cases, jitter and source frequency shift will have a minor effect on the detection resolution both in terms of amplitude and differential phase at the lower sampling rates (i.e., tens to hundreds of KS/s). The real-time processing of the data obtained from the biosensor will eliminate the need for data storage and memory requirements and lead to lower costs for the overall system. A less complicated data processing algorithm with lower memory requirements, such as 3PSF, facilitates using the same microcontroller for data processing and other calibration or balancing of the differential system, e.g., the bridge-based system [20]. More straightforward data processing and less complicated readout implementation that are compatible to interface with ultra-sensitive transducers are crucial for the commercialization of cheaper biosensors.

5. Conclusions

A readout interface board suitable for high-precision impedance measurement, particularly for biosensing applications, is designed and implemented. The provided design details are first-hand knowledge for researchers in the field of impedance sensors and biosensors requiring precise measurement with specific resolution and accuracy. Moreover, the procedure provided here for developing a real-time data-acquisition unit is a guideline for making custom-designed, low-cost, and real-time digitization and processing units for numerous sensitive transducers that are currently being characterized with lab instrumentation. Therefore, utilizing the information provided in this paper for less complicated and yet accurate real-time readout facilitates the deployment of transducers for various in situ applications.

Author Contributions

Conceptualization, S.N., N.M.N. and D.J.C.; methodology, S.N., N.M.N. and D.J.C.; software, S.N., K.M. and N.M.N.; validation, S.N.; formal analysis, S.N.; investigation, S.N.; resources, S.N., N.M.N. and D.J.C.; data curation, S.N.; writing—original draft preparation, S.N. and N.M.N.; writing—review and editing, S.N., N.M.N., K.M. and D.J.C.; visualization, S.N., K.M. and N.M.N.; supervision, N.M.N. and D.J.C.; project administration, S.N., N.M.N. and D.J.C.; funding acquisition, N.M.N. and D.J.C. All authors have read and agreed to the published version of the manuscript.

Funding

This research was funded by U.S. Department of Agriculture under Grant 2015-67021-23128 and the University of Alabama.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Not applicable.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Daniels, J.S.; Pourmand, N. Label-Free Impedance Biosensors: Opportunities and Challenges. Electroanalysis 2007, 19, 1239–1257. [Google Scholar] [CrossRef] [PubMed]

- Loyprasert, S.; Thavarungkul, P.; Asawatreratanakul, P.; Wongkittisuksa, B.; Limsakul, C.; Kanatharana, P. Label-Free Capacitive Immunosensor for Microcystin-LR Using Self-Assembled Thiourea Monolayer Incorporated with Ag Nanoparticles on Gold Electrode. Biosens. Bioelectron. 2008, 24, 78–86. [Google Scholar] [CrossRef] [PubMed]

- Katz, E.; Willner, I. Probing Biomolecular Interactions at Conductive and Semiconductive Surfaces by Impedance Spectroscopy: Routes to Impedimetric Immunosensors, DNA-Sensors, and Enzyme Biosensors. Electroanalysis 2003, 15, 913. [Google Scholar] [CrossRef]

- Abdelrasoul, G.N.; Anwar, A.; MacKay, S.; Tamura, M.; Shah, M.A.; Khasa, D.P.; Montgomery, R.R.; Ko, A.I.; Chen, J. DNA Aptamer-Based Non-Faradaic Impedance Biosensor for Detecting E. Coli. Anal. Chim. Acta 2020, 1107, 135–144. [Google Scholar] [CrossRef]

- Alsabbagh, K.; Hornung, T.; Voigt, A.; Sadir, S.; Rajabi, T.; Länge, K. Microfluidic Impedance Biosensor Chips Using Sensing Layers Based on DNA-Based Self-Assembled Monolayers for Label-Free Detection of Proteins. Biosensors 2021, 11, 80. [Google Scholar] [CrossRef] [PubMed]

- Bar-On, L.; Garlando, U.; Sophocleous, M.; Jog, A.; Motto Ros, P.; Sade, N.; Avni, A.; Shacham-Diamand, Y.; Demarchi, D. Electrical Modelling of In-Vivo Impedance Spectroscopy of Nicotiana Tabacum Plants. Front. Electron. 2021, 2, 753145. [Google Scholar] [CrossRef]

- Heinze, J.; Allen, J.; Bard, F.; Larry, F. Faulkner: Electrochemical Methods—Fundamentals and Applications; Wiley: New York, NY, USA, 1981; Volume 85, pp. 1085–1086. [Google Scholar] [CrossRef]

- Baghbani, R.; Moradi, M.H.; Shadmehr, M.B.; Momayez Sanat, Z. A New Bio-Impedance Forceps Sensor for Measuring Electrical Conductivity of the Biological Tissues. IEEE Sens. J. 2019, 19, 11721–11731. [Google Scholar] [CrossRef]

- Kim, S.; Song, H.; Ahn, H.; Kim, T.; Jung, J.; Cho, S.K.; Shin, D.-M.; Choi, J.; Hwang, Y.-H.; Kim, K. A Review of Advanced Impedance Biosensors with Microfluidic Chips for Single-Cell Analysis. Biosensors 2021, 11, 412. [Google Scholar] [CrossRef]

- Magar, H.S.; Hassan, R.Y.A.; Mulchandani, A. Electrochemical Impedance Spectroscopy (EIS): Principles, Construction, and Biosensing Applications. Sensors 2021, 21, 6578. [Google Scholar] [CrossRef]

- Wang, S.; Zhang, J.; Gharbi, O.; Vivier, V.; Gao, M.; Orazem, M.E. Electrochemical Impedance Spectroscopy. Nat. Rev. Methods Prim. 2021, 1, 41. [Google Scholar] [CrossRef]

- Berggren, C.; Bjarnason, B.; Johansson, G. Capacitive Biosensors. Electroanalysis 2001, 13, 173–180. [Google Scholar] [CrossRef]

- Manickam, A.; Chevalier, A.; McDermott, M.; Ellington, A.D.; Hassibi, A. A CMOS Electrochemical Impedance Spectroscopy (EIS) Biosensor Array. IEEE Trans. Biomed. Circuits Syst. 2010, 4, 379–390. [Google Scholar] [CrossRef] [PubMed]

- Loyprasert, S.; Hedström, M.; Thavarungkul, P.; Kanatharana, P.; Mattiasson, B. Sub-Attomolar Detection of Cholera Toxin Using a Label-Free Capacitive Immunosensor. Biosens. Bioelectron. 2010, 25, 1977–1983. [Google Scholar] [CrossRef] [PubMed]

- Luka, G.; Samiei, E.; Dehghani, S.; Johnson, T.; Najjaran, H.; Hoorfar, M. Label-Free Capacitive Biosensor for Detection of Cryptosporidium. Sensors 2019, 19, 258. [Google Scholar] [CrossRef]

- Sharma, R.; Deacon, S.E.; Nowak, D.; George, S.E.; Szymonik, M.P.; Tang, A.A.S.; Tomlinson, D.C.; Davies, A.G.; McPherson, M.J.; Wälti, C. Label-Free Electrochemical Impedance Biosensor to Detect Human Interleukin-8 in Serum with Sub-Pg/Ml Sensitivity. Biosens. Bioelectron. 2016, 80, 607–613. [Google Scholar] [CrossRef]

- Soraya, G.V.; Abeyrathne, C.D.; Buffet, C.; Huynh, D.H.; Uddin, S.M.; Chan, J.; Skafidas, E.; Kwan, P.; Rogerson, S.J. Ultrasensitive and Label-Free Biosensor for the Detection of Plasmodium Falciparum Histidine-Rich Protein II in Saliva. Sci. Rep. 2019, 9, 17495. [Google Scholar] [CrossRef]

- Tanak, A.S.; Jagannath, B.; Tamrakar, Y.; Muthukumar, S.; Prasad, S. Non-Faradaic Electrochemical Impedimetric Profiling of Procalcitonin and C-Reactive Protein as a Dual Marker Biosensor for Early Sepsis Detection. Anal. Chim. Acta X 2019, 3, 100029. [Google Scholar] [CrossRef]

- Uygun, Z.O.; Atay, S. Label-Free Highly Sensitive Detection of DNA Approximate Length and Concentration by Impedimetric CRISPR-DCas9 Based Biosensor Technology. Bioelectrochemistry 2021, 140, 107812. [Google Scholar] [CrossRef]

- Neshani, S.; Nyamekye, C.K.A.; Melvin, S.; Smith, E.A.; Chen, D.J.; Neihart, N.M. AC and DC Differential Bridge Structure Suitable for Electrochemical Interfacial Capacitance Biosensing Applications. Biosensors 2020, 10, 28. [Google Scholar] [CrossRef]

- Zumbahlen, H. Basic Linear Design; Analog Devices: Norwood, MA, USA, 2007; ISBN 978-0-916550-28-8. [Google Scholar]

- Lokere, K.; Hutchison, T.; Zimmer, G. Precision Matched Resistors Automatically Improve Differential Amplifier CMRR—Here’s How. Linear Technol. Des. Note 2013, 20, 1023. [Google Scholar]

- Pallas-Areny, R.; Webster, J.G. Common Mode Rejection Ratio for Cascaded Differential Amplifier Stages. IEEE Trans. Instrum. Meas. 1991, 40, 677–681. [Google Scholar] [CrossRef]

- Gesteland, R.C.; Howland, B.; Lettvin, J.Y.; Pitts, W.H. Comments on Microelectrodes. Proc. IRE 1959, 47, 1856–1862. [Google Scholar] [CrossRef]

- Karki, J. Fully-Differential Amplifiers. Available online: https://www.ti.com/lit/an/sloa054e/sloa054e.pdf?ts=1672562718439&ref_url=https%253A%252F%252Fwww.google.com%252F (accessed on 15 October 2022).

- Texas Instruments. Noise Analysis in Operational Amplifier Circuits. In Application Report; Texas Instruments: Dallas, TX, USA, 2007. [Google Scholar]

- Sobering, T.J. Equivalent Noise Bandwidth. 1991, p. 3. Available online: https://www.k-state.edu/edl/docs/pubs/technical-resources/Technote1.pdf (accessed on 15 October 2022).

- Pintelon, R.; Schoukens, J. An Improved Sine-Wave Fitting Procedure for Characterizing Data Acquisition Channels. IEEE Trans. Instrum. Meas. 1996, 45, 588–593. [Google Scholar] [CrossRef]

- Ramos, P.M.; Cruz Serra, A. A New Sine-Fitting Algorithm for Accurate Amplitude and Phase Measurements in Two Channel Acquisition Systems. Measurement 2008, 41, 135–143. [Google Scholar] [CrossRef]

- Masi, A.; Danisi, A.; Di Castro, M.; Losito, R. Real-Time High-Precision Reading Algorithm for the Ironless Inductive Position Sensor. IEEE Trans. Nucl. Sci. 2013, 60, 3661–3668. [Google Scholar] [CrossRef]

- IEEE Std 1057-1994; IEEE Standard for Digitizing Waveform Recorders. IEEE: New York, NY, USA, 1994. [CrossRef]

- Martino, M.; Losito, R.; Masi, A. Analytical Metrological Characterization of the Three-Parameter Sine Fit Algorithm. ISA Trans. 2012, 51, 262–270. [Google Scholar] [CrossRef]

- Andersson, T.; Handel, P. IEEE Standard 1057, Crame/Spl Acute/r-Rao Bound and the Parsimony Principle. IEEE Trans. Instrum. Meas. 2006, 55, 44–53. [Google Scholar] [CrossRef]

- Ang, A.H.-S.; Tang, W.H.; Ang, A.H.-S. Probability Concepts in Engineering: Emphasis on Applications in Civil & Environmental Engineering, 2nd ed.; Wiley: New York, NY, USA, 2007; ISBN 978-0-471-72064-5. [Google Scholar]

- Alegria, F.C.; Serra, A.C. Gaussian Jitter-Induced Bias of Sine Wave Amplitude Estimation Using Three-Parameter Sine Fitting. IEEE Trans. Instrum. Meas. 2010, 59, 2328–2333. [Google Scholar] [CrossRef]

- Aperture Jitter Calculator for ADCs. Available online: https://www.maximintegrated.com/en/design/technical-documents/app-notes/4/4466.html (accessed on 1 July 2022).

- Ramos, P.M.; Janeiro, F.M.; Tlemcani, M.; Serra, A.C. Recent Developments on Impedance Measurements With DSP-Based Ellipse-Fitting Algorithms. IEEE Trans. Instrum. Meas. 2009, 58, 1680–1689. [Google Scholar] [CrossRef]

- Piasecki, T. Fast Impedance Measurements at Very Low Frequencies Using Curve Fitting Algorithms. Meas. Sci. Technol. 2015, 26, 065002. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).