Design and Fabrication of a Low-Voltage OPAMP Based on a-IGZO Thin-Film Transistors

Abstract

1. Introduction

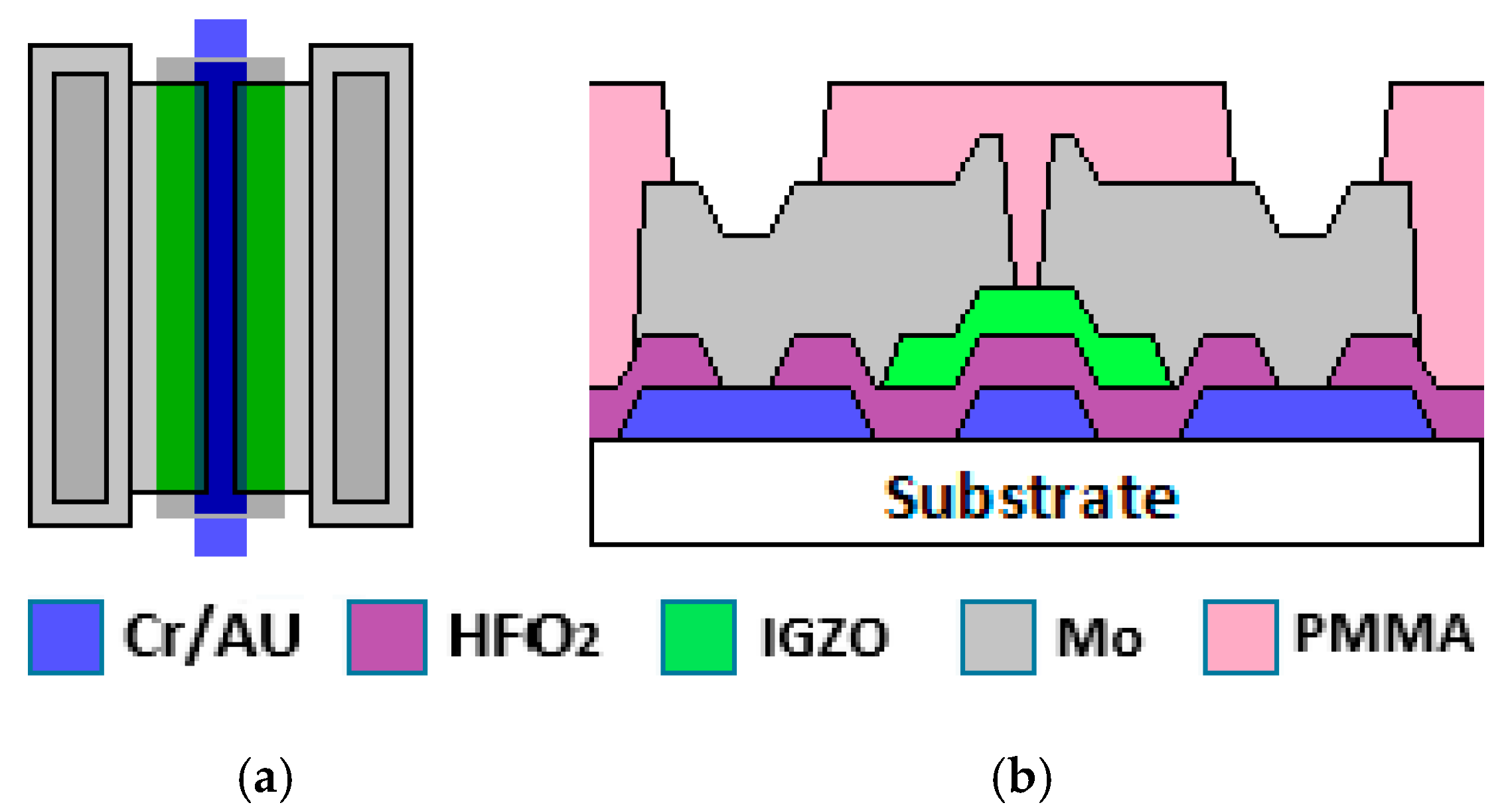

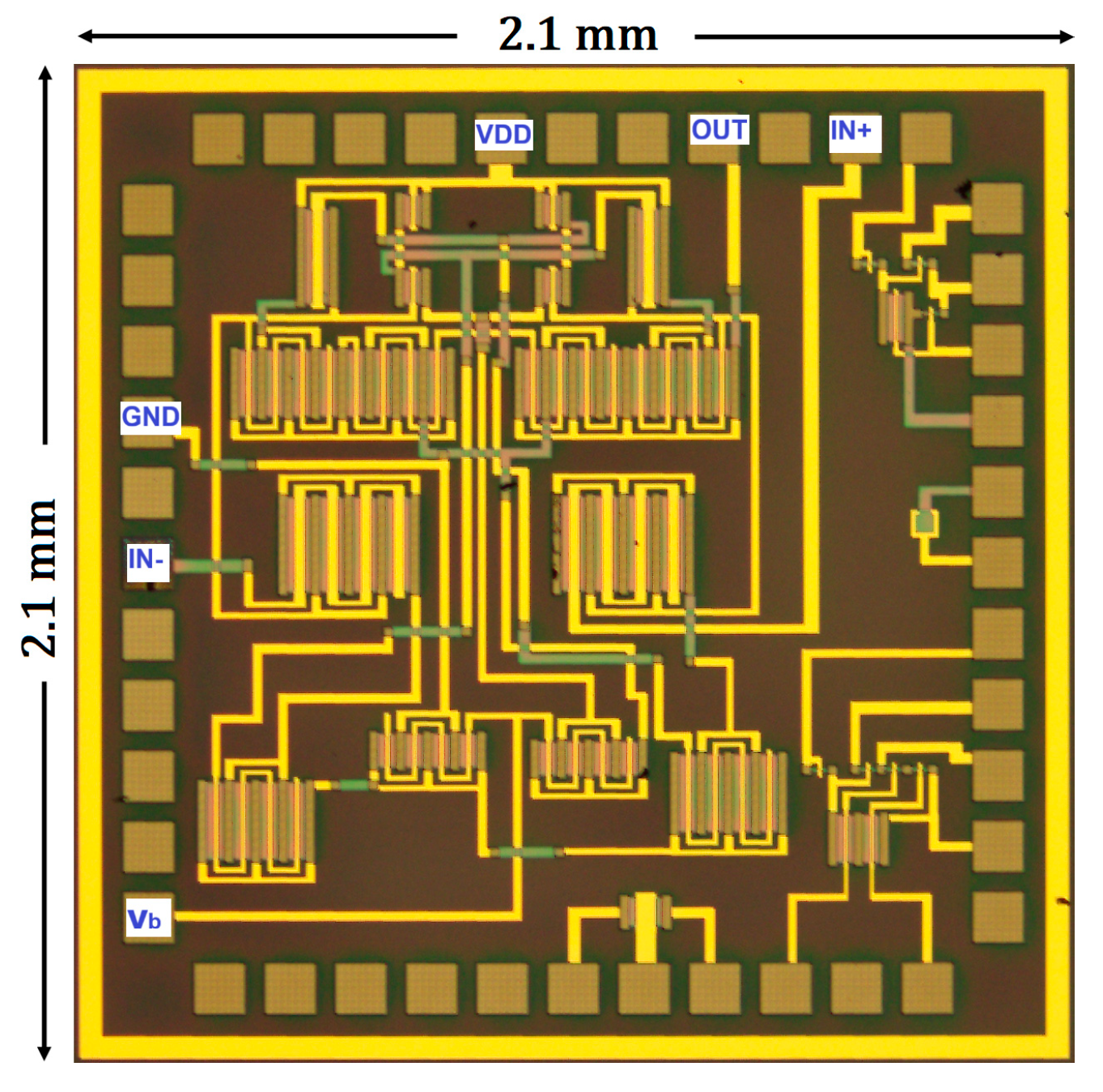

2. Fabrication Process

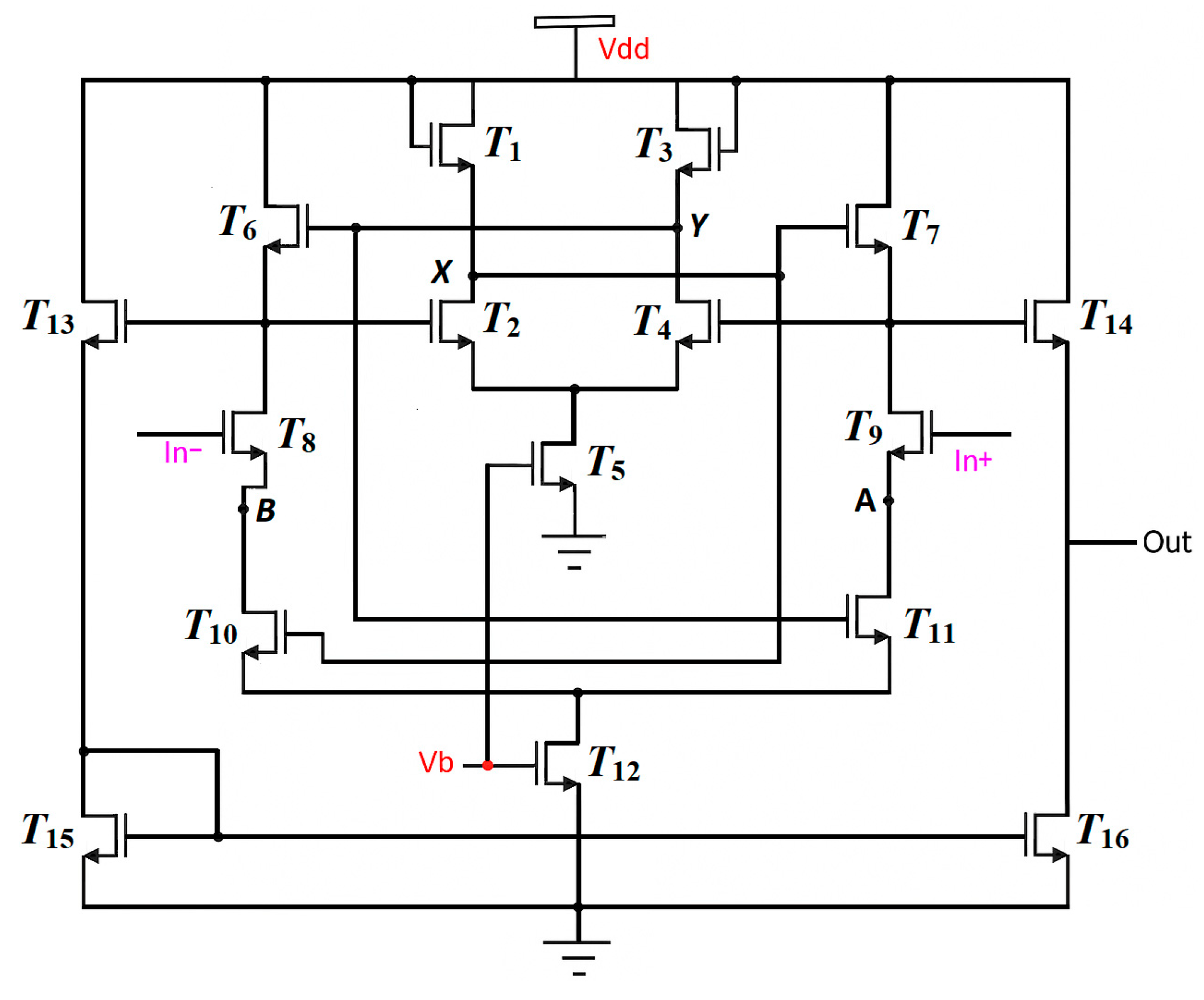

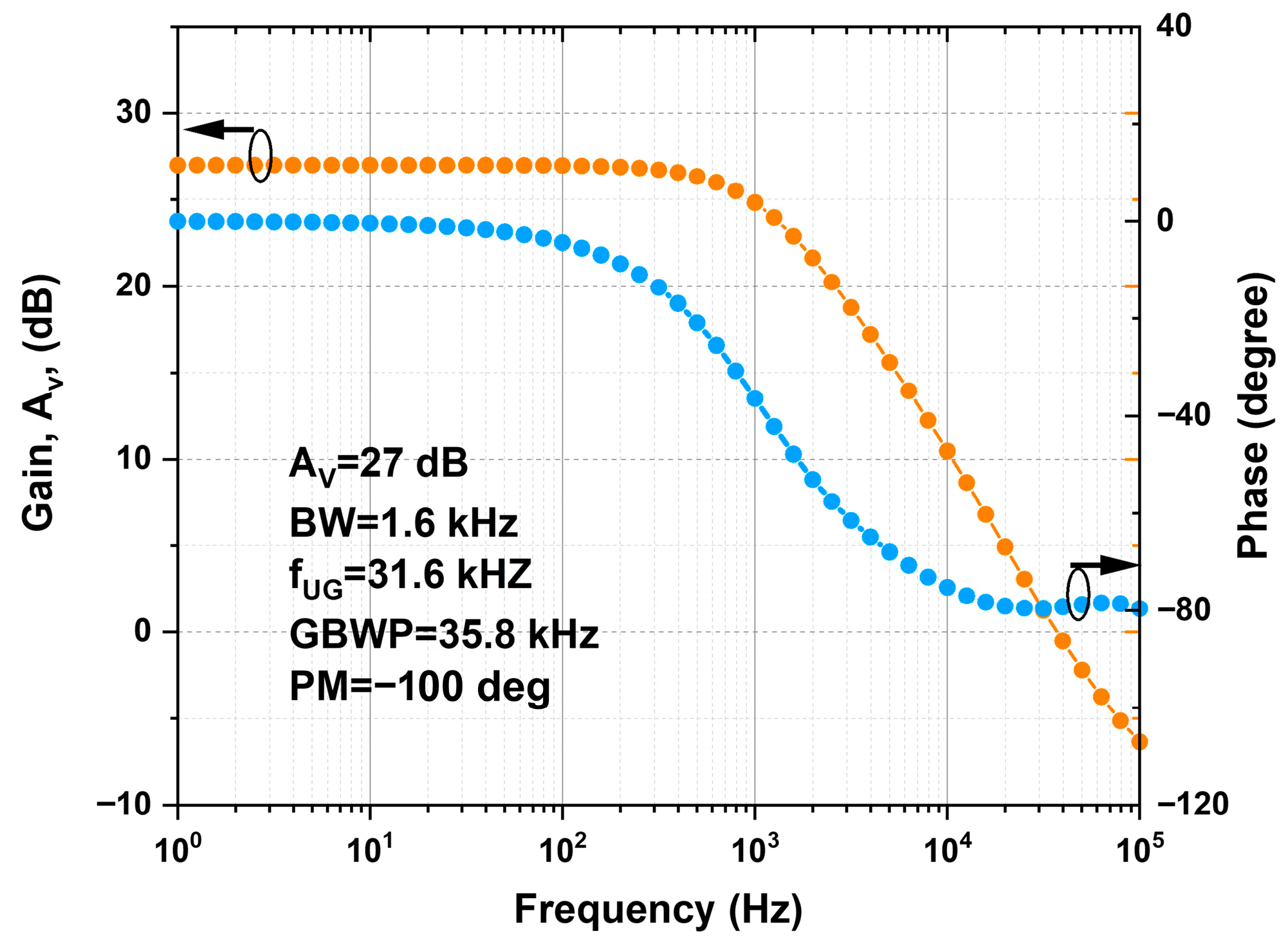

3. OPAMP Design and Simulation

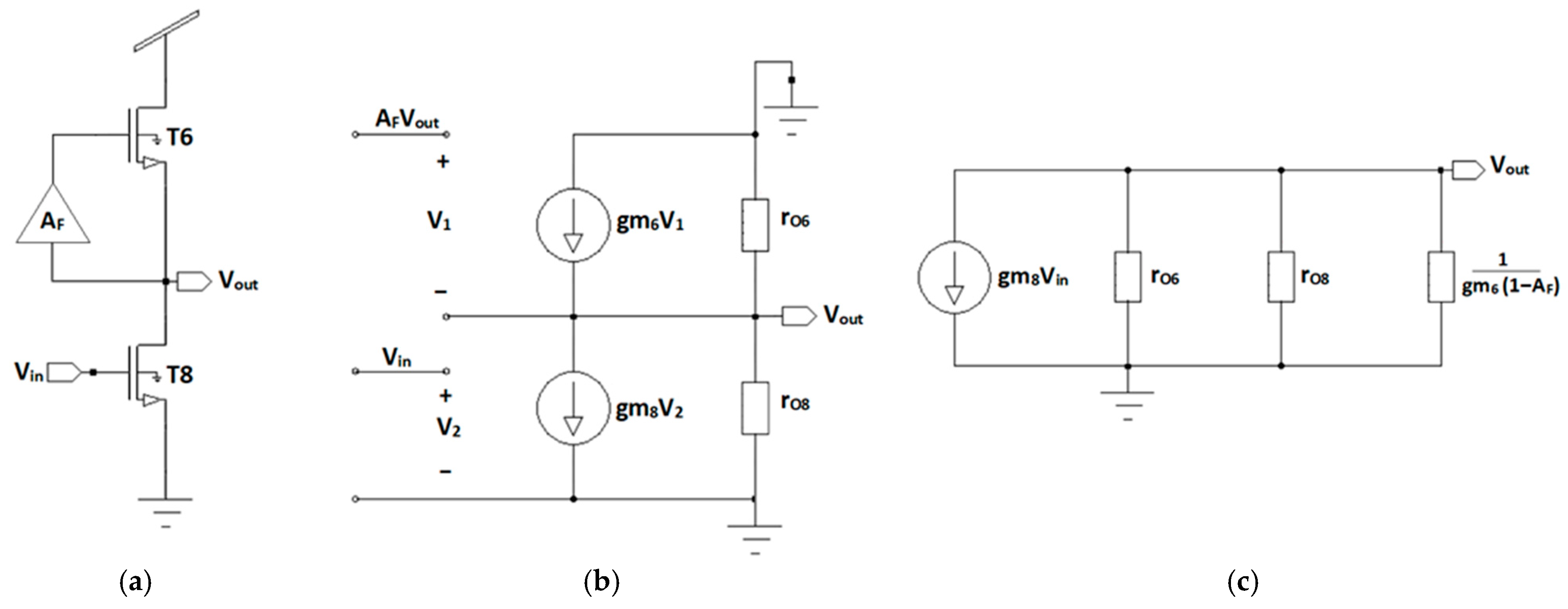

Circuit Analysis

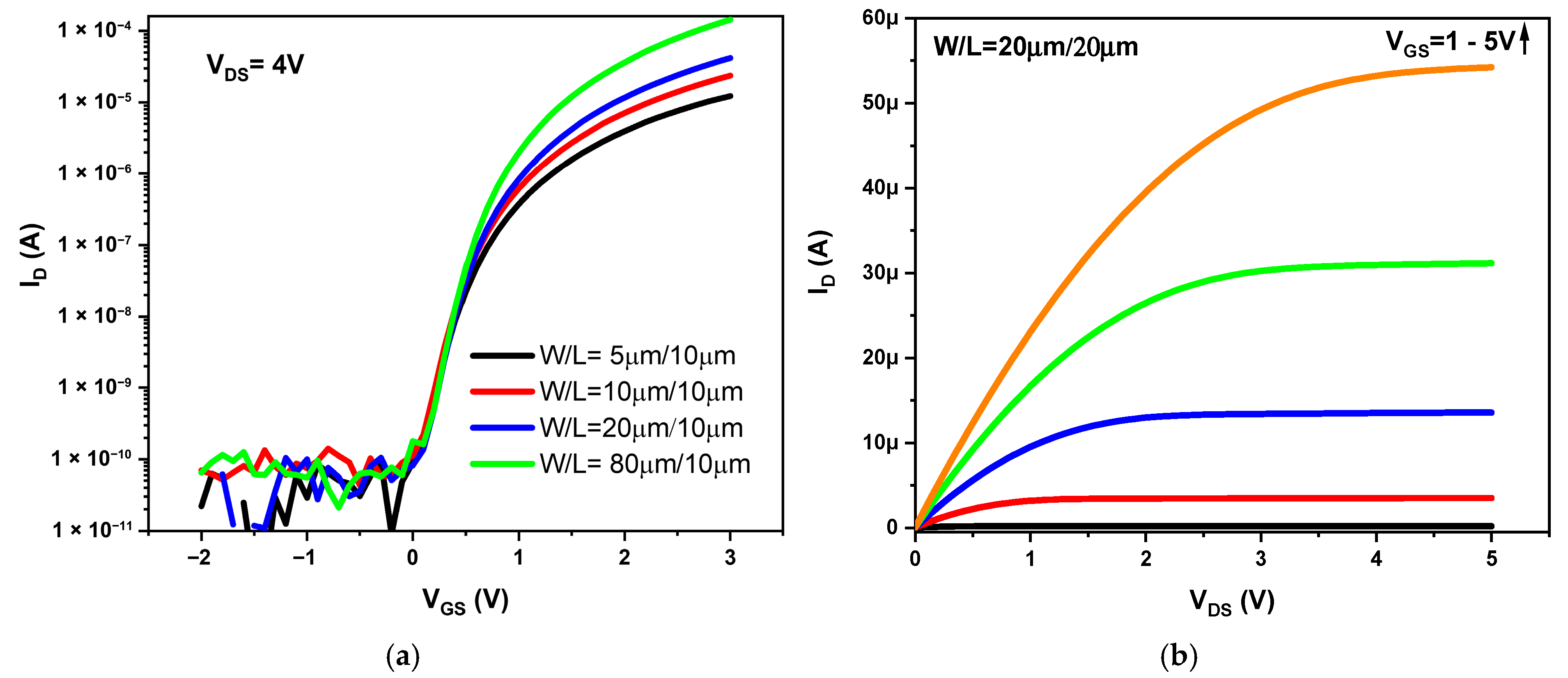

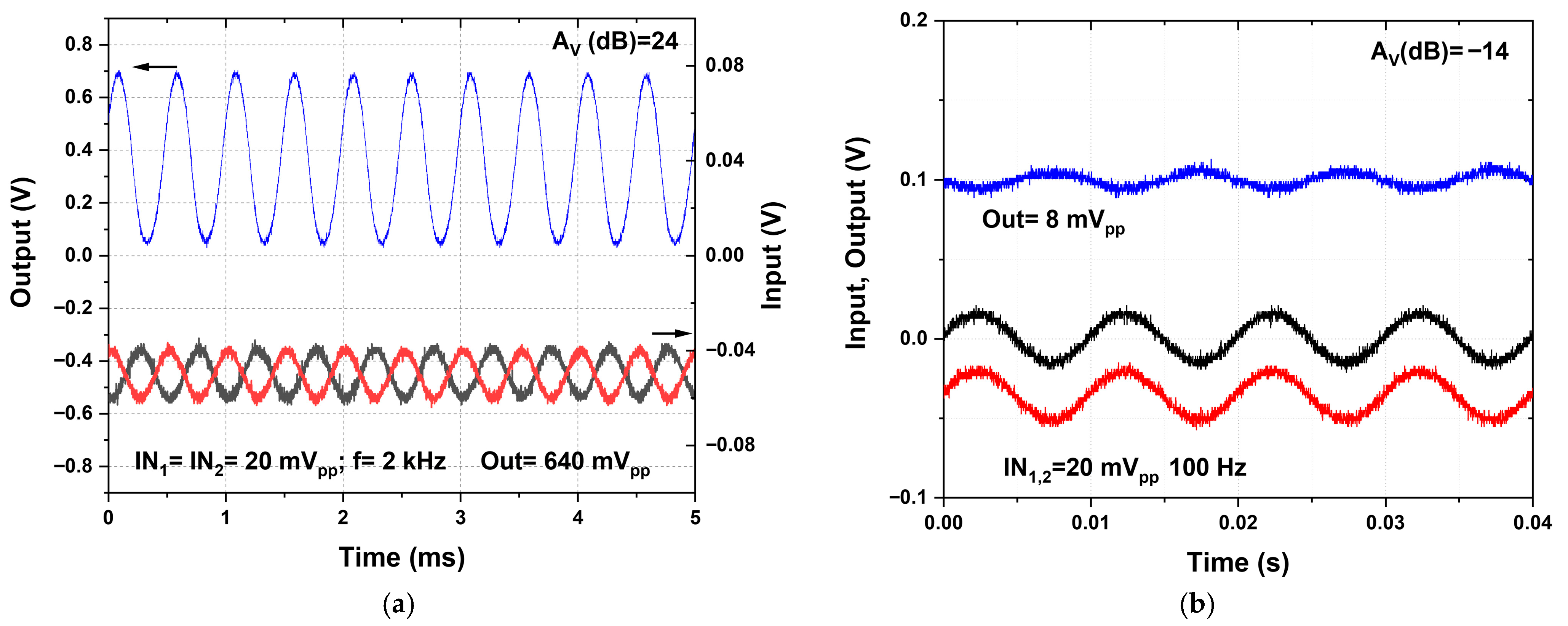

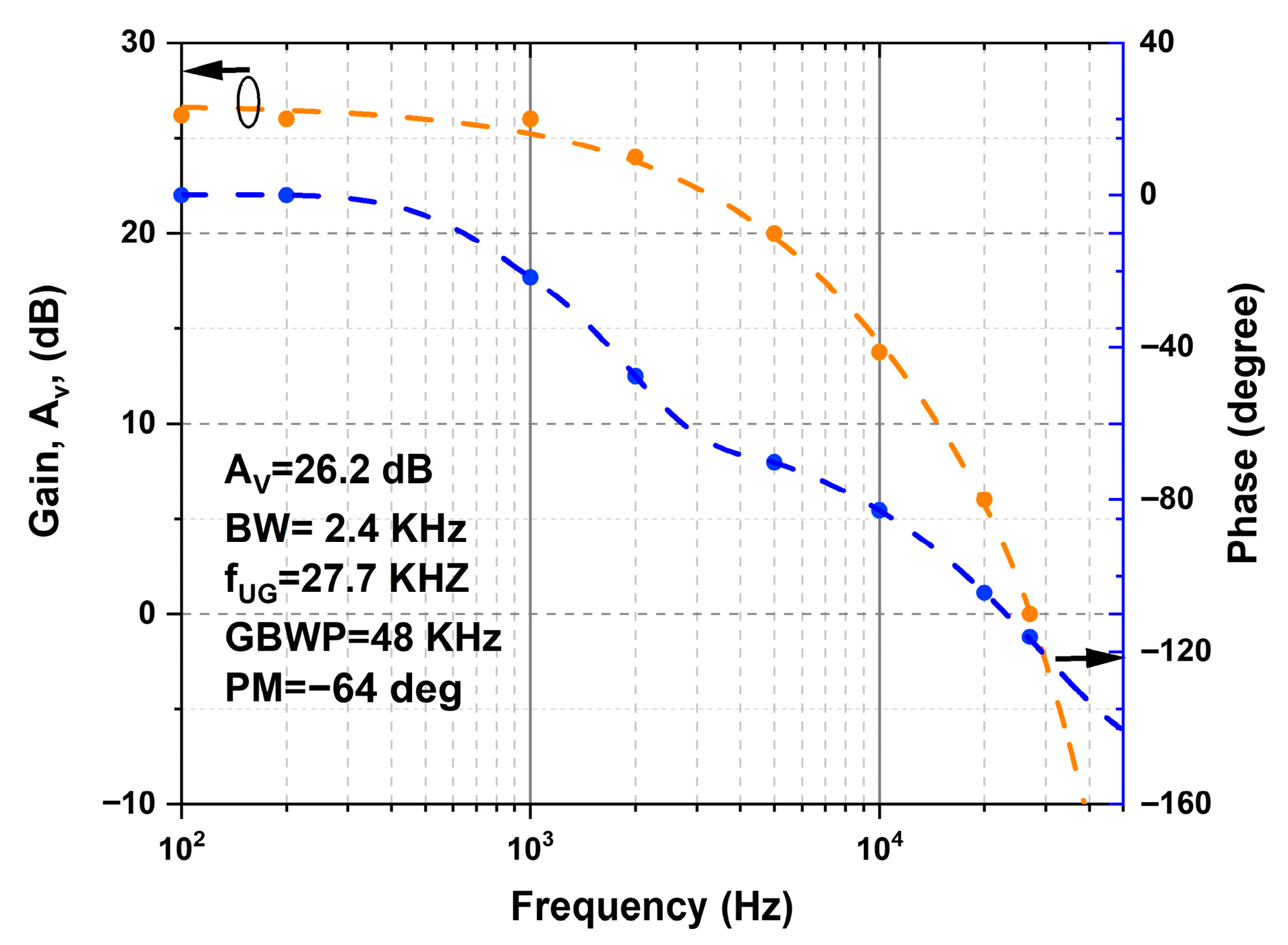

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Chen, Z.J.; Peng, J.B.; Xu, W.X.; Wu, J.D.; Zhou, L.; Wu, W.J.; Zou, J.H.; Xu, M.; Wang, L.; Liu, Y.R. A New High-Gain Operational Amplifier Using Tansconductance-Enrhancement Topology Integrated with Metal Oxide TFTs. IEEE J. Electron Devices Soc. 2018, 7, 111–117. [Google Scholar] [CrossRef]

- Deng, L.; Han, L.; Ouyang, B.; Yin, X.; Guo, X. Low-Voltage Operated High DC Gain Amplification Stage Based on Large-Area Manufacturable Amorphous Oxide Semiconductor Thin-Film Transistor. IEEE Trans. Electron Devices 2023, 70, 3112–3116. [Google Scholar] [CrossRef]

- Shabanpour, R.; Ishida, K.; Meister, T.; Munzenrieder, N.; Petti, L.; Salvatore, G.; Kheradmand-Boroujeni, B.; Carta, C.; Troster, G.; Ellinger, F. A 70°phase margin OPAMP with positive feedback in flexible a-IGZO TFT technology. Midwest Symp. Circuits Syst. 2015, 2015, 13–16. [Google Scholar]

- Meng, F.; Li, Y.; Li, J.; Liang, J.; Zhang, J. A Performance Optimized Operational Amplifier Using Transconductance Enhancement Topology Based on a-IGZO TFTs. IEEE J. Electron Devices Soc. 2024, 12, 159–164. [Google Scholar] [CrossRef]

- Cho, M.H.; Seol, H.; Yang, H.; Yun, P.S.; Bae, J.U.; Park, K.-S.; Jeong, J.K. High-Performance Amorphous Indium Gallium Zinc Oxide Thin-Film Transistors Fabricated by Atomic Layer Deposition. IEEE Electron Device Lett. 2018, 39, 688–691. [Google Scholar] [CrossRef]

- Jeong, J.K.; Chung, H.J.; Mo, Y.G.; Kim, H.D. Comprehensive Study on the Transport Mechanism of Amorphous Indium-Gallium-Zinc Oxide Transistors. J. Electrochem. Soc. 2008, 155, H873. [Google Scholar] [CrossRef]

- Sahoo, A.K.; Wu, G.M. Effects of argon flow rate on electrical properties of amorphous indium gallium zinc oxide thin-film transistors. Thin Solid Films 2015, 605, 129–135. [Google Scholar] [CrossRef]

- Tiwari, B.; Bahubalindruni, P.G.; Santos, A.; Santa, A.; Figueiredo, C.; Pereira, M.; Martins, R.; Fortunato, E.; Barquinha, P. Low-Voltage High-Speed Ring Oscillator with a-InGaZnO TFTs. IEEE J. Electron Devices Soc. 2020, 8, 584–588. [Google Scholar] [CrossRef]

- Zhang, S.; Liu, B.; Zhang, X.; Wen, C.; Sun, H.; Liu, X.; Yao, Q.; Zi, X.; Bao, Z.; Xiao, Z.; et al. Reduction of internal stress in InGaZnO (IGZO) thin film transistors by ultra-thin metal oxide layer. Mater. Sci. Semicond. Process. 2023, 173, 108093. [Google Scholar] [CrossRef]

- Lin, C.I.; Fang, Y.K.; Chang, W.C.; Chiou, M.W.; Chen, C.W. Effect of gate barrier and channel buffer layer on electric properties and transparence of the a-IGZO thin film transistor. Microelectron. Reliab. 2014, 54, 905–910. [Google Scholar] [CrossRef]

- Kim, J.; Park, J.; Yoon, G.; Khushabu, A.; Kim, J.S.; Pae, S.; Yi, J. Effect of IGZO thin films fabricated by Pulsed-DC and RF sputtering on TFT characteristics. Mater. Sci. Semicond. Process. 2020, 120, 105264. [Google Scholar] [CrossRef]

- Yu, G.; Wu, C.-F.; Lu, H.; Ren, F.-F.; Zhang, R.; Zheng, Y.-D.; Huang, X.-M. Frequency performance of ring oscillators based on a-IGZO thin-film transistors. Chin. Phys. Lett. 2015, 32, 4. [Google Scholar] [CrossRef]

- Takenaka, K.; Nunomura, S.; Hayashi, Y.; Komatsu, H.; Toko, S.; Tampo, H.; Setsuhara, Y. Stability and gap states of amorphous In-Ga-Zn-O thin film transistors: Impact of sputtering configuration and post-annealing on device performance. Thin Solid Films 2023, 790, 140203. [Google Scholar] [CrossRef]

- Zhu, Y.; He, Y.; Jiang, S.; Zhu, L.; Chen, C.; Wan, Q. Indium-gallium-zinc-oxide thin-film transistors: Materials, devices, and applications. J. Semicond. 2021, 42, 031101. [Google Scholar] [CrossRef]

- Jang, S.C.; Shim, J.; Jang, H.; Lee, Y.; Biswas, S.; Park, J.; Shin, H.; Kim, H.; Kim, S.; Kim, H.-S. Recent progress in the development of backplane thin-film transistors for information displays. J. Inf. Disp. 2025, 26, 341–356. [Google Scholar] [CrossRef]

- Chen, J.R.; Xu, W.X.; Zuo, W.C.; Mei, X.L.; Zhou, L.; Xu, M.; Wang, L.; Wu, W.J.; Liu, Y.R.; Peng, J.B. A 50 dB high-gain operational amplifier integrated with metal-oxide TFTs. Semicond. Sci. Technol. 2022, 37, 105010. [Google Scholar] [CrossRef]

- Fujii, M.; Yano, H.; Hatayama, T.; Uraoka, Y.; Fuyuki, T.; Jung, J.S.; Kwon, J.Y. Thermal Analysis of Degradation in Ga2O3–In2O3–ZnO Thin-Film Transistors. Jpn. J. Appl. Phys. 2008, 47, 6236. [Google Scholar] [CrossRef]

- Abe, K.; Ota, K.; Kuwagaki, T. Simulation Study of Self-Heating and Edge Effects on Oxide-Semiconductor TFTs: Channel-Width Dependence. In Proceedings of the International Display Workshops, Sapporo, Japan, 27–29 November 2019; pp. 461–464. [Google Scholar]

- Liu, K.; Chang, T.C.; Wu, M.S.; Hung, Y.S.; Hung, P.H.; Hsieh, T.Y.; Chou, W.C.; Chu, A.K.; Sze, S.M.; Yeh, B.L. Investigation of channel width-dependent threshold voltage variation in a-InGaZnO thin-film transistors. Appl. Phys. Lett. 2014, 104, 133503. [Google Scholar] [CrossRef]

- Razavi, B. Design of Analog CMOS Integrated Circuits, 2nd ed.; McGraw-Hill: New York, NY, USA, 2017. [Google Scholar]

- Tsividis, Y.P.; Gray, P.R. An integrated NMOS operational amplifier with internal compensation. IEEE J. Solid State Circuits 1976, 16, 748–753. [Google Scholar] [CrossRef]

- Sharma, A.; Bahubalindruni, P.G.; Bharti, M.; Barquinha, P. High gain operational amplifier and a comparator with a-IGZO TFTs. IET Circuits, Devices Syst. 2020, 14, 1214–1219. [Google Scholar] [CrossRef]

- Rahaman, A.; Chen, Y.; Hasan, M.; Jang, J. A High Performance Operational Amplifier Using Coplanar Dual Gate a-IGZO TFTs. IEEE J. Electron Devices Soc. 2019, 7, 655–661. [Google Scholar] [CrossRef]

- Min, H.J.; Jang, S.C.; Kim, K.J.; Rim, Y.S.; Kim, H.S. Metal oxide semiconductor-based negative capacitance field-effect transistors with a sub-threshold swing of below 30 mV/dec. Mater. Today Electron. 2025, 14, 100178. [Google Scholar] [CrossRef]

| W/L (µm/µm) | Vth (V) | µfet (cm2/Vs) | IDmax (µA) | ION/IOFF | SS (mV/Decade) |

|---|---|---|---|---|---|

| W = 5; L = 10 | 0.67 | 24.0 | 12.2 | 2.1 × 105 | 177 |

| W = 10; L = 10 | 0.73 | 23.4 | 23.6 | 2.5 × 105 | 167 |

| W = 20; L = 10 | 0.79 | 21.3 | 41.7 | 5.6 × 105 | 137 |

| W = 80; L = 10 | 0.89 | 19.2 | 143.5 | 1.5 × 106 | 127 |

| W/L (µm/µm) | W/L (µm/µm) | W/L (µm/µm) | |||

|---|---|---|---|---|---|

| T1, T3 | 67/5 | T8, T9 | 800/20 | T15, T16 | 560/5 |

| T2, T4 | 71/5 | T10, T11 | 120/15 | ||

| T5 | 280/5 | T12 | 560/5 | ||

| T6, T7 | 200/20 | T13–T116 | 560/5 |

| Circuit | [16] | [22] | [3] | [4] | [23] | This Work |

|---|---|---|---|---|---|---|

| Year | 2022 | 2018 | 2015 | 2023 | 2019 | 2025 |

| Technology | Metal-Oxide | Metal-Oxide | a-IGZO | a-IGZO | a-IGZO | a-IGZO |

| Topology | Positive-feedback | Positive-feedback | Positive-feedback | Positive-feedback | N-MOS diode | Positive-feedback |

| VDD | 20 | 15 | 6 | 15 | 10 | 5.5 |

| AV (dB) | 50 | 29.5 | 19 | 32.67 | 19.6 | 26 |

| BW (kHz) | 15.2 | 9.33 | 25 | 15 | 350 | 2.4 |

| GBWP (kHz) | 4806 | 279.9 | 223 | - | 3342 | 48 |

| fUG (kHz) | 500 | 180.2 | 330 | 200 | 1600 | 27.7 |

| PM | −24 | −21.5 | −70 | −35.8 | −102 | −64 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.

Share and Cite

Torres-Sánchez, A.; Hernandez-Luna, I.S.; Hernández-Cuevas, F.J.; León-Puertos, C.; Hernández-Como, N. Design and Fabrication of a Low-Voltage OPAMP Based on a-IGZO Thin-Film Transistors. Nanomaterials 2026, 16, 84. https://doi.org/10.3390/nano16020084

Torres-Sánchez A, Hernandez-Luna IS, Hernández-Cuevas FJ, León-Puertos C, Hernández-Como N. Design and Fabrication of a Low-Voltage OPAMP Based on a-IGZO Thin-Film Transistors. Nanomaterials. 2026; 16(2):84. https://doi.org/10.3390/nano16020084

Chicago/Turabian StyleTorres-Sánchez, Arturo, Isai S. Hernandez-Luna, Francisco J. Hernández-Cuevas, Cuauhtémoc León-Puertos, and Norberto Hernández-Como. 2026. "Design and Fabrication of a Low-Voltage OPAMP Based on a-IGZO Thin-Film Transistors" Nanomaterials 16, no. 2: 84. https://doi.org/10.3390/nano16020084

APA StyleTorres-Sánchez, A., Hernandez-Luna, I. S., Hernández-Cuevas, F. J., León-Puertos, C., & Hernández-Como, N. (2026). Design and Fabrication of a Low-Voltage OPAMP Based on a-IGZO Thin-Film Transistors. Nanomaterials, 16(2), 84. https://doi.org/10.3390/nano16020084