Novel 4H-SiC Double-Trench MOSFETs with Integrated Schottky Barrier and MOS-Channel Diodes for Enhanced Breakdown Voltage and Switching Characteristics

Abstract

1. Introduction

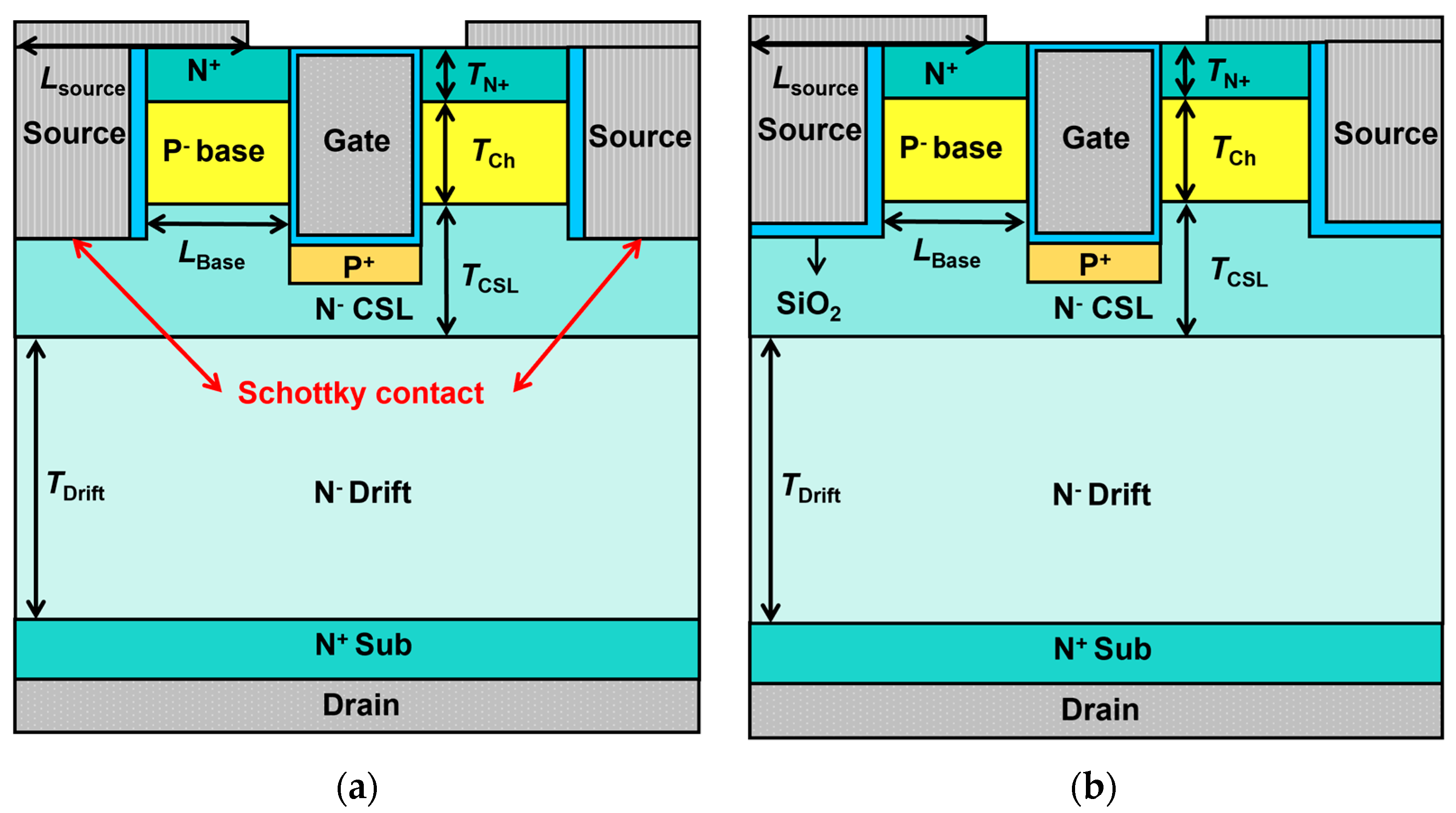

2. Device Structure Design

3. Simulation Results and Discussion

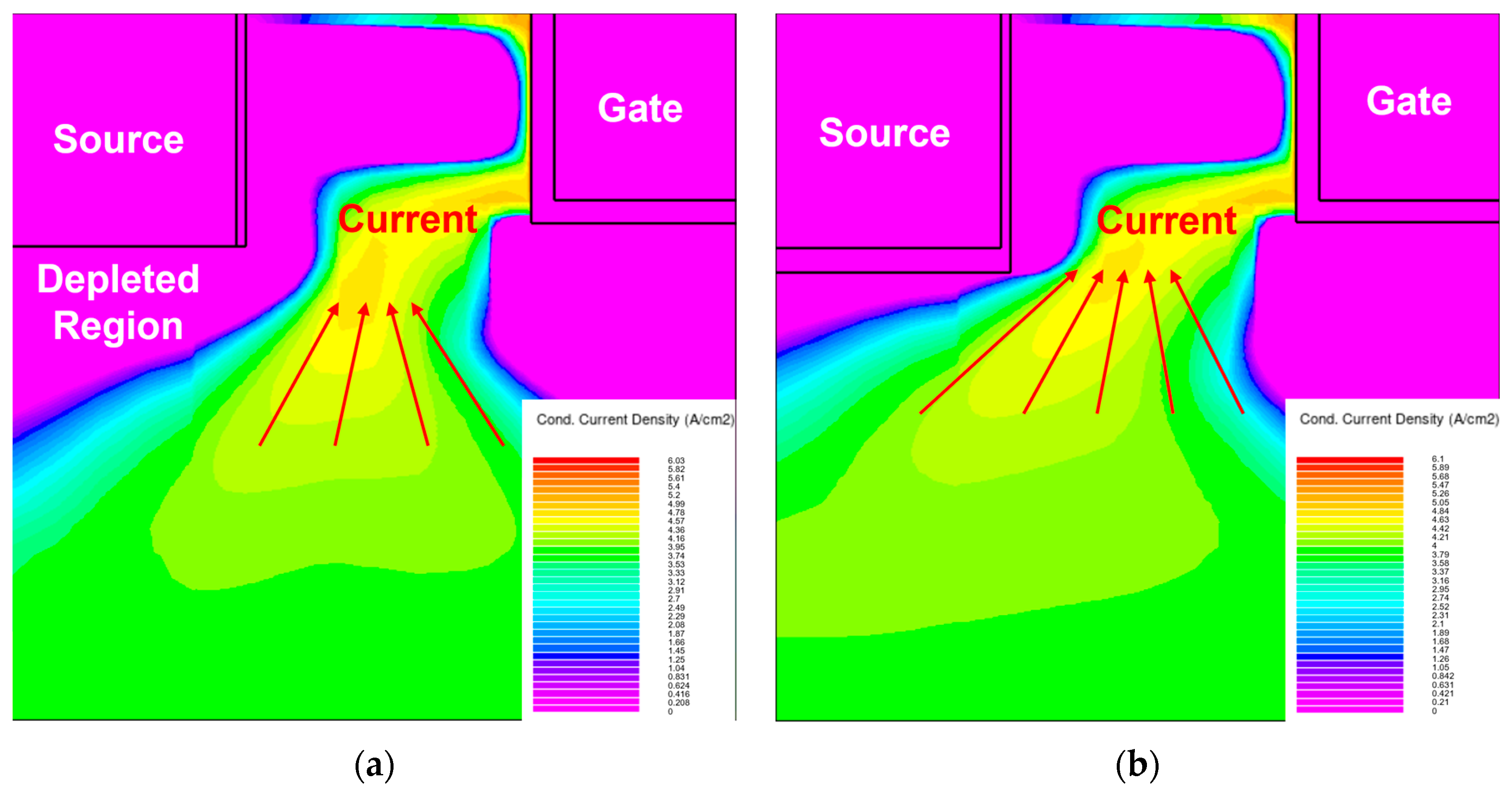

3.1. Forward Output and Reverse Conduction Characteristics

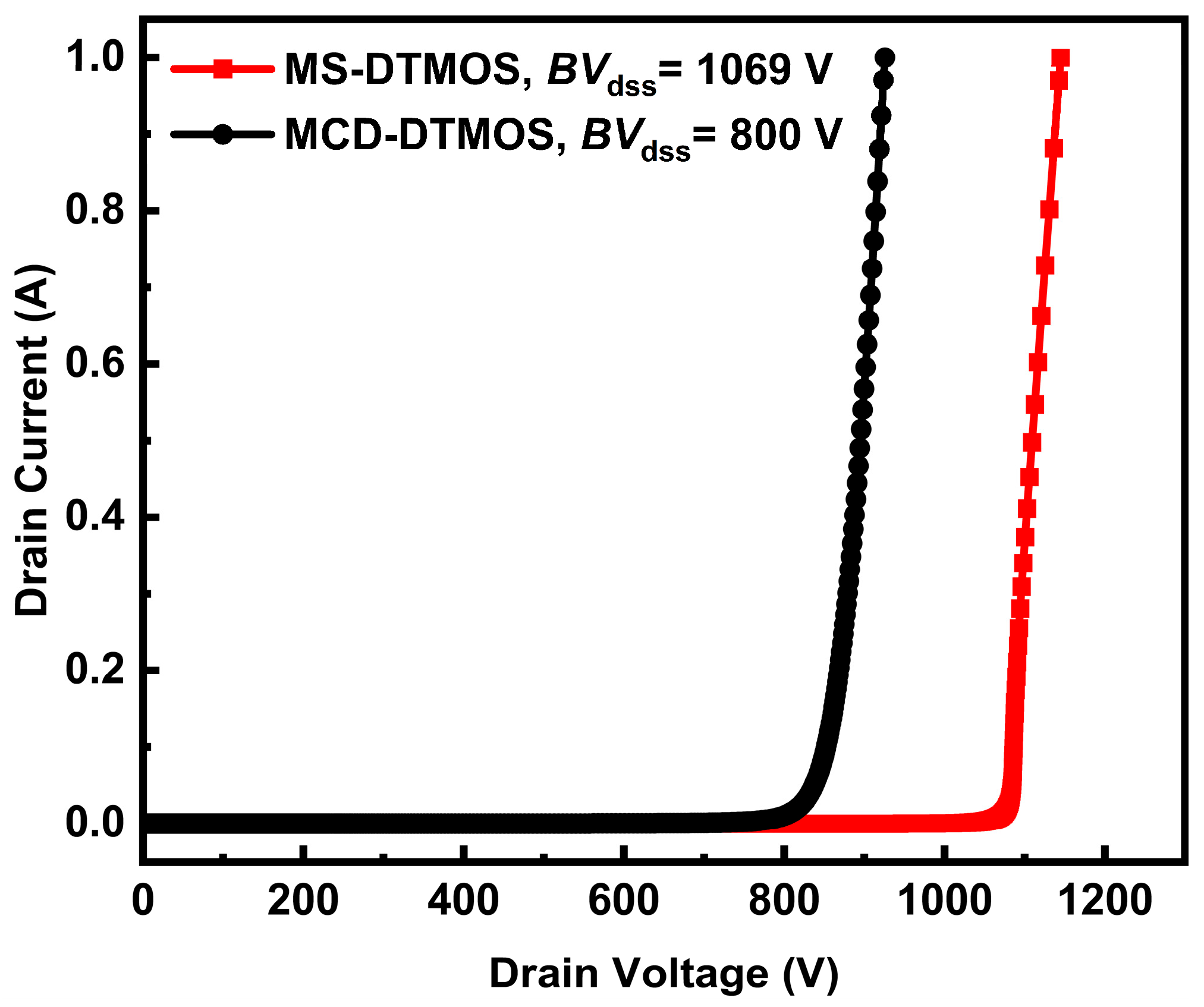

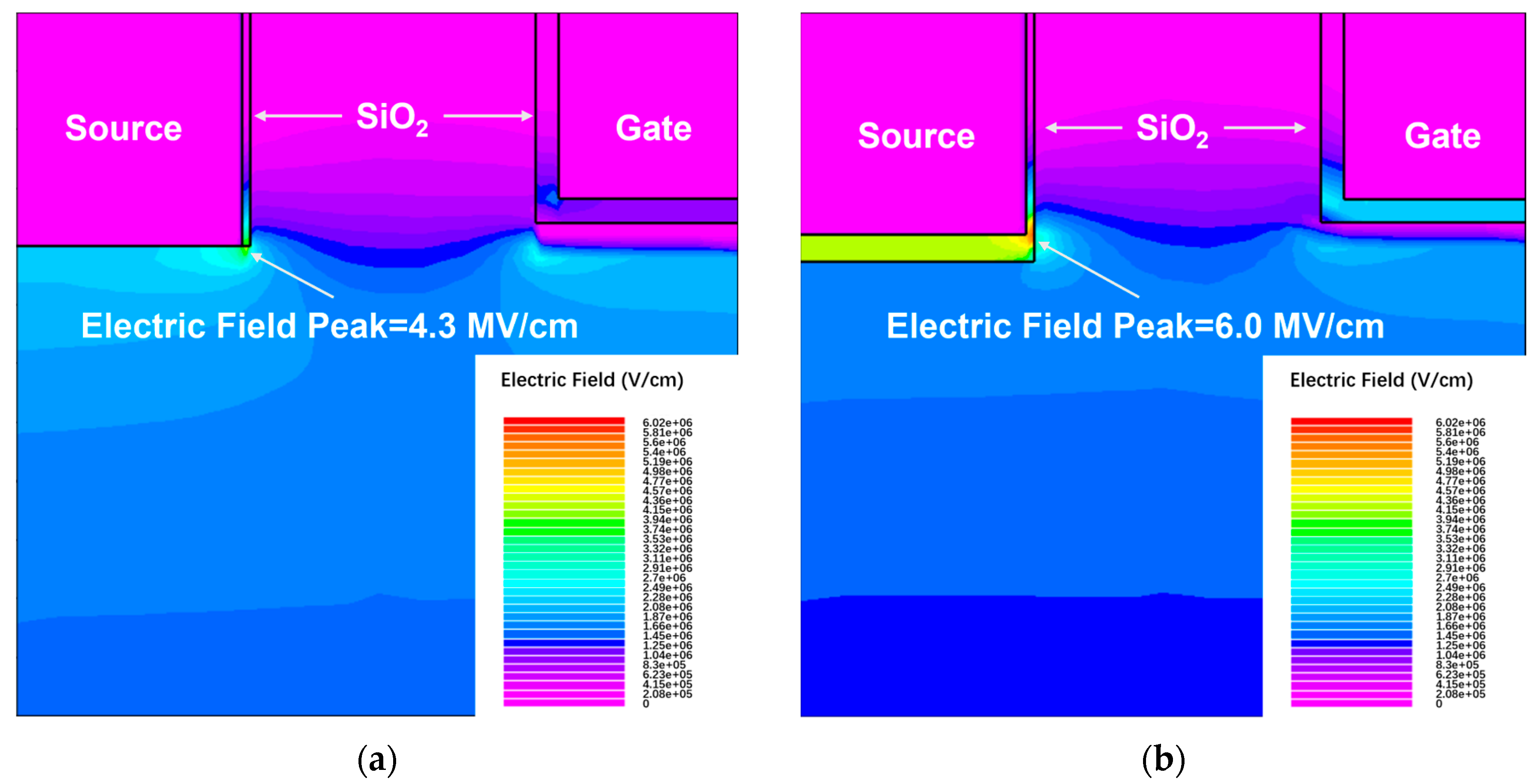

3.2. Breakdown Characteristics and Electric Field Distribution

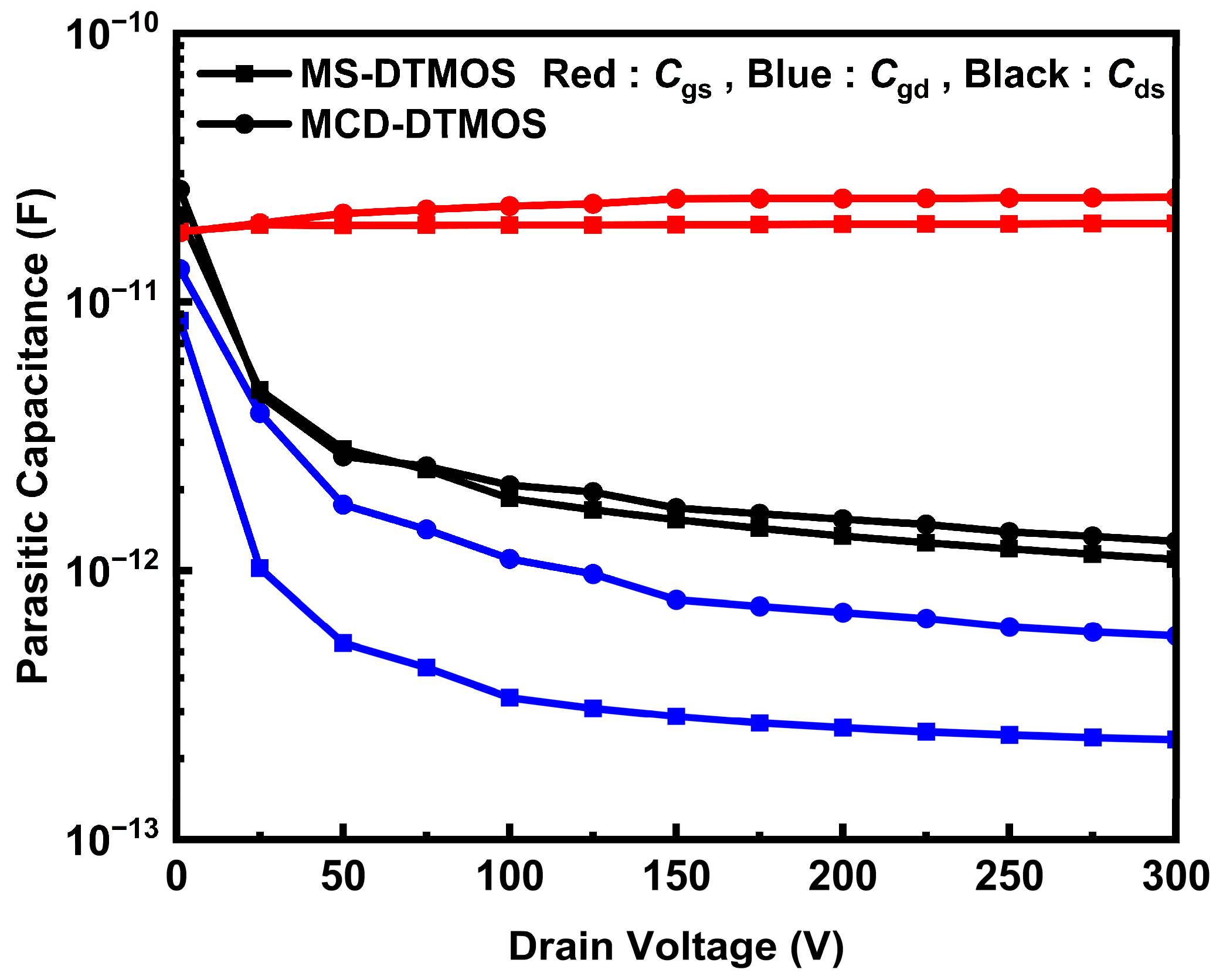

3.3. Parasitic Capacitance and Transient Characteristics

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Codreanu, C.; Avram, M.; Carbunescu, E.; Iliescu, E. Comparison of 3C–SiC, 6H–SiC and 4H–SiC MESFETs performances. Mater. Sci. Semicond. Process. 2000, 3, 137–142. [Google Scholar] [CrossRef]

- Zolper, J. Emerging silicon carbide power electronics components. In Proceedings of the Twentieth Annual IEEE Applied Power Electronics Conference and Exposition, APEC 2005, Austin, TX, USA, 6–10 March 2025; pp. 11–17. [Google Scholar]

- Manikandan, E.; Agarwal, L. A Comprehensive Review of Recent Progress, Prospect and Challenges of Silicon Carbide and its Applications. Silicon 2022, 14, 12887–12900. [Google Scholar] [CrossRef]

- Li, L.; Li, C.; Cao, Y.; Wang, F. Recent progress of SiC power devices and applications. IEEJ Trans. Electr. Electron. Eng. 2013, 8, 515–521. [Google Scholar] [CrossRef]

- Akbar, G.; Di Fatta, A.; Rizzo, G.; Ala, G.; Romano, P.; Imburgia, A. Comprehensive Review of Wide-Bandgap (WBG) Devices: SiC MOSFET and Its Failure Modes Affecting Reliability. Physchem 2025, 5, 10. [Google Scholar] [CrossRef]

- Harasimczuk, M.; Kopacz, R.; Trochimiuk, P.; Miśkiewicz, R.; Rąbkowski, J. Experimental Investigation on SiC MOSFET Turn-Off Power Loss Reduction Using the Current Sink Capacitor Technique. Energies 2024, 17, 189. [Google Scholar] [CrossRef]

- Amirpour, S.; Thiringer, T.; Hagstedt, D. Power Loss Analysis in a SiC/IGBT Propulsion Inverter Including Blanking Time, MOSFET’s Reverse Conduction and the Effect of Thermal Feedback Using a PMSM Model. In Proceedings of the IECON 2020 The 46th Annual Conference of the IEEE Industrial Electronics Society, Singapore, 18–21 October 2020; pp. 1424–1430. [Google Scholar]

- Li, Y.; Cooper, J.; Capano, M. High-voltage (3 kV) UMOSFETs in 4H-SiC. IEEE Trans. Electron. Devices 2002, 49, 972–975. [Google Scholar] [CrossRef]

- Skowronski, M.; Ha, S. Degradation of hexagonal silicon-carbide-based bipolar devices. J. Appl. Phys. 2006, 99, 011101. [Google Scholar] [CrossRef]

- Pal, A.; Pilli, N.K.; Klumpner, C.; Ahmed, R. Improved Switching Performance of 3.3kV SiC MOSFETs using Synchronous Rectification in A Voltage Source Inverter. In Proceedings of the 2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Houston, TX, USA, 20–24 March 2022; pp. 1–6. [Google Scholar]

- Ishigaki, T.; Hayakawa, S.; Murata, T.; Masuda, T.; Oda, T.; Takayanagi, Y. Diode-Less SiC Power Module With Countermeasures Against Bipolar Degradation to Achieve Ultrahigh Power Density. IEEE Trans. Electron. Devices 2020, 67, 2035–2043. [Google Scholar] [CrossRef]

- Sung, W.; Baliga, B.J. Monolithically Integrated 4H-SiC MOSFET and JBS Diode (JBSFET) Using a Single Ohmic/Schottky Process Scheme. IEEE Electron Device Lett. 2016, 37, 1605–1608. [Google Scholar] [CrossRef]

- Jiang, H.; Wei, J.; Dai, X.; Zheng, C.; Ke, M.; Deng, X.; Sharma, Y.; Deviny, I.; Mawby, P. SiC MOSFET with built-in SBD for reduction of reverse recovery charge and switching loss in 10-kV applications. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017; pp. 49–52. [Google Scholar]

- Matsui, K.; Aiba, R.; Yano, H.; Iwamuro, N.; Baba, M.; Harada, S. Comprehensive Study on Electrical Characteristics in 1.2 kV SiC SBD-integrated Trench and Planar MOSFETs. In Proceedings of the 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 30 May–3 June 2021; pp. 215–218. [Google Scholar]

- Todaka, S.; Matsui, K.; Aiba, R.; Yano, H.; Iwamuro, N.; Baba, M.; Harada, S. Experimental and Numerical Demonstration of Superior RBSOAs in 1.2 kV SiC Trench and SBD-integrated Trench MOSFETs. In Proceedings of the 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 30 May–3 June 2021; pp. 219–222. [Google Scholar]

- Han, K.; Agarwal, A.; Kanale, A.; Baliga, B.J.; Bhattacharya, S.; Cheng, T.-H.; Hopkins, D.; Amarasinghe, V.; Ransom, J. Monolithic 4-Terminal 1.2 kV/20 A 4H-SiC Bi-Directional Field Effect Transistor (BiDFET) with Integrated JBS Diodes. In Proceedings of the 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020; pp. 242–245. [Google Scholar]

- Sundaresan, S.; Park, J.; Mulpuri, V.; Singh, R. Performance and Robustness of 6500 V SiC DMOSFETs with Integrated MPS diodes. In Proceedings of the 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 30 May–3 June 2021; pp. 235–238. [Google Scholar]

- Li, X.; Tong, X.; Huang, A.Q.; Tao, H.; Zhou, K.; Jiang, Y.; Jiang, J.; Deng, X.; She, X.; Zhang, B.; et al. SiC Trench MOSFET With Integrated Self-Assembled Three-Level Protection Schottky Barrier Diode. IEEE Trans. Electron. Devices 2017, 65, 347–351. [Google Scholar] [CrossRef]

- Uchida, M.; Horikawa, N.; Tanaka, K.; Takahashi, K.; Kiyosawa, T.; Hayashi, M.; Niwayama, M.; Kusumoto, O.; Adachi, K.; Kudou, C.; et al. Novel SiC power MOSFET with integrated unipolar internal inverse MOS-channel diode. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 26.6.1–26.6.4. [Google Scholar] [CrossRef]

- Zhang, M.; Wei, J.; Zhou, X.; Jiang, H.; Li, B.; Chen, K.J. Simulation Study of a Power MOSFET with Built-in Channel Diode for Enhanced Reverse Recovery Performance. IEEE Electron Device Lett. 2019, 40, 79–82. [Google Scholar] [CrossRef]

- Zhou, X.; Gong, H.; Jia, Y.; Hu, D.; Wu, Y.; Xia, T.; Pang, H.; Zhao, Y. SiC Planar MOSFETs With Built-In Reverse MOS-Channel Diode for Enhanced Performance. IEEE J. Electron Devices Soc. 2020, 8, 619–625. [Google Scholar] [CrossRef]

- Deng, X.; Xu, X.; Li, X.; Li, X.; Wen, Y.; Chen, W. A Novel SiC MOSFET Embedding Low Barrier Diode With Enhanced Third Quadrant and Switching Performance. IEEE Electron Device Lett. 2020, 41, 1472–1475. [Google Scholar] [CrossRef]

- Li, P.; Guo, J.; Hu, S.; Lin, Z. A SiC Planar MOSFET with an Embedded MOS-Channel Diode to Improve Reverse Conduction and Switching. Micromachines 2023, 14, 1282. [Google Scholar] [CrossRef] [PubMed]

- Wei, J.; Jiang, Q.; Luo, X.; Huang, J.; Yang, K.; Ma, Z.; Fang, J.; Yang, F. High performance SiC trench-type MOSFET with an integrated MOS-channel diode. Chin. Phys. B 2023, 32, 028503. [Google Scholar] [CrossRef]

- ATLAS User’s Manual; Silvaco Int.: Santa Clara, CA, USA, 2010.

- Luo, X.; Liao, T.; Wei, J.; Fang, J.; Yang, F.; Zhang, B. A novel 4H-SiC trench MOSFET with double shielding structures and ultralow gate-drain charge. J. Semicond. 2019, 40, 052803. [Google Scholar] [CrossRef]

- Han, Z.; Bai, Y.; Chen, H.; Li, C.; Lu, J.; Yang, C.; Yao, Y.; Tian, X.; Tang, Y.; Song, G.; et al. A novel 4H-SiC trench MOSFET integrated with mesa-sidewall SBD. IEEE Trans. Electron. Devices 2020, 68, 192–196. [Google Scholar] [CrossRef]

- Tian, K.; Hallen, A.; Qi, J.; Ma, S.; Fei, X.; Zhang, A.; Liu, W. An improved 4H-SiC trench-gate MOSFET with low ON-resistance and switching loss. IEEE Trans. Electron. Devices 2019, 66, 2307–2313. [Google Scholar] [CrossRef]

- Huang, M.; Deng, Y.; Lai, L.; Yang, Z.; Gao, B.; Gong, M. A vertical superjunction MOSFET with n-Si and p-3C-SiC pillars. IEEE Trans. Electron. Devices 2019, 66, 3922–3928. [Google Scholar] [CrossRef]

- Yang, T.; Wang, Y.; Yue, R. SiC trench MOSFET with reduced switching loss and increased short-circuit capability. IEEE Trans. Electron. Devices 2020, 67, 3685–3690. [Google Scholar] [CrossRef]

| Parameters | Values |

|---|---|

| N− Drift layer thickness (TDrift) | 9 µm |

| N− Drift layer concentration (NDrift) | 7 × 1015/cm3 |

| N− CSL layer thickness (TCSL) | 1.4 µm |

| N− CSL Concentration (NCSL) | 1 × 1016/cm3 |

| Trench size | 1.0 × 1.0 µm |

| Source length (Lsource) | 1.0 µm |

| P− base layer length (LBase) | 0.63 µm |

| P− base layer thickness (Tch) | 0.5 µm |

| P− base layer concentration (Nbase) | 3 × 1016/cm3 |

| N+/P+ concentration (NN+) | 1 × 1019/cm3 |

| N+ layer thickness (TN+) | 0.1 µm |

| N+ Sub layer concentration (NSub) | 1 × 1018/cm3 |

| N+ Sub layer thickness (TSub) | 1 µm |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, P.; Li, C.; Deng, C.; Yang, Q.; Xu, S.; Tang, X.; Wang, Z.; Tao, W.; Tao, N.; Wang, Q.; et al. Novel 4H-SiC Double-Trench MOSFETs with Integrated Schottky Barrier and MOS-Channel Diodes for Enhanced Breakdown Voltage and Switching Characteristics. Nanomaterials 2025, 15, 946. https://doi.org/10.3390/nano15120946

Wang P, Li C, Deng C, Yang Q, Xu S, Tang X, Wang Z, Tao W, Tao N, Wang Q, et al. Novel 4H-SiC Double-Trench MOSFETs with Integrated Schottky Barrier and MOS-Channel Diodes for Enhanced Breakdown Voltage and Switching Characteristics. Nanomaterials. 2025; 15(12):946. https://doi.org/10.3390/nano15120946

Chicago/Turabian StyleWang, Peiran, Chenglong Li, Chenkai Deng, Qinhan Yang, Shoucheng Xu, Xinyi Tang, Ziyang Wang, Wenchuan Tao, Nick Tao, Qing Wang, and et al. 2025. "Novel 4H-SiC Double-Trench MOSFETs with Integrated Schottky Barrier and MOS-Channel Diodes for Enhanced Breakdown Voltage and Switching Characteristics" Nanomaterials 15, no. 12: 946. https://doi.org/10.3390/nano15120946

APA StyleWang, P., Li, C., Deng, C., Yang, Q., Xu, S., Tang, X., Wang, Z., Tao, W., Tao, N., Wang, Q., & Yu, H. (2025). Novel 4H-SiC Double-Trench MOSFETs with Integrated Schottky Barrier and MOS-Channel Diodes for Enhanced Breakdown Voltage and Switching Characteristics. Nanomaterials, 15(12), 946. https://doi.org/10.3390/nano15120946