Effect of Temperature-Dependent Low Oxygen Partial Pressure Annealing on SiC MOS

Abstract

1. Introduction

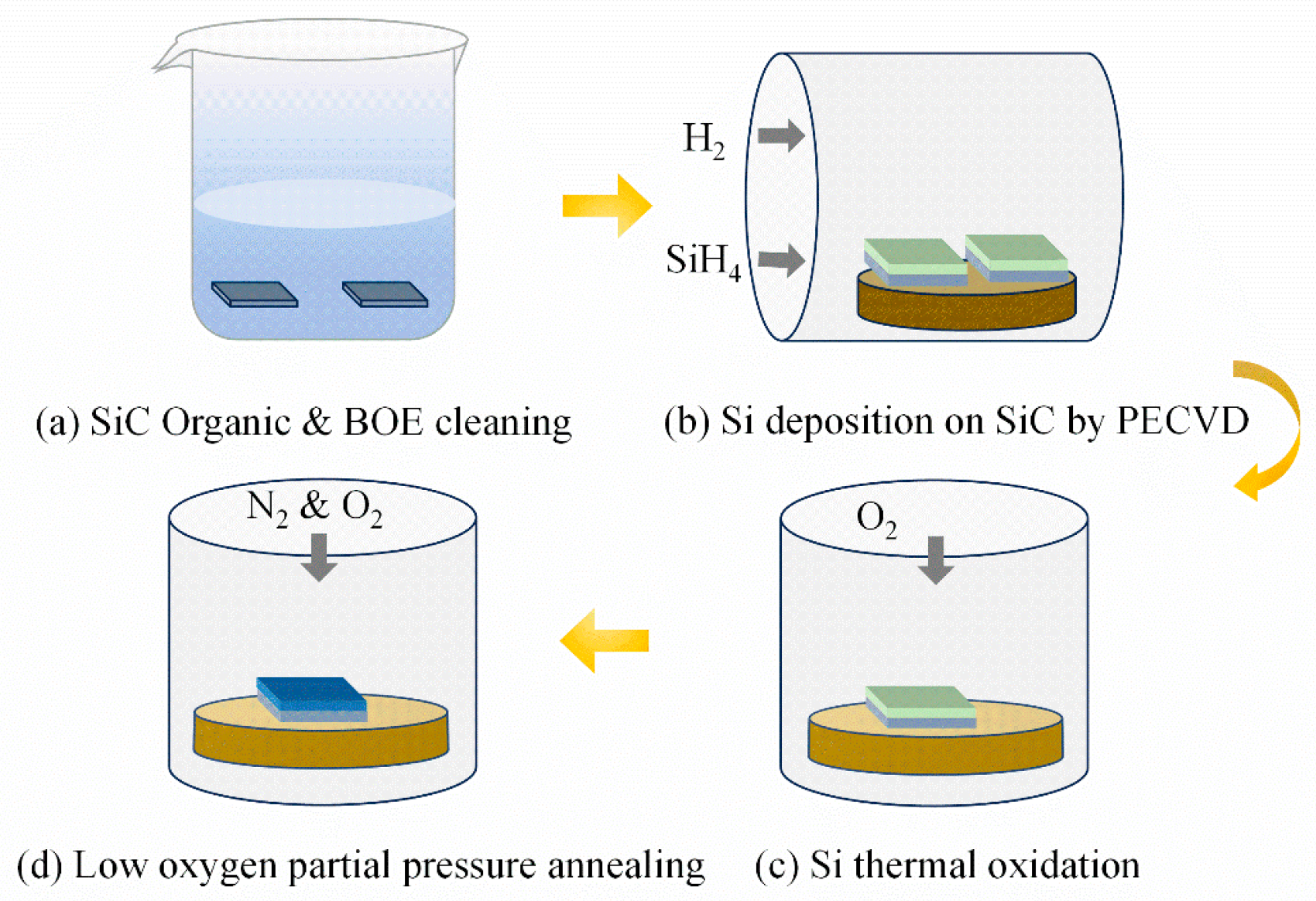

2. Materials and Methods

3. Results and Discussion

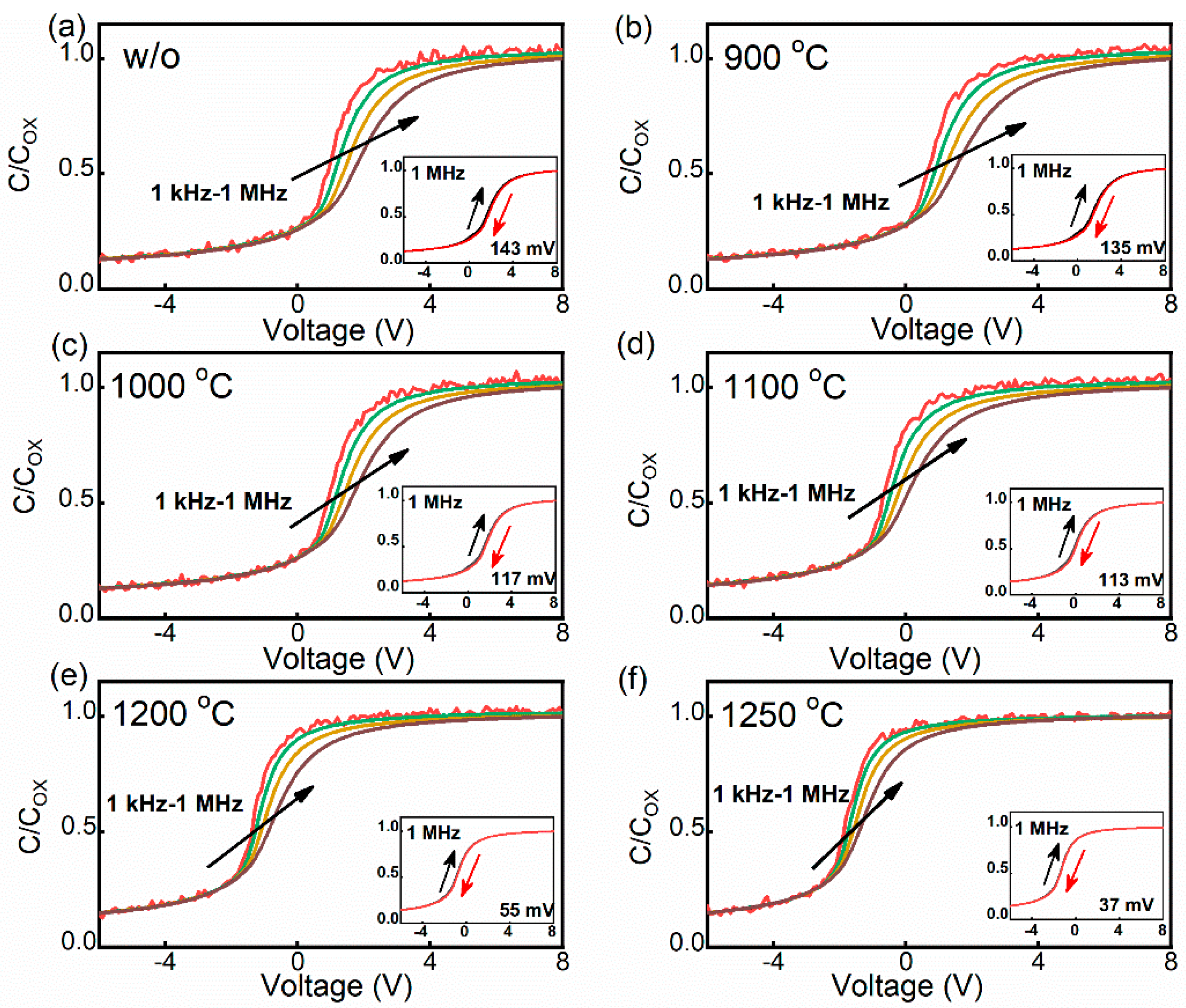

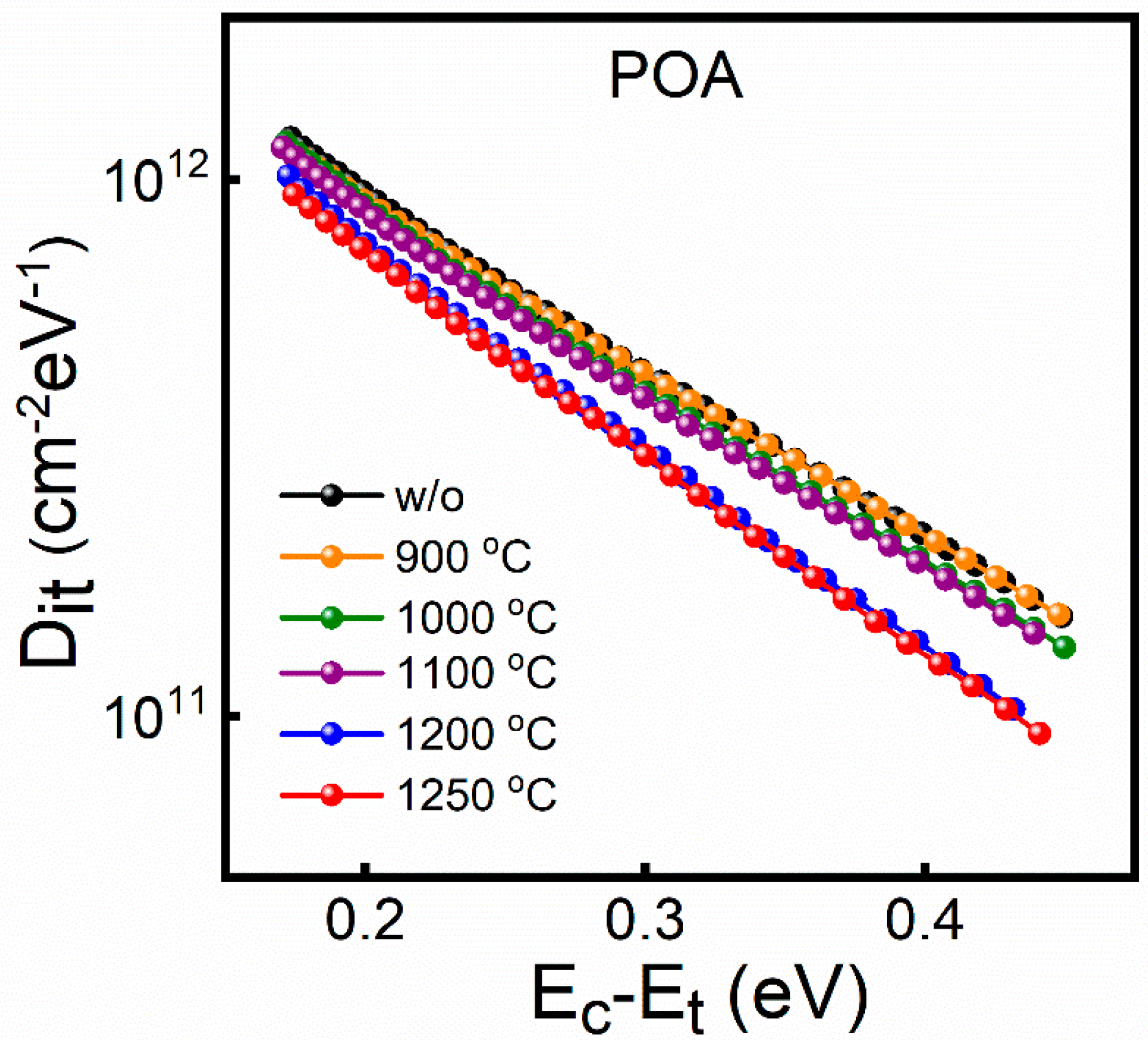

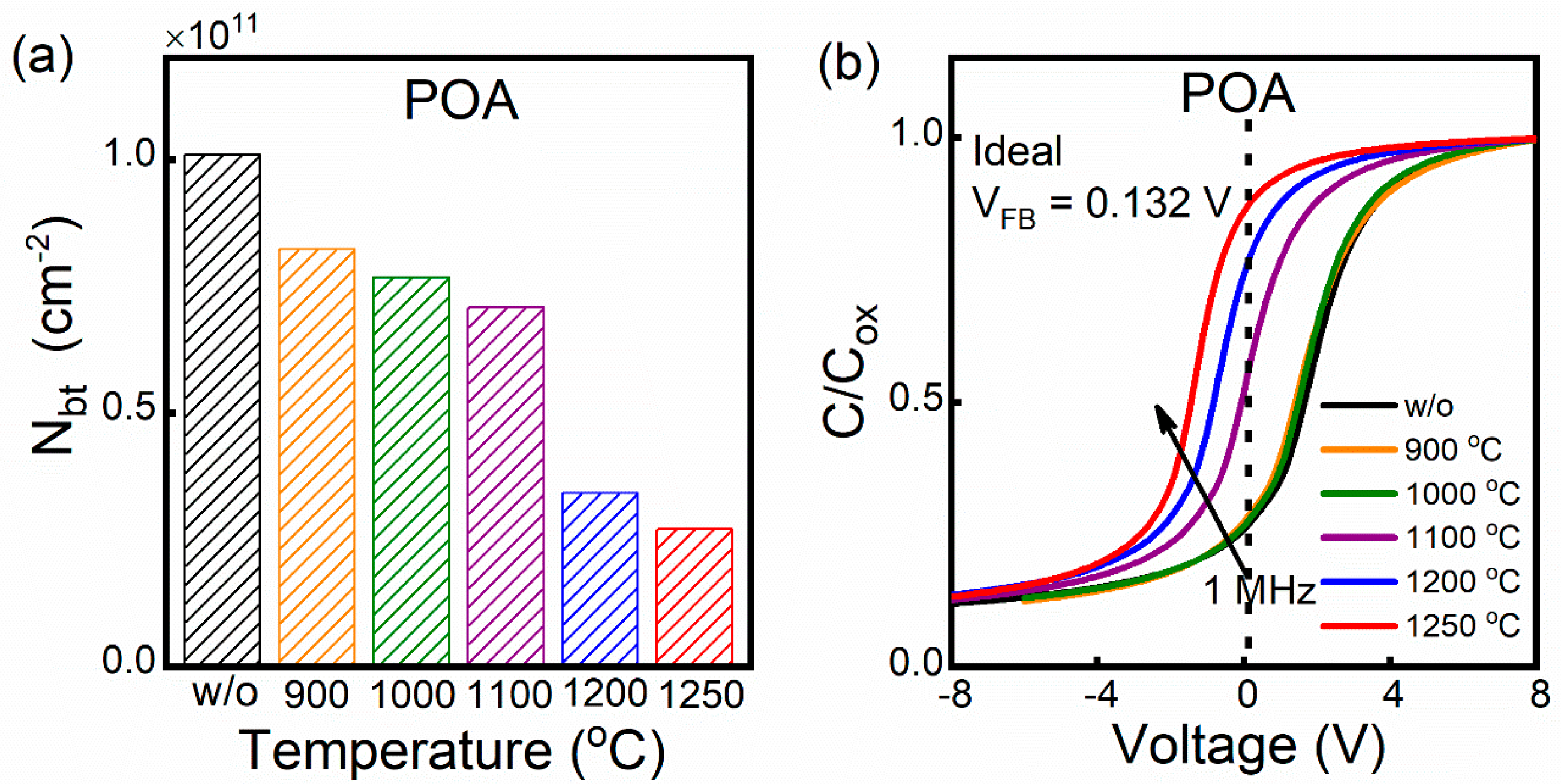

3.1. Effect of Low Oxygen Partial Pressure Annealing at Different Temperatures

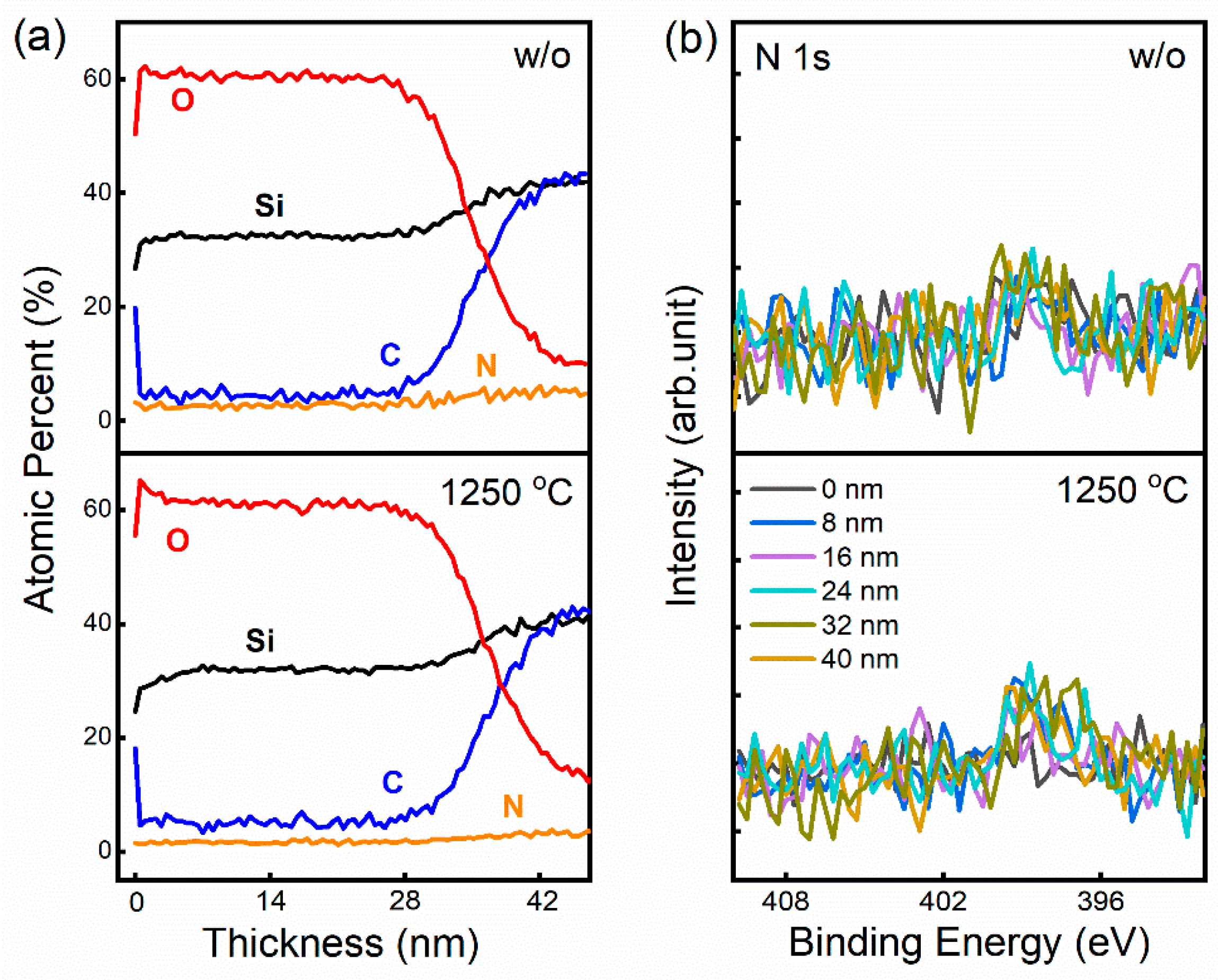

3.2. Annealing Mechanism of Low Oxygen Partial Pressure at Different Temperatures

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kimoto, T. Bulk and epitaxial growth of silicon carbide. Prog. Cryst. Growth Charact. Mater. 2016, 62, 329–351. [Google Scholar] [CrossRef]

- Stefanakis, D.; Chi, X.; Maeda, T.; Kaneko, M.; Kimoto, T. Experimental determination of impact ionization coefficients along (1120) in 4H-SiC. IEEE Trans. Electron Devices 2020, 67, 3740–3744. [Google Scholar] [CrossRef]

- Matsunami, H. Fundamental research on semiconductor SiC and its applications to power electronics. Proc. Jpn. Acad. Ser. B 2020, 96, 235–254. [Google Scholar] [CrossRef]

- Xie, Y.; Chen, C.; Yan, Y.Y.; Huang, Z.Z.; Kang, Y. Investigation on Ultralow Turn-off Losses Phenomenon for SiC MOSFETs With Improved Switching Model. IEEE Trans. Power Electron. 2021, 36, 9382–9397. [Google Scholar] [CrossRef]

- Kimoto, T. High-voltage SiC power devices for improved energy efficiency. Proc. Jpn. Acad. Ser. B 2022, 98, 161–189. [Google Scholar] [CrossRef]

- Arnold, E.; Alok, D. Effect of interface states on electron transport in 4H-SiC inversion layers. IEEE Trans. Electron Devices 2001, 48, 1870. [Google Scholar] [CrossRef]

- Yoshioka, H.; Senzaki, J.; Shimozato, A.; Tanaka, Y.; Okumura, H. N-channel field- effect mobility inversely proportional to the interface state density at the conduction band edges of SiO2/4H-SiC interfaces. AIP Adv. 2015, 5, 017109. [Google Scholar] [CrossRef]

- Hatakeyama, T.; Kiuchi, Y.; Sometani, M.; Harada, S.; Okamoto, D.; Yano, H.; Yonezawa, Y.; Okumura, H. Characterization of traps at nitrided SiO2/SiC interfaces near the conduction band edge by using Hall effect measurements. Appl. Phys. Express 2017, 10, 046601. [Google Scholar] [CrossRef]

- Kobayashi, T.; Okuda, T.; Tachiki, K.; Ito, K.; Matsushita, Y.I.; Kimoto, T. Design and formation of SiC (0001)/SiO2 interfaces via Si deposition followed by low temperature oxidation and high-temperature nitridation. Appl. Phys. Express 2020, 13, 091003. [Google Scholar] [CrossRef]

- Liu, X.Y.; Hao, J.L.; You, N.N.; Bai, Y.; Wang, S.K. High-pressure microwave plasma oxidation of 4H-SiC with low interface trap density. AIP Adv. 2019, 9, 125150. [Google Scholar] [CrossRef]

- Morishita, R.; Yano, H.; Okamoto, D.; Hatayama, T.; Fuyuki, T. Effect of POCl3 Annealing on Reliability of Thermal Oxides Grown on 4H-SiC. Mater. Sci. Forum 2012, 717, 739–742. [Google Scholar] [CrossRef]

- Jamet, P.; Dimitrijev, S.; Tanner, P. Effects of nitridation in gate oxides grown on 4H-SiC. J. Appl. Phys. 2001, 90, 5058–5063. [Google Scholar] [CrossRef]

- Chung, G.Y.; Tin, C.C.; Williams, J.R.; Mcdonald, K.; Palmour, J.W. Improved inversion channel mobility for 4H-SiC MOSFETs following high temperature anneals in nitric oxide. IEEE Electron Device Lett. 2001, 22, 176–178. [Google Scholar] [CrossRef]

- Kimoto, T.; Kanzaki, Y.; Noborio, M.; Kawano, H.; Matsunami, H. Interface Properties of Metal–Oxide–Semiconductor Structures on 4H-SiC {0001} and (1120) Formed by N2O Oxidation. Jpn. J. Appl. Phys. 2005, 44, 1213–1218. [Google Scholar] [CrossRef]

- Shirasawa, T.; Hayashi, K.; Mizuno, S.; Tanaka, S.; Nakatsuji, K.; Komori, F.; Tochihara, H. Epitaxial Silicon Oxynitride Layer on a 6H−SiC (0001) Surface. Phys. Rev. Lett. 2007, 98, 136105. [Google Scholar] [CrossRef] [PubMed]

- Xu, Y.; Zhu, X.; Lee, H.D.; Xu, C.; Shubeita, S.M.; Ahyi, A.C.; Sharma, Y.; Williams, J.R.; Lu, W.; Ceesay, S.; et al. Atomic state and characterization of nitrogen at the SiC/SiO2 interface. J. Appl. Phys. 2014, 115, 033502. [Google Scholar] [CrossRef]

- Kao, W.C.; Goryll, M.; Marinella, M.; Kaplar, R.J.; Jiao, C.; Dhar, S.; Cooper, J.A.; Schroder, D.K. Characterization of fast interface states in nitrogen- and phosphorus-treated 4H-SiC MOS capacitors. Semicond. Sci. Technol. 2015, 30, 075011. [Google Scholar] [CrossRef]

- Zhang, Q.; You, N.N.; Liu, P.; Wang, J.Y.; Xu, Y.; Wang, S.K. Study of defects distribution in SiO2/SiC with plasma oxidation and post oxidation annealing. Appl. Surf. Sci. 2023, 610, 155500. [Google Scholar] [CrossRef]

- Kobayashi, T.; Tachiki, K.; Ito, K.; Kimoto, T. Reduction of interface state density in SiC (0001) MOS structures by low-oxygen-partial-pressure annealing. Appl. Phys. Express 2019, 12, 031001. [Google Scholar] [CrossRef]

- Ziegler, K.; Klausmann, E. Static technique for precise measurements of surface potential and interface state density in MOS structures. Appl. Phys. Lett. 1975, 26, 400–402. [Google Scholar] [CrossRef]

- Southwick, R.G., III; Knowlton, W.B. Stacked dual oxide MOS energy band diagram visual representation program. IEEE Trans. Device Mater. Reliab. 2006, 6, 136–145. [Google Scholar] [CrossRef]

- Southwick, R.G., III; Sup, A.; Jain, A.; Knowlton, W.B. An interactive simulation tool for complex multilayer dielectric devices. IEEE Trans. Device Mater. Reliab. 2011, 11, 236–243. [Google Scholar] [CrossRef]

- Nicollian, E.H.; Brews, J.R. MOS (Metal Oxide Semiconductor) Physics and Technology; Wiley: Hoboken, NJ, USA, 1982; pp. 176–230. [Google Scholar]

- Berglund, C.N. Surface states at steam-grown silicon-silicon dioxide interfaces. IEEE Trans. Electron Devices 1966, ED-13, 701–705. [Google Scholar] [CrossRef]

- Lelis, A.J.; Habersat, D.; Green, R.; Ogunniyi, A.; Gurfinkel, M.; Suehle, J.; Goldsman, N. Time Dependence of Bias-Stress-Induced SiC MOSFET Threshold-Voltage Instability Measurements. IEEE Trans. Electron Devices 2008, 55, 1835–1840. [Google Scholar] [CrossRef]

- Evangelou, E.K.; Rahman, M.S.; Dimoulas, A. Correlation of Charge Buildup and Stress-Induced Leakage Current in Cerium Oxide Films Grown on Ge (100) Substrates. IEEE Trans. Electron Devices 2009, 56, 399–407. [Google Scholar] [CrossRef]

- Fleetwood, D.M.; Saks, N.S. Oxide, interface, and border traps in thermal, N2O, and N2O-nitrided oxides. J. Appl. Phys. 1996, 79, 1583–1594. [Google Scholar] [CrossRef]

- Pitthan, E.; Lopes, L.D.; Palmieri, R.; Corrêa, S.A.; Soares, G.V.; Boudinov, H.I.; Stedile, F.C. Influence of thermal growth parameters on the SiO2/4H-SiC interfacial region. APL Mater. 2013, 1, 022101. [Google Scholar] [CrossRef]

- Agarwal, A.K.; Haney, S. Some critical materials and processing issues in SiC power devices. J. Electron. Mater. 2008, 37, 646–654. [Google Scholar] [CrossRef]

- Lelis, A.J.; Green, R.; Habersat, D.B.; El, M. Basic mechanisms of threshold-voltage instability and implications for reliability testing of SiC MOSFETs. IEEE Trans. Electron Devices 2015, 62, 316–323. [Google Scholar] [CrossRef]

- Wang, S.K.; Kita, K.; Lee, C.H.; Tabata, T.; Nishimura, T.; Nagashio, K.; Toriumi, A. Desorption kinetics of GeO from GeO2/Ge structure. J. Appl. Phys. 2010, 108, 054104. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, Q.; You, N.; Wang, J.; Xu, Y.; Zhang, K.; Wang, S. Effect of Temperature-Dependent Low Oxygen Partial Pressure Annealing on SiC MOS. Nanomaterials 2024, 14, 192. https://doi.org/10.3390/nano14020192

Zhang Q, You N, Wang J, Xu Y, Zhang K, Wang S. Effect of Temperature-Dependent Low Oxygen Partial Pressure Annealing on SiC MOS. Nanomaterials. 2024; 14(2):192. https://doi.org/10.3390/nano14020192

Chicago/Turabian StyleZhang, Qian, Nannan You, Jiayi Wang, Yang Xu, Kuo Zhang, and Shengkai Wang. 2024. "Effect of Temperature-Dependent Low Oxygen Partial Pressure Annealing on SiC MOS" Nanomaterials 14, no. 2: 192. https://doi.org/10.3390/nano14020192

APA StyleZhang, Q., You, N., Wang, J., Xu, Y., Zhang, K., & Wang, S. (2024). Effect of Temperature-Dependent Low Oxygen Partial Pressure Annealing on SiC MOS. Nanomaterials, 14(2), 192. https://doi.org/10.3390/nano14020192