A Coupling Mechanism between Flicker Noise and Hot Carrier Degradations in FinFETs

Abstract

1. Introduction

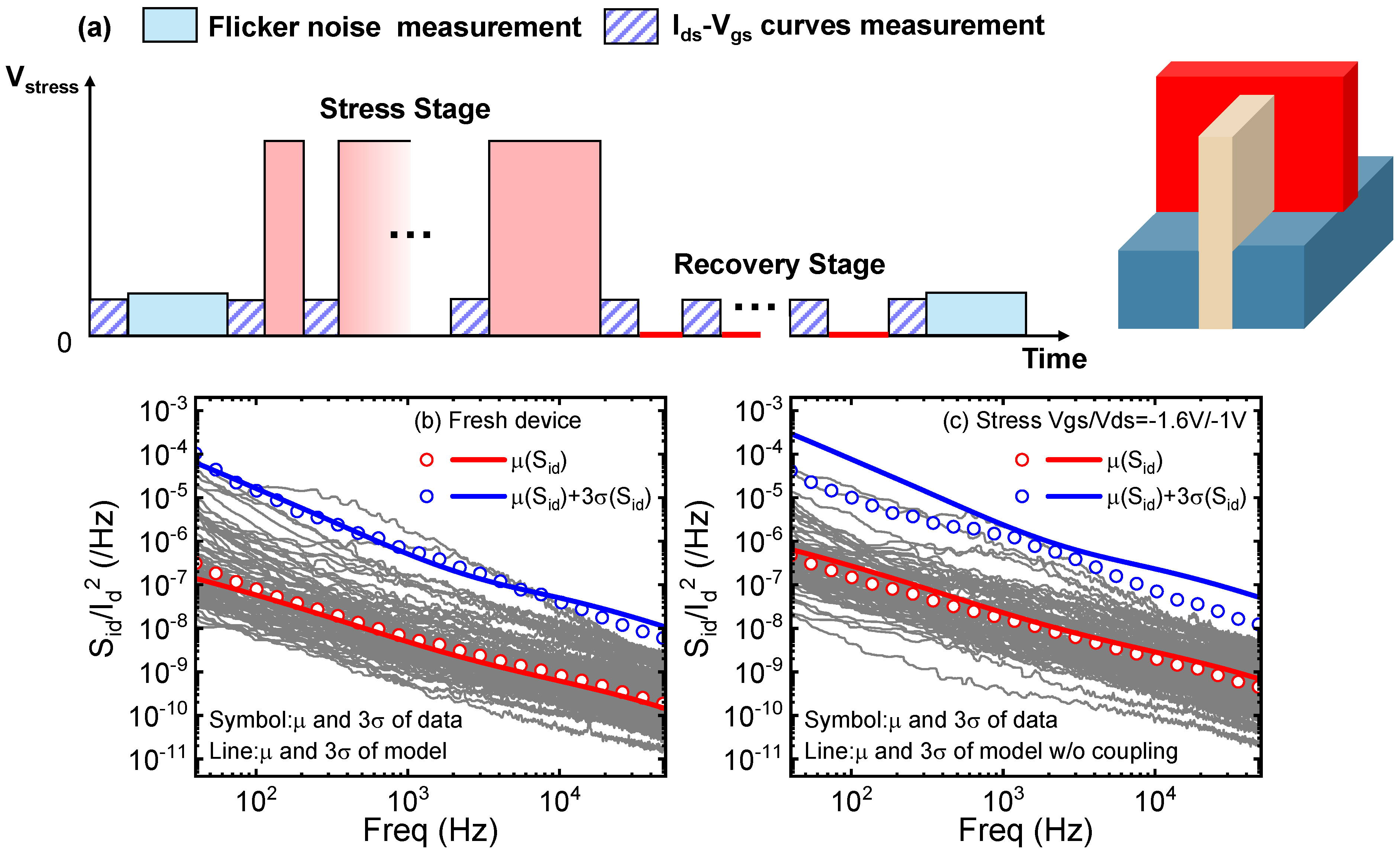

2. Characterizing Flicker Noise of FinFETs

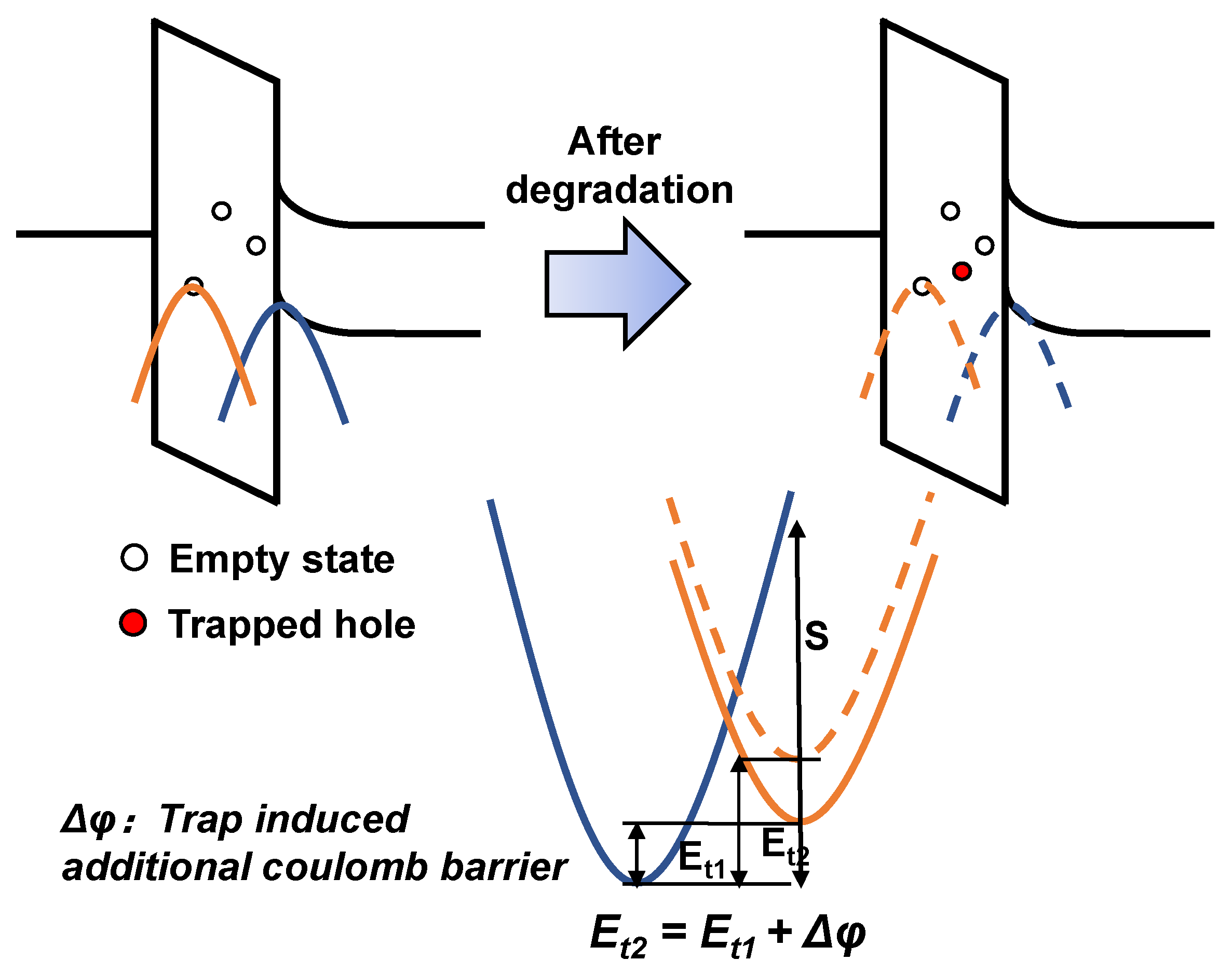

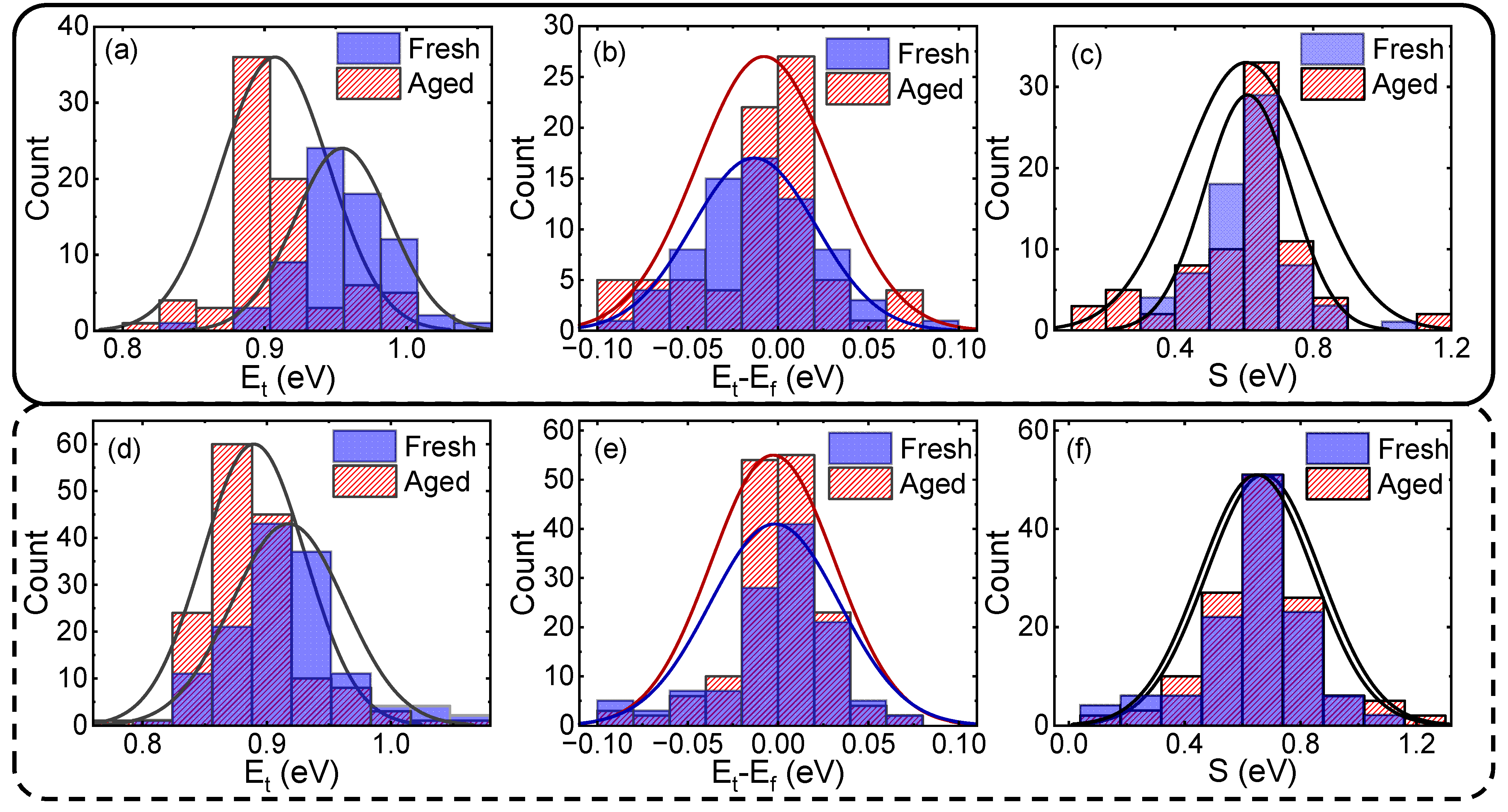

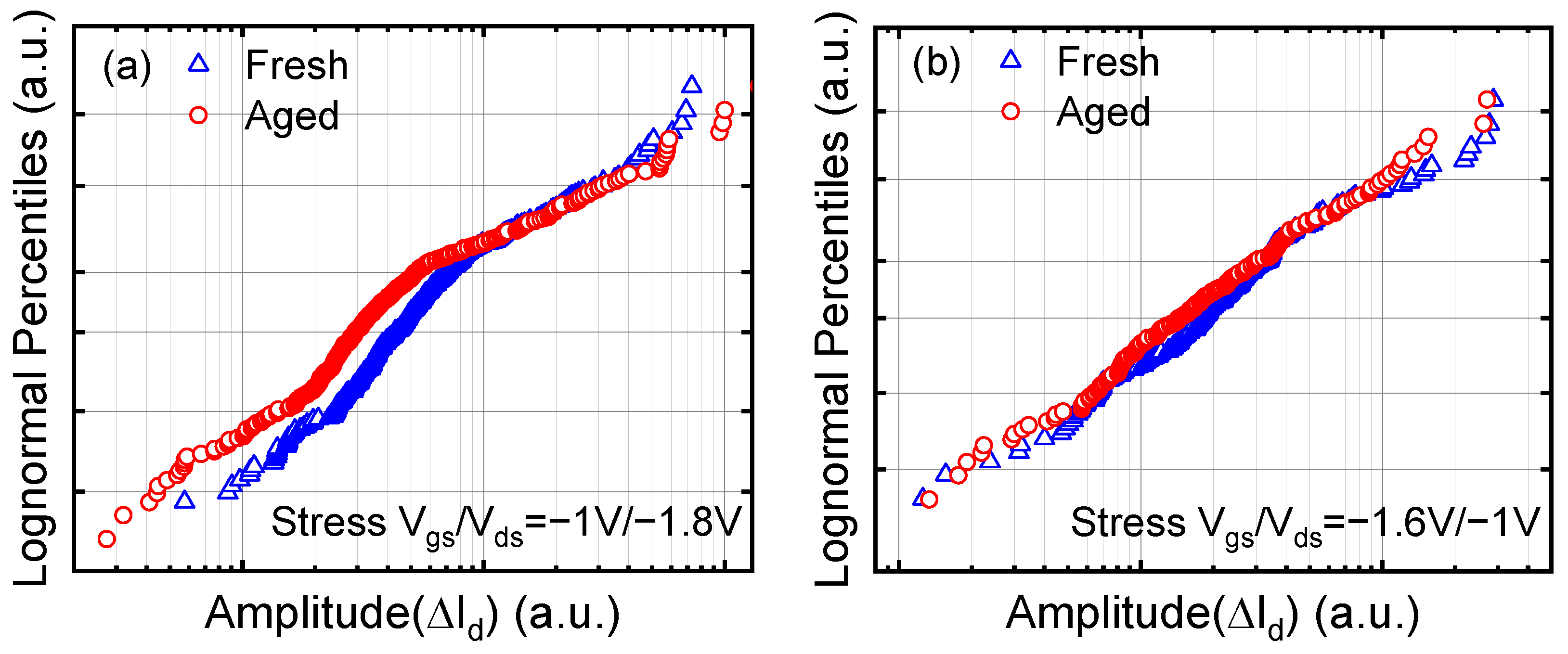

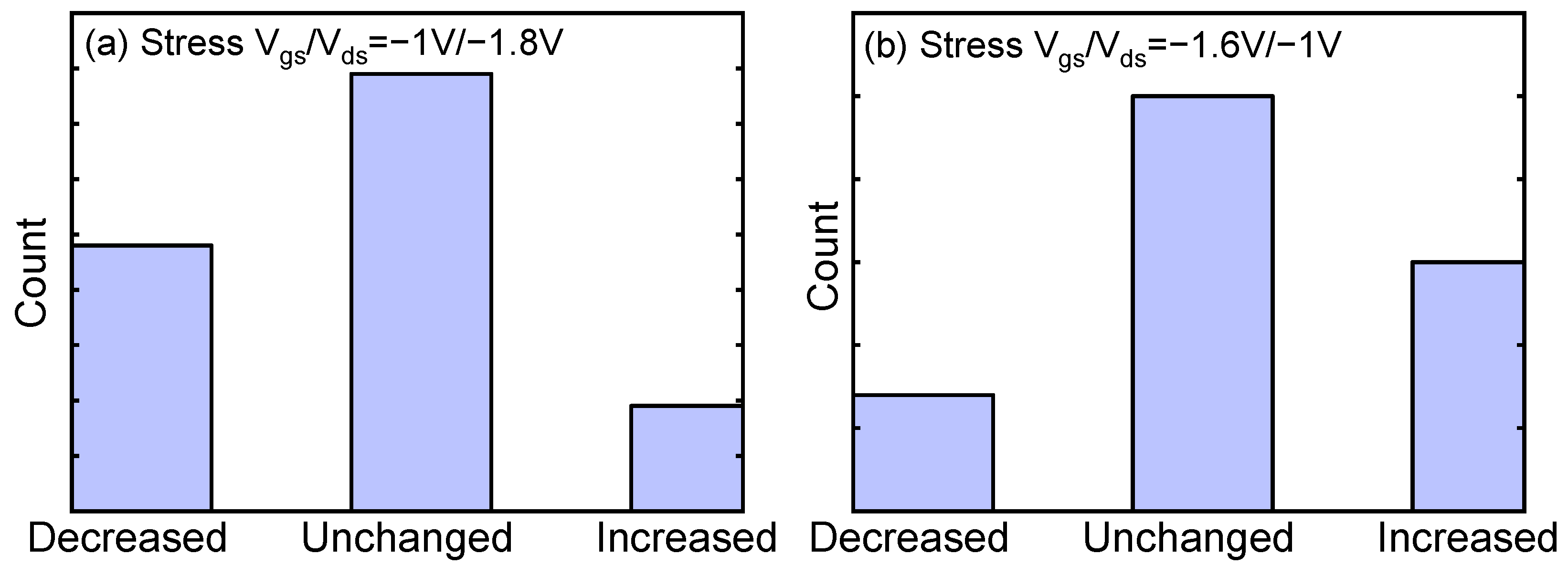

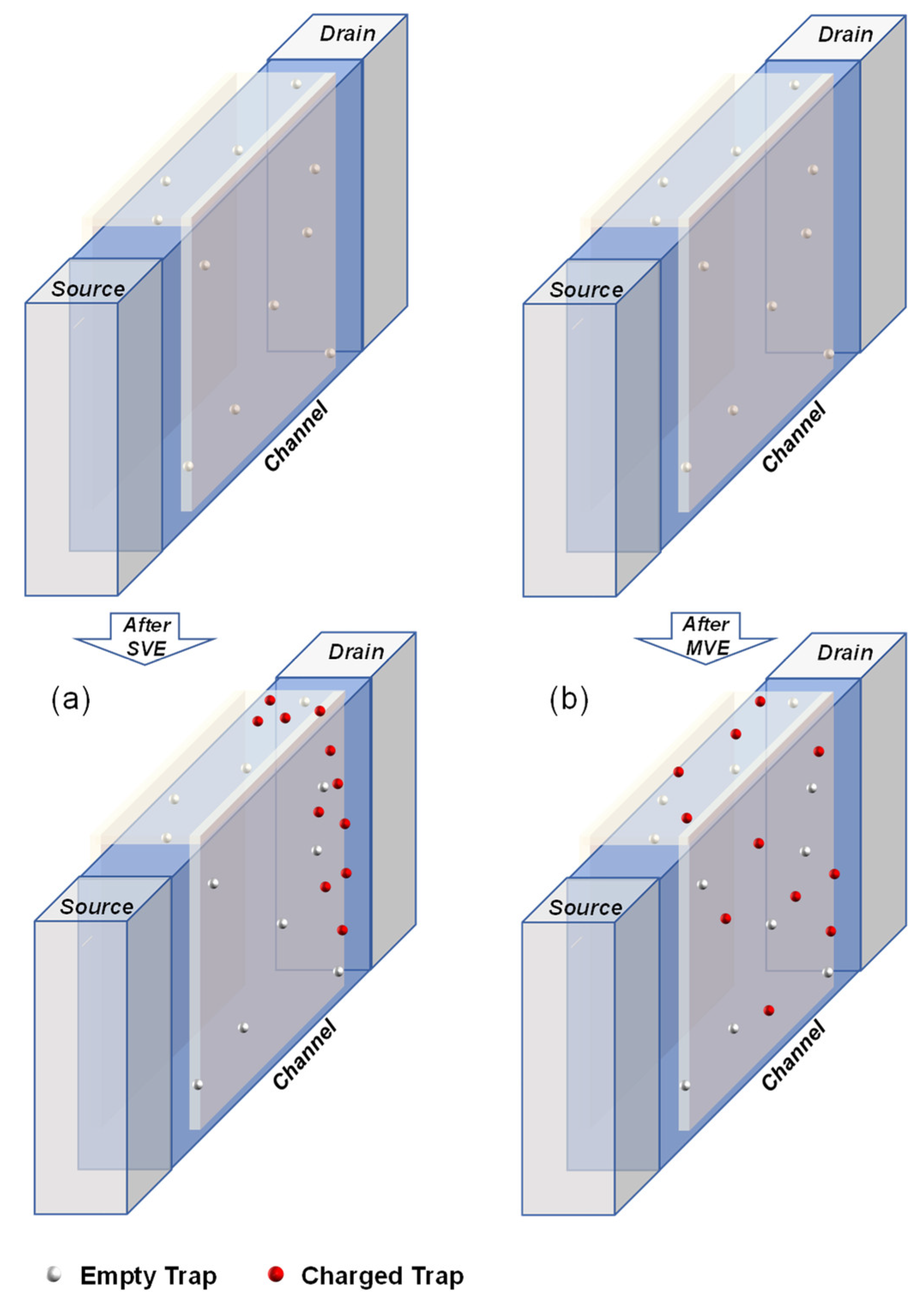

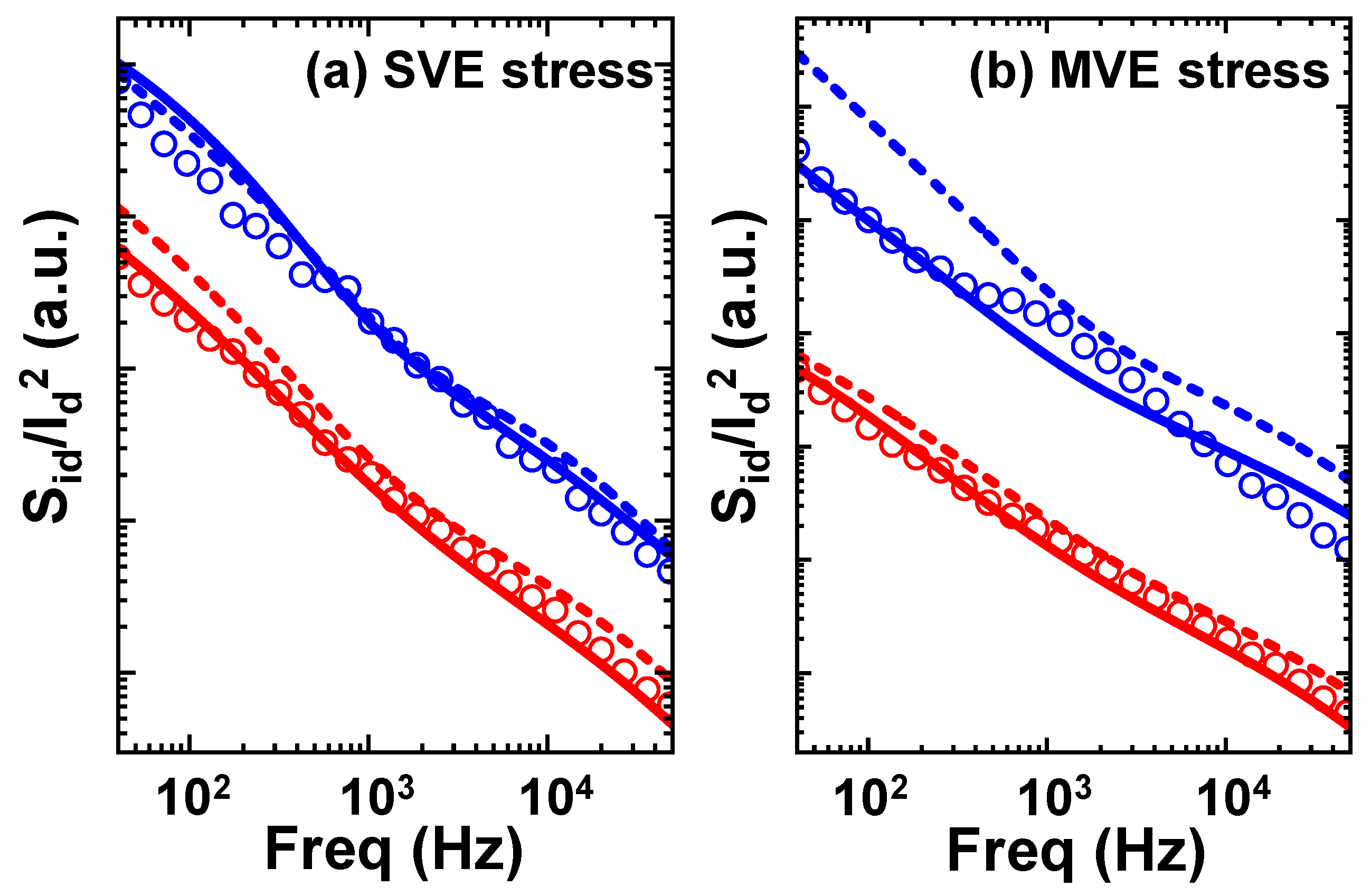

3. Analyzing the Flicker Noise

4. Flicker Noise with the Coupling Mechanism

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Deen, M.J. Low frequency noise in silicon-based devices, circuits and systems. In Proceedings of the 2013 22nd International Conference on Noise and Fluctuations (ICNF), Montpellier, France, 24–28 June 2013; pp. 1–5. [Google Scholar]

- Grasser, T. Hot Carrier Degradation in Semiconductor Devices; Springer: Berlin/Heidelberg, Germany, 2015. [Google Scholar]

- Tyaginov, S.; Grill, A.; Vandemaele, M.; Grasser, T.; Hellings, G.; Makarov, A.; Jech, M.; Linten, D.; Kaczer, B. A compact physics analytical model for hot-carrier degradation. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020; pp. 1–7. [Google Scholar]

- Morshed, T.H.; Dunga, M.V.; Zhang, J.; Lu, D.D.; Niknejad, A.M.; Hu, C. Compact modeling of flicker noise variability in small size MOSFETs. In Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009; pp. 1–4. [Google Scholar]

- Kushwaha, P.; Agarwal, H.; Lin, Y.K.; Dasgupta, A.; Kao, M.Y.; Lu, Y.; Yue, Y.; Chen, X.; Wang, J.; Sy, W.; et al. Characterization and modeling of flicker noise in FinFETs at advanced technology node. IEEE Electron Device Lett. 2019, 40, 985–988. [Google Scholar] [CrossRef]

- Zhang, B.; Hu, C.; Xin, Y.; Li, Y.; Xie, Y.; Xing, Q.; Guo, Z.; Xue, Z.; Li, D.; Zhang, G.; et al. Analysis of low-frequency 1/f noise characteristics for MoTe2 ambipolar field-effect transistors. Nanomaterials 2022, 12, 1325. [Google Scholar] [CrossRef] [PubMed]

- Yan, C.; Ding, Y.; Qu, Y.; Zhao, L.; Zhao, Y. Universal hot carrier degradation model under DC and AC stresses. In Proceedings of the 2022 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 27–31 March 2022; pp. 7A. 1-1–7A. 1-6. [Google Scholar]

- Da Silva, M.B.; Wirth, G.I.; Tuinhout, H.P.; Zegers-van Duijnhoven, A.; Scholten, A.J. Random Telegraph Noise in Analog CMOS Circuits. IEEE Trans. Circ. Syst. I Reg. Pap. 2023, 1–4. [Google Scholar] [CrossRef]

- Van der Ziel, A. Flicker noise in electronic devices. In Advances in Electronics and Electron Physics; Academic Press: Cambridge, MA, USA, 1979; Volume 49, pp. 225–297. [Google Scholar]

- Macucci, M.; Marconcini, P. Theoretical comparison between the flicker noise behavior of graphene and of ordinary semiconductors. J. Sens. 2020, 2020, 1–11. [Google Scholar] [CrossRef]

- Yu, Z.; Zhang, J.; Wang, R.; Guo, S.; Liu, C.; Huang, R. New insights into the hot carrier degradation (HCD) in FinFET: New observations, unified compact model, and impacts on circuit reliability. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 7.2. 1–7.2. 4. [Google Scholar]

- Varghese, D.; Alam, M.A.; Weir, B. A generalized, IB-independent, physical HCI lifetime projection methodology based on universality of hot-carrier degradation. In Proceedings of the 2010 IEEE International Reliability Physics Symposium, Anaheim, CA, USA, 2–6 May 2010; pp. 1091–1094. [Google Scholar]

- Randriamihaja, Y.M.; Huard, V.; Federspiel, X.; Zaka, A.; Palestri, P.; Rideau, D.; Roy, D.; Bravaix, A. Microscopic scale characterization and modeling of transistor degradation under HC stress. Microelectron. Reliab. 2012, 52, 2513–2520. [Google Scholar] [CrossRef]

- Yu, Z.; Zhang, Z.; Sun, Z.; Wang, R.; Huang, R. On the trap locations in bulk finFETs after hot carrier degradation (HCD). IEEE Trans. Electron. Dev. 2020, 67, 3005–3009. [Google Scholar] [CrossRef]

- Rahman, A.; Dacuna, J.; Nayak, P.; Leatherman, G.; Ramey, S. Reliability studies of a 10nm high-performance and low-power CMOS technology featuring 3rd generation FinFET and 5th generation HK/MG. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018; pp. 6F. 4-1–6F. 4-6. [Google Scholar]

- Wong, H.; Kakushima, K. On the vertically stacked gate-all-around nanosheet and nanowire transistor scaling beyond the 5 nm technology node. Nanomaterials 2022, 12, 1739. [Google Scholar] [CrossRef] [PubMed]

- Bravaix, A.; Huard, V.; Goguenheim, D.; Vincent, E. Hot-carrier to cold-carrier device lifetime modeling with temperature for low power 40 nm Si-bulk NMOS and PMOS FETs. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 27.5. 1–27.5. 4. [Google Scholar]

- Liu, M.; Zhang, J.; Sun, Z.; Wang, R.; Huang, R. Physics-based Compact Modeling of Statistical Flicker Noise in FinFET Technology. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 18.6. 1–18.6. 4. [Google Scholar]

- Zhang, J.; Zhang, Z.; Wang, R.; Sun, Z.; Zhang, Z.; Guo, S.; Huang, R. Comprehensive Study on the “Anomalous” Complex RTN in Advanced Multi-Fin Bulk FinFET Technology. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 17.3.1–17.3.4. [Google Scholar]

- Grasser, T.; Wagner, P.J.; Reisinger, H.; Aichinger, T.; Pobegen, G.; Nelhiebel, M.; Kaczer, B. Analytic modeling of the bias temperature instability using capture/emission time maps. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 27.4.1–27.4.4. [Google Scholar]

- Goes, W.; Wimmer, Y.; El-Sayed, A.M.; Rzepa, G.; Jech, M.; Shluger, A.L.; Grasser, T. Identification of oxide defects in semiconductor devices: A systematic approach linking DFT to rate equations and experimental evidence. Microelectr. Reliab. 2018, 87, 286–320. [Google Scholar] [CrossRef]

- Grasser, T. Stochastic charge trapping in oxides: From random telegraph noise to bias temperature instabilities. Microelectr. Reliab. 2012, 52, 39–70. [Google Scholar] [CrossRef]

- Sun, Z.; Yu, Z.; Zhang, Z.; Zhang, J.; Wang, R.; Lu, P.; Huang, R. Investigation on the lateral trap distributions in nanoscale MOSFETs during hot carrier stress. IEEE Electron Device Lett. 2019, 40, 490–493. [Google Scholar] [CrossRef]

| Conventional Model | Statistical Model | Statistical Model with Coupling | |

|---|---|---|---|

| Theoretical basis | Number fluctuation theory and mobility fluctuation theory | Inelastic trapping/de-trapping with the assistance of multi-phonons | Inelastic trapping/de-trapping with the assistance of multi-phonons |

| Key factors | Trap energy and trap position | Trap energy, relaxation energy, and amplitude | Trap energy, relaxation energy, and amplitude |

| Method of reflecting variations | Corner model | Monto-Carlo method | Monto-Carlo method |

| Whether to reflect RTN feature | No | Yes | Yes |

| Whether to consider the coupling effect between flicker noise and HCD | No | No | Yes |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, M.; Sun, Z.; Lu, H.; Shen, C.; Zhang, L.; Wang, R.; Huang, R. A Coupling Mechanism between Flicker Noise and Hot Carrier Degradations in FinFETs. Nanomaterials 2023, 13, 1507. https://doi.org/10.3390/nano13091507

Liu M, Sun Z, Lu H, Shen C, Zhang L, Wang R, Huang R. A Coupling Mechanism between Flicker Noise and Hot Carrier Degradations in FinFETs. Nanomaterials. 2023; 13(9):1507. https://doi.org/10.3390/nano13091507

Chicago/Turabian StyleLiu, Minghao, Zixuan Sun, Haoran Lu, Cong Shen, Lining Zhang, Runsheng Wang, and Ru Huang. 2023. "A Coupling Mechanism between Flicker Noise and Hot Carrier Degradations in FinFETs" Nanomaterials 13, no. 9: 1507. https://doi.org/10.3390/nano13091507

APA StyleLiu, M., Sun, Z., Lu, H., Shen, C., Zhang, L., Wang, R., & Huang, R. (2023). A Coupling Mechanism between Flicker Noise and Hot Carrier Degradations in FinFETs. Nanomaterials, 13(9), 1507. https://doi.org/10.3390/nano13091507