Simulation of Capacitorless DRAM Based on the Polycrystalline Silicon Nanotube Structure with Multiple Grain Boundaries

Abstract

:1. Introduction

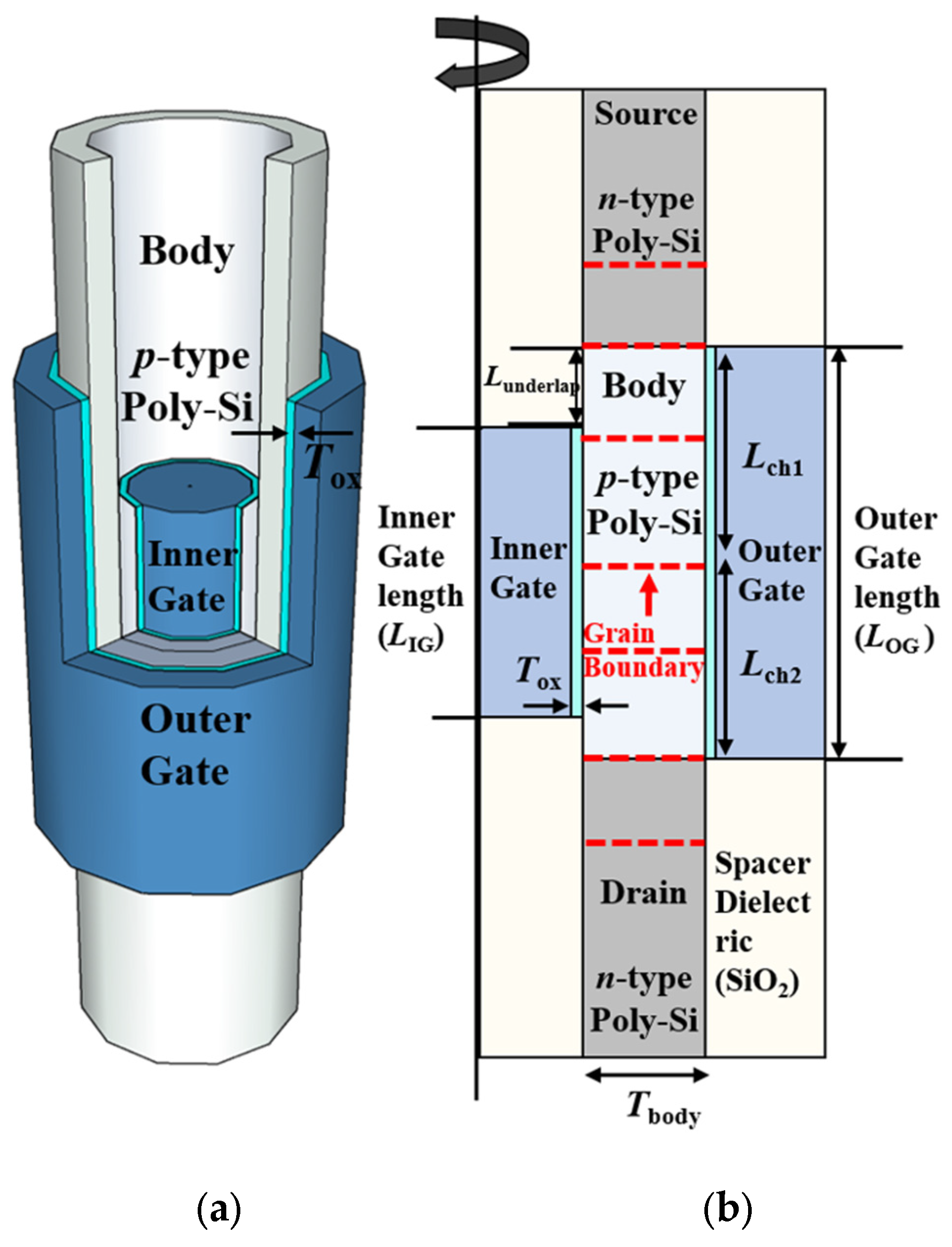

2. Device Structure and Simulation Methodology

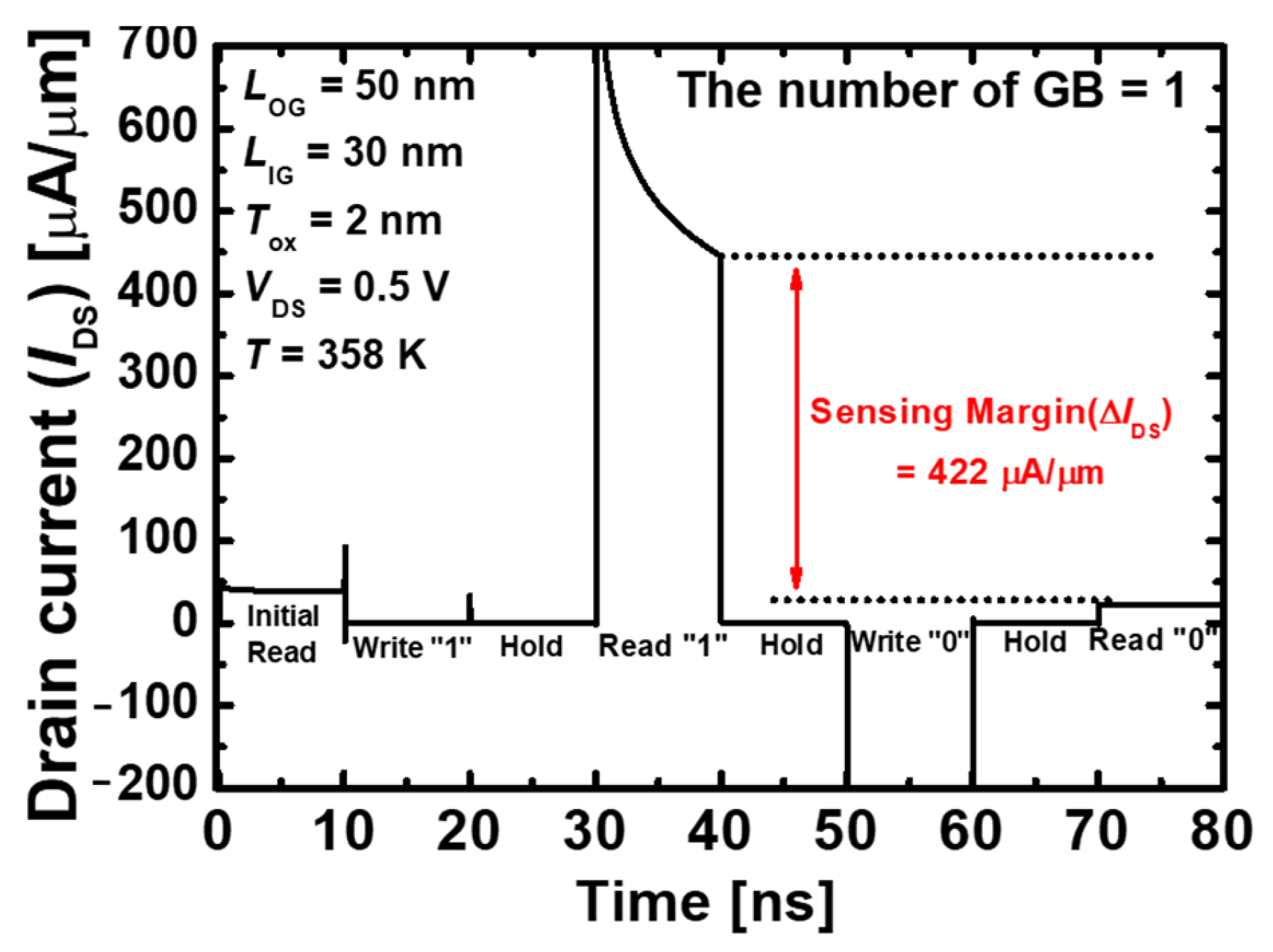

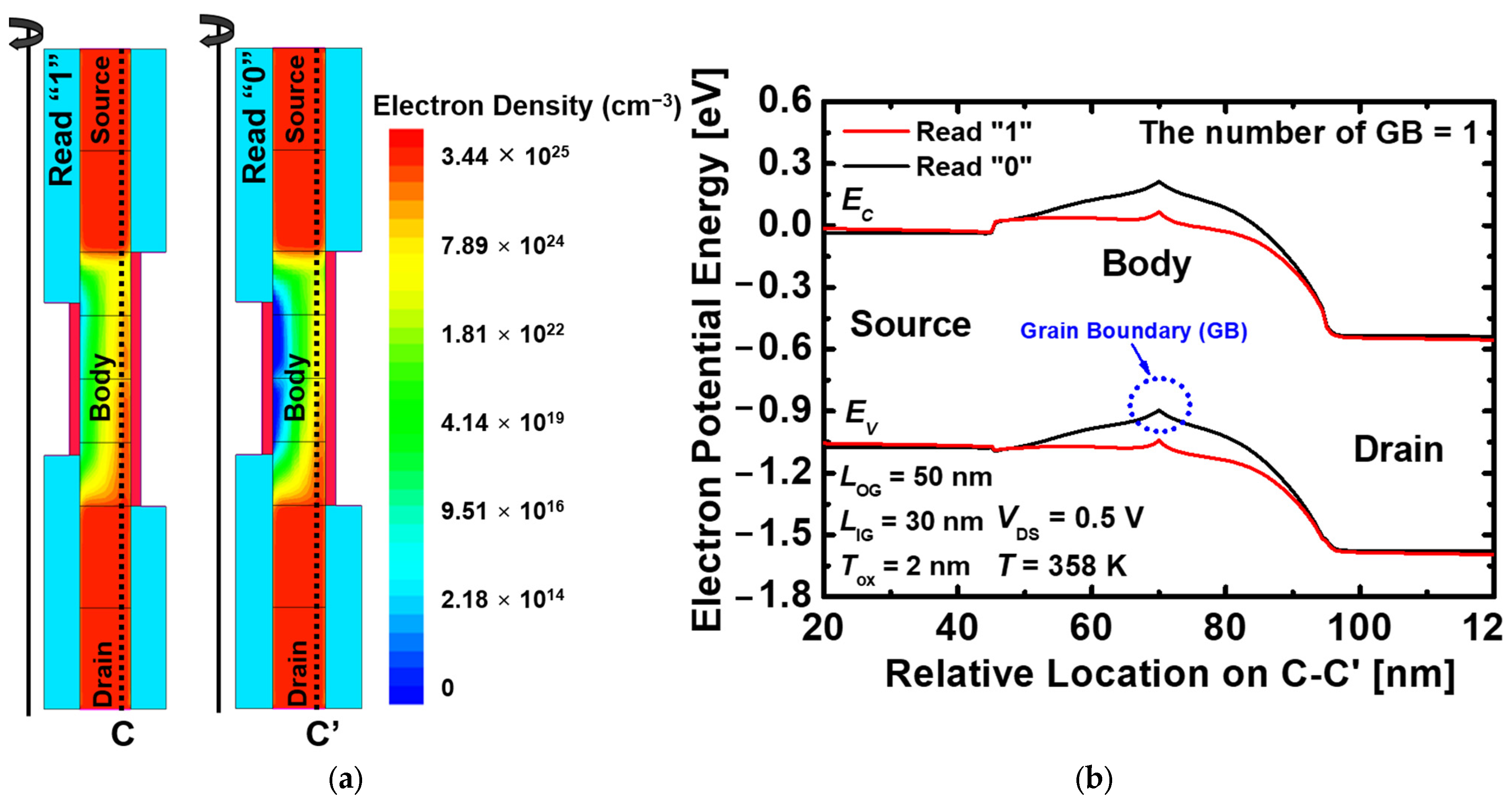

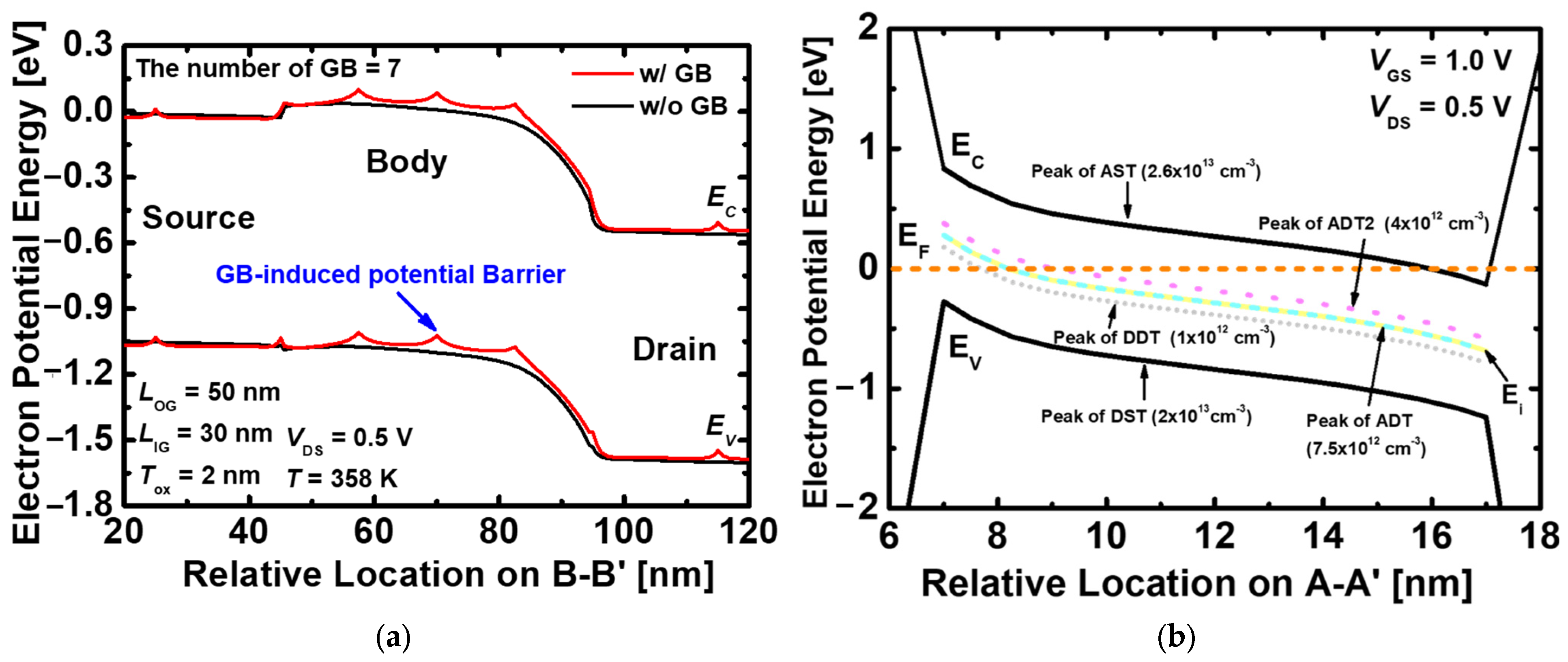

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kim, K.; Hwang, C.-G.; Lee, J.G. DRAM technology perspective for gigabit era. IEEE Trans. Electron. Devices 1998, 45, 598–608. [Google Scholar] [CrossRef]

- Mandelman, J.A.; Dennard, R.H.; Bronner, G.B.; DeBrosse, J.K.; Divakaruni, R.; Li, Y.; Radens, C.J. Challenges and future directions for the scaling of dynamic random-access memory (DRAM). IBM J. Res. Dev. 2002, 46, 187–212. [Google Scholar] [CrossRef]

- Wann, H.-J.; Hu, C. A capacitorless DRAM cell on SOI substrate. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 5–8 December 1993; pp. 635–638. [Google Scholar]

- Lee, W.; Choi, W.Y. A novel capacitorless 1T DRAM cell for data retention time improvement. IEEE Trans. Nanotechnol. 2001, 10, 462–466. [Google Scholar] [CrossRef]

- Yoshida, E.; Tanaka, T. A capacitorless 1T-DRAM technology using gate-induced drain-leakage (GIDL) current for low-power and high-speed embedded memory. IEEE Trans. Electron. Devices 2006, 53, 692–697. [Google Scholar] [CrossRef]

- Song, K.-W.; Jeong, H.; Lee, J.-W.; Hong, S.I.; Tak, N.-K.; Kim, Y.-T.; Choi, Y.L.; Joo, H.S.; Kim, S.H.; Song, H.J.; et al. 55 nm capacitor-less 1T DRAM cell transistor with non-overlap structure. In Proceedings of the 2008 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar]

- Giusi, G.; Iannaccone, G. Junction engineering of 1T-DRAMs. IEEE Electron Dev. Lett. 2013, 34, 408–410. [Google Scholar] [CrossRef]

- Giusi, G.; Alam, M.A.; Crupi, F.; Pierr, S. Bipolar mode operation and scalability of double-gate capacitorless 1T-DRAM cells. IEEE Trans. Electron. Devices 2010, 57, 1748–1750. [Google Scholar] [CrossRef]

- Bawedin, M.; Cristoloveanu, S.; Flandre, D. A capacitorless 1T-DRAM on SOI based on dynamic coupling and double-gate operation. IEEE Electron Dev. Lett. 2008, 29, 795–798. [Google Scholar] [CrossRef]

- Kim, S.; Choi, S.-J.; Moon, D.-I.; Choi, Y.-K. Carrier lifetime engineering for floating-body cell memory. IEEE Trans. Electron. Devices 2012, 59, 367–373. [Google Scholar] [CrossRef]

- Lee, S.H.; Park, J.; Kim, G.U.; Kang, G.E.; Heo, J.H.; Jeon, S.R.; Yoon, Y.J.; Seo, J.H.; Jang, J.; Bae, J.-H.; et al. Bulk-fin field-effect transistor-based capacitorless dynamic random-access memory and its immunity to the work-function variation effect. Jpn. J. Appl. Phys. 2023, 62, SC1016-1–SC1016-6. [Google Scholar] [CrossRef]

- Lee, S.H.; Jang, W.D.; Yoon, Y.J.; Seo, J.H.; Mun, H.J.; Cho, M.S.; Jang, J.; Bae, J.-H.; Kang, I.M. Polycrystalline-Silicon-MOSFET-Based Capacitorless DRAM With Grain Boundaries and Its Performances. IEEE Access 2021, 9, 50281–50290. [Google Scholar] [CrossRef]

- Lee, S.H.; Park, J.; Kim, G.U.; Min, S.R.; Jang, J.; Bae, J.-H.; Lee, S.-H.; Kang, I.M. 3-D stacked polycrystalline-silicon-MOSFET-based capacitorless DRAM with superior immunity to grain-boundary’s influence. Sci. Rep. 2022, 12, 14455. [Google Scholar] [CrossRef]

- An, H.D.; Lee, S.H.; Park, J.; Min, S.R.; Kim, G.U.; Yoon, Y.J.; Seo, J.H.; Cho, M.S.; Jang, J.; Bae, J.-H.; et al. De-sign of a Capacitorless DRAM Based on a Polycrystalline-Silicon Dual-Gate MOSFET with a Fin-Shaped Structure. Nanomaterials 2022, 12, 3526. [Google Scholar] [CrossRef]

- Kim, G.U.; Yoon, Y.J.; Seo, J.H.; Lee, S.H.; Park, J.; Kang, G.E.; Heo, J.H.; Jang, J.; Bae, J.-H.; Lee, S.-H.; et al. Design of a Capacitorless DRAM Based on Storage Layer Separated Using Separation Oxide and Polycrystalline Silicon. Electronics 2022, 11, 3365. [Google Scholar] [CrossRef]

- Park, J.; Cho, M.S.; Lee, S.H.; An, H.D.; Min, S.R.; Kim, G.U.; Yoon, Y.J.; Seo, J.H.; Lee, S.-H.; Jang, J.; et al. Design of Capacitorless DRAM Based on Polycrystalline Silicon Nanotube Structure. IEEE Access 2021, 9, 163675–163685. [Google Scholar] [CrossRef]

- Yoon, Y.J.; Lee, J.S.; Kim, D.-S.; Lee, S.H.; Kang, I.M. One-transistor dynamic random-access memory based on gate-all-around junction-less field-effect transistor with a Si/SiGe heterostructure. Electronics 2020, 9, 2134. [Google Scholar] [CrossRef]

- Yoon, Y.J.; Seo, J.H.; Cho, S.; Lee, J.-H.; Kang, I.M. A polycrystalline-silicon dual-gate MOSFET-based 1T-DRAM using grain boundary-induced variable resistance. Appl. Phys. Lett. 2019, 114, 183503. [Google Scholar] [CrossRef]

- Kim, H.; Yoo, S.; Kang, I.M.; Cho, S.; Sun, W.; Shin, H. Analysis of the Sensing Margin of Silicon and Poly-Si 1T-DRAM. Micromahines 2020, 11, 228. [Google Scholar] [CrossRef] [Green Version]

- Sentaurus Device User Guide Version L-2016.03; Synopsys TCAD Sentaurus: San Jose, CA, USA, 2016.

- Jang, W.D.; Yoon, Y.J.; Cho, M.S.; Jung, J.H.; Lee, S.H.; Jang, J.; Bae, J.-H.; Kang, I.M. Polycrystalline silicon metal-oxide-semiconductor field-effect transistor-based stacked multi-layer one-transistor dynamic random-access memory with double-gate structure for the embedded systems. Jpn. J. Appl. Phys. 2020, 59, SGGB01-1–SGGB01-7. [Google Scholar] [CrossRef]

- Hanna, N.; Hussain, M.M. Si/Ge hetero-structure nanotube tunnel field effect transistor. J. Appl. Phys. 2015, 117, 014310. [Google Scholar] [CrossRef] [Green Version]

- Sahay, S.; Kuma, M.J. Nanotube junctionless FET: Proposal, design, and investigation. IEEE Trans. Electron. Devices 2017, 64, 1851–1856. [Google Scholar] [CrossRef]

- Tekleab, D.; Tran, H.H.; Slight, J.W.; Chidambarrao, D. Silicon Nanotube MOSFET. U.S. Patent 0217468, 30 August 2012. [Google Scholar]

- Fahad, H.M.; Smith, C.E.; Rojas, J.P.; Hussain, M.M. Silicon nanotube field effect transistor with core–shell gate stacks for enhanced high-performance operation and area scaling benefits. Nano Lett. 2011, 11, 4393–4399. [Google Scholar] [CrossRef] [PubMed]

- Tiwari, P.K.; Samoju, V.R.; Sunkara, T.; Dubey, S.; Jit, S. Analytical modeling of threshold voltage for symmetrical silicon nano-tube field-effect-transistors (Si-NT FETs). J. Comput. Electron. 2016, 15, 516–524. [Google Scholar] [CrossRef]

- Ho, C.H.; Panagopoulos, G.; Roy, K. A Physical Model for Grain-Boundary-Induced Threshold Voltage Variation in Polysilicon Thin-Film Transistors. IEEE Trans. Electron. Devices 2012, 59, 2396–2402. [Google Scholar] [CrossRef]

- Ranica, R.; Villaret, A.; Fenouillet-Beranger, C.; Malinge, P.; Mazoyer, P.; Masson, P.; Delille, D.; Charbuillet, C.; Candelier, P.; Skotnicki, T. A capacitor-less DRAM cell on 75 nm gate length, 16 nm thin Fully Depleted SOI device for high density embedded memories. In Proceedings of the IEDM Technical Digest. IEEE International Electron Devices Meeting, San Francisco, CA, USA, 13–15 December 2004; pp. 277–280. [Google Scholar]

- Yoon, S.; Kim, K.; Cho, H.; Yoon, J.-S.; Lee, M.J.; Meyyappan, M.; Baek, C.-K. Polysilicon near-infrared photodetector with performance comparable to crystalline silicon devices. Opt. Express 2017, 25, 32910–32918. [Google Scholar] [CrossRef]

- Kimura, M.; Inoue, S.; Shimoda, T.; Sameshima, T. Device simulation of carrier transport through grain boundaries in lightly doped polysilicon films and dependence on dopant density. Jpn. J. Appl. Phys. 2001, 40, 5237–5243. [Google Scholar] [CrossRef] [Green Version]

- Troutman, R.R. VLSI limitations from drain-induced barrier lowering. IEEE J. Solid-State Circuits 1979, 14, 383–391. [Google Scholar] [CrossRef]

- Sajjad, R.N.; Chern, W.; Hoyt, J.L.; Antoniadis, D.A. Trap assisted tunneling and its effect on subthreshold swing of tunnel FETs. IEEE Trans. Electron. Devices 2016, 63, 4380–4387. [Google Scholar] [CrossRef]

- Ansari MH, R.; Cho, S. Performance Improvement of 1T DRAM by Raised Source and Drain Engineering. IEEE Trans. Electron. Devices 2021, 68, 1577–1584. [Google Scholar] [CrossRef]

- Ansari, M.H.R.; Navlakha, N.; Lee, J.Y.; Cho, S. Double-gate junctionless 1T DRAM with physical barriers for retention improvement. IEEE Trans. Electron. Devices 2020, 67, 1471–1479. [Google Scholar] [CrossRef]

- James, A.; Saurabh, S. Dopingless 1T DRAM: Proposal, design, and analysis. IEEE Access 2019, 7, 88960–88969. [Google Scholar] [CrossRef]

- More Moore, 2021 International Roadmap for Devices and Systems (IRDS™) Edition. 2021. Available online: https://irds.ieee.org/editions/2021 (accessed on 1 September 2022).

| Parameters | Values |

|---|---|

| Outer gate length (LOG) | 50 nm |

| Inner gate length (LIG) | 30 nm |

| Underlap length (Lunderlap) | 10 nm |

| Body thickness (Tbody) | 10 nm |

| Gate dielectric (HfO2) thickness (Tox) | 2 nm |

| Source/Drain doping concentration | n-type 5 × 1019 cm−3 |

| Body doping concentration | p-type 1 × 1017 cm−3 |

| Outer gate work function | 4.8 eV |

| Inner gate work function | 5.2 eV |

| Operation | Program (Write “1”) | Erase (Write “0”) | Read | Hold |

|---|---|---|---|---|

| Outer gate voltage [V] | 2.0 | 0.0 | 1.0 | 0.0 |

| Inner gate voltage [V] | −2.0 | 0.0 | 0.0 | −0.5 |

| Drain voltage [V] | 0.0 | −1.0 | 0.5 | 0.0 |

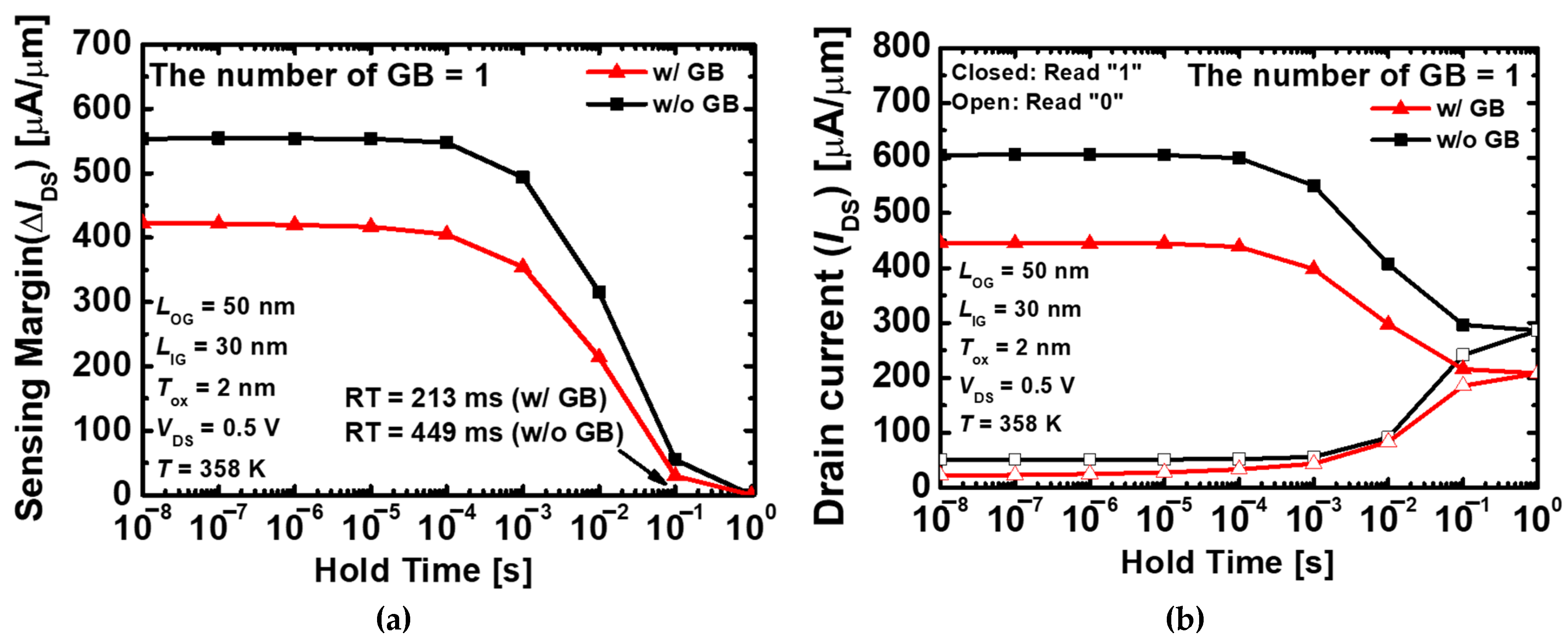

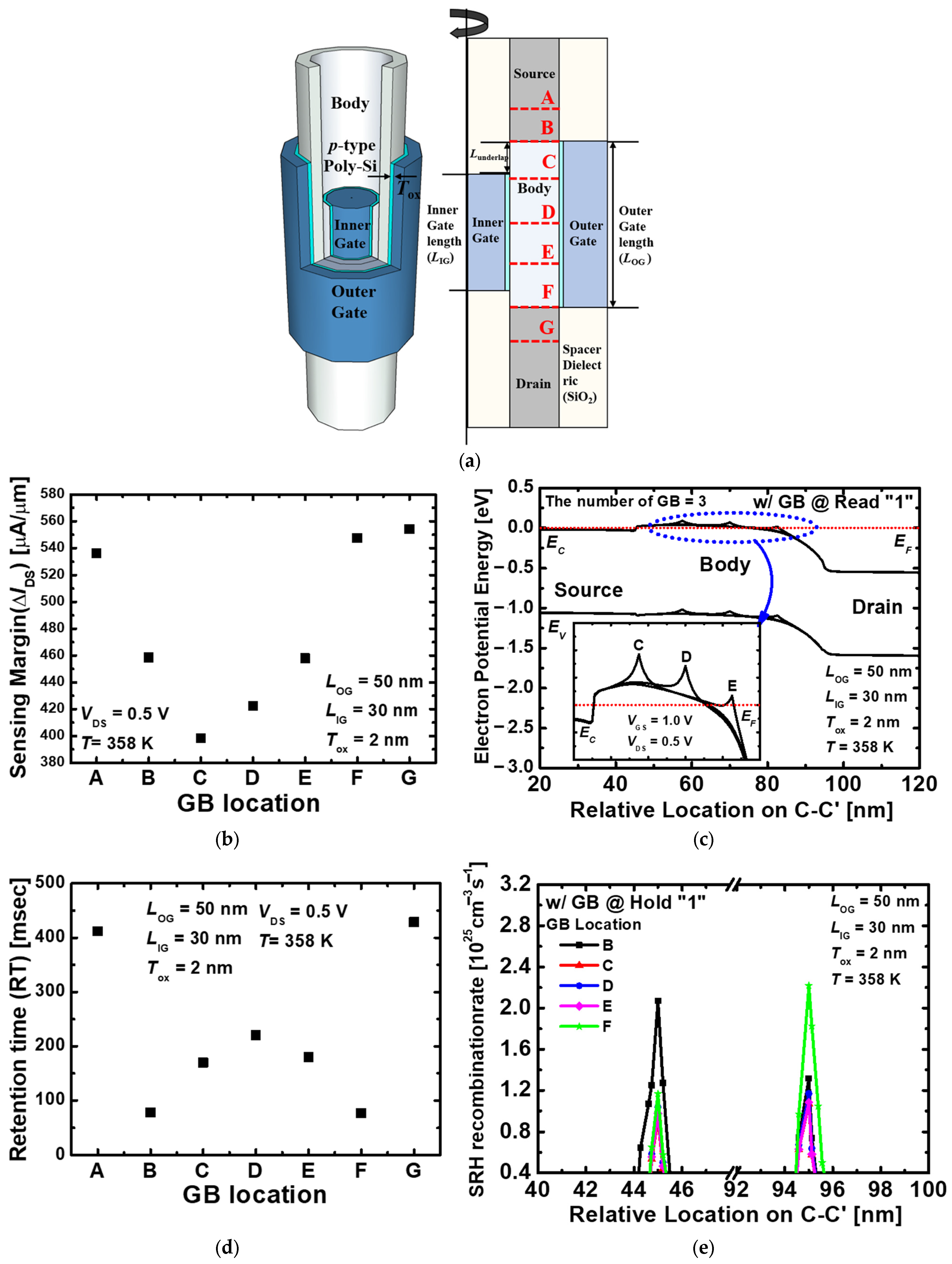

| GB Location | A | B | C | D | E | F | G | w/o GB |

|---|---|---|---|---|---|---|---|---|

| Sensing margin [μA/μm] | 536 | 458 | 398 | 422 | 458 | 547 | 554 | 556 |

| Retention time [ms] | 412 | 78 | 170 | 213 | 180 | 77 | 429 | 449 |

| No. | Reference | Sensing Margin [µA/µm] | Retention Time [ms] |

|---|---|---|---|

| 1 | [14] | 2.51 | 598 |

| 2 | [15] | 14.10 | 251 |

| 3 | [17] | 0.39 | 10 |

| 4 | [33] | 11.7 | 148 |

| 5 | [34] | 2.5 | 33 |

| 6 | [35] | 12 | 170 |

| 7 | This work (w/o GB) | 422 | 213 |

| 8 | This work (w/GB) | 554 | 449 |

| Groups | Number of Samples |

|---|---|

| (A), (B), (C), (D), (E), (F), (G) | 7 |

| (AB), (AC), (AD)…(FG) | 21 |

| (ABC), (ABD), (ABE)…(EFG) | 35 |

| (ABCD), (ABCE)…(DEFG) | 35 |

| (ABCDE), (ABCDF)…(CDEFG) | 21 |

| (ABCDEF), (ABCDEG)…(BCDEFG) | 7 |

| (ABCDEFG) | 1 |

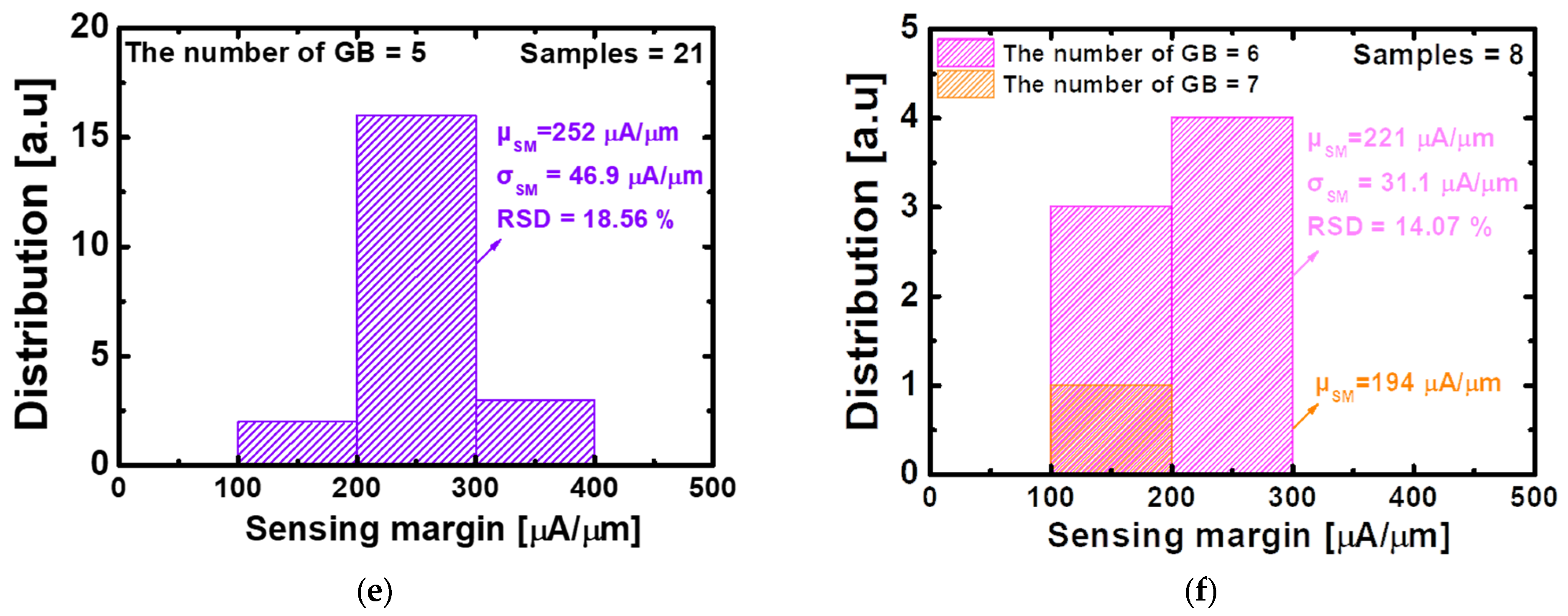

| GB Number | 1 | 2 | 3 | 4 | 5 | 6 | 7 | |

|---|---|---|---|---|---|---|---|---|

| Mean | 482 | 405 | 333 | 292 | 252 | 221 | 194 | |

| Sensing margin [μA/μm] | SD | 63.5 | 94.4 | 85.8 | 63.4 | 46.9 | 31.1 | X |

| RSD | 13.17% | 23.27% | 25.7% | 21.68% | 18.56% | 14.07% | X | |

| Mean | 223 | 127 | 91 | 70 | 60 | 54 | 50.4 | |

| Retention time [ms] | SD | 144 | 92 | 47 | 14 | 8 | 4 | X |

| RSD | 64.53% | 72.09% | 52.2% | 20.87% | 13.27% | 8.82% | X |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, J.; Lee, S.-H.; Kang, G.-E.; Heo, J.-H.; Jeon, S.-R.; Kim, M.-S.; Bae, S.-J.; Hong, J.-W.; Jang, J.-w.; Bae, J.-H.; et al. Simulation of Capacitorless DRAM Based on the Polycrystalline Silicon Nanotube Structure with Multiple Grain Boundaries. Nanomaterials 2023, 13, 2026. https://doi.org/10.3390/nano13132026

Park J, Lee S-H, Kang G-E, Heo J-H, Jeon S-R, Kim M-S, Bae S-J, Hong J-W, Jang J-w, Bae J-H, et al. Simulation of Capacitorless DRAM Based on the Polycrystalline Silicon Nanotube Structure with Multiple Grain Boundaries. Nanomaterials. 2023; 13(13):2026. https://doi.org/10.3390/nano13132026

Chicago/Turabian StylePark, Jin, Sang-Ho Lee, Ga-Eon Kang, Jun-Hyeok Heo, So-Ra Jeon, Min-Seok Kim, Seung-Ji Bae, Jeong-Woo Hong, Jae-won Jang, Jin-Hyuk Bae, and et al. 2023. "Simulation of Capacitorless DRAM Based on the Polycrystalline Silicon Nanotube Structure with Multiple Grain Boundaries" Nanomaterials 13, no. 13: 2026. https://doi.org/10.3390/nano13132026

APA StylePark, J., Lee, S.-H., Kang, G.-E., Heo, J.-H., Jeon, S.-R., Kim, M.-S., Bae, S.-J., Hong, J.-W., Jang, J.-w., Bae, J.-H., Lee, S.-H., & Kang, I.-M. (2023). Simulation of Capacitorless DRAM Based on the Polycrystalline Silicon Nanotube Structure with Multiple Grain Boundaries. Nanomaterials, 13(13), 2026. https://doi.org/10.3390/nano13132026