Resistive Switching Memory Cell Property Improvement by Al/SrZrTiO3/Al/SrZrTiO3/ITO with Embedded Al Layer

Abstract

:1. Introduction

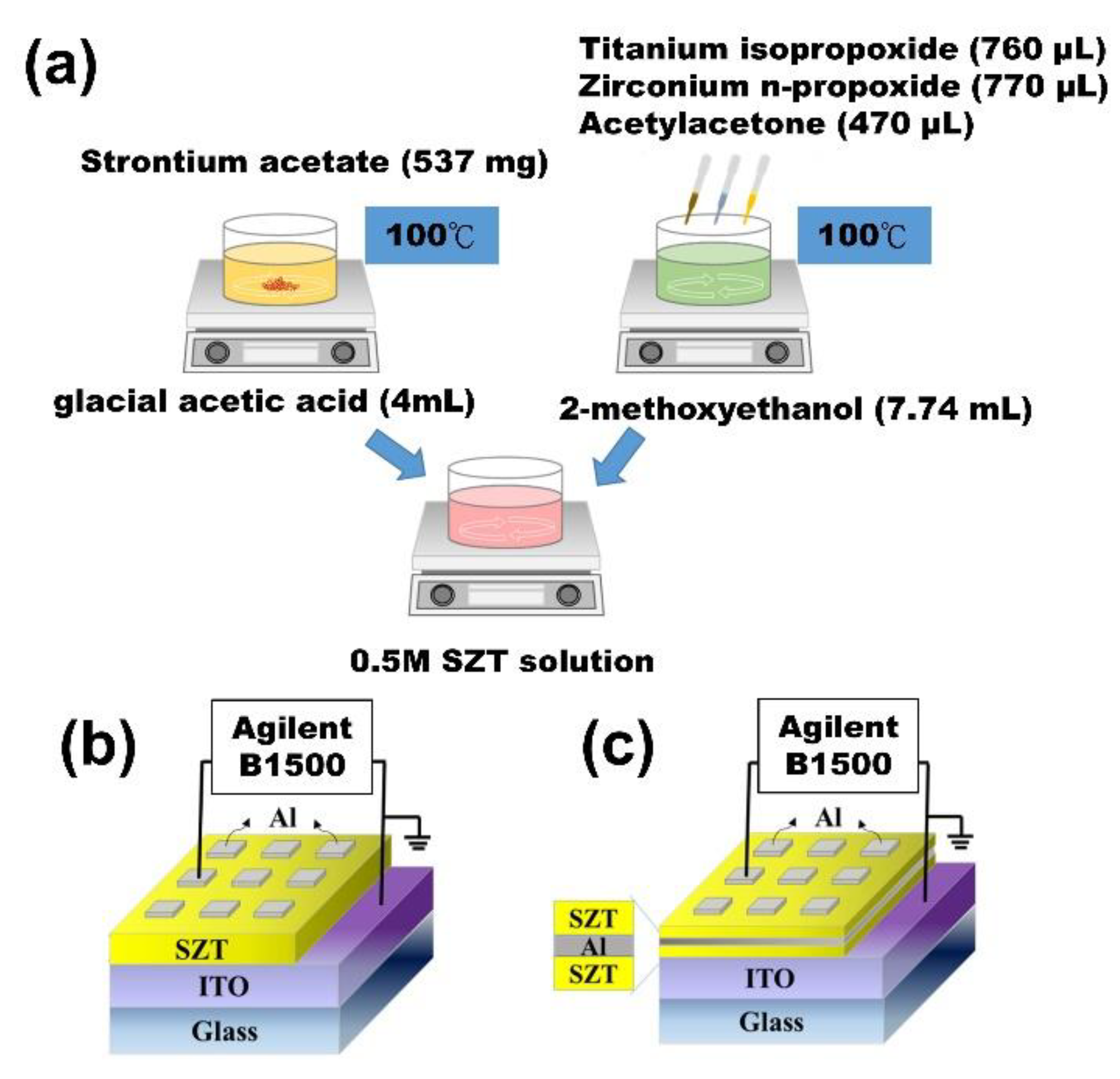

2. Materials and Methods

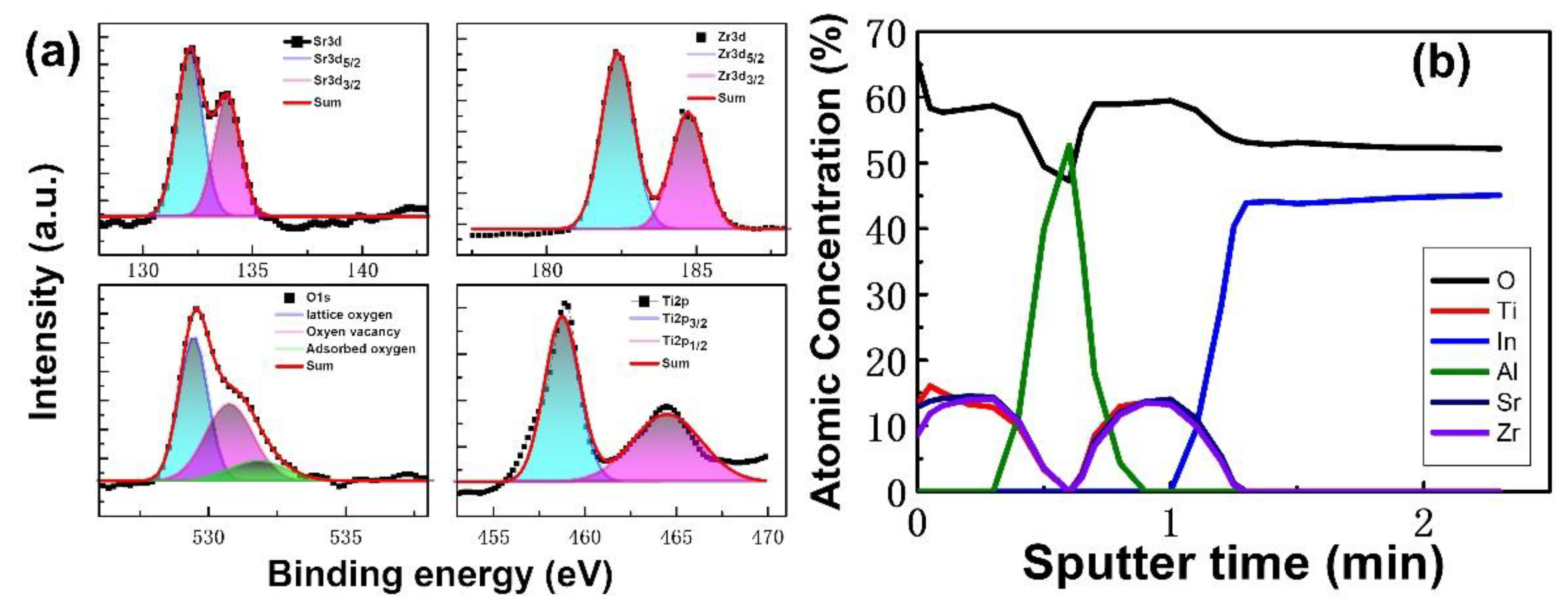

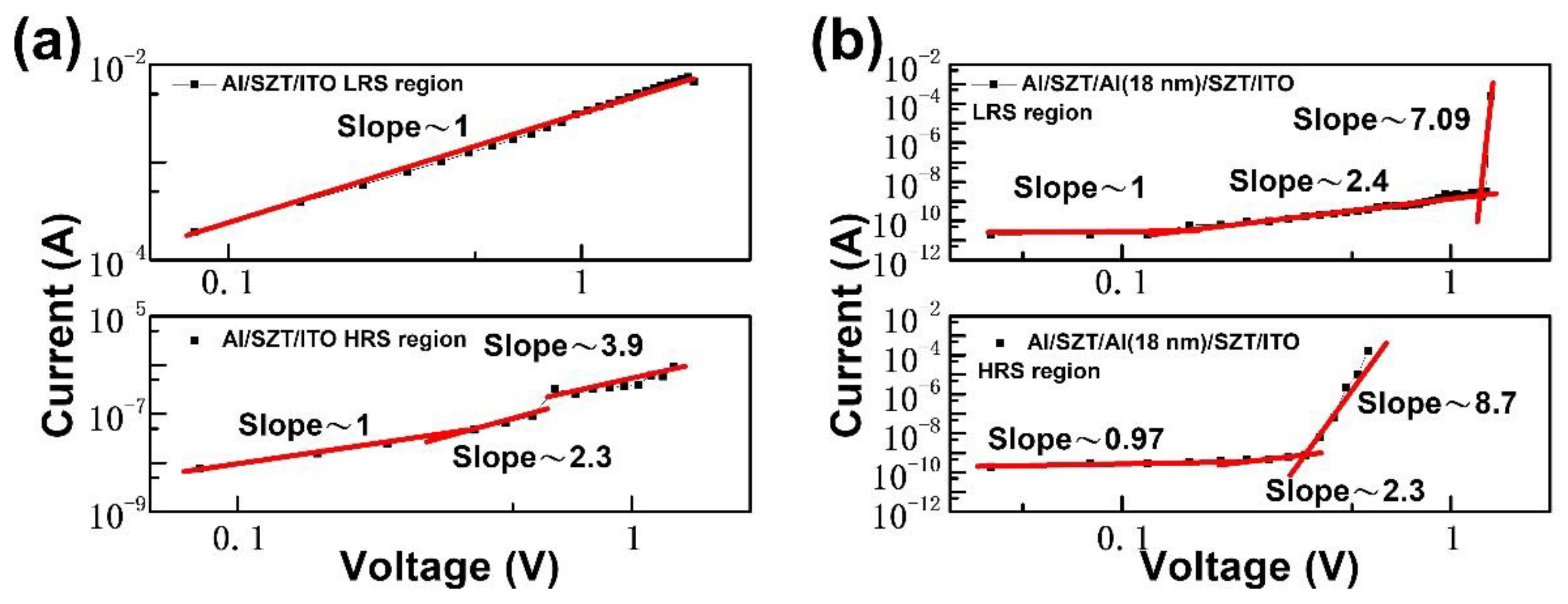

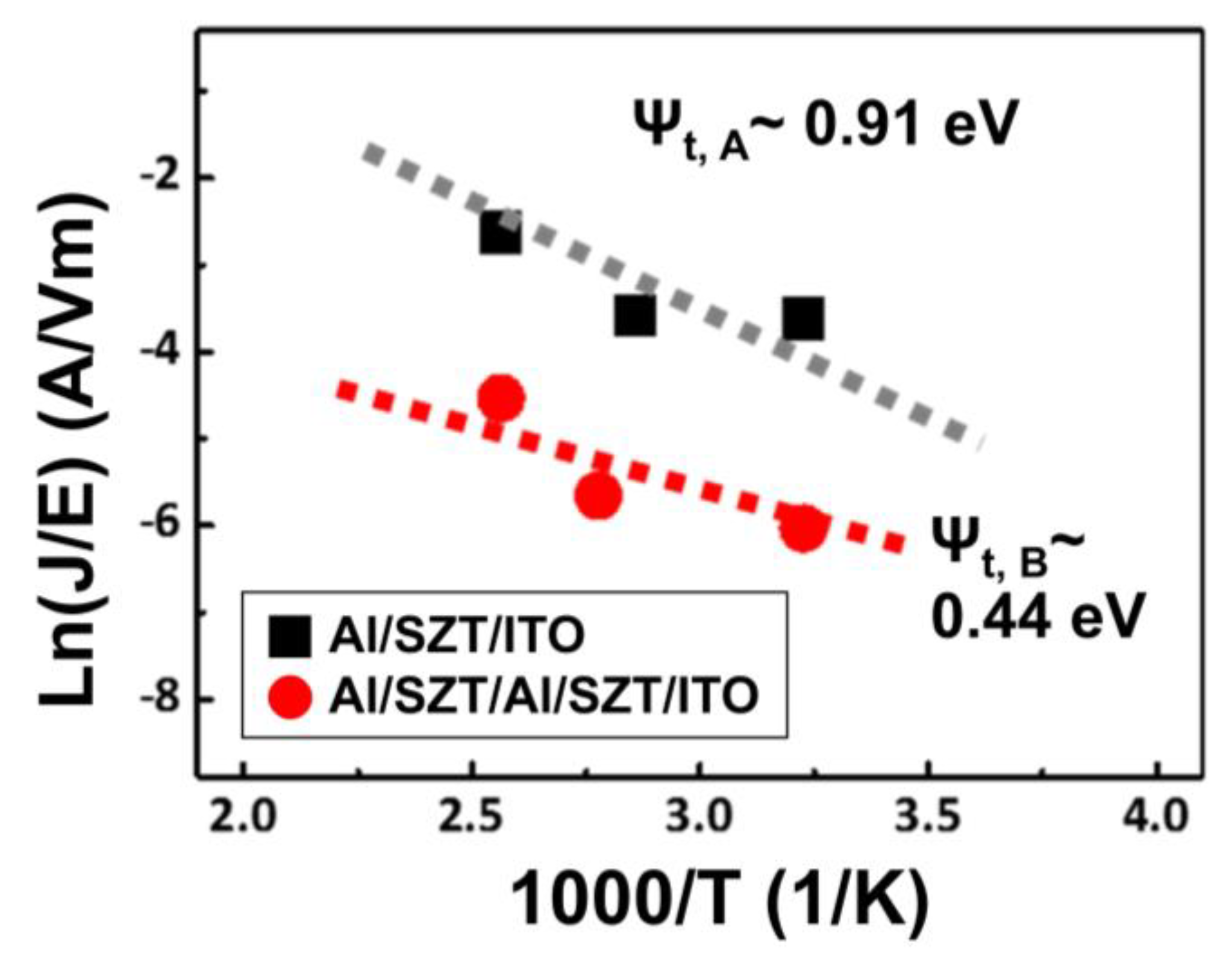

3. Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Muhamad, N.F.; Osman, R.A.M.; Idris, M.S.; Yasin, M.N.M. Physical and electrical properties of SrTiO3 and SrZrO3. EPJ Web Conf. 2017, 162, 01052. [Google Scholar] [CrossRef] [Green Version]

- Muhamad, N.F.; Osman, R.A.M.; Idris, M.S.; Jamlos, F.; Hambali, N.A.M.A. Microwave and Electrical Properties of Zr-Doped SrTiO3 for Dielectric Resonator Antenna Application. Solid State Phenom. 2018, 280, 142–148. [Google Scholar] [CrossRef]

- Lee, K.-J.; Chang, Y.-C.; Lee, C.-J.; Wang, L.-W.; Chou, D.-W.; Chiang, T.-K.; Wang, Y.-H. Effects of Ni in Strontium Titanate Nickelate Thin Films for Flexible Nonvolatile Memory Applications. IEEE Trans. Electron Devices 2017, 64, 2001–2007. [Google Scholar] [CrossRef]

- Chen, G.; Zhang, P.; Pan, L.; Qi, L.; Yu, F.; Gao, C. Flexible nonvolatile resistive memory devices based on SrTiO3 nanosheets and polyvinylpyrrolidone composites. J. Mater. Chem. C 2017, 5, 9799–9805. [Google Scholar] [CrossRef]

- Padmini, E.; Ramachandran, K. Electrical properties of Mo-doped SrTiO3 prepared by solid state reaction method. Mater. Res. Express 2019, 6, 115919. [Google Scholar] [CrossRef]

- Zhang, W.; Wang, H.; Xu, J.; Liu, G.; Xie, H.; Yang, L. Effects of Mg Doping Concentration on Resistive Switching Behavior and Properties of SrTi1-yMgyO3 Films. J. Wuhan Univ. Technol.-Mater. Sci. Ed. 2019, 34, 888–892. [Google Scholar] [CrossRef]

- Zhang, T.F.; Tang, X.G.; Liu, Q.X.; Jiang, Y.P. Electrode effect regulated resistance switching and selector characteristics in Nb doped SrTiO3 single crystal for potential cross-point memory applications. J. Alloys Compd. 2018, 730, 516–520. [Google Scholar] [CrossRef]

- Bera, J.; Rout, S.K. SrTiO3–SrZrO3 solid solution: Phase formation kinetics and mechanism through solid-oxide reaction. Mater. Res. Bull. 2005, 40, 1187–1193. [Google Scholar] [CrossRef]

- Wei, C.Y.; Huang, W.C.; Yang, C.K.; Chang, Y.Y.; Wang, Y.H. Low-operating-voltage pentacene-based transistors and inverters with solution-processed barium zirconate titanate insulators. IEEE Electron Device Lett. 2011, 32, 1755–1757. [Google Scholar] [CrossRef]

- Lee, K.-J.; Wang, Y.-H. Effect of Alkaline Earth Metal on AZrOx (A = Mg, Sr, Ba) Memory Application. Gels 2022, 8, 20. [Google Scholar] [CrossRef]

- Yang, Y.C.; Pan, F.; Zeng, F.; Liu, M. Switching mechanism transition induced by annealing treatment in nonvolatile Cu/ZnO/Cu/ZnO/Pt resistive memory: From carrier trapping/detrapping to electrochemical metallization. J. Appl. Phys. 2009, 106, 123705-1–123705-5. [Google Scholar] [CrossRef]

- Chung, Y.L.; Lai, Y.; Chen, Y.C.; Chen, J.S. Schottky barrier mediated single-polarity resistive switching in Pt layer-included TiOx memory device. ACS Appl. Mater. Interfaces 2011, 3, 1918–1924. [Google Scholar] [CrossRef] [PubMed]

- Lee, D.; Sung, Y.; Lee, I.; Kim, J.; Sohn, H.; Ko, D.H. Enhanced bipolar resistive switching of HfO2 with a Ti interlayer. Appl. Phys. A 2011, 102, 997–1001. [Google Scholar] [CrossRef]

- Liu, Q.; Long, S.; Wang, W.; Zuo, Q.; Zhang, S.; Chen, J.; Liu, M. Improvement of resistive switching properties in ZrO2-based ReRAM with implanted Ti ions. IEEE Electron Device Lett. 2009, 30, 1335–1337. [Google Scholar] [CrossRef]

- Ruth, E.; McKnight, A.; Kennedy, B.J.; Zhou, Q.; Carpenter, M.A. Elastic anomalies associated with transformation sequences in perovskites: II. The strontium zirconate–titanate Sr (Zr, Ti)O3 solid solution series. J. Phys. Condens. Matter 2008, 21, 015902. [Google Scholar] [CrossRef] [Green Version]

- Dixit, D.; Agrawal, C.; Mohapatra, Y.N.; Majumder, S.B.; Katiyar, R.S. Studies on the dielectric and relaxor behavior of sol–gel derived barium strontium zirconate titanate thin films. Mater. Lett. 2007, 61, 3685–3688. [Google Scholar] [CrossRef]

- Huang, S.; Lee, K.-J.; Wang, Y.-H. Magnesium Zirconate Titanate Thin Films Used as an NO2 Sensing Layer for Gas Sensor Applications Developed Using a Sol–Gel Method. Sensors 2021, 21, 2825. [Google Scholar] [CrossRef] [PubMed]

- Avilés, M.A.; Córdoba, J.M.; Sayagués, M.J.; Gotor, F.J. Mechanochemical synthesis of Ti1−xZrxB2 and Ti1−xHfxB2 solid solutions. J. Phys. Chem. B 1998, 102, 5094–5098. [Google Scholar] [CrossRef]

- Victor, S.B. Krupanidhi, Impact of microstructure on electrical characteristics of laser ablation grown ZrTiO4 thin films on Si substrate. J. Phys. D. Appl. Phys 2005, 38, 41–50. [Google Scholar] [CrossRef]

- Praveen, T.; Rose, T.P.; Saji, K.J. Top electrode dependent resistive switching in M/ZnO/ITO memristors, M = Al, ITO, Cu, and Au. Microelectron. J. 2022, 121, 105388. [Google Scholar] [CrossRef]

- Zhang, W.; Kong, Z.J.; Cao, Y.Z.; Li, D.A.; Wang, G.L.; Zhu, L.; Li, X.; Cao, Y.-Q.; Wu, D. Bipolar Resistive Switching Characteristics of HfO2/TiO2/HfO2 Trilayer-Structure RRAM Devices on Pt and TiN-Coated Substrates Fabricated by Atomic Layer Deposition. Nanoscale Res. Lett. 2017, 12, 393. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Saleem, F.; Simanjuntak, M.; Chandrasekaran, S.; Rajasekaran, S.; Tseng, T.-Y.; Prodromakis, T. Transformation of digital to analog switching in TaOx-based memristor device for neuromorphic applications. Appl. Phys. Lett. 2021, 118, 112103. [Google Scholar] [CrossRef]

- Lampert, M.A. Simplified Theory of Space-Charge-Limited Currents in an Insulator with Traps. Phys. Rev. J. Arch. 1956, 103, 1648. [Google Scholar] [CrossRef]

- Chiu, F.C. A review on conduction mechanisms in dielectric films. Adv. Mater. Sci. Eng. 2014, 2014, 1–18. [Google Scholar] [CrossRef] [Green Version]

- Wang, Z.S.; Zeng, F.; Yang, J.; Chen, C.; Yang, Y.C.; Pan, F. Reproducible and controllable organic resistive memory based on Al/poly(3,4-ethylene-dioxythiophene):poly(styrenesulfonate)/Al structure. Appl. Phys. Lett. 2010, 97, 253301. [Google Scholar] [CrossRef]

- Yang, Y.C.; Pan, F.; Liu, Q.; Liu, M.; Zeng, F. Fully Room-Temperature-Fabricated Nonvolatile Resistive Memory for Ultrafast and High-Density Memory Application. Nano Lett. 2009, 9, 1636–1643. [Google Scholar] [CrossRef]

- Park, K.H.; Jung, J.H.; Li, F.; Son, D.I.; Kim, T.W. Carrier transport mechanisms of nonvolatile memory devices based on nanocomposites consisting of ZnO nanoparticles with polymethylmethacrylate nanocomposites sandwiched between two C60 layers. Appl. Phys. Lett. 2008, 93, 132104. [Google Scholar] [CrossRef]

- Sedghi, N.; Davey, W.; Mitrovic, I.Z.; Hall, S. Design and focused ion beam fabrication of single crystal diamond nanobeam cavities. J. Vac. Sci. Technol. 2011, B29, 01AB10. [Google Scholar] [CrossRef]

- Ryu, S.W.; Cho, S.; Park, J.; Kwac, J.; Kim, H.J.; Nishi, Y. Effects of ZrO2 doping on HfO2 resistive switching memory characteristics. Appl. Phys. Lett. 2014, 105, 072102. [Google Scholar] [CrossRef]

- Chen, L.; Dai, Y.W.; Sun, Q.Q.; Guo, J.J.; Zhou, P.; Zhang, D.W. Al2O3/HfO2 functional stack films based resistive switching memories with controlled SET and RESET voltages. Solid State Ion. 2015, 273, 66–69. [Google Scholar] [CrossRef]

- Wong, H.S.; Lee, H.Y.; Yu, S.; Chen, Y.S.; Wu, Y.; Chen, S.; Lee, B.; Chen, F.T.; Tsai, M.J. Metal-oxide RRAM. Proc. IEEE 2012, 100, 1951–1970. [Google Scholar] [CrossRef]

| Insulator Material | Insert Metal | Fabrication of the Insulator | Fabrication of the Insert Metal | Resistance Ratio | Vest (V) | Vreset (V) | Current of HRS (A) | Ref |

|---|---|---|---|---|---|---|---|---|

| ZnO | Cu | Sputter | Sputter | 104 | 0.9 | −0.6 | 10−4 | [11] |

| TiOx | Pt | Thermal oxidation | -- | 105 | 3.7 | −0.9 | 10−8 | [12] |

| HfO2 | Ti | Sputter | Sputter | 50 | 0.7 | −1.3 | 10−3 | [13] |

| ZrO2 | Ti | Electron-beam evaporation | Implant | 104 | 1.3 | −0.66 | 10−9 | [14] |

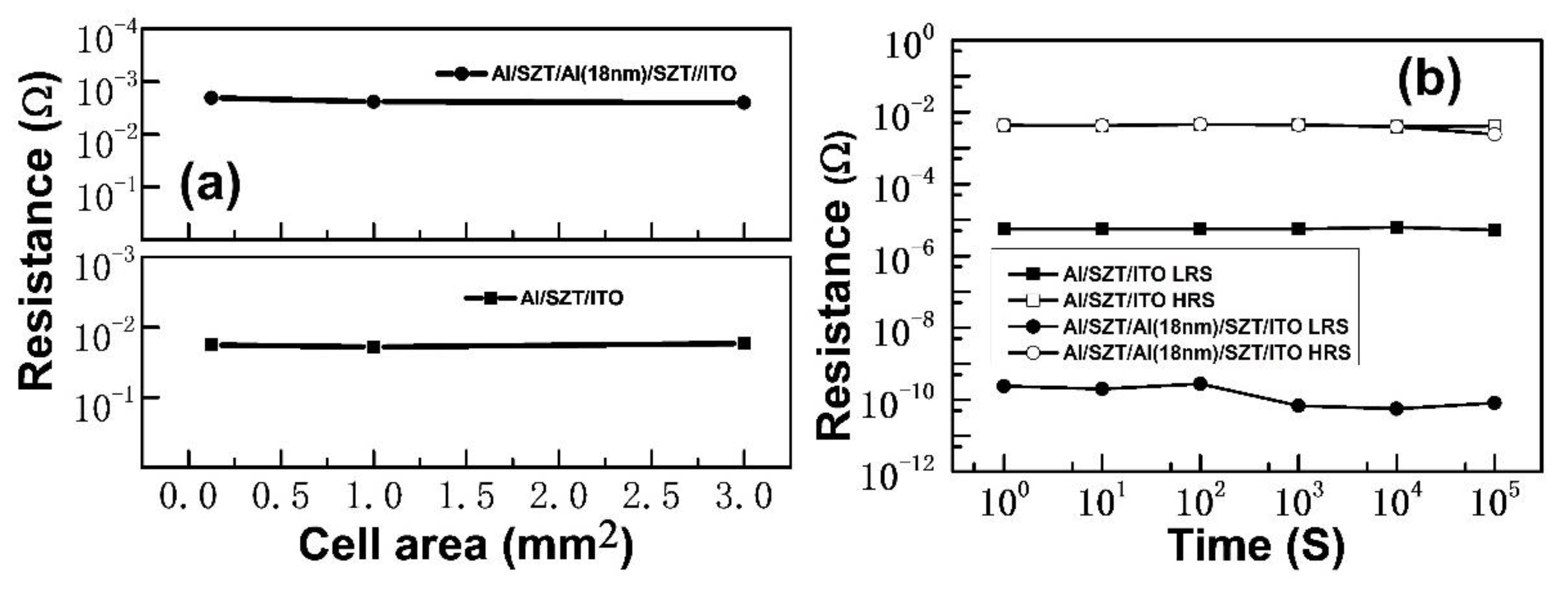

| SZT | -- | Sol-gel | Sputter | 103 | −1.28 | 2.08 | 10−8 | This work |

| SZT | Al | Sol-gel | Sputter | 107 | −0.32 | 1.28 | 10−10 | This work |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, K.-J.; Lin, W.-S.; Wang, L.-W.; Lin, H.-N.; Wang, Y.-H. Resistive Switching Memory Cell Property Improvement by Al/SrZrTiO3/Al/SrZrTiO3/ITO with Embedded Al Layer. Nanomaterials 2022, 12, 4412. https://doi.org/10.3390/nano12244412

Lee K-J, Lin W-S, Wang L-W, Lin H-N, Wang Y-H. Resistive Switching Memory Cell Property Improvement by Al/SrZrTiO3/Al/SrZrTiO3/ITO with Embedded Al Layer. Nanomaterials. 2022; 12(24):4412. https://doi.org/10.3390/nano12244412

Chicago/Turabian StyleLee, Ke-Jing, Wei-Shao Lin, Li-Wen Wang, Hsin-Ni Lin, and Yeong-Her Wang. 2022. "Resistive Switching Memory Cell Property Improvement by Al/SrZrTiO3/Al/SrZrTiO3/ITO with Embedded Al Layer" Nanomaterials 12, no. 24: 4412. https://doi.org/10.3390/nano12244412

APA StyleLee, K.-J., Lin, W.-S., Wang, L.-W., Lin, H.-N., & Wang, Y.-H. (2022). Resistive Switching Memory Cell Property Improvement by Al/SrZrTiO3/Al/SrZrTiO3/ITO with Embedded Al Layer. Nanomaterials, 12(24), 4412. https://doi.org/10.3390/nano12244412