Recent Progress in Contact Engineering of Field-Effect Transistor Based on Two-Dimensional Materials

Abstract

1. Introduction

2. Fermi-Level Pinning

2.1. Fermi-Level Pinning and Pinning Factor

2.2. Origins of Fermi-Level Pinning

3. Contact Engineering of 2D FETs

3.1. Top Contact Engineering

3.1.1. Bulk Metals

3.1.2. Bulk Semimetals

3.1.3. Two-Dimensional Metals/Semimetals

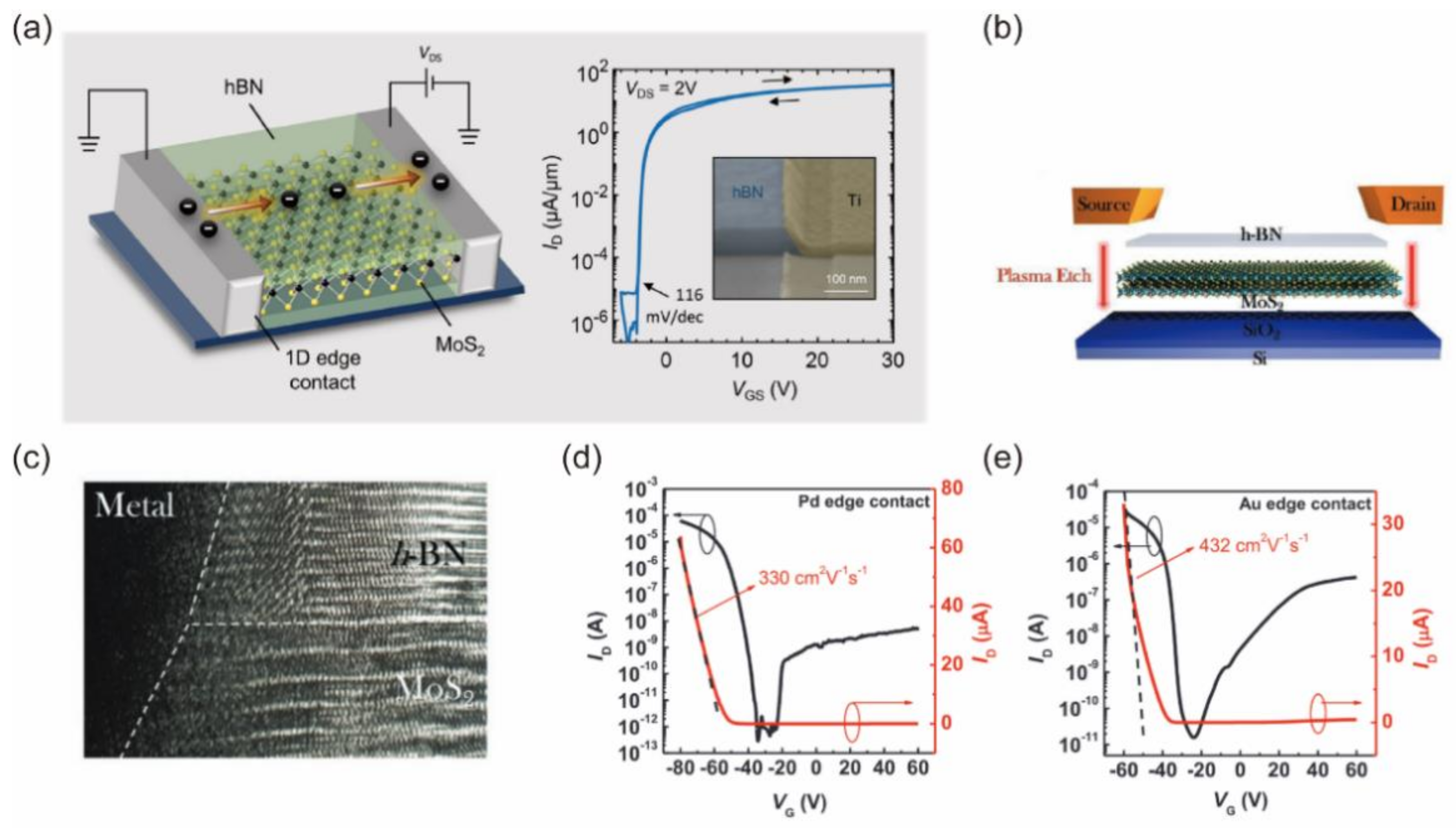

3.2. Edge Contact Engineering

3.2.1. Plasma Etching and Metallization

3.2.2. Phase Engineering and Degenerate Doping of 2D Layers

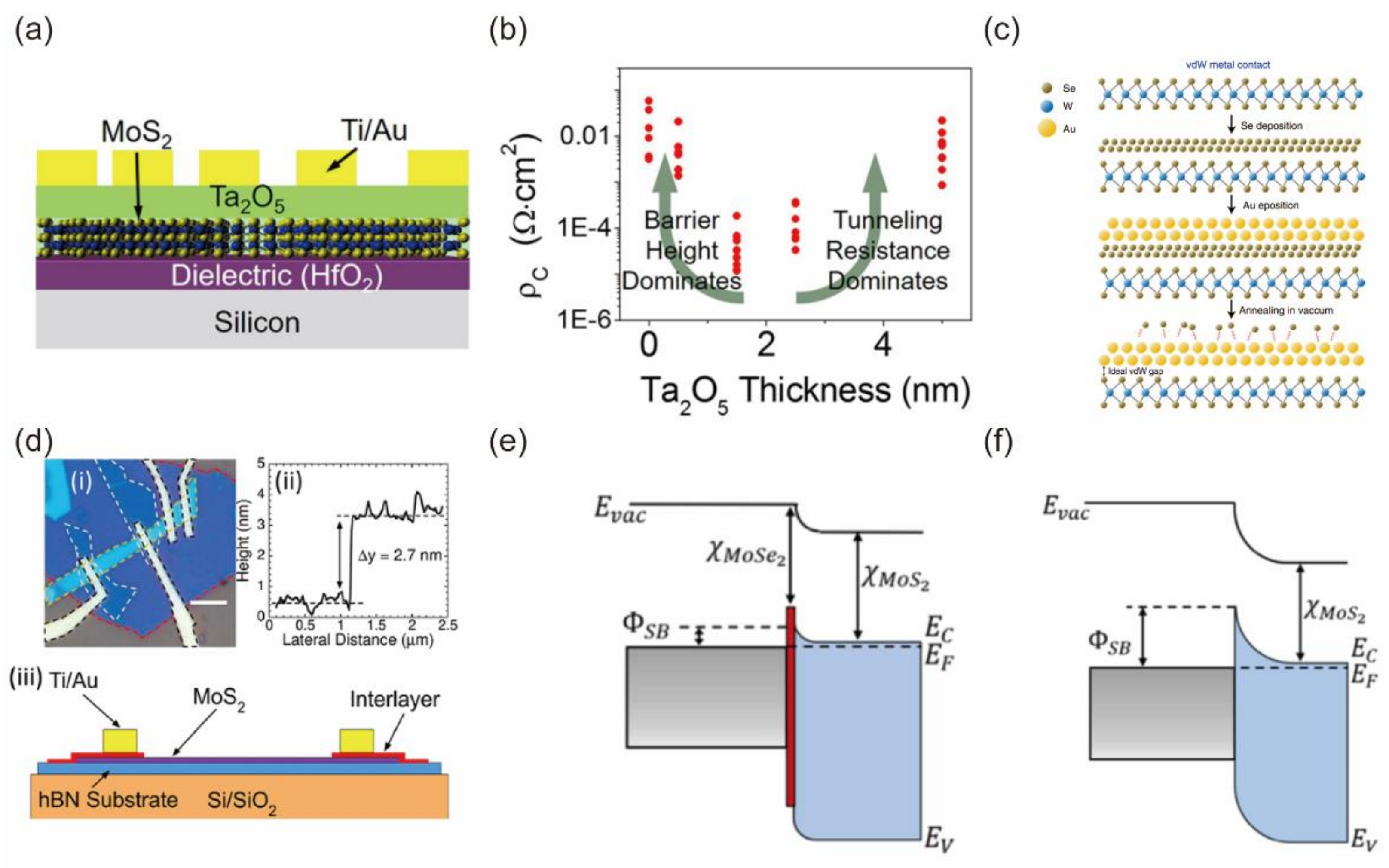

3.3. Inserting Interlayer between Metal and 2D Materials

4. Determination Methods of Contact Resistance

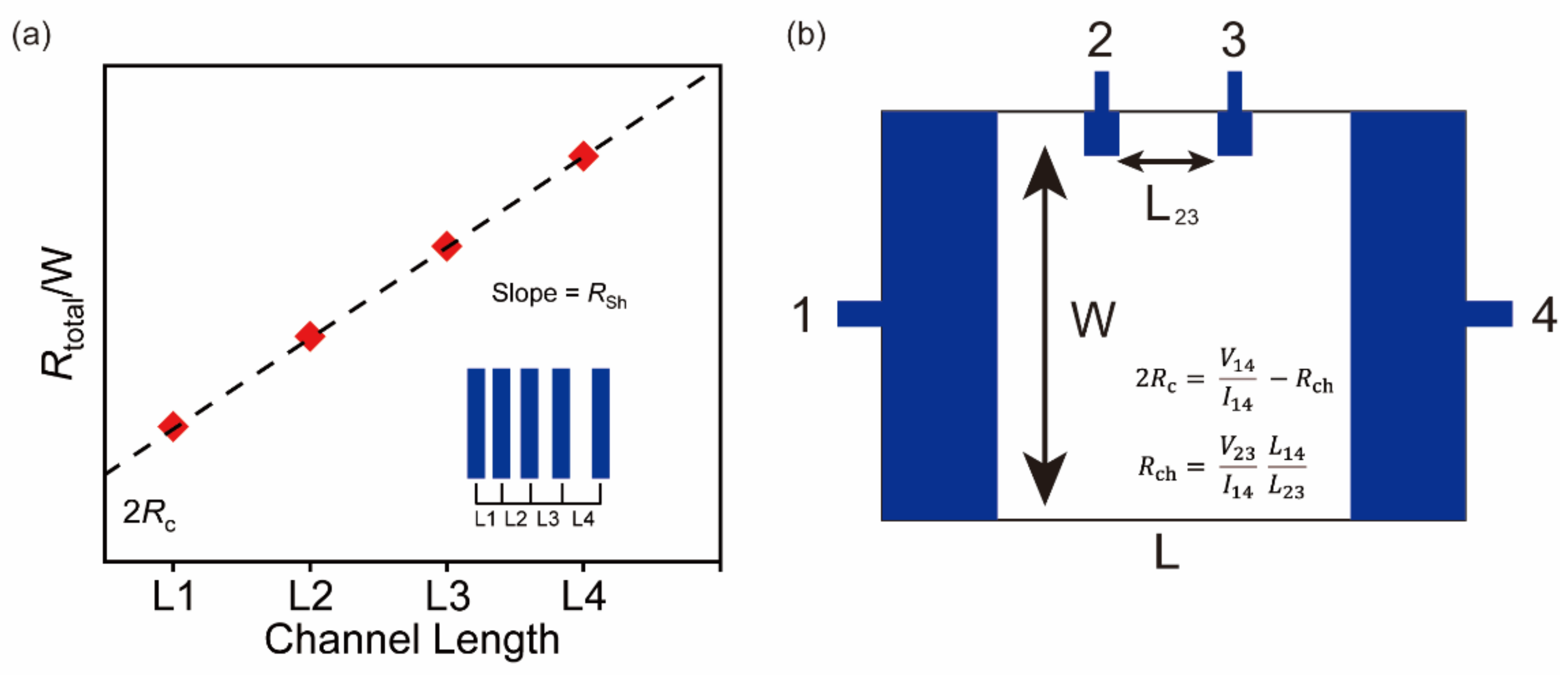

4.1. Transfer Length Method

4.2. Y-Function Method

4.3. Four-Point Probe Method

5. Conclusions and Outlook

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Liu, Y.; Duan, X.; Shin, H.-J.; Park, S.; Huang, Y.; Duan, X. Promises and prospects of two-dimensional transistors. Nature 2021, 591, 43–53. [Google Scholar] [CrossRef] [PubMed]

- Liu, L.; Li, T.; Ma, L.; Li, W.; Gao, S.; Sun, W.; Dong, R.; Zou, X.; Fan, D.; Shao, L.; et al. Uniform nucleation and epitaxy of bilayer molybdenum disulfide on sapphire. Nature 2022, 605, 69–75. [Google Scholar] [CrossRef] [PubMed]

- Kim, Y.; Kim, T.; Lee, J.; Choi, Y.S.; Moon, J.; Park, S.Y.; Lee, T.H.; Park, H.K.; Lee, S.A.; Kwon, M.S.; et al. Tailored Graphene Micropatterns by Wafer-Scale Direct Transfer for Flexible Chemical Sensor Platform. Adv. Mater. 2021, 33, 2004827. [Google Scholar] [CrossRef]

- Zhao, Y.; Xu, K.; Pan, F.; Zhou, C.; Zhou, F.; Chai, Y. Doping, Contact and Interface Engineering of Two-Dimensional Layered Transition Metal Dichalcogenides Transistors. Adv. Funct. Mater. 2017, 27, 1603484. [Google Scholar] [CrossRef]

- Yu, Z.; Ning, H.; Cheng, C.C.; Li, W.; Liu, L.; Meng, W.; Luo, Z.; Li, T.; Cai, S.; Wang, P.; et al. Reliability of Ultrathin High−κ Dielectrics on Chemical-Vapor Deposited 2D Semiconductors. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 3.2.1–3.3.4. [Google Scholar]

- Sebastian, A.; Pendurthi, R.; Choudhury, T.H.; Redwing, J.M.; Das, S. Benchmarking monolayer MoS2 and WS2 field-effect transistors. Nat. Commun. 2021, 12, 693. [Google Scholar] [CrossRef]

- Shen, P.-C.; Su, C.; Lin, Y.; Chou, A.-S.; Cheng, C.-C.; Park, J.-H.; Chiu, M.-H.; Lu, A.-Y.; Tang, H.-L.; Tavakoli, M.M.; et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 2021, 593, 211–217. [Google Scholar] [CrossRef]

- Wang, Y.; Kim, J.C.; Li, Y.; Ma, K.Y.; Hong, S.; Kim, M.; Shin, H.S.; Jeong, H.Y.; Chhowalla, M. P-type electrical contacts for two-dimensional transition metal dichalcogenides. Nature 2022, 610, 61–66. [Google Scholar] [CrossRef]

- Wu, R.; Tao, Q.; Li, J.; Li, W.; Chen, Y.; Lu, Z.; Shu, Z.; Zhao, B.; Ma, H.; Zhang, Z.; et al. Bilayer tungsten diselenide transistors with on-state currents exceeding 1.5 milliamperes per micrometre. Nat. Electron. 2022, 5, 497–504. [Google Scholar] [CrossRef]

- Badaroglu, M. More Moore. In Proceedings of the 2021 IEEE International Roadmap for Devices and Systems Outbriefs, Santa Clara, CA, USA, 30 November 2021; pp. 1–38. [Google Scholar]

- Schottky, W. Zur Halbleitertheorie der Sperrschicht- und Spitzengleichrichter. Z. Für Phys. 1939, 113, 367–414. [Google Scholar] [CrossRef]

- Mott, N.F. The theory of crystal rectifiers. Proc. Royal Soc. A Math. Phys. Eng. Sci. 1939, 171, 27–38. [Google Scholar] [CrossRef]

- Liu, Y.; Guo, J.; Zhu, E.; Liao, L.; Lee, S.-J.; Ding, M.; Shakir, I.; Gambin, V.; Huang, Y.; Duan, X. Approaching the Schottky–Mott limit in van der Waals metal–semiconductor junctions. Nature 2018, 557, 696–700. [Google Scholar] [CrossRef] [PubMed]

- Kim, G.-S.; Kim, S.-H.; Park, J.; Han, K.H.; Kim, J.; Yu, H.-Y. Schottky Barrier Height Engineering for Electrical Contacts of Multilayered MoS2 Transistors with Reduction of Metal-Induced Gap States. ACS Nano 2018, 12, 6292–6300. [Google Scholar] [CrossRef] [PubMed]

- Tersoff, J. Schottky Barrier Heights and the Continuum of Gap States. Phys. Rev. Lett. 1984, 52, 465–468. [Google Scholar] [CrossRef]

- Guo, Y.; Liu, D.; Robertson, J. 3D Behavior of Schottky Barriers of 2D Transition-Metal Dichalcogenides. ACS Appl. Mater. Interfaces 2015, 7, 25709–25715. [Google Scholar] [CrossRef]

- Szczęśniak, D.; Hoehn, R.D.; Kais, S. Canonical Schottky barrier heights of transition metal dichalcogenide monolayers in contact with a metal. Phys. Rev. B 2018, 97, 195315. [Google Scholar] [CrossRef]

- Shautsova, V.; Sinha, S.; Hou, L.; Zhang, Q.; Tweedie, M.; Lu, Y.; Sheng, Y.; Porter, B.F.; Bhaskaran, H.; Warner, J.H. Direct Laser Patterning and Phase Transformation of 2D PdSe2 Films for On-Demand Device Fabrication. ACS Nano 2019, 13, 14162–14171. [Google Scholar] [CrossRef]

- Choi, M.S.; Lee, M.; Ngo, T.D.; Hone, J.; Yoo, W.J. Chemical Dopant-Free Doping by Annealing and Electron Beam Irradiation on 2D Materials. Adv. Electron. Mater. 2021, 7, 2100449. [Google Scholar] [CrossRef]

- Li, F.; Gao, F.; Xu, M.; Liu, X.; Zhang, X.; Wu, H.; Qi, J. Tuning Transport and Photoelectric Performance of Monolayer MoS2 Device by E-Beam Irradiation. Adv. Mater. Interfaces 2018, 5, 1800348. [Google Scholar] [CrossRef]

- Zhao, Y.; Bertolazzi, S.; Maglione, M.S.; Rovira, C.; Mas-Torrent, M.; Samorì, P. Molecular Approach to Electrochemically Switchable Monolayer MoS2 Transistors. Adv. Mater. 2020, 32, 2000740. [Google Scholar] [CrossRef]

- Matsunaga, M.; Higuchi, A.; He, G.; Yamada, T.; Krüger, P.; Ochiai, Y.; Gong, Y.; Vajtai, R.; Ajayan, P.M.; Bird, J.P.; et al. Nanoscale-Barrier Formation Induced by Low−Dose Electron-Beam Exposure in Ultrathin MoS2 Transistors. ACS Nano 2016, 10, 9730–9737. [Google Scholar] [CrossRef]

- Poddar, P.K.; Zhong, Y.; Mannix, A.J.; Mujid, F.; Yu, J.; Liang, C.; Kang, J.-H.; Lee, M.; Xie, S.; Park, J. Resist-Free Lithography for Monolayer Transition Metal Dichalcogenides. Nano Lett. 2022, 22, 726–732. [Google Scholar] [CrossRef] [PubMed]

- Wu, R.J.; Udyavara, S.; Ma, R.; Wang, Y.; Chhowalla, M.; Birol, T.; Koester, S.J.; Neurock, M.; Mkhoyan, K.A. Visualizing the metal−MoS2 contacts in two-dimensional field-effect transistors with atomic resolution. Phys. Rev. Mater. 2019, 3, 111001. [Google Scholar] [CrossRef]

- Smyth, C.M.; Addou, R.; Hinkle, C.L.; Wallace, R.M. Origins of Fermi-level pinning between Molybdenum Dichalcogenides (MoSe2, MoTe2) and Bulk Metal Contacts: Interface Chemistry and Band Alignment. J. Phys. Chem. C 2019, 123, 23919–23930. [Google Scholar] [CrossRef]

- Das, S.; Chen, H.-Y.; Penumatcha, A.V.; Appenzeller, J. High Performance Multilayer MoS2 Transistors with Scandium Contacts. Nano Lett. 2013, 13, 100–105. [Google Scholar] [CrossRef]

- Kim, C.; Moon, I.; Lee, D.; Choi, M.S.; Ahmed, F.; Nam, S.; Cho, Y.; Shin, H.-J.; Park, S.; Yoo, W.J. Fermi Level Pinning at Electrical Metal Contacts of Monolayer Molybdenum Dichalcogenides. ACS Nano 2017, 11, 1588–1596. [Google Scholar] [CrossRef]

- Yuan, H.; Cheng, G.; Yu, S.; Hight Walker, A.R.; Richter, C.A.; Pan, M.; Li, Q. Field effects of current crowding in metal−MoS2 contacts. Appl. Phys. Lett. 2016, 108, 103505. [Google Scholar] [CrossRef]

- Taur, Y.; Ning, T.H. Fundamentals of Modern VLSI Devices; Cambridge University Press: Cambridge, UK, 2021. [Google Scholar]

- Kwon, J.; Lee, J.-Y.; Yu, Y.-J.; Lee, C.-H.; Cui, X.; Hone, J.; Lee, G.-H. Thickness-dependent Schottky barrier height of MoS2 field-effect transistors. Nanoscale 2017, 9, 6151–6157. [Google Scholar] [CrossRef]

- Wang, J.; Guo, X.; Yu, Z.; Ma, Z.; Liu, Y.; Chan, M.; Zhu, Y.; Wang, X.; Chai, Y. Steep Slope p-type 2D WSe2 Field-Effect Transistors with Van Der Waals Contact and Negative Capacitance. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 22.3.1–22.3.4. [Google Scholar] [CrossRef]

- Han, B.; Zhao, Y.; Ma, C.; Wang, C.; Tian, X.; Wang, Y.; Hu, W.; Samorì, P. Asymmetric Chemical Functionalization of Top-Contact Electrodes: Tuning the Charge Injection for High-Performance MoS2 Field-Effect Transistors and Schottky Diodes. Adv. Mater. 2022, 34, 2109445. [Google Scholar] [CrossRef]

- Mao, J.-Y.; Wu, S.; Ding, G.; Wang, Z.-P.; Qian, F.-S.; Yang, J.-Q.; Zhou, Y.; Han, S.-T. A van der Waals Integrated Damage-Free Memristor Based on Layered 2D Hexagonal Boron Nitride. Small 2022, 18, 2106253. [Google Scholar] [CrossRef]

- Jung, Y.; Choi, M.S.; Nipane, A.; Borah, A.; Kim, B.; Zangiabadi, A.; Taniguchi, T.; Watanabe, K.; Yoo, W.J.; Hone, J.; et al. Transferred via contacts as a platform for ideal two-dimensional transistors. Nat. Electron. 2019, 2, 187–194. [Google Scholar] [CrossRef]

- English, C.D.; Shine, G.; Dorgan, V.E.; Saraswat, K.C.; Pop, E. Improved Contacts to MoS2 Transistors by Ultra-High Vacuum Metal Deposition. Nano Lett. 2016, 16, 3824–3830. [Google Scholar] [CrossRef] [PubMed]

- Wang, Y.; Kim, J.C.; Wu, R.J.; Martinez, J.; Song, X.; Yang, J.; Zhao, F.; Mkhoyan, A.; Jeong, H.Y.; Chhowalla, M. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. Nature 2019, 568, 70–74. [Google Scholar] [CrossRef] [PubMed]

- Kumar, A.; Schauble, K.; Neilson, K.M.; Tang, A.; Ramesh, P.; Wong, H.S.P.; Pop, E.; Saraswat, K. Sub−200 Ω·µm Alloyed Contacts to Synthetic Monolayer MoS2. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 7.3.1–7.3.4. [Google Scholar] [CrossRef]

- Jin, L.; Koester, S.J. High-Performance Dual-Gated Single-Layer WS2 MOSFETs With Bi Contacts. IEEE Electron Device Lett. 2022, 43, 639–642. [Google Scholar] [CrossRef]

- Chou, A.S.; Wu, T.; Cheng, C.C.; Zhan, S.S.; Ni, I.C.; Wang, S.Y.; Chang, Y.C.; Liew, S.L.; Chen, E.; Chang, W.H.; et al. Antimony Semimetal Contact with Enhanced Thermal Stability for High Performance 2D Electronics. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 7.2.1–7.2.4. [Google Scholar] [CrossRef]

- Liu, Y.; Stradins, P.; Wei, S.-H. Van der Waals metal-semiconductor junction: Weak Fermi level pinning enables effective tuning of Schottky barrier. Sci. Adv. 2016, 2, e1600069. [Google Scholar] [CrossRef] [PubMed]

- Murali, K.; Dandu, M.; Watanabe, K.; Taniguchi, T.; Majumdar, K. Accurate Extraction of Schottky Barrier Height and Universality of Fermi Level De-Pinning of van der Waals Contacts. Adv. Funct. Mater. 2021, 31, 2010513. [Google Scholar] [CrossRef]

- Zhang, C.; Gong, C.; Nie, Y.; Min, K.-A.; Liang, C.; Oh, Y.J.; Zhang, H.; Wang, W.; Hong, S.; Colombo, L.; et al. Systematic study of electronic structure and band alignment of monolayer transition metal dichalcogenides in Van der Waals heterostructures. 2D Mater. 2016, 4, 015026. [Google Scholar] [CrossRef]

- Liu, Y.; Wu, H.; Cheng, H.-C.; Yang, S.; Zhu, E.; He, Q.; Ding, M.; Li, D.; Guo, J.; Weiss, N.O.; et al. Toward Barrier Free Contact to Molybdenum Disulfide Using Graphene Electrodes. Nano Lett. 2015, 15, 3030–3034. [Google Scholar] [CrossRef]

- Chuang, H.-J.; Chamlagain, B.; Koehler, M.; Perera, M.M.; Yan, J.; Mandrus, D.; Tománek, D.; Zhou, Z. Low-Resistance 2D/2D Ohmic Contacts: A Universal Approach to High-Performance WSe2, MoS2, and MoSe2 Transistors. Nano Lett. 2016, 16, 1896–1902. [Google Scholar] [CrossRef]

- Jang, J.; Ra, H.-S.; Ahn, J.; Kim, T.W.; Song, S.H.; Park, S.; Taniguch, T.; Watanabe, K.; Lee, K.; Hwang, D.K. Fermi-level pinning-Free WSe2 Transistors via 2D Van der Waals Metal Contacts and Their Circuits. Adv. Mater. 2022, 34, 2109899. [Google Scholar] [CrossRef]

- Zhao, Y.; Qiao, J.; Yu, Z.; Yu, P.; Xu, K.; Lau, S.P.; Zhou, W.; Liu, Z.; Wang, X.; Ji, W.; et al. High-Electron-Mobility and Air-STable 2D Layered PtSe2 FETs. Adv. Mater. 2017, 29, 1604230. [Google Scholar] [CrossRef]

- Wang, Y.; Li, L.; Yao, W.; Song, S.; Sun, J.T.; Pan, J.; Ren, X.; Li, C.; Okunishi, E.; Wang, Y.-Q.; et al. Monolayer PtSe2, a New Semiconducting Transition-Metal-Dichalcogenide, Epitaxially Grown by Direct Selenization of Pt. Nano Lett. 2015, 15, 4013–4018. [Google Scholar] [CrossRef] [PubMed]

- Zhang, K.; Yan, M.; Zhang, H.; Huang, H.; Arita, M.; Sun, Z.; Duan, W.; Wu, Y.; Zhou, S. Experimental evidence for type−II Dirac semimetal in PtSe2. Phys. Rev. B 2017, 96, 125102. [Google Scholar] [CrossRef]

- Shi, J.; Huan, Y.; Hong, M.; Xu, R.; Yang, P.; Zhang, Z.; Zou, X.; Zhang, Y. Chemical Vapor Deposition Grown Large-Scale Atomically Thin Platinum Diselenide with Semimetal–Semiconductor Transition. ACS Nano 2019, 13, 8442–8451. [Google Scholar] [CrossRef]

- Das, T.; Yang, E.; Seo, J.E.; Kim, J.H.; Park, E.; Kim, M.; Seo, D.; Kwak, J.Y.; Chang, J. Doping-Free All PtSe2 Transistor via Thickness-Modulated Phase Transition. ACS Appl. Mater. Interfaces 2021, 13, 1861–1871. [Google Scholar] [CrossRef] [PubMed]

- Zhang, X.; Yu, H.; Tang, W.; Wei, X.; Gao, L.; Hong, M.; Liao, Q.; Kang, Z.; Zhang, Z.; Zhang, Y. All-van-der-Waals Barrier-Free Contacts for High-Mobility Transistors. Adv. Mater. 2022, 34, 2109521. [Google Scholar] [CrossRef] [PubMed]

- Mootheri, V.; Arutchelvan, G.; Banerjee, S.; Sutar, S.; Leonhardt, A.; Boulon, M.-E.; Huyghebaert, C.; Houssa, M.; Asselberghs, I.; Radu, I. Graphene based Van der Waals contacts on MoS2 field effect transistors. 2D Mater. 2021, 8, 015003. [Google Scholar] [CrossRef]

- Choi, M.S.; Ali, N.; Ngo, T.D.; Choi, H.; Oh, B.; Yang, H.; Yoo, W.J. Recent Progress in 1D Contacts for 2D-Material-Based Devices. Adv. Mater. 2022, 34, 2202408. [Google Scholar] [CrossRef]

- Liu, G.-B.; Xiao, D.; Yao, Y.; Xu, X.; Yao, W. Electronic structures and theoretical modelling of two-dimensional group-VIB transition metal dichalcogenides. Chem. Soc. Rev. 2015, 44, 2643–2663. [Google Scholar] [CrossRef]

- Yang, Z.; Kim, C.; Lee, K.Y.; Lee, M.; Appalakondaiah, S.; Ra, C.-H.; Watanabe, K.; Taniguchi, T.; Cho, K.; Hwang, E.; et al. A Fermi-Level-Pinning-Free 1D Electrical Contact at the Intrinsic 2D MoS2–Metal Junction. Adv. Mater. 2019, 31, 1808231. [Google Scholar] [CrossRef]

- Jain, A.; Szabó, Á.; Parzefall, M.; Bonvin, E.; Taniguchi, T.; Watanabe, K.; Bharadwaj, P.; Luisier, M.; Novotny, L. One-Dimensional Edge Contacts to a Monolayer Semiconductor. Nano Lett. 2019, 19, 6914–6923. [Google Scholar] [CrossRef]

- Mirabelli, G.; McGeough, C.; Schmidt, M.; McCarthy, E.K.; Monaghan, S.; Povey, I.M.; McCarthy, M.; Gity, F.; Nagle, R.; Hughes, G.; et al. Air sensitivity of MoS2, MoSe2, MoTe2, HfS2, and HfSe2. J. Appl. Phys. 2016, 120, 125102. [Google Scholar] [CrossRef]

- Illarionov, Y.Y.; Waltl, M.; Rzepa, G.; Kim, J.-S.; Kim, S.; Dodabalapur, A.; Akinwande, D.; Grasser, T. Long-Term Stability and Reliability of Black Phosphorus Field-Effect Transistors. ACS Nano 2016, 10, 9543–9549. [Google Scholar] [CrossRef] [PubMed]

- Wang, Y.; Gao, J.; Wei, B.; Han, Y.; Wang, C.; Gao, Y.; Liu, H.; Han, L.; Zhang, Y. Reduction of the ambient effect in multilayer InSe transistors and a strategy toward sTable 2D-based optoelectronic applications. Nanoscale 2020, 12, 18356–18362. [Google Scholar] [CrossRef]

- Chai, Y.; Ionescu, R.; Su, S.; Lake, R.; Ozkan, M.; Ozkan, C.S. Making one-dimensional electrical contacts to molybdenum disulfide-based heterostructures through plasma etching. Phys. Status Solidi A 2016, 213, 1358–1364. [Google Scholar] [CrossRef]

- Cheng, Z.; Yu, Y.; Singh, S.; Price, K.; Noyce, S.G.; Lin, Y.-C.; Cao, L.; Franklin, A.D. Immunity to Contact Scaling in MoS2 Transistors Using in Situ Edge Contacts. Nano Lett. 2019, 19, 5077–5085. [Google Scholar] [CrossRef] [PubMed]

- Duerloo, K.-A.N.; Li, Y.; Reed, E.J. Structural phase transitions in two-dimensional Mo− and W−dichalcogenide monolayers. Nat. Commun. 2014, 5, 4214. [Google Scholar] [CrossRef]

- Voiry, D.; Mohite, A.; Chhowalla, M. Phase engineering of transition metal dichalcogenides. Chem. Soc. Rev. 2015, 44, 2702–2712. [Google Scholar] [CrossRef]

- Huang, H.H.; Fan, X.; Singh, D.J.; Zheng, W.T. Recent progress of TMD nanomaterials: Phase transitions and applications. Nanoscale 2020, 12, 1247–1268. [Google Scholar] [CrossRef]

- Kim, J.; Park, H.; Yoo, S.; Im, Y.-H.; Kang, K.; Kim, J. Defect-Engineered n-Doping of WSe2 via Argon Plasma Treatment and Its Application in Field-Effect Transistors. Adv. Mater. Interfaces 2021, 8, 2100718. [Google Scholar] [CrossRef]

- Ma, R.; Zhang, H.; Yoo, Y.; Degregorio, Z.P.; Jin, L.; Golani, P.; Ghasemi Azadani, J.; Low, T.; Johns, J.E.; Bendersky, L.A.; et al. MoTe2 Lateral Homojunction Field-Effect Transistors Fabricated using Flux-Controlled Phase Engineering. ACS Nano 2019, 13, 8035–8046. [Google Scholar] [CrossRef]

- Lee, E.K.; Abdullah, H.; Torricelli, F.; Lee, D.H.; Ko, J.K.; Kim, H.H.; Yoo, H.; Oh, J.H. Boosting the Optoelectronic Properties of Molybdenum Diselenide by Combining Phase Transition Engineering with Organic Cationic Dye Doping. ACS Nano 2021, 15, 17769–17779. [Google Scholar] [CrossRef]

- Kappera, R.; Voiry, D.; Yalcin, S.E.; Branch, B.; Gupta, G.; Mohite, A.D.; Chhowalla, M. Phase-engineered low-resistance contacts for ultrathin MoS2 transistors. Nat. Mater. 2014, 13, 1128–1134. [Google Scholar] [CrossRef] [PubMed]

- Zhao, Y.; Bertolazzi, S.; Samorì, P. A Universal Approach toward Light-Responsive Two-Dimensional Electronics: Chemically Tailored Hybrid van der Waals Heterostructures. ACS Nano 2019, 13, 4814–4825. [Google Scholar] [CrossRef] [PubMed]

- Cho, S.; Kim, S.; Kim, J.H.; Zhao, J.; Seok, J.; Keum, D.H.; Baik, J.; Choe, D.-H.; Chang, K.J.; Suenaga, K.; et al. Phase patterning for ohmic homojunction contact in MoTe2. Science 2015, 349, 625–628. [Google Scholar] [CrossRef] [PubMed]

- Keum, D.H.; Cho, S.; Kim, J.H.; Choe, D.-H.; Sung, H.-J.; Kan, M.; Kang, H.; Hwang, J.-Y.; Kim, S.W.; Yang, H.; et al. Bandgap opening in few-layered monoclinic MoTe2. Nat. Phys. 2015, 11, 482–486. [Google Scholar] [CrossRef]

- Naz, M.; Hallam, T.; Berner, N.C.; McEvoy, N.; Gatensby, R.; McManus, J.B.; Akhter, Z.; Duesberg, G.S. A New 2H−2H′/1T Cophase in Polycrystalline MoS2 and MoSe2 Thin Films. ACS Appl. Mater. Interfaces 2016, 8, 31442–31448. [Google Scholar] [CrossRef] [PubMed]

- Ma, Y.; Liu, B.; Zhang, A.; Chen, L.; Fathi, M.; Shen, C.; Abbas, A.N.; Ge, M.; Mecklenburg, M.; Zhou, C. Reversible Semiconducting-to-Metallic Phase Transition in Chemical Vapor Deposition Grown Monolayer WSe2 and Applications for Devices. ACS Nano 2015, 9, 7383–7391. [Google Scholar] [CrossRef]

- Zhu, J.; Wang, Z.; Yu, H.; Li, N.; Zhang, J.; Meng, J.; Liao, M.; Zhao, J.; Lu, X.; Du, L.; et al. Argon Plasma Induced Phase Transition in Monolayer MoS2. J. Am. Chem. Soc. 2017, 139, 10216–10219. [Google Scholar] [CrossRef]

- Oyedele, A.D.; Yang, S.; Feng, T.; Haglund, A.V.; Gu, Y.; Puretzky, A.A.; Briggs, D.; Rouleau, C.M.; Chisholm, M.F.; Unocic, R.R.; et al. Defect-Mediated Phase Transformation in Anisotropic Two-Dimensional PdSe2 Crystals for Seamless Electrical Contacts. J. Am. Chem. Soc. 2019, 141, 8928–8936. [Google Scholar] [CrossRef]

- Cai, X.; Wu, Z.; Han, X.; Chen, Y.; Xu, S.; Lin, J.; Han, T.; He, P.; Feng, X.; An, L.; et al. Bridging the gap between atomically thin semiconductors and metal leads. Nat. Commun. 2022, 13, 1777. [Google Scholar] [CrossRef]

- Li, H.; Cheng, M.; Wang, P.; Du, R.; Song, L.; He, J.; Shi, J. Reducing Contact Resistance and Boosting Device Performance of Monolayer MoS2 by In Situ Fe Doping. Adv. Mater. 2022, 34, 2200885. [Google Scholar] [CrossRef] [PubMed]

- Vu, V.T.; Vu, T.T.H.; Phan, T.L.; Kang, W.T.; Kim, Y.R.; Tran, M.D.; Nguyen, H.T.T.; Lee, Y.H.; Yu, W.J. One-Step Synthesis of NbSe2/Nb−Doped−WSe2 Metal/Doped−Semiconductor van der Waals Heterostructures for Doping Controlled Ohmic Contact. ACS Nano 2021, 15, 13031–13040. [Google Scholar] [CrossRef] [PubMed]

- Hemanjaneyulu, K.; Kumar, J.; Shrivastava, M. MoS2 Doping Using Potassium Iodide for Reliable Contacts and Efficient FET Operation. IEEE Trans. Electron Devices 2019, 66, 3224–3228. [Google Scholar] [CrossRef]

- Khan, M.F.; Rehman, S.; Akhtar, I.; Aftab, S.; Ajmal, H.M.S.; Khan, W.; Kim, D.-K.; Eom, J. High mobility ReSe2 field effect transistors: Schottky-barrier-height-dependent photoresponsivity and broadband light detection with Co decoration. 2D Mater. 2020, 7, 015010. [Google Scholar] [CrossRef]

- Sarkar, D.; Xie, X.; Kang, J.; Zhang, H.; Liu, W.; Navarrete, J.; Moskovits, M.; Banerjee, K. Functionalization of Transition Metal Dichalcogenides with Metallic Nanoparticles: Implications for Doping and Gas-Sensing. Nano Lett. 2015, 15, 2852–2862. [Google Scholar] [CrossRef]

- Wang, J.; Yao, Q.; Huang, C.-W.; Zou, X.; Liao, L.; Chen, S.; Fan, Z.; Zhang, K.; Wu, W.; Xiao, X.; et al. High Mobility MoS2 Transistor with Low Schottky Barrier Contact by Using Atomic Thick h−BN as a Tunneling Layer. Adv. Mater. 2016, 28, 8302–8308. [Google Scholar] [CrossRef]

- Chen, J.-R.; Odenthal, P.M.; Swartz, A.G.; Floyd, G.C.; Wen, H.; Luo, K.Y.; Kawakami, R.K. Control of Schottky Barriers in Single Layer MoS2 Transistors with Ferromagnetic Contacts. Nano Lett. 2013, 13, 3106–3110. [Google Scholar] [CrossRef]

- Lee, S.; Tang, A.; Aloni, S.; Philip Wong, H.S. Statistical Study on the Schottky Barrier Reduction of Tunneling Contacts to CVD Synthesized MoS2. Nano Lett. 2016, 16, 276–281. [Google Scholar] [CrossRef]

- Mleczko, M.J.; Yu, A.C.; Smyth, C.M.; Chen, V.; Shin, Y.C.; Chatterjee, S.; Tsai, Y.-C.; Nishi, Y.; Wallace, R.M.; Pop, E. Contact Engineering High-Performance n-Type MoTe2 Transistors. Nano Lett. 2019, 19, 6352–6362. [Google Scholar] [CrossRef]

- Cui, X.; Shih, E.-M.; Jauregui, L.A.; Chae, S.H.; Kim, Y.D.; Li, B.; Seo, D.; Pistunova, K.; Yin, J.; Park, J.-H.; et al. Low-Temperature Ohmic Contact to Monolayer MoS2 by van der Waals Bonded Co/h−BN Electrodes. Nano Lett. 2017, 17, 4781–4786. [Google Scholar] [CrossRef]

- Jang, J.; Kim, Y.; Chee, S.-S.; Kim, H.; Whang, D.; Kim, G.-H.; Yun, S.J. Clean Interface Contact Using a ZnO Interlayer for Low-Contact-Resistance MoS2 Transistors. ACS Appl. Mater. Interfaces 2020, 12, 5031–5039. [Google Scholar] [CrossRef] [PubMed]

- Kwon, G.; Choi, Y.-H.; Lee, H.; Kim, H.-S.; Jeong, J.; Jeong, K.; Baik, M.; Kwon, H.; Ahn, J.; Lee, E.; et al. Interaction- and defect-free van der Waals contacts between metals and two-dimensional semiconductors. Nat. Electron. 2022, 5, 241–247. [Google Scholar] [CrossRef]

- Andrews, K.; Bowman, A.; Rijal, U.; Chen, P.-Y.; Zhou, Z. Improved Contacts and Device Performance in MoS2 Transistors Using a 2D Semiconductor Interlayer. ACS Nano 2020, 14, 6232–6241. [Google Scholar] [CrossRef]

- Chang, H.-Y.; Zhu, W.; Akinwande, D. On the mobility and contact resistance evaluation for transistors based on MoS2 or two-dimensional semiconducting atomic crystals. Appl. Phys. Lett. 2014, 104, 113504. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Miao, J.; Zhang, X.; Tian, Y.; Zhao, Y. Recent Progress in Contact Engineering of Field-Effect Transistor Based on Two-Dimensional Materials. Nanomaterials 2022, 12, 3845. https://doi.org/10.3390/nano12213845

Miao J, Zhang X, Tian Y, Zhao Y. Recent Progress in Contact Engineering of Field-Effect Transistor Based on Two-Dimensional Materials. Nanomaterials. 2022; 12(21):3845. https://doi.org/10.3390/nano12213845

Chicago/Turabian StyleMiao, Jialei, Xiaowei Zhang, Ye Tian, and Yuda Zhao. 2022. "Recent Progress in Contact Engineering of Field-Effect Transistor Based on Two-Dimensional Materials" Nanomaterials 12, no. 21: 3845. https://doi.org/10.3390/nano12213845

APA StyleMiao, J., Zhang, X., Tian, Y., & Zhao, Y. (2022). Recent Progress in Contact Engineering of Field-Effect Transistor Based on Two-Dimensional Materials. Nanomaterials, 12(21), 3845. https://doi.org/10.3390/nano12213845