Effect of Back-Gate Voltage on the High-Frequency Performance of Dual-Gate MoS2 Transistors

Abstract

1. Introduction

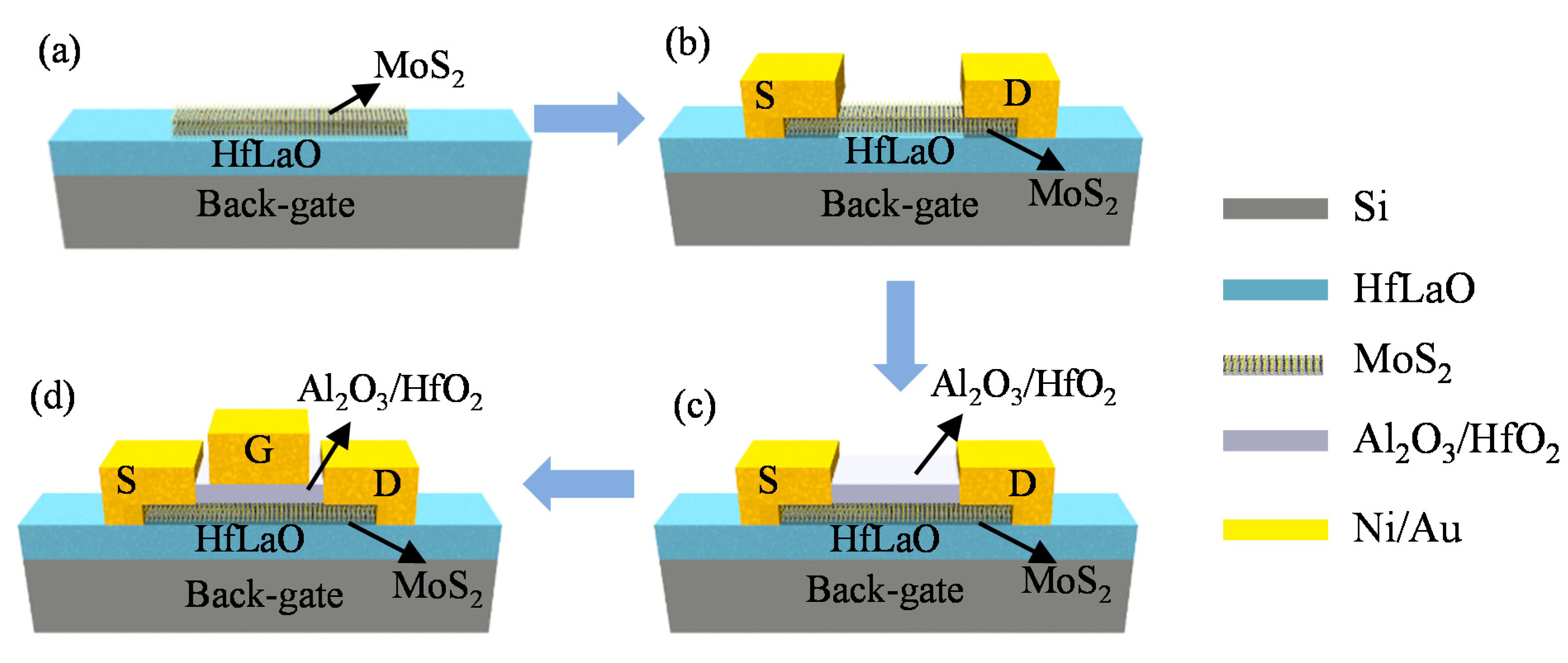

2. Materials and Methods

3. Results and Discussion

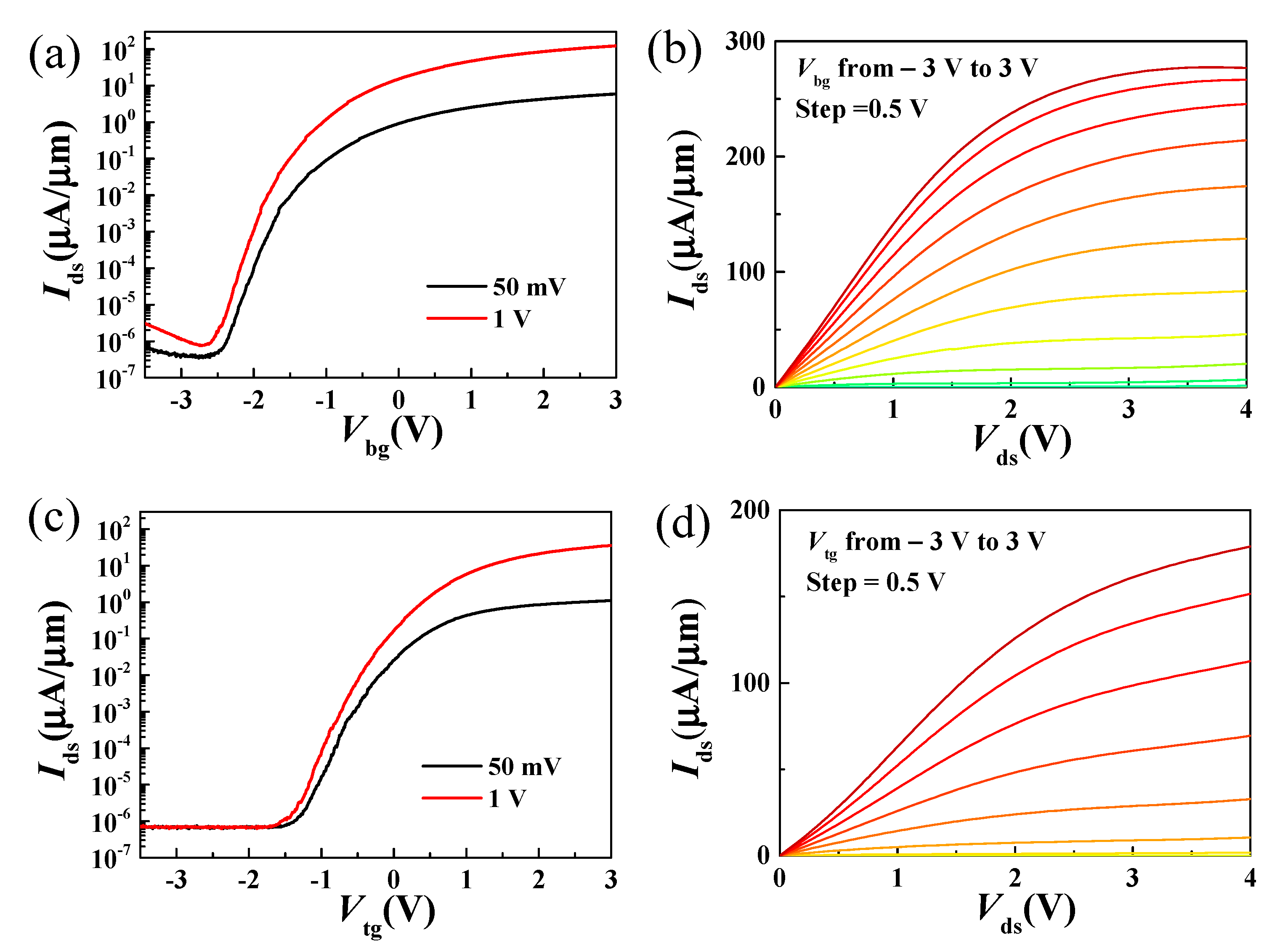

3.1. DC Characterization

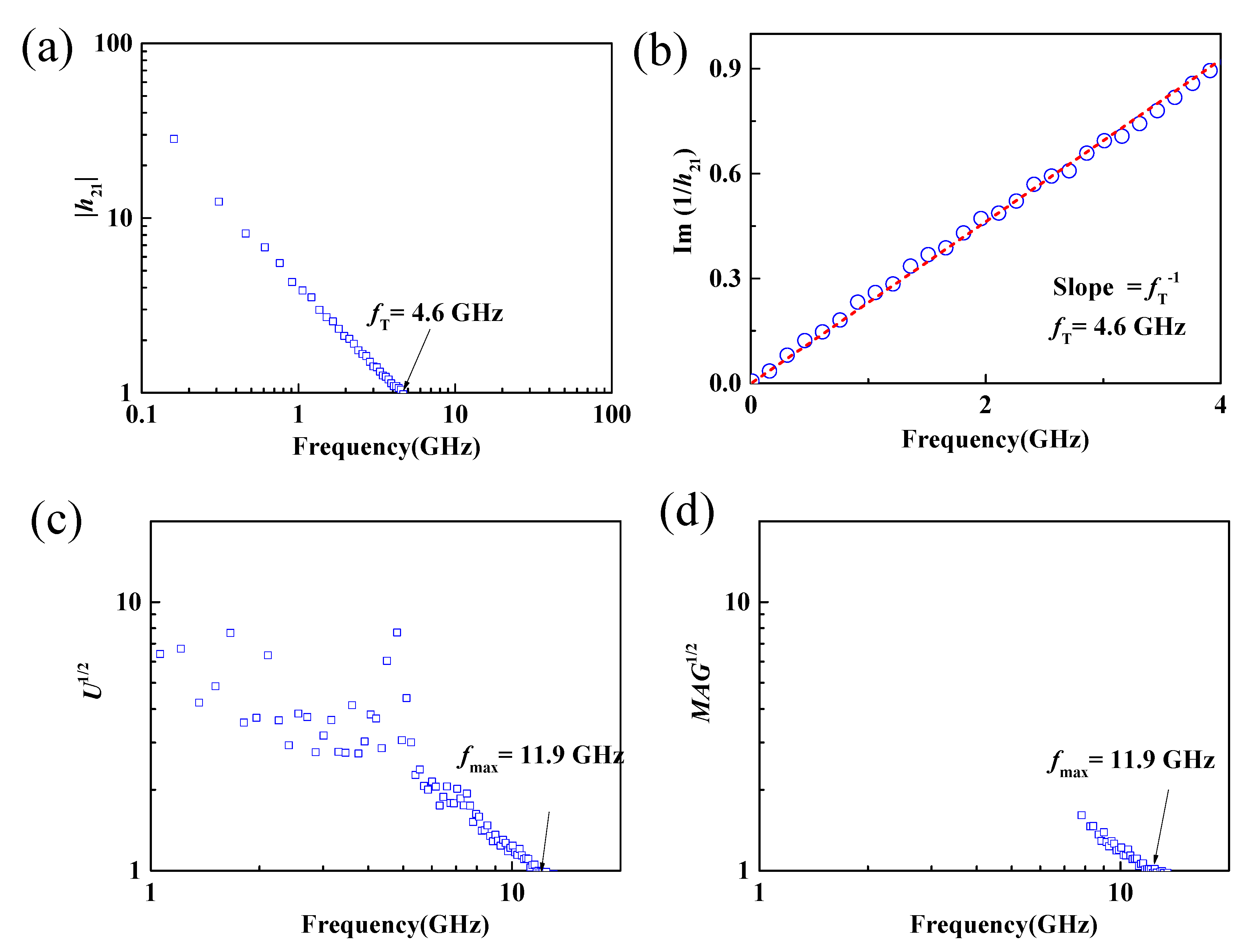

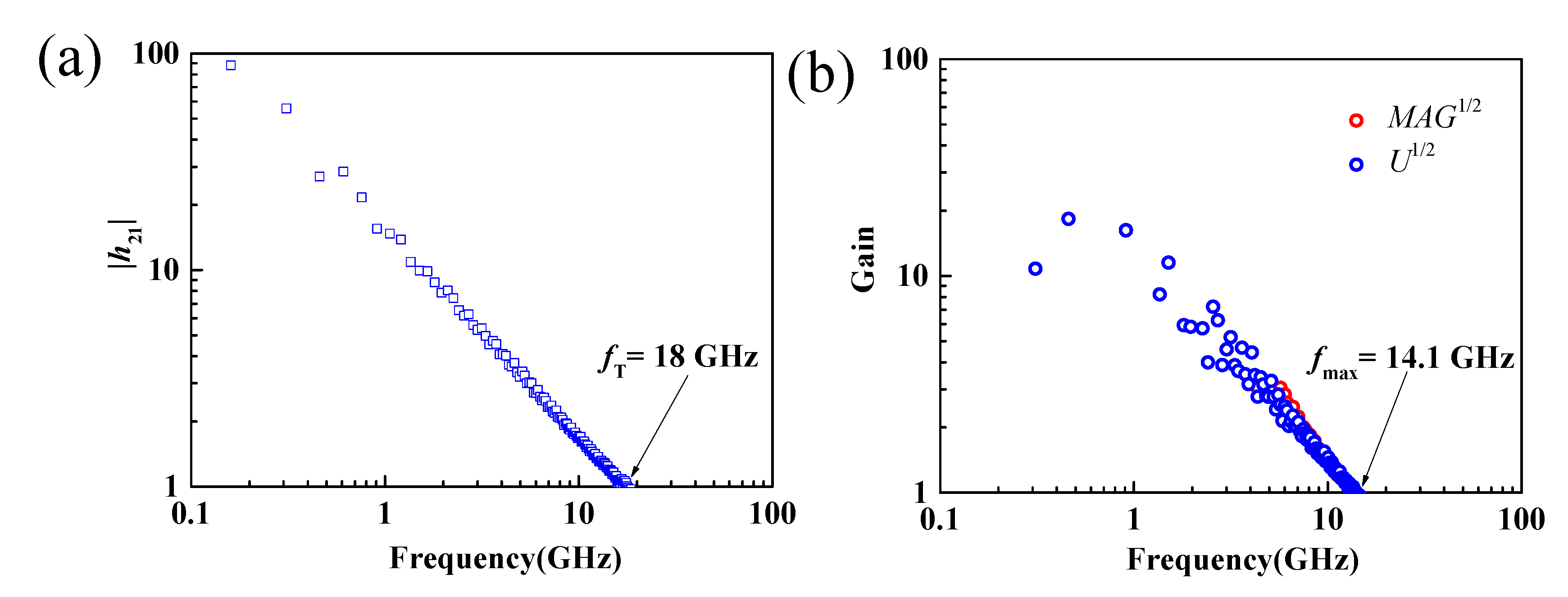

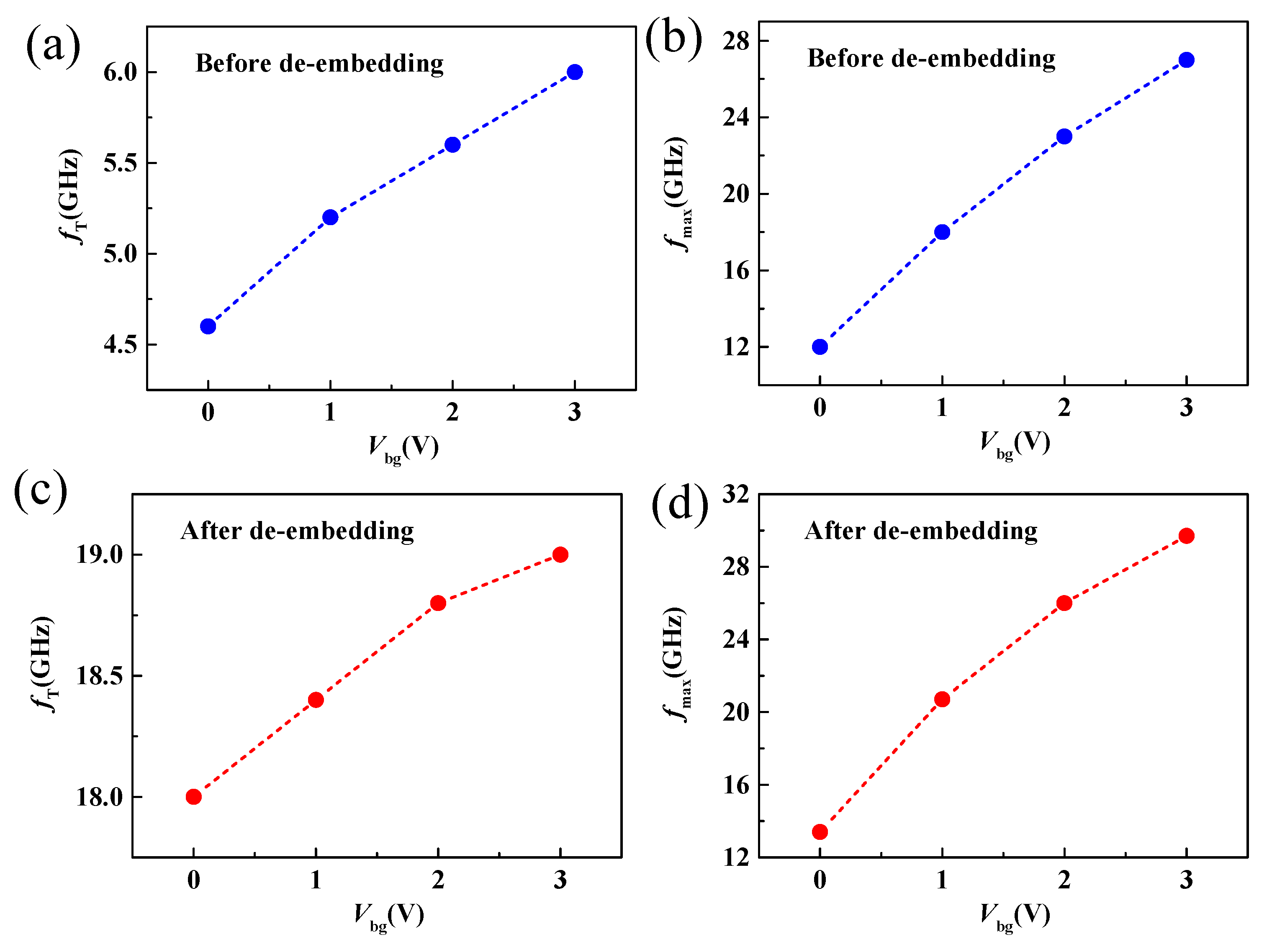

3.2. RF Characterization

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Novoselov, K.S.; Geim, A.K.; Morozov, S.V.; Jiang, D.; Zhang, Y.; Dubonos, S.V.; Grigorieva, I.V.; Firsov, A.A. Electric field effect in atomically thin carbon films. Science 2004, 306, 666–669. [Google Scholar] [CrossRef]

- Schwierz, F. Graphene transistors. Nat. Nanotechnol. 2010, 5, 487–496. [Google Scholar] [CrossRef]

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 2011, 6, 147–150. [Google Scholar] [CrossRef] [PubMed]

- Desai, S.B.; Madhvapathy, S.R.; Sachid, A.B.; Llinas, J.P.; Wang, Q.; Ahn, G.H.; Pitner, G.; Kim, M.J.; Bokor, J.; Hu, C.; et al. MoS2 transistors with 1-nanometer gate lengths. Science 2016, 354, 99–102. [Google Scholar] [CrossRef] [PubMed]

- Tombros, N.; Jozsa, C.; Popinciuc, M.; Jonkman, H.T.; Van Wees, B.J. Electronic spin transport and spin precession in single graphene layers at room temperature. Nature 2007, 448, 571–574. [Google Scholar] [CrossRef] [PubMed]

- Cho, S.; Chen, Y.-F.; Fuhrer, M.S. Gate-tunable graphene spin valve. Appl. Phys. Lett. 2007, 91, 123105. [Google Scholar] [CrossRef]

- Schedin, F.; Geim, A.K.; Morozov, S.V.; Hill, E.W.; Blake, P.; Katsnelson, M.I.; Novoselov, K. Detection of individual gas molecules adsorbed on graphene. Nat. Mater. 2007, 6, 652–655. [Google Scholar] [CrossRef] [PubMed]

- Ohno, Y.; Maehashi, K.; Yamashiro, Y.; Matsumoto, K. Electrolyte-Gated Graphene Field-Effect Transistors for Detecting pH and Protein Adsorption. Nano Lett. 2009, 9, 3318–3322. [Google Scholar] [CrossRef] [PubMed]

- Cheng, Z.; Li, Q.; Li, Z.; Zhou, Q.; Fang, Y. Suspended Graphene Sensors with Improved Signal and Reduced Noise. Nano Lett. 2010, 10, 1864–1868. [Google Scholar] [CrossRef]

- Cohen-Karni, T.; Qing, Q.; Li, Q.; Fang, Y.; Lieber, C.M. Graphene and Nanowire Transistors for Cellular Interfaces and Electrical Recording. Nano Lett. 2010, 10, 1098–1102. [Google Scholar] [CrossRef]

- Bunch, J.S.; Van Der Zande, A.M.; Verbridge, S.S.; Frank, I.W.; Tanenbaum, D.M.; Parpia, J.M.; Craighead, H.G.; McEuen, P.L. Electromechanical Resonators from Graphene Sheets. Science 2007, 315, 490–493. [Google Scholar] [CrossRef]

- Stoller, M.D.; Park, S.; Zhu, Y.; An, J.; Ruoff, R.S. Graphene-Based Ultracapacitors. Nano Lett. 2008, 8, 3498–3502. [Google Scholar] [CrossRef]

- Wang, Q.H.; Kalantar-Zadeh, K.; Kis, A.; Coleman, J.N.; Strano, M.S. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. Nat. Nanotechnol. 2012, 7, 699–712. [Google Scholar] [CrossRef]

- Yoon, Y.; Ganapathi, K.; Salahuddin, S. How good can monolayer MoS2 transistors be? Nano Lett. 2011, 11, 3768–3773. [Google Scholar] [CrossRef]

- Akinwande, D.; Petrone, N.; Hone, J. Two-dimensional flexible nanoelectronics. Nat. Commun. 2014, 5, 5678. [Google Scholar] [CrossRef] [PubMed]

- Gao, Q.; Zhang, Z.; Xu, X.; Song, J.; Li, X.; Wu, Y. Scalable high performance radio frequency electronics based on large domain bilayer MoS2. Nat. Commun. 2018, 9, 4778. [Google Scholar] [CrossRef] [PubMed]

- Lin, Z.; Liu, Y.; Halim, U.; Ding, M.; Liu, Y.; Wang, Y.; Jia, C.; Chen, P.; Duan, X.; Wang, C.; et al. Solution-processable 2D semiconductors for high-performance large-area electronics. Nat. Cell Biol. 2018, 562, 254–258. [Google Scholar] [CrossRef]

- Zhang, X.; Grajal, J.; Vazquez-Roy, J.L.; Radhakrishna, U.; Wang, X.; Chern, W.; Zhou, L.; Lin, Y.; Shen, P.-C.; Ji, X.; et al. Two-dimensional MoS2-enabled flexible rectenna for Wi-Fi-band wireless energy harvesting. Nature 2019, 566, 368–372. [Google Scholar] [CrossRef] [PubMed]

- Na, J.; Joo, M.-K.; Shin, M.; Huh, J.; Kim, J.-S.; Piao, M.; Jin, J.-E.; Jang, H.-K.; Choi, H.J.; Shim, J.H.; et al. Low-frequency noise in multilayer MoS2 field-effect transistors: the effect of high-k passivation. Nanoscale 2014, 6, 433–441. [Google Scholar] [CrossRef]

- Liu, N.; Baek, J.; Kim, S.M.; Hong, S.; Hong, Y.K.; Kim, Y.S.; Kim, H.-S.; Kim, S.; Park, J. Improving the Stability of High-Performance Multilayer MoS2 Field-Effect Transistors. ACS Appl. Mater. Interfaces 2017, 9, 42943–42950. [Google Scholar] [CrossRef] [PubMed]

- Chang, H.-Y.; Yogeesh, M.N.; Ghosh, R.; Rai, A.; Sanne, A.; Yang, S.; Lu, N.; Banerjee, S.K.; Akinwande, D. Large-Area Monolayer MoS2 for Flexible Low-Power RF Nanoelectronics in the GHz Regime. Adv. Mater. 2016, 28, 1818–1823. [Google Scholar] [CrossRef] [PubMed]

- Krasnozhon, D.; Lembke, D.; Nyffeler, C.; Leblebici, Y.; Kis, A. MoS2 Transistors Operating at Gigahertz Frequencies. Nano Lett. 2014, 14, 5905–5911. [Google Scholar] [CrossRef] [PubMed]

- Sanne, A.; Ghosh, R.; Rai, A.; Yogeesh, M.N.; Shin, S.H.; Sharma, A.; Jarvis, K.; Mathew, L.; Rao, R.; Akinwande, D.; et al. Radio Frequency Transistors and Circuits Based on CVD MoS2. Nano Lett. 2015, 15, 5039–5045. [Google Scholar] [CrossRef] [PubMed]

- Sanne, A.; Park, S.; Ghosh, R.; Yogeesh, M.N.; Liu, C.; Mathew, L.; Rao, R.; Akinwande, D.; Banerjee, S.K. Embedded gate CVD MoS2 microwave FETs. npj 2D Mater. Appl. 2017, 1, 26. [Google Scholar] [CrossRef]

- Cheng, R.; Jiang, S.; Chen, Y.; Liu, Y.; Weiss, N.O.; Cheng, H.-C.; Wu, H.; Huang, Y.; Duan, X. Few-layer molybdenum disulfide transistors and circuits for high-speed flexible electronics. Nat. Commun. 2014, 5, 514. [Google Scholar] [CrossRef]

- Krasnozhon, D.; Dutta, S.; Nyffeler, C.; Leblebici, Y.; Kis, A. High-frequency, scaled MoS2 transistors. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 27.4.1–27.4.4. [Google Scholar]

- Gao, Q.; Zhang, C.; Yang, K.; Pan, X.; Zhang, Z.; Yang, J.; Yi, Z.; Chi, F.; Liu, L. High-Performance CVD Bilayer MoS2 Radio Frequency Transistors and Gigahertz Mixers for Flexible Nanoelectronics. Micromachines 2021, 12, 451. [Google Scholar] [CrossRef] [PubMed]

- Li, X.; Li, T.; Zhang, Z.; Xiong, X.; Li, S.; Wu, Y. Tunable Low-Frequency Noise in Dual-Gate MoS2 Transistors. IEEE Electron Device Lett. 2017, 39, 131–134. [Google Scholar] [CrossRef]

- Bolshakov, P.; Khosravi, A.; Zhao, P.; Hurley, P.K.; Hinkle, C.L.; Wallace, R.M.; Young, C.D. Dual-gate MoS2 transistors with sub-10 nm top-gate high-k dielectrics. Appl. Phys. Lett. 2018, 112, 253502. [Google Scholar] [CrossRef]

- Lee, G.-H.; Cui, X.; Kim, Y.D.; Arefe, G.; Zhang, X.; Lee, C.-H.; Ye, F.; Watanabe, K.; Taniguchi, T.; Kim, P.; et al. Highly Stable, Dual-Gated MoS2 Transistors Encapsulated by Hexagonal Boron Nitride with Gate-Controllable Contact, Resistance, and Threshold Voltage. ACS Nano 2015, 9, 7019–7026. [Google Scholar] [CrossRef] [PubMed]

- Li, X.-X.; Chen, X.-Y.; Chen, J.-X.; Zeng, G.; Li, Y.-C.; Huang, W.; Ji, Z.-G.; Zhang, D.W.; Lu, H.-L. Dual-gate MoS2 phototransistor with atomic-layer-deposited HfO2 as top-gate dielectric for ultrahigh photoresponsivity. Nanotechnology 2021, 32, 215203. [Google Scholar] [CrossRef]

- Li, X.; Xiong, X.; Li, T.; Li, S.; Zhang, Z.; Wu, Y. Effect of Dielectric Interface on the Performance of MoS2 transistors. ACS Appl. Mater. Interfaces 2017, 9, 44602–44608. [Google Scholar] [CrossRef]

- Lin, Y.-M.; Chiu, H.-Y.; Jenkins, K.A.; Farmer, D.B.; Avouris, P.; Valdes-Garcia, A. Dual-gate graphene FETs with fT of 50 GHz. IEEE Electron Device Lett. 2009, 31, 68–70. [Google Scholar] [CrossRef]

- Zhu, W.; Low, T.; Farmer, D.B.; Jenkins, K.; Ek, B.; Avouris, P. Effect of dual gate control on the alternating current performance of graphene radio frequency device. J. Appl. Phys. 2013, 114, 44307. [Google Scholar] [CrossRef]

- Gao, Q.; Zhang, C.; Yi, Z.; Pan, X.; Chi, F.; Liu, L.; Li, X.; Wu, Y. Improved low-frequency noise in CVD bilayer MoS2 field-effect transistors. Appl. Phys. Lett. 2021, 118, 153103. [Google Scholar] [CrossRef]

- Xiong, X.; Li, X.; Huang, M.; Li, T.; Gao, T.; Wu, Y. High Performance Black Phosphorus Electronic and Photonic Devices with HfLaO Dielectric. IEEE Electron Device Lett. 2017, 39, 127–130. [Google Scholar] [CrossRef]

- Li, S.; Tian, M.; Gao, Q.; Wang, M.; Li, T.; Hu, Q.; Li, X.; Wu, Y. Nanometre-thin indium tin oxide for advanced high-performance electronics. Nat. Mater. 2019, 18, 1091–1097. [Google Scholar] [CrossRef] [PubMed]

- McDonnell, S.; Brennan, B.; Azcatl, A.; Lu, N.; Dong, H.; Buie, C.; Kim, J.; Hinkle, C.L.; Kim, M.J.; Wallace, R.M. HfO2 on MoS2 by Atomic Layer Deposition: Adsorption Mechanisms and Thickness Scalability. ACS Nano 2013, 7, 10354–10361. [Google Scholar] [CrossRef]

- Kim, H.G.; Lee, H.-B.-R. Atomic Layer Deposition on 2D Materials. Chem. Mater. 2017, 29, 3809–3826. [Google Scholar] [CrossRef]

- Wang, H.; Yu, L.; Lee, Y.-H.; Shi, Y.; Hsu, A.; Chin, M.L.; Li, L.-J.; Dubey, M.; Kong, J.; Palacios, T. Integrated Circuits Based on Bilayer MoS2 Transistors. Nano Lett. 2012, 12, 4674–4680. [Google Scholar] [CrossRef]

- Joo, M.-K.; Moon, B.H.; Ji, H.; Han, G.H.; Kim, H.; Lee, G.; Lim, S.C.; Suh, D.; Lee, Y.H. Understanding Coulomb Scattering Mechanism in Monolayer MoS2 Channel in the Presence ofh-BN Buffer Layer. ACS Appl. Mater. Interfaces 2017, 9, 5006–5013. [Google Scholar] [CrossRef]

- Renteria, J.; Samnakay, R.; Rumyantsev, S.; Jiang, C.; Goli, P.; Shur, M.A.; Balandin, A. Low-frequency 1/f noise in MoS2 transistors: Relative contributions of the channel and contacts. Appl. Phys. Lett. 2014, 104, 153104. [Google Scholar] [CrossRef]

- Qing-Guo, G.; Meng-Chuan, T.; Si-Chao, L.; Xue-Fei, L.; Yan-Qing, W. Gigahertz frequency doubler based on millimeter-scale single-crystal graphene. Acta Phys. Sin. 2017, 66, 217305. [Google Scholar] [CrossRef]

- Wu, Y.; Lin, Y.-M.; Bol, A.; Jenkins, K.A.; Xia, F.; Farmer, D.B.; Zhu, Y.; Avouris, P. High-frequency, scaled graphene transistors on diamond-like carbon. Nat. Cell Biol. 2011, 472, 74–78. [Google Scholar] [CrossRef] [PubMed]

- Gummel, H. On the definition of the cutoff frequency fT. Proc. IEEE 1969, 57, 2159. [Google Scholar] [CrossRef]

- Gupta, M. Power gain in feedback amplifiers, a classic revisited. IEEE Trans. Microw. Theory Tech. 1992, 40, 864–879. [Google Scholar] [CrossRef]

- Li, T.; Tian, M.; Li, S.; Huang, M.; Xiong, X.; Hu, Q.; Li, S.; Li, X.; Wu, Y. Black Phosphorus Radio Frequency Electronics at Cryogenic Temperatures. Adv. Electron. Mater. 2018, 4, 1800138. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gao, Q.; Zhang, C.; Liu, P.; Hu, Y.; Yang, K.; Yi, Z.; Liu, L.; Pan, X.; Zhang, Z.; Yang, J.; et al. Effect of Back-Gate Voltage on the High-Frequency Performance of Dual-Gate MoS2 Transistors. Nanomaterials 2021, 11, 1594. https://doi.org/10.3390/nano11061594

Gao Q, Zhang C, Liu P, Hu Y, Yang K, Yi Z, Liu L, Pan X, Zhang Z, Yang J, et al. Effect of Back-Gate Voltage on the High-Frequency Performance of Dual-Gate MoS2 Transistors. Nanomaterials. 2021; 11(6):1594. https://doi.org/10.3390/nano11061594

Chicago/Turabian StyleGao, Qingguo, Chongfu Zhang, Ping Liu, Yunfeng Hu, Kaiqiang Yang, Zichuan Yi, Liming Liu, Xinjian Pan, Zhi Zhang, Jianjun Yang, and et al. 2021. "Effect of Back-Gate Voltage on the High-Frequency Performance of Dual-Gate MoS2 Transistors" Nanomaterials 11, no. 6: 1594. https://doi.org/10.3390/nano11061594

APA StyleGao, Q., Zhang, C., Liu, P., Hu, Y., Yang, K., Yi, Z., Liu, L., Pan, X., Zhang, Z., Yang, J., & Chi, F. (2021). Effect of Back-Gate Voltage on the High-Frequency Performance of Dual-Gate MoS2 Transistors. Nanomaterials, 11(6), 1594. https://doi.org/10.3390/nano11061594