An Organic/Inorganic Nanomaterial and Nanocrystal Quantum Dots-Based Multi-Level Resistive Memory Device

Abstract

:1. Introduction

2. Experimental Section

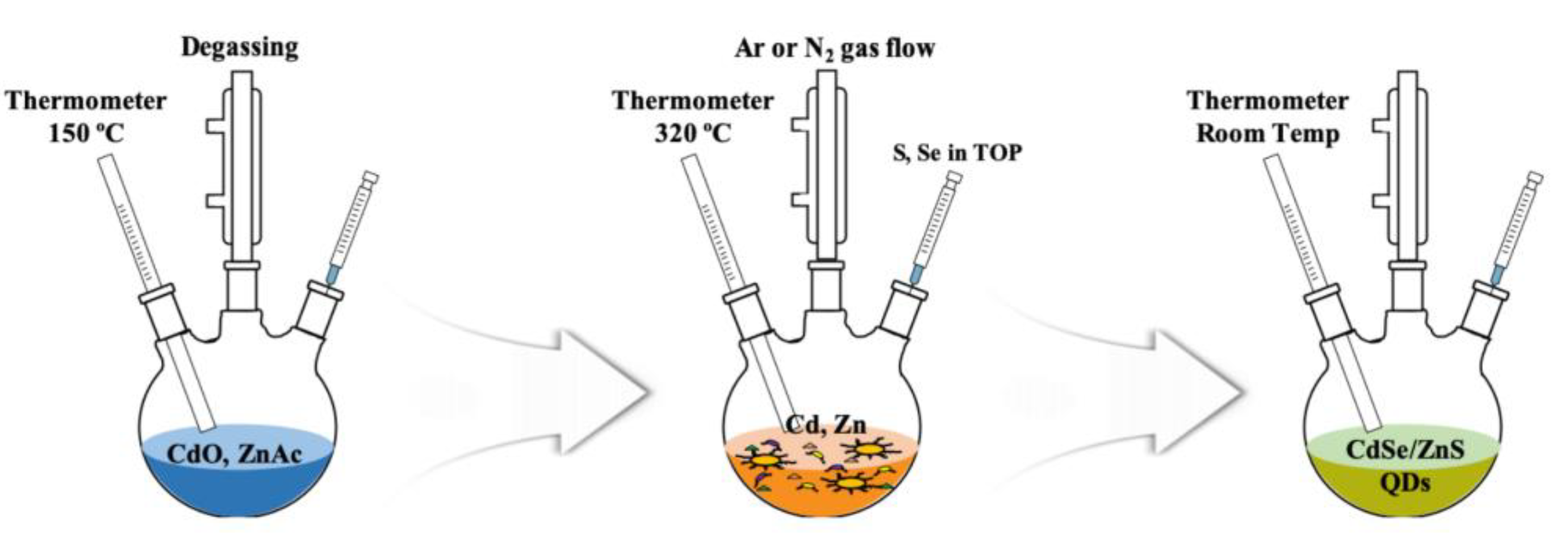

2.1. Synthesis of Colloidal Quantum Dots (QDs)

2.2. Synthesis of Semiconductor Nanocrystal ZnO Nanoparticles (NPs)

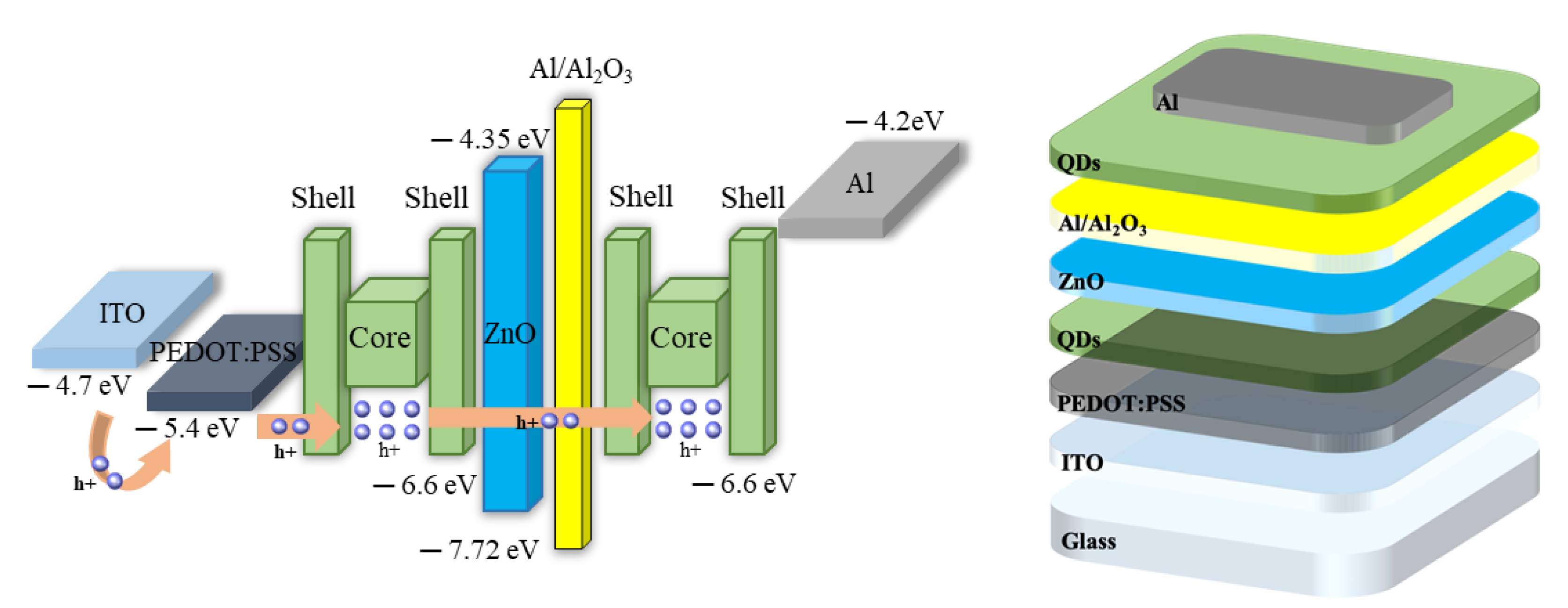

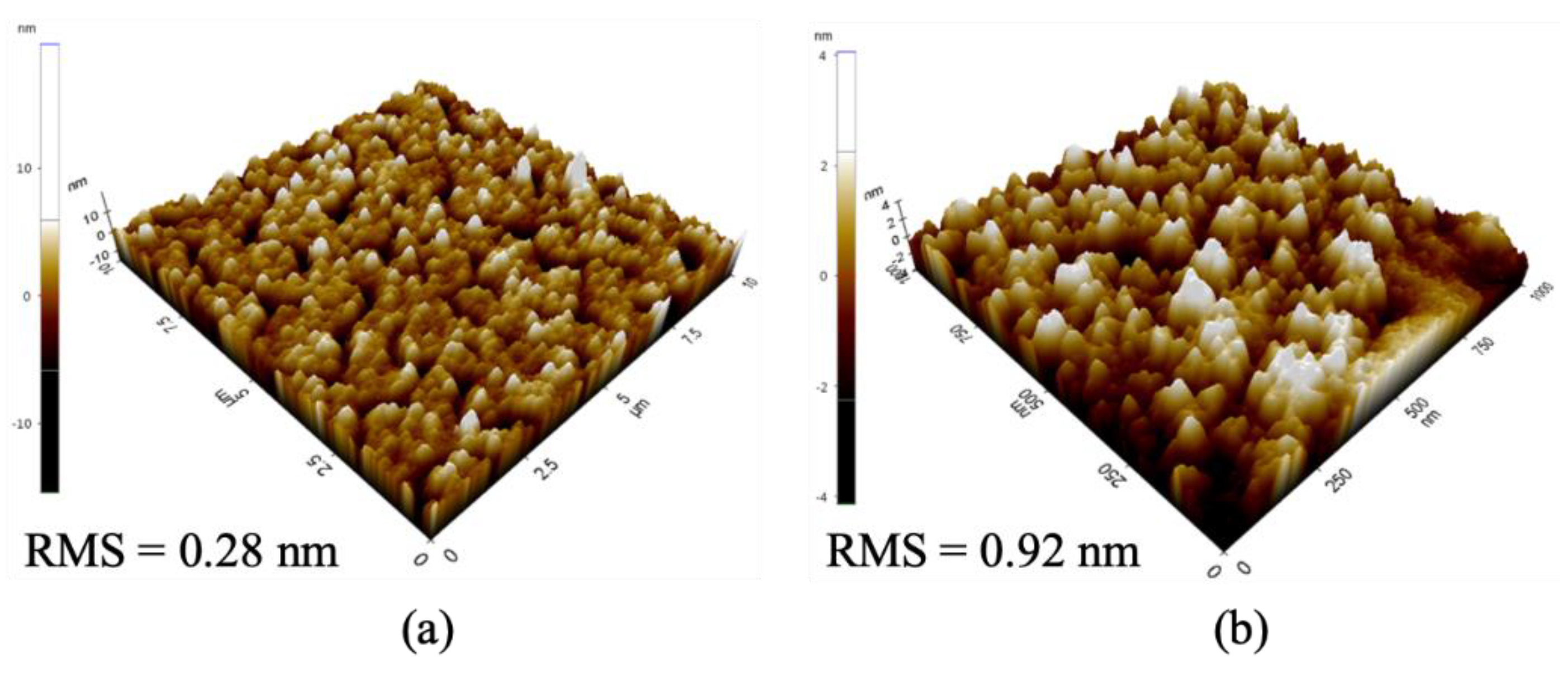

2.3. Formation of QDs/Al Nanocluster Based Memory Device

3. Results and Discussion

3.1. Optical and Physical Properties of the Synthesized QDs

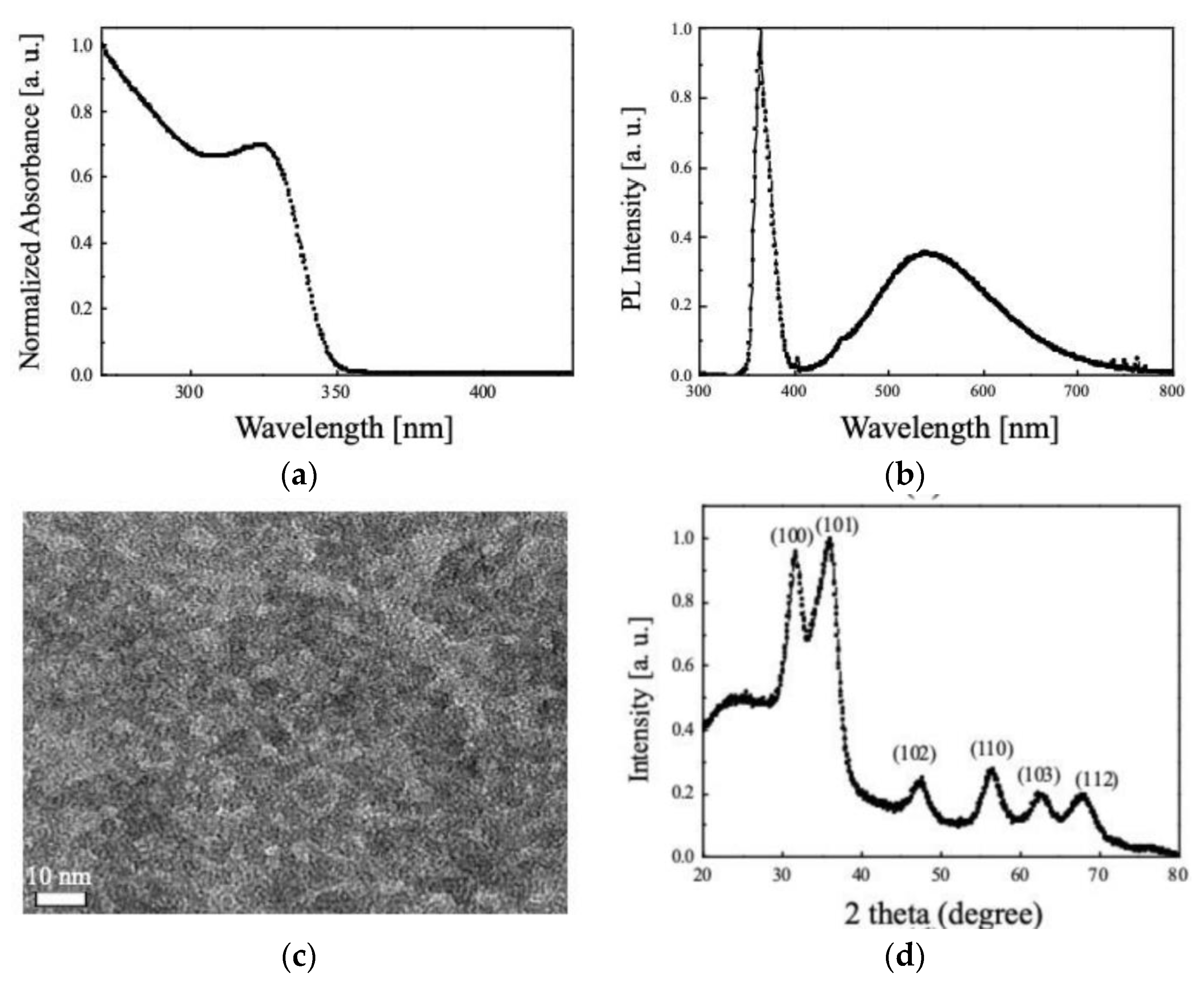

3.2. Properties of the Synthesized ZnO NPs

3.3. Nanocluster(NC) Verification

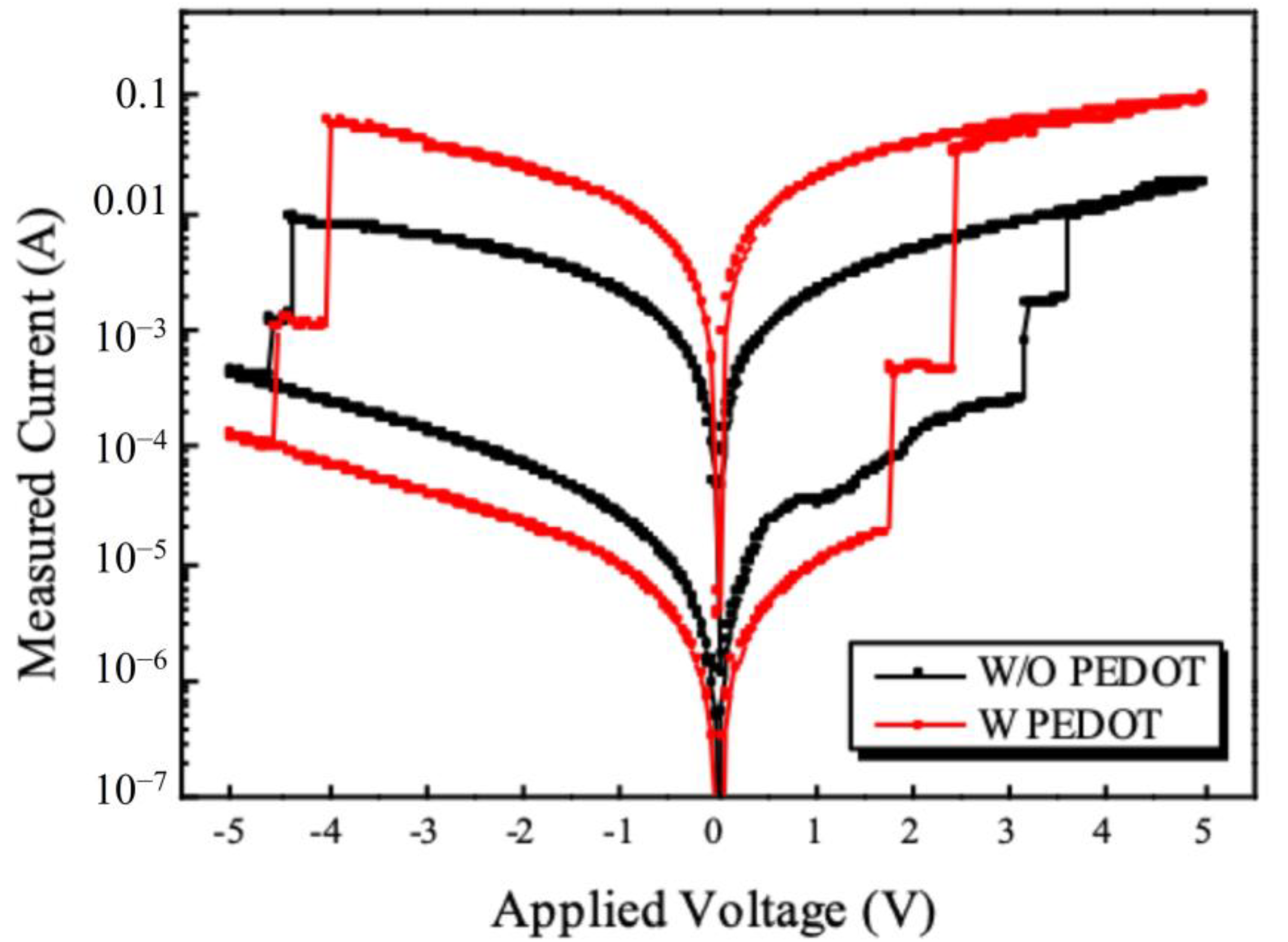

3.4. I-V Properties of Fabricated Memory Devices

3.5. Retention Properties

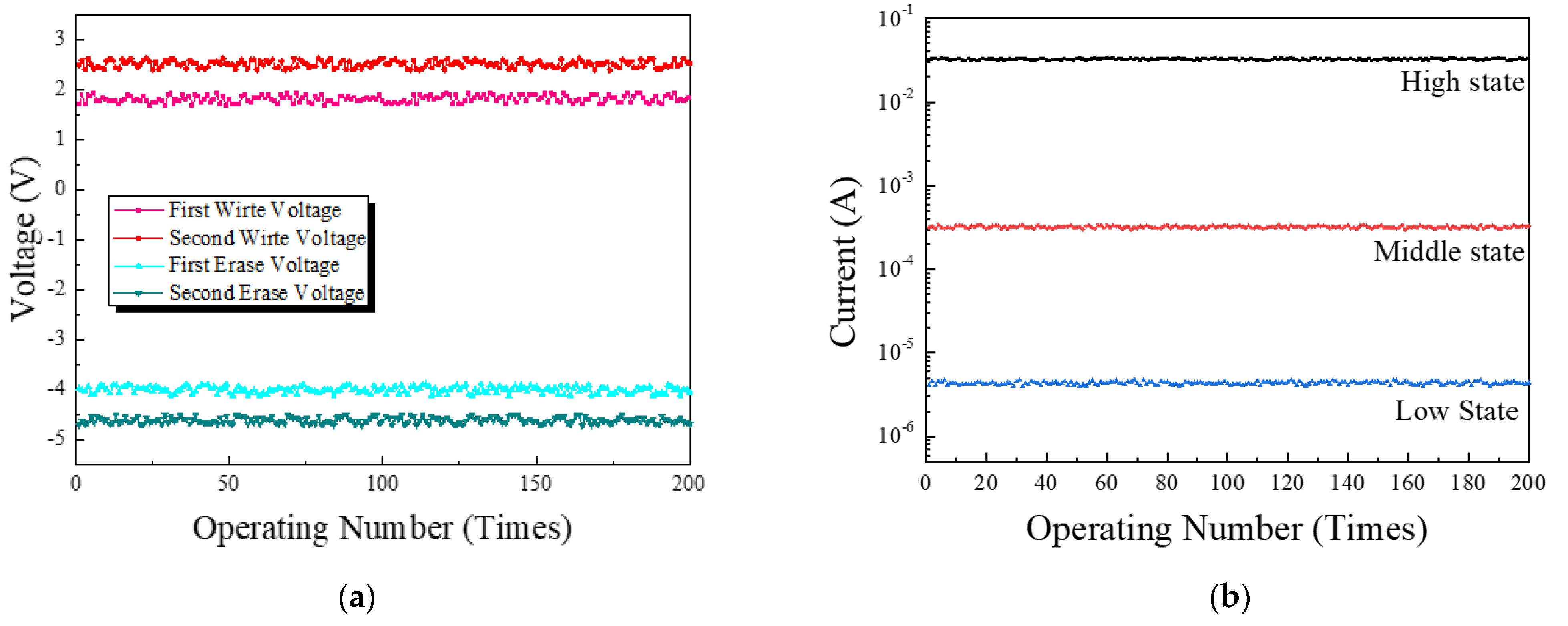

3.6. Robustness Properties

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Evans, D. The Internet of Things How the Next Evolution of the Internet Is Changing Everything. Cisco IBSG White Paper. 2011. Available online: http://www.cisco.com/web/about/ac79/docs/innov/IoT_IBSG_0411FINAL.pdf (accessed on 4 November 2021).

- Reinsel, D.; Gantz, J.; Rydning, J. The Digitization of the World from Edge to Core. IDC White Paper. 2018. Available online: https://resources.moredirect.com/white-papers/idc-report-the-digitization-of-the-world-from-edge-to-core (accessed on 4 November 2021).

- Yun, D.Y.; Song, W.S.; Kim, T.W.; Kim, S.W.; Kim, S.W. Electrical stabilities and carrier transport mechanism of flexible organic bistable devices based on CdSe-InP core-shell nanoparticle/polystyrene nanocomposites. Appl. Phys. Lett. 2012, 101, 103305–103309. [Google Scholar] [CrossRef]

- Wu, C.; Kim, T.W.; Choi, H.Y.; Strukov, D.B.; Yang, J.J. Flexible three-dimensional artificial synapse networks with correlated learning and trainable memory capability. Nat. Commun. 2017, 8, 752. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Wong, H.-S.P.; Salahuddin, S. Memory leads the way to better computing. Nat. Nanotechnol. 2015, 10, 191–194. [Google Scholar] [CrossRef] [Green Version]

- Yu, S. Resistive Random Access Memory (RRAM) from Device to Array Architectures; Morgan & Claypool: San Rafael, CA, USA, 2016. [Google Scholar]

- Hu, J.-M.; Li, Z.; Chen, L.-Q.; Nan, C.-W. High-density magnetoresistive random access memory operating at ultralow voltage at room temperature. Nat. Commun. 2011, 2, 553. [Google Scholar] [CrossRef] [PubMed]

- Salinga, M.; Kersting, B.; Ronneberger, I.; Jonnalagadda, V.P.; Vu, X.T.; Le Gallo, M.; Giannopoulos, I.; Cojocaru-Mirédin, O.; Mazzarello, R.; Sebastian, A. Monatomic phase change memory. Nat. Mater. 2018, 17, 681–686. [Google Scholar] [CrossRef]

- Wong, H.S.; Lee, H.Y.; Yu, S.; Chen, Y.S.; Wu, Y.; Chen, P.S.; Lee, B.G.; Chen, F.T.; Tsai, M.J. Metal-oxide RRAM. Proc. IEEE 2012, 100, 1951–1970. [Google Scholar] [CrossRef]

- Bousoulas, P.; Giannopoulos, I.; Asenov, P.; Karageorgiou, I.; Tsoukalas, D. Investigating the origins of high multilevel resistive switching in forming free Ti/TiO2−x-based memory devices through experiments and simulations. J. Appl. Phys. 2017, 121, 094501–094509. [Google Scholar] [CrossRef]

- Seo, S.; Lee, M.-J.; Seo, D.H.; Jeoung, E.J.; Suh, D.-S.; Joung, Y.S.; Yoo, I.K.; Hwang, I.R.; Kim, S.H.; Byun, I.S.; et al. Reproducible resistance switching in polycrystalline NiO films. Appl. Phys. Lett. 2004, 85, 5655–5657. [Google Scholar] [CrossRef]

- Choi, B.J.; Jeong, D.S.; Kim, S.K.; Rohde, C.; Choi, S.; Oh, J.H.; Kim, H.J.; Hwang, C.S.; Szot, K.; Waser, R.; et al. Resistive switching mechanism of TiO2 thin films grown by atomic-layer deposition. J. Appl. Phys. 2005, 98, 033715–033724. [Google Scholar] [CrossRef] [Green Version]

- Choi, J.-Y.; Lee, J.; Jeon, J.; Im, J.; Jang, J.; Jin, S.-W.; Joung, H.; Yu, H.-C.; Nam, K.-N.; Park, H.-J.; et al. High-performance non-volatile resistive switching memory based on a polyimide/graphene oxide nanocomposite. Polym. Chem. 2020, 11, 7685–7695. [Google Scholar] [CrossRef]

- Lin, C.Y.; Wu, C.Y.; Wu, C.Y.; Tseng, T.Y. Modified resistive switching behavior of ZrO2 memory films based on the interface layer formed by using Ti top electrode. J. Appl. Phys. 2007, 102, 094101–094105. [Google Scholar] [CrossRef]

- Lee, H.Y.; Chen, P.S.; Wu, T.Y.; Chen, Y.S.; Wang, C.C.; Tzeng, P.J.; Lin, C.H.; Chen, F.; Lien, C.H.; Tasi, M.J. Low power and high speed bipolar switching with a thin reactive Ti buffer layer in robust HfO2 based RRAM. In Proceedings of the 2008 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 14–17 December 2008; pp. 1–4. [Google Scholar]

- Kang, B.-H.; Seo, J.-S.; Jeong, S.; Lee, J.; Han, C.-S.; Kim, D.-E.; Kim, K.-J.; Yeom, S.-H.; Kwon, D.-H.; Kim, H.-R.; et al. Highly efficient hybrid light-emitting device using complex of CdSe/ZnS quantum dots embedded in co-polymer as an active layer. Opt. Express 2010, 18, 18303–18311. [Google Scholar] [CrossRef]

- Bang, J.H.; Kamat, P.V. CdSe Quantum Dot–Fullerene Hybrid Nanocomposite for Solar Energy Conversion: Electron Transfer and Photoelectrochemistry. ACS Nano 2011, 5, 9421–9427. [Google Scholar] [CrossRef]

- Ooi, P.C.; Lin, J.; Kim, T.W.; Li, F. Indium-tin-oxide, free, flexible, nonvolatile memory devices based on graphene quantum dots sandwiched between polymethylsilsesquioxane layers. Org. Electron. 2016, 32, 115–119. [Google Scholar] [CrossRef]

- Kim, T.W.; Yang, Y.; Li, F.; Kwan, W.L. Electrical memory devices based on inorganic/organic nanocomposites. NPG Asia Mater. 2012, 4, 18–29. [Google Scholar] [CrossRef] [Green Version]

- Lu, Z.; Klein, B.; Zunger, A. Thermodynamic instability of Ag/Au and Cu/Pd metal superlattices. Superlattices Microstruct. 1995, 18, 161–175. [Google Scholar] [CrossRef]

- Peng, Z.A.; Peng, X. Nearly Monodisperse and Shape-Controlled CdSe Nanocrystals via Alternative Routes: Nucleation and Growth. J. Am. Chem. Soc. 2002, 124, 3343–3353. [Google Scholar] [CrossRef]

- Kannan, V.; Rhee, J.K. Robust switching characteristics of CdSe/ZnS quantum dot non-volatile memory devices. Phys. Chem. Chem. Phys. 2013, 15, 12762–12766. [Google Scholar] [CrossRef] [PubMed]

- Bok, H.; Wu, C.; Kim, T.W. Operating mechanism of highly-reproducible write-once-readmany-times memory devices based on graphene quantum dot:poly (methylsilsesquioxane) nanocomposites. Appl. Phys. Lett. 2017, 110, 013301–013304. [Google Scholar] [CrossRef]

- Yun, D.Y.; Park, H.M.; Kim, S.W.; Kim, S.W.; Kim, T.W. Enhancement of memory margins for stable organic bistable devices based on graphene-oxide layers due to embedded CuInS2 quantum dots. Carbon 2014, 75, 244–248. [Google Scholar] [CrossRef]

- Shim, J.H.; Jung, J.H.; Lee, M.H.; Kim, T.W.; Son, D.I.; Na Han, A.; Kim, S.W. Memory mechanisms of nonvolatile organic bistable devices based on colloidal CuInS2/ZnS core–shell quantum dot–Poly(N-vinylcarbazole) nanocomposites. Org. Electron. 2011, 12, 1566–1570. [Google Scholar] [CrossRef]

- Kundu, S.; Halder, N.N.; Biswas, P.; Biswas, D.; Banerji, P.; Mukherjee, R.; Chakraborty, S. Charge storage properties of InP quantum dots in GaAs metal-oxide-semiconductor based nonvolatile flash memory devices. Appl. Phys. Lett. 2012, 101, 212108–212111. [Google Scholar] [CrossRef]

- Kim, S.W.; Kwon, J.B.; Kim, N.R.; Lee, J.S.; Lee, S.W.; Kang, B.H.; Kim, J.S.; Xu, B.; Bae, J.H.; Kang, S.W. Stable hybrid or-ganic/inorganic multiple-read quantum-dot memory device based on a PVK/QDs solution. Appl. Surf. Sci. 2019, 481, 25–32. [Google Scholar] [CrossRef]

- Kim, S.-W.; Jung, I.-S.; Kang, B.-H.; Kwon, J.-B.; Lee, J.-S.; Lee, S.-W.; Kim, O.-S.; Kim, J.-S.; Bae, J.-H.; Kang, S.-W. Facile and One-step Processible CdSe/ZnS Quantum Dots and Pentacene-based Nonvolatile Memory Device. J. Semicond. Technol. Sci. 2018, 18, 180–186. [Google Scholar] [CrossRef]

- Waser, R.; Aono, M. Nanoionics-based resistive switching memories. Nat. Mater. 2007, 6, 833–840. [Google Scholar] [CrossRef]

- Bhattacharjee, S.; Das, J.; Sarkar, P.K.; Roy, A. Stable charge retention in graphene-MoS2 assemblies for resistive switching effect in ultra-thin super-flexible organic memory devices. Org. Electron. 2018, 58, 145–152. [Google Scholar] [CrossRef]

- Geller, M.; Marent, A.; Nowozin, T.; Bimberg, D.; AKÇAY, N.; Öncan, N. A write time of 6ns for quantum dot–based memory structures. Appl. Phys. Lett. 2008, 92, 092108–092110. [Google Scholar] [CrossRef]

- Sung, S.; Wu, C.; Jung, H.S.; Kim, T.W. Highly-stable write-once-read-many-times switching behaviors of 1D–1R memristive devices based on graphene quantum dot nanocomposites. Sci. Rep. 2018, 8, 12081–12087. [Google Scholar] [CrossRef] [Green Version]

- Chen, Z.; Zhang, Y.; Zhang, H.; Yu, Y.; Song, X.; Zhang, H.; Cao, M.; Che, Y.; Jin, L.; Li, Y.; et al. Low-voltage all-inorganic perovskite quantum dot transistor memory. Appl. Phys. Lett. 2018, 112, 212101–212105. [Google Scholar] [CrossRef]

- Ooi, P.; Aw, K.; Razak, K.; Makhsin, S.R.; Gao, W. Effects of metal electrodes and dielectric thickness on non-volatile memory with embedded gold nanoparticles in polymethylsilsesquioxane. Microelectron. Eng. 2012, 98, 74–79. [Google Scholar] [CrossRef]

- Zhang, Y.; Zu, F.; Lee, S.-T.; Liao, L.; Zhao, N.; Sun, B. Heterojunction with Organic Thin Layers on Silicon for Record Efficiency Hybrid Solar Cells. Adv. Energy Mater. 2014, 4, 1300923–1300929. [Google Scholar] [CrossRef]

- Erickson, A.S.; Kedem, N.K.; Haj-Yahia, A.E.; Cahen, D. Aluminum oxide–n-Si field effect inversion layer solar cells with organic top contact. Appl. Phys. Lett. 2012, 101, 233901–233919. [Google Scholar] [CrossRef] [Green Version]

- Zhang, F.; Han, X.; Lee, S.-T.; Sun, B. Heterojunction with organic thin layer for three dimensional high performance hybrid solar cells. J. Mater. Chem. 2012, 22, 5362–5368. [Google Scholar] [CrossRef]

- He, L.; Jiang, C.; Rusli; Lai, D.; Wang, H. Highly efficient Si-nanorods/organic hybrid core-sheath heterojunction solar cells. Appl. Phys. Lett. 2011, 99, 021104. [Google Scholar] [CrossRef]

- Kim, J.-S.; Kang, B.-H.; Jeong, H.-M.; Kim, S.-W.; Xu, B.; Kang, S.-W. Quantum dot light emitting diodes using size-controlled ZnO NPs. Curr. Appl. Phys. 2018, 18, 681–685. [Google Scholar] [CrossRef]

- Xu, B.; Sai-Anand, G.; Unni, G.E.; Jeong, H.-M.; Kim, J.-S.; Kim, S.-W.; Kwon, J.-B.; Bae, J.-H.; Kang, S.-W. Pyridine-based additive optimized P3HT:PC61BM nanomorphology for improved performance and stability in polymer solar cells. Appl. Surf. Sci. 2019, 484, 825–834. [Google Scholar] [CrossRef]

- Bae, W.K.; Lim, J.; Lee, D.; Park, M.; Lee, H.; Kwak, J.; Char, K.; Lee, C.; Lee, S. R/G/B/Natural White Light Thin Colloidal Quantum Dot-Based Light-Emitting Devices. Adv. Mater. 2014, 26, 6387–6393. [Google Scholar] [CrossRef]

- Zhang, H.; Su, Q.; Chen, S. Quantum-dot and organic hybrid tandem light-emitting diodes with multi-functionality of full-color-tunability and white-light-emission. Nat. Commun. 2020, 11, 2826–2833. [Google Scholar] [CrossRef] [PubMed]

- Kang, B.-H.; Lee, J.-S.; Lee, S.-W.; Kim, S.-W.; Lee, J.-W.; Gopalan, S.; Park, J.-S.; Kwon, D.-H.; Bae, J.-H.; Kim, H.-R.; et al. Efficient exciton generation in atomic passivated CdSe/ZnS quantum dots light-emitting devices. Sci. Rep. 2016, 6, 34659. [Google Scholar] [CrossRef] [Green Version]

- Kumaresan, N.; Ramamurthi, K.; Babu, R.R.; Sethuraman, K.; Babu, S.M. Hydrothermally grown ZnO nanoparticles for effective photocatalytic activity. Appl. Surf. Sci. 2017, 418, 138–146. [Google Scholar] [CrossRef]

- Kannan, V.; Chae, Y.S.; Ramana, C.V.V.; Ko, D.-S.; Rhee, J.K. All-inorganic spin-cast quantum dot based bipolar nonvolatile resistive memory. J. Appl. Phys. 2011, 109, 086103–086105. [Google Scholar] [CrossRef]

- Lee, J.-S.; Kang, B.-H.; Kim, S.-W.; Kwon, J.-B.; Kim, O.-S.; Byun, Y.T.; Kwon, D.-H.; Bae, J.-H.; Kang, S.-W. Al atomistic surface modulation on colloidal gradient quantum dots for high-brightness and stable light-emitting devices. Sci. Rep. 2019, 9, 1–9. [Google Scholar]

- Kannan, V.; Rhee, J.K. A solution processed nonvolatile resistive memory device with Ti/CdSe quantum/Ti-TiOx/CdSe quantum dot/indium tin-oxide structure. J. Appl. Phys. 2011, 110, 074505–074508. [Google Scholar] [CrossRef]

- Gao, Y.; Zhang, Q.; Gao, Q.; Tian, Y.; Zhou, W.; Zheng, L.; Zhang, S. Synthesis of high quality CdSe quantum dots through a mild solution-phase synthetic route. Mater. Chem. Phys. 2009, 115, 724–727. [Google Scholar] [CrossRef]

- Kim, N.-R.; Kim, S.-W.; Bae, J.-H.; Kang, S.-W. Multi-level resistive write-once-read-many memory device based on CdSe/ZnS quantum dots and ZnO nanoparticles. Thin Solid Films 2020, 709, 138120–138129. [Google Scholar] [CrossRef]

- Meulenkamp, E.A. Synthesis and Growth of ZnO Nanoparticles. J. Phys. Chem. B 1998, 102, 5566–5572. [Google Scholar] [CrossRef]

- Musić, S.; Šarić, A. Formation of hollow ZnO particles by simple hydrolysis of zinc acetylacetonate. Ceram. Int. 2012, 38, 6047–6052. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, S.-W.; Kwon, J.; Lee, J.-S.; Kang, B.-H.; Lee, S.-W.; Jung, D.G.; Lee, J.-Y.; Han, M.; Kim, O.-G.; Saianand, G.; et al. An Organic/Inorganic Nanomaterial and Nanocrystal Quantum Dots-Based Multi-Level Resistive Memory Device. Nanomaterials 2021, 11, 3004. https://doi.org/10.3390/nano11113004

Kim S-W, Kwon J, Lee J-S, Kang B-H, Lee S-W, Jung DG, Lee J-Y, Han M, Kim O-G, Saianand G, et al. An Organic/Inorganic Nanomaterial and Nanocrystal Quantum Dots-Based Multi-Level Resistive Memory Device. Nanomaterials. 2021; 11(11):3004. https://doi.org/10.3390/nano11113004

Chicago/Turabian StyleKim, Sae-Wan, JinBeom Kwon, Jae-Sung Lee, Byoung-Ho Kang, Sang-Won Lee, Dong Geon Jung, Jun-Yeop Lee, Maeum Han, Ok-Geun Kim, Gopalan Saianand, and et al. 2021. "An Organic/Inorganic Nanomaterial and Nanocrystal Quantum Dots-Based Multi-Level Resistive Memory Device" Nanomaterials 11, no. 11: 3004. https://doi.org/10.3390/nano11113004

APA StyleKim, S.-W., Kwon, J., Lee, J.-S., Kang, B.-H., Lee, S.-W., Jung, D. G., Lee, J.-Y., Han, M., Kim, O.-G., Saianand, G., & Jung, D. (2021). An Organic/Inorganic Nanomaterial and Nanocrystal Quantum Dots-Based Multi-Level Resistive Memory Device. Nanomaterials, 11(11), 3004. https://doi.org/10.3390/nano11113004