Significant Performance and Stability Improvements of Low-Temperature IGZO TFTs by the Formation of In-F Nanoparticles on an SiO2 Buffer Layer

Abstract

1. Introduction

2. Materials and Methods

3. Results and Discussions

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef]

- Yabuta, H.; Sano, M.; Abe, K.; Aiba, T.; Den, T.; Kumomi, H.; Nomura, K.; Kamiya, T.; Hosono, H. High-mobility thin-film transistor with amorphous InGaZnO4 channel fabricated by room temperature rf-magnetron sputtering. Appl. Phys. Lett. 2006, 89, 112123. [Google Scholar] [CrossRef]

- Kamiya, T.; Nomura, K.; Hosono, H. Present status of amorphous In–Ga–Zn–O thin-film transistors. Sci. Technol. Adv. Mater. 2010, 11, 044305. [Google Scholar] [CrossRef] [PubMed]

- Mativenga, M.; Choi, M.H.; Choi, J.W.; Jang, J. Transparent Flexible Circuits Based on Amorphous-Indium–Gallium–Zinc–Oxide Thin-Film Transistors. IEEE Electron Device Lett. 2011, 32, 170–172. [Google Scholar] [CrossRef]

- Wu, C.W.; Yoo, S.Y.; Ning, C.; Yang, W.; Shang, G.L.; Wang, K.; Liu, C.H.; Liu, X.; Yuan, G.C.; Chen, J.; et al. Improvement of Stability on a-IGZO LCD. SID Symp. Dig. Tech. Pap. 2013, 44, 97–99. [Google Scholar] [CrossRef]

- Oh, S.; Baeck, J.H.; Lee, D.; Park, T.; Shin, H.S.; Bae, J.U.; Park, K.S.; Kang, I.B. Improvement of PBTS Stability in Self-Aligned Coplanar a-IGZO TFTs. SID Symp. Dig. Tech. Pap. 2015, 46, 1143–1146. [Google Scholar] [CrossRef]

- Nag, M.; Roose, F.D.; Myny, K.; Steudel, S.; Genoe, J.; Groeseneken, G.; Heremans, P. Characteristics improvement of top-gate self-aligned amorphous indium gallium zinc oxide thin-film transistors using a dual-gate control. J. Soc. Inf. Disp. 2017, 25, 349–355. [Google Scholar] [CrossRef]

- Rahaman, A.; Chen, Y.; Hasan, M.M.; Jang, J. A High Performance Operational Amplifier Using Coplanar Dual Gate a-IGZO TFTs. IEEE J. Electron Devices Soc. 2019, 7, 655–661. [Google Scholar] [CrossRef]

- Kang, D.H.; Kang, I.; Ryu, S.H.; Jang, J. Self-Aligned Coplanar a-IGZO TFTs and Application to High Circuits. IEEE Electron Device Lett. 2011, 32, 1385–1387. [Google Scholar] [CrossRef]

- Wu, C.H.; Hsieh, H.H.; Chien, C.W.; Wu, C.C. Self-Aligned Top-Gate Coplanar In-Ga-Zn-O Thin-Film Transistors. J. Disp. Technol. 2009, 5, 515–519. [Google Scholar] [CrossRef]

- Geng, D.; Kang, D.H.; Seok, M.J.; Mativenga, M.; Jang, J. High-Speed and Low-Voltage-Driven Shift Register with Self-Aligned Coplanar a-IGZO TFTs. IEEE Electron Device Lett. 2012, 33, 1012–1014. [Google Scholar] [CrossRef]

- Choi, S.; Han, M. Effect of Deposition Temperature of SiOx Passivation Layer on the Electrical Performance of a-IGZO TFTs. IEEE Electron Device Lett. 2012, 33, 396–398. [Google Scholar] [CrossRef]

- Ha, C.; Lee, H.J.; Kwon, J.W.; Seok, S.Y.; Ryoo, C.I.; Yun, K.Y.; Kim, B.C.; Shin, W.S.; Cha, S.Y. High Reliable a-IGZO TFTs with Self-Aligned Coplanar Structure for Large-Sized Ultrahigh-Definition OLED TV. SID Symp. Dig. Tech. Pap. 2015, 46, 1020–1022. [Google Scholar] [CrossRef]

- Shin, H.J.; Takasugi, S.; Park, K.M.; Choi, S.H.; Jeong, Y.S.; Song, B.C.; Kim, H.S.; Oh, C.H.; Ahn, B.C. Novel OLED Display Technologies for Large-Size UHD OLED TVs. SID Symp. Dig. Tech. Pap. 2015, 46, 53–56. [Google Scholar] [CrossRef]

- Yoon, J.S.; Hong, S.J.; Kim, J.H.; Kim, D.H.; Ryosuke, T.; Nam, W.J.; Song, B.C.; Kim, J.M.; Kim, P.Y.; Park, K.H.; et al. 55-inch OLED TV using Optimal Driving Method for Large-Size Panel based on InGaZnO TFTs. SID Symp. Dig. Tech. Pap. 2014, 58, 849–852. [Google Scholar] [CrossRef]

- Arai, T. The Advantages of the Self-Aligned Top Gate Oxide TFT Technology for AM-OLED Displays. SID Symp. Dig. Tech. Pap. 2015, 46, 1016–1019. [Google Scholar] [CrossRef]

- Ryu, M.K.; Park, S.H.K.; Hwang, C.S.; Yoon, S.M. Comparative studies on electrical bias temperature instabilities of In–Ga–Zn–O thin film transistors with different device configurations. Solid-State Electron. 2013, 89, 171–176. [Google Scholar] [CrossRef]

- Jiang, J.; Toda, T.; Hung, M.P.; Wang, D.; Furuta, M. Highly stable fluorine-passivated In-Ga-Zn-O thin-film transistors under positive gate bias and temperature stress. Appl. Phys. Express 2014, 7, 114103. [Google Scholar] [CrossRef]

- Jiang, J.; Tatsuya, T.; Tatsuoka, G.; Wang, D.; Furuta, M. Improvement of Electrical Properties and Bias Stability of InGaZnO Thin-Film Transistors by Fluorinated Silicon Nitride Passivation. {ECS} Trans. 2014, 64, 59–64. [Google Scholar] [CrossRef]

- Yamazaki, H.; Ishikawa, Y.; Fujii, M.; Ueoka, Y.; Fujiwara, M.; Takahashi, E.; Andoh, Y.; Maejima, N.; Matsui, H.; Matsui, F.; et al. The Influence of Fluorinated Silicon Nitride Gate Insulator on Positive Bias Stability toward Highly Reliable Amorphous InGaZnO Thin-Film Transistors. {ECS} J. Solid State Sci. Technol. 2013, 3, 20–23. [Google Scholar] [CrossRef]

- Um, J.G.; Jang, J. Heavily doped n-type a-IGZO by F plasma treatment and its thermal stability up to 600 °C. Appl. Phys. Lett. 2018, 112, 162104. [Google Scholar] [CrossRef]

- Lee, S.; Shin, J.; Jang, J. Top Interface Engineering of Flexible Oxide Thin-Film Transistors by Splitting Active Layer. Adv. Funct. Mater. 2017, 27, 1604921. [Google Scholar] [CrossRef]

- Jeong, H.Y.; Lee, B.Y.; Lee, Y.J.; Lee, J.I.; Yang, M.S.; Kang, I.B.; Mativenga, M.; Jang, J. Coplanar amorphous-indium-gallium-zinc-oxide thin film transistor with He plasma treated heavily doped layer. Appl. Phys. Lett. 2014, 104, 022115. [Google Scholar] [CrossRef]

- Otten, M.T. High-Angle annular dark-field imaging on a tem/stem system. J. Electron Microsc. Tech. 1991, 17, 221–230. [Google Scholar] [CrossRef]

- Herbig, M.; Choi, P.; Raabe, D. Combining structural and chemical information at the nanometer scale by correlative transmission electron microscopy and atom probe tomography. Ultramicroscopy 2015, 153, 32–39. [Google Scholar] [CrossRef]

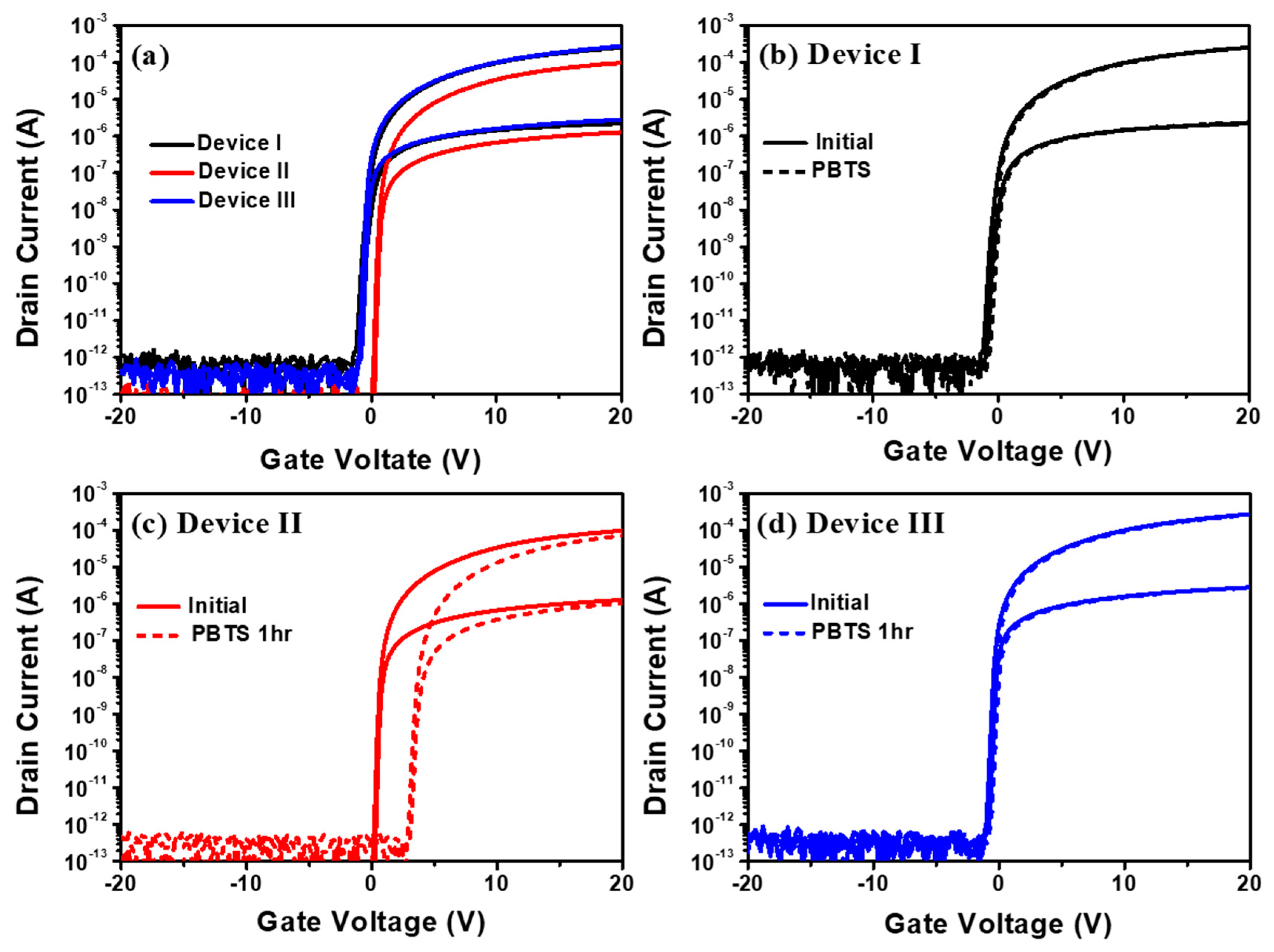

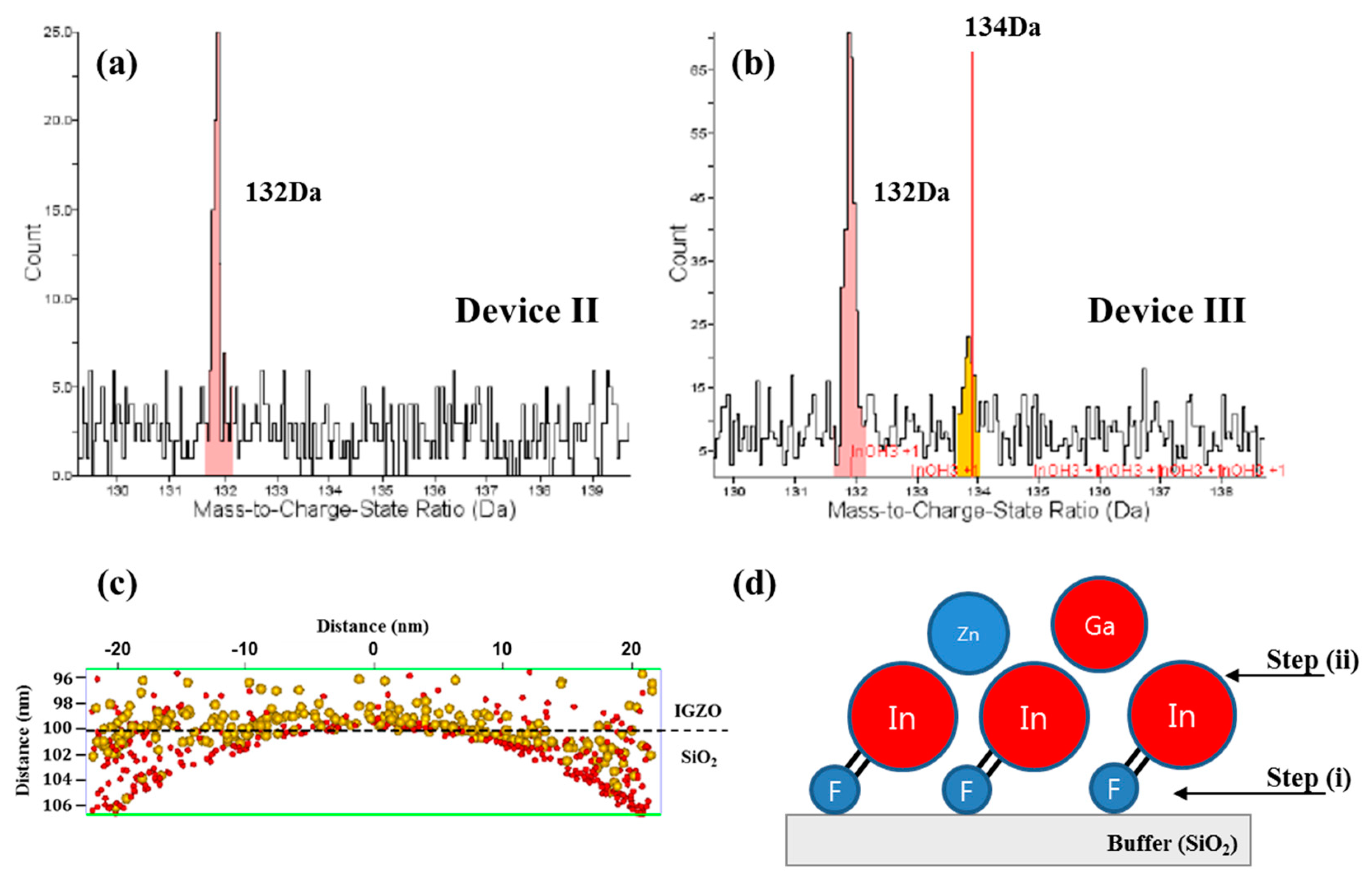

| Vth (V) | µFE (cm2/V·s) | SS (mV/dec) | ΔVth (V) | |

|---|---|---|---|---|

| Device I | 0.0 | 9.2 | 181 | 0.2 |

| Device II | 1.1 | 3.8 | 109 | 3.2 |

| Device III | −0.2 | 9.0 | 139 | 0.2 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jeong, H.-y.; Nam, S.-h.; Park, K.-s.; Yoon, S.-y.; Park, C.; Jang, J. Significant Performance and Stability Improvements of Low-Temperature IGZO TFTs by the Formation of In-F Nanoparticles on an SiO2 Buffer Layer. Nanomaterials 2020, 10, 1165. https://doi.org/10.3390/nano10061165

Jeong H-y, Nam S-h, Park K-s, Yoon S-y, Park C, Jang J. Significant Performance and Stability Improvements of Low-Temperature IGZO TFTs by the Formation of In-F Nanoparticles on an SiO2 Buffer Layer. Nanomaterials. 2020; 10(6):1165. https://doi.org/10.3390/nano10061165

Chicago/Turabian StyleJeong, Ho-young, Seung-hee Nam, Kwon-shik Park, Soo-young Yoon, Chanju Park, and Jin Jang. 2020. "Significant Performance and Stability Improvements of Low-Temperature IGZO TFTs by the Formation of In-F Nanoparticles on an SiO2 Buffer Layer" Nanomaterials 10, no. 6: 1165. https://doi.org/10.3390/nano10061165

APA StyleJeong, H.-y., Nam, S.-h., Park, K.-s., Yoon, S.-y., Park, C., & Jang, J. (2020). Significant Performance and Stability Improvements of Low-Temperature IGZO TFTs by the Formation of In-F Nanoparticles on an SiO2 Buffer Layer. Nanomaterials, 10(6), 1165. https://doi.org/10.3390/nano10061165