A Methodology to Distribute On-Chip Voltage Regulators to Improve the Security of Hardware Masking

Abstract

1. Introduction

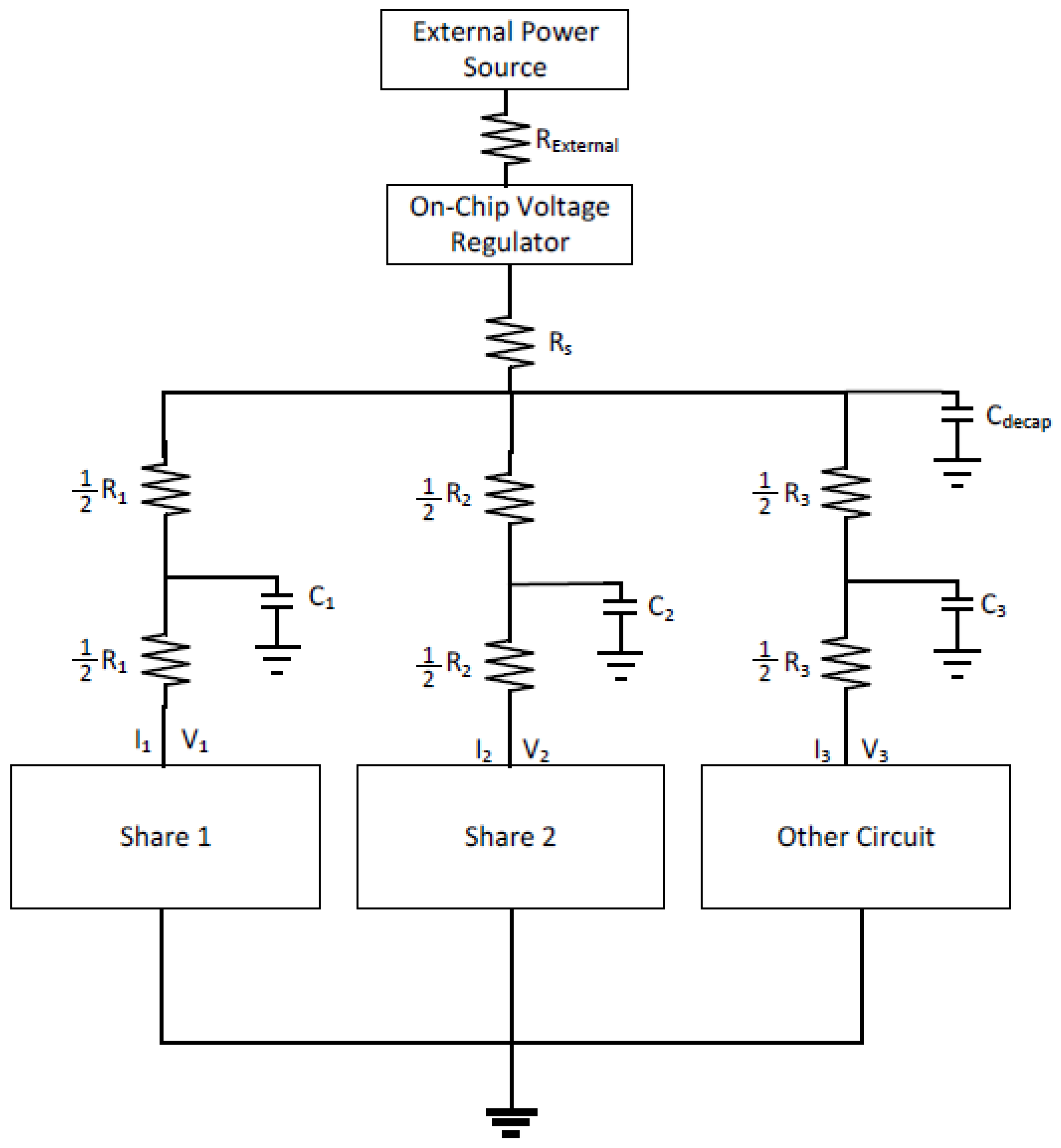

2. Distributed On-Chip Voltage Regulators

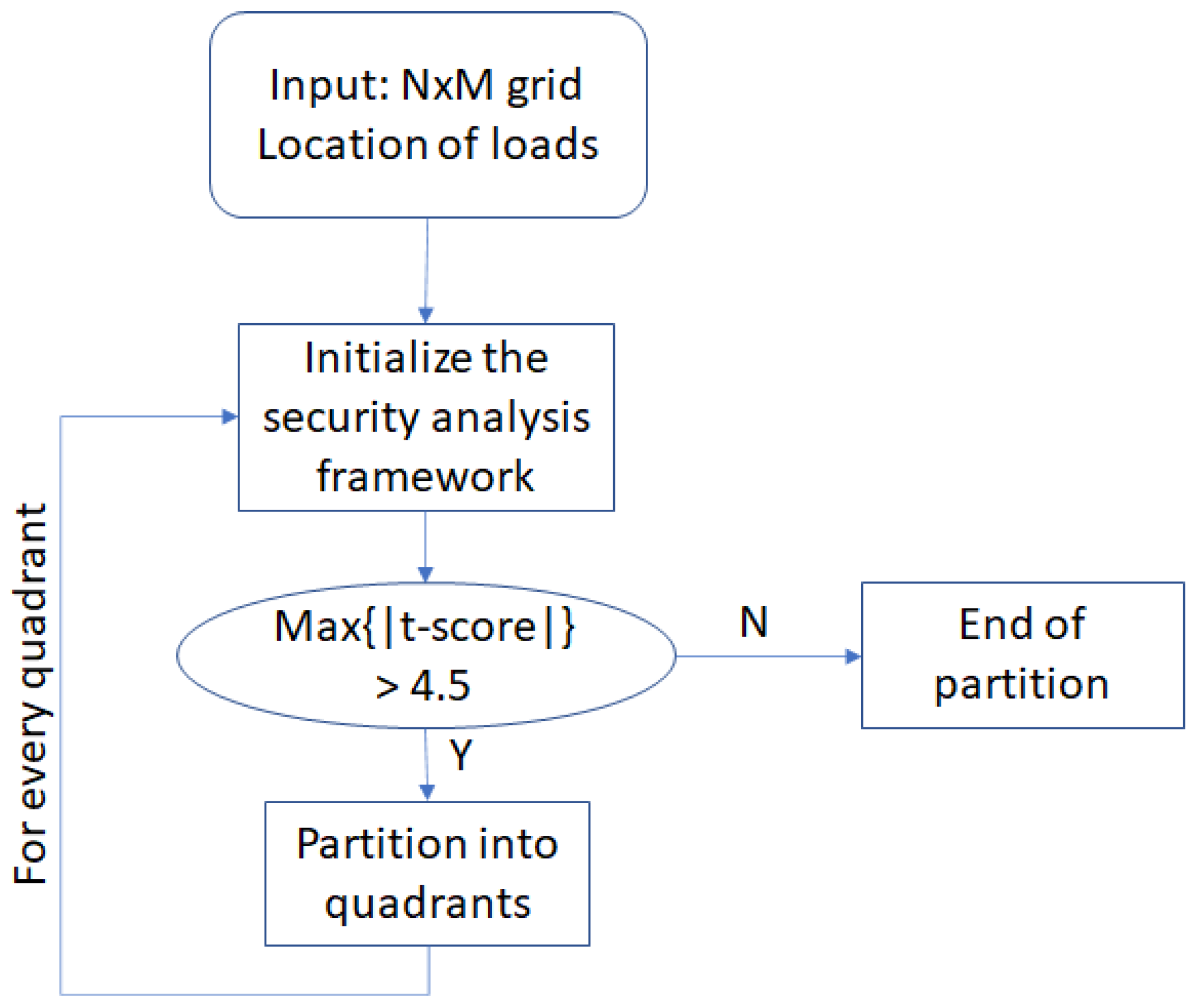

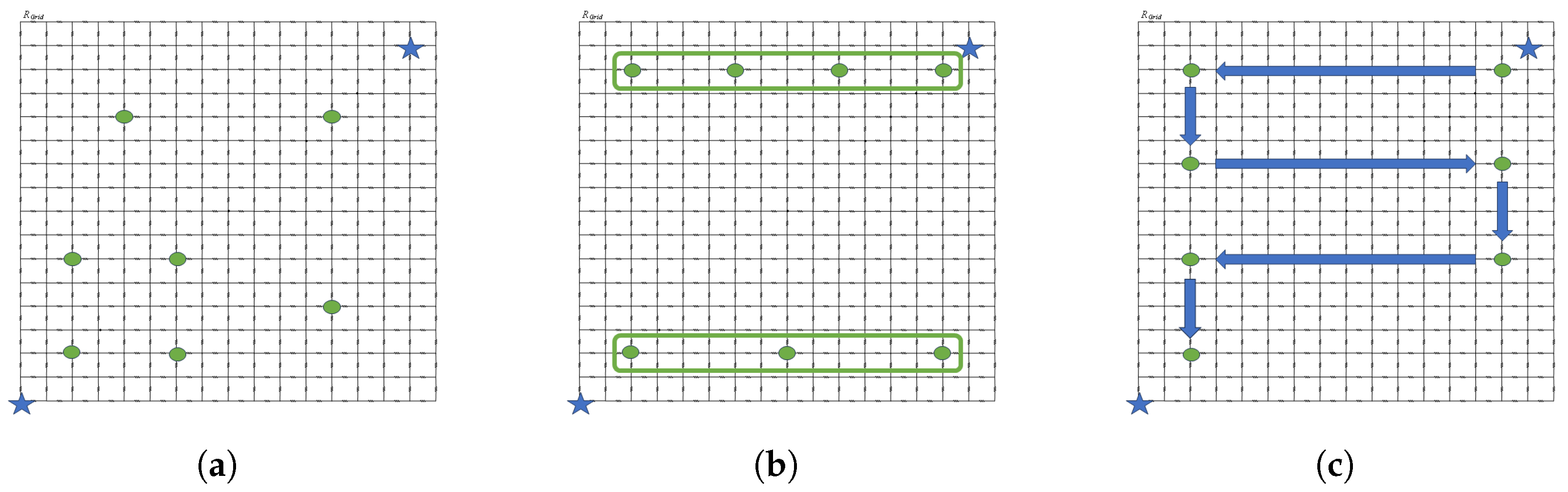

2.1. Proposed Algorithm

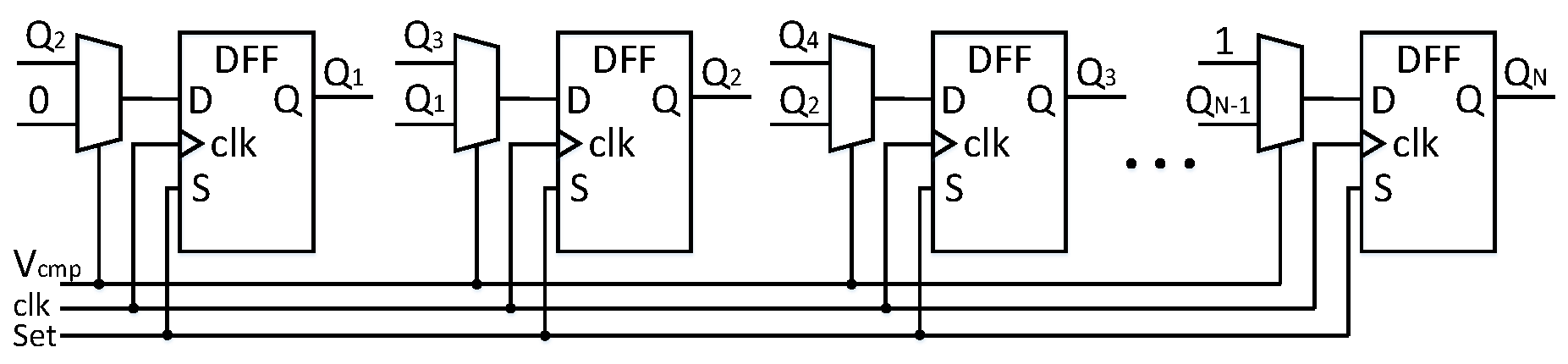

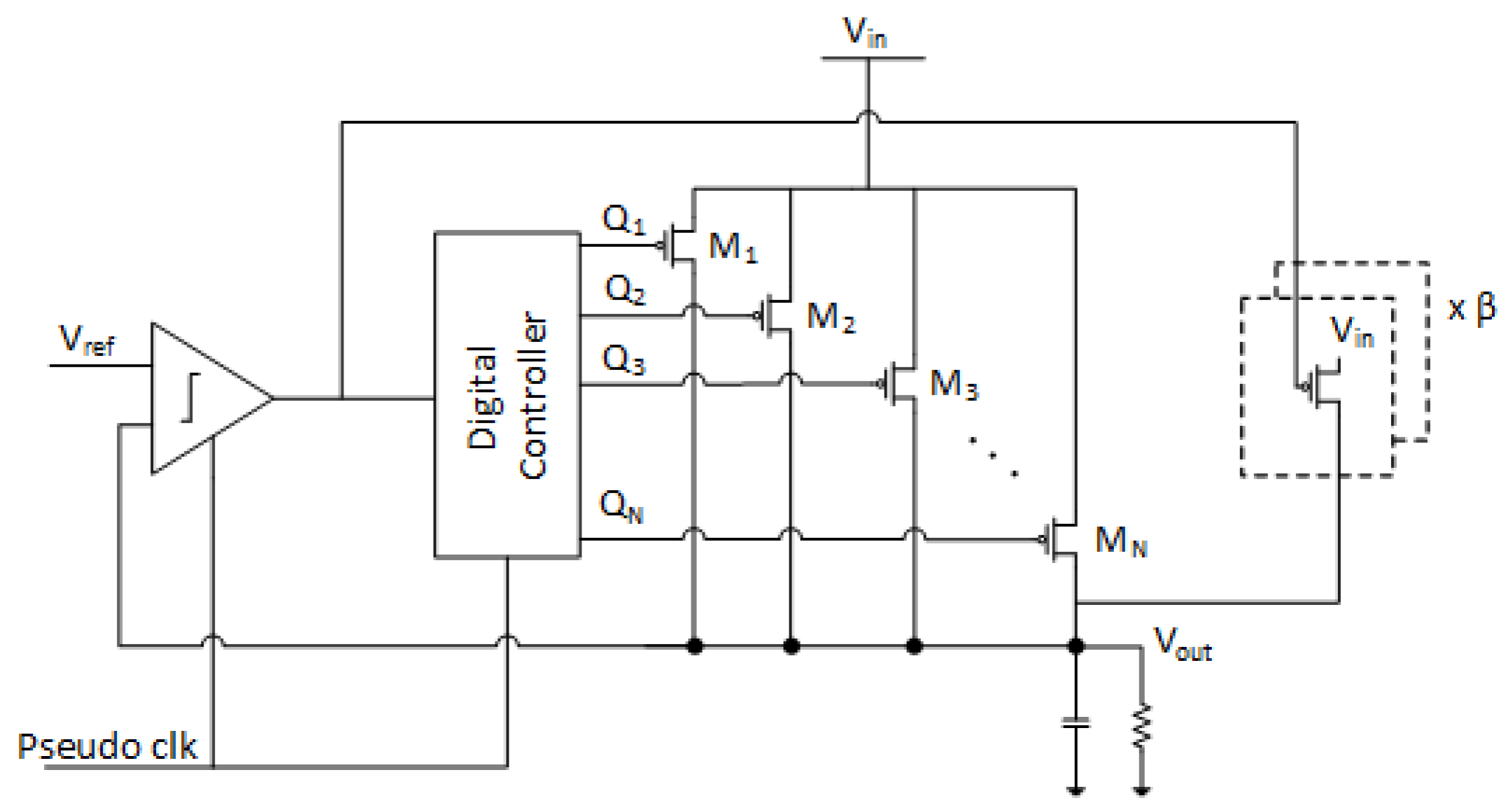

2.2. Proposed Digital Low Dropout Voltage Regulators

2.3. Proposed Pre-Silicon Leakage Detection Framework

3. Power Grid Analyses

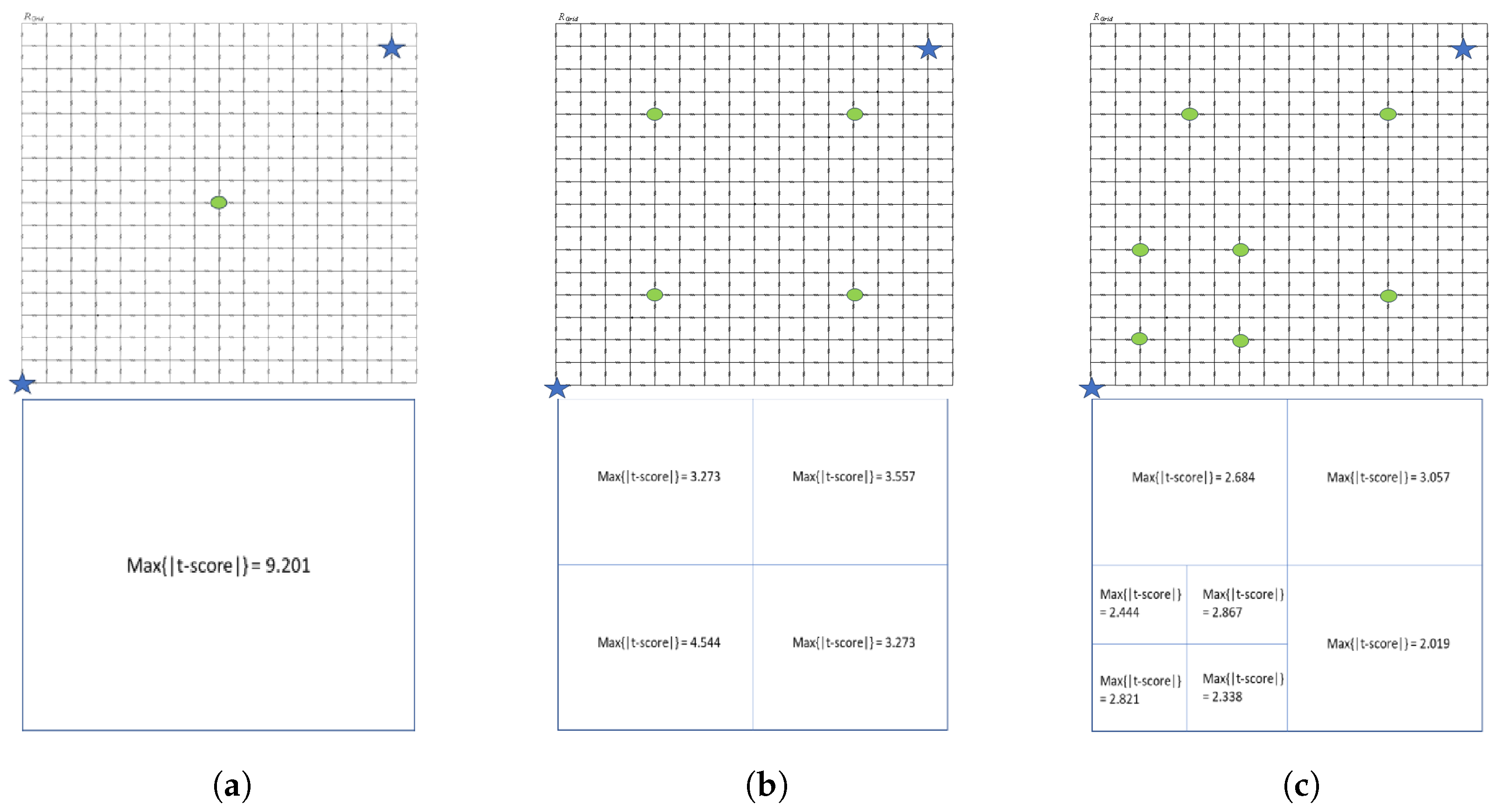

3.1. Distribution of Ideal Voltage Regulators

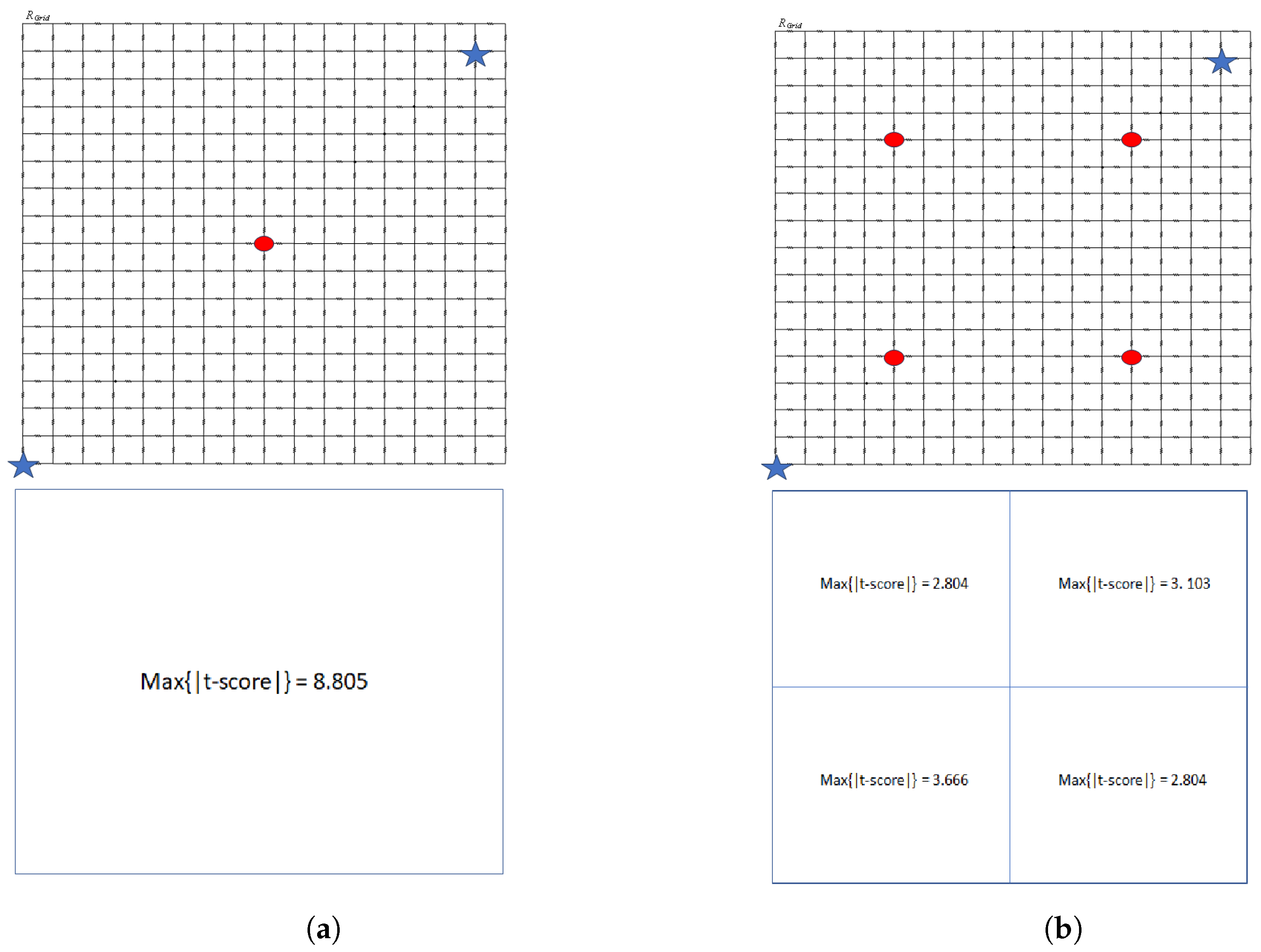

3.2. Distribution of Conventional DLDO Voltage Regulators

3.3. Distribution of Proposed DLDO Voltage Regulators

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Mayhew, M.; Muresan, R. On-chip nanoscale capacitor decoupling architectures for hardware security. IEEE Trans. Emerg. Top. Comput. 2014, 2, 4–15. [Google Scholar] [CrossRef]

- Yu, W.; Köse, S. Time-delayed converter-reshuffling: An efficient and secure power delivery architecture. IEEE Embed. Syst. Lett. 2015, 7, 73–76. [Google Scholar] [CrossRef]

- Nawaz, K.; Kamel, D.; Standaert, F.X.; Flandre, D. Scaling trends for dual-rail logic styles against side-channel attacks: A case-study. In Proceedings of the International Workshop on Constructive Side-Channel Analysis and Secure Design, Paris, France, 13–14 April 2017; pp. 19–33. [Google Scholar]

- Duc, A.; Faust, S.; Standaert, F.X. Making masking security proofs concrete (or how to evaluate the security of any leaking device), extended version. J. Cryptol. 2019, 32, 1263–1297. [Google Scholar] [CrossRef]

- De Cnudde, T.; Ender, M.; Moradi, A. Hardware masking, revisited. IACR Trans. Cryptogr. Hardw. Embed. Syst. 2018, 2018, 123–148. [Google Scholar] [CrossRef]

- Balasch, J.; Gierlichs, B.; Grosso, V.; Reparaz, O.; Standaert, F.X. On the cost of lazy engineering for masked software implementations. In Proceedings of the International Conference on Smart Card Research and Advanced Applications, Paris, France, 5–7 November 2014; pp. 64–81. [Google Scholar]

- Šijačić, D.; Balasch, J.; Verbauwhede, I. Sweeping for leakage in masked circuit layouts. In Proceedings of the Design, Automation and Test in Europe Conference and Exhibition, Grenoble, France, 9–13 March 2020; pp. 915–920. [Google Scholar]

- Dai, H.; Köse, S. On the vulnerability of hardware masking in practical implementations. In Proceedings of the 2021 on Great Lakes Symposium on VLSI, Virtual Event, 22–25 June 2021; pp. 77–82. [Google Scholar]

- Dyrkolbotn, G.O.; Wold, K.; Snekkenes, E. Security implications of crosstalk in switching cmos gates. In Proceedings of the International Conference on Information Security, Boca Raton, FL, USA, 25–28 October 2010; pp. 269–275. [Google Scholar]

- Giechaskiel, I.; Eguro, K. Information leakage between FPGA long wires. arXiv 2016, arXiv:1611.08882. [Google Scholar]

- Zussa, L.; Exurville, I.; Dutertre, J.M.; Rigaud, J.B.; Robisson, B.; Tria, A.; Clediere, J. Evidence of an information leakage between logically independent blocks. In Proceedings of the Second Workshop on Cryptography and Security in Computing Systems, Amsterdam, The Netherlands, 19–21 January 2015; pp. 25–30. [Google Scholar]

- Schellenberg, F.; Gnad, D.R.; Moradi, A.; Tahoori, M.B. An inside job: Remote power analysis attacks on FPGAs. In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition, Dresden, Germany, 19–23 March 2018; pp. 1111–1116. [Google Scholar]

- De Cnudde, T.; Bilgin, B.; Gierlichs, B.; Nikov, V.; Nikova, S.; Rijmen, V. Does coupling affect the security of masked implementations? In Proceedings of the International Workshop on Constructive Side-Channel Analysis and Secure Design, Paris, France, 13–14 April 2017; pp. 1–18. [Google Scholar]

- Addisu, M.; Salau, A.O.; Takele, H. Fuzzy logic based optimal placement of voltage regulators and capacitors for distribution systems efficiency improvement. Heliyon 2021, 7, e07848. [Google Scholar] [CrossRef] [PubMed]

- Salau, A.; Nweke, J.; Ogbuefi, U. Effective implementation of mitigation measures against voltage collapse in distribution power systems. Prz. Elektrotechniczny 2021, 97, 65–68. [Google Scholar] [CrossRef]

- Kar, M.; Singh, A.; Mathew, S.; Rajan, A.; De, V.; Mukhopadhyay, S. Exploiting fully integrated inductive voltage regulators to improve side channel resistance of encryption engines. In Proceedings of the International Symposium on Low Power Electronics and Design, San Francisco, CA, USA, 8–10 August 2016; pp. 130–135. [Google Scholar]

- Yu, W.; Köse, S. Exploiting voltage regulators to enhance various power attack countermeasures. IEEE Trans. Emerg. Top. Comput. 2016, 6, 244–257. [Google Scholar] [CrossRef]

- Yu, W.; Uzun, O.A.; Köse, S. Leveraging on-chip voltage regulators as a countermeasure against side-channel attacks. In Proceedings of the IEEE/ACM Design Automation Conference, San Francisco, CA, USA, 8–12 June 2015; pp. 1–6. [Google Scholar]

- Sijacic, D.; Balasch, J.; Yang, B.; Ghosh, S.; Verbauwhede, I. Towards efficient and automated side channel evaluations at design time. Kalpa Publ. Comput. 2018, 7, 16–31. [Google Scholar]

- Monta, K.; Sonoda, H.; Okidono, T.; Araga, Y.; Watanabe, N.; Shimamoto, H.; Kikuchi, K.; Miura, N.; Miki, T.; Nagata, M. 3-D CMOS chip stacking for security ICs featuring backside buried metal power delivery networks with distributed capacitance. IEEE Trans. Electron Devices 2021, 68, 2077–2082. [Google Scholar] [CrossRef]

- Dey, S.; Park, J.; Pundir, N.; Saha, D.; Shuvo, A.M.; Mehta, D.; Asadi, N.; Rahman, F.; Farahmandi, F.; Tehranipoor, M. Secure Physical Design. Cryptology ePrint Archive, Paper 2022/891, 2022.

- Buhan, I.; Batina, L.; Yarom, Y.; Schaumont, P. SoK: Design tools for side-channel-aware implementations. In Proceedings of the ACM on Asia Conference on Computer and Communications Security, Nagasaki, Japan, 30 May–3 June 2022; pp. 756–770. [Google Scholar]

- Gilbert Goodwill, B.J.; Jaffe, J.; Rohatgi, P. A testing methodology for side-channel resistance validation. In Proceedings of the NIST Non-Invasive Attack Testing Workshop, Nara, Japan, 25–27 September 2011; Volume 7, pp. 115–136. [Google Scholar]

- Wang, L.; Khatamifard, S.K.; Karpuzcu, U.R.; Köse, S. Mitigation of NBTI induced performance degradation in on-chip digital LDOs. In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 19–23 March 2018; pp. 803–808. [Google Scholar]

- Huang, M.; Lu, Y.; Sin, S.W.; Seng-Pan, U.; Martins, R.P.; Ki, W.H. Limit cycle oscillation reduction for digital low dropout regulators. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 903–907. [Google Scholar] [CrossRef]

- Okuma, Y.; Ishida, K.; Ryu, Y.; Zhang, X.; Chen, P.H.; Watanabe, K.; Takamiya, M.; Sakurai, T. 0.5-V input digital LDO with 98.7% current efficiency and 2.7-μA quiescent current in 65nm CMOS. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 19–22 September 2010; pp. 1–4. [Google Scholar]

- Singh, T.; Schaefer, A.; Rangarajan, S.; John, D.; Henrion, C.; Schreiber, R.; Rodriguez, M.; Kosonocky, S.; Naffziger, S.; Novak, A. Zen: An Energy-Efficient High-Performance x86 Core. IEEE J. Solid-State Circuits 2017, 53, 102–114. [Google Scholar] [CrossRef]

- Muthukaruppan, R.; Mahajan, T.; Krishnamurthy, H.K.; Mangal, S.; Dhanashekar, A.; Ghayal, R.; De, V. A digitally controlled linear regulator for per-core wide-range DVFS of atom™ cores in 14nm tri-gate CMOS featuring non-linear control, adaptive gain and code roaming. In Proceedings of the ESSCIRC 2017-43rd IEEE European Solid State Circuits Conference, Leuven, Belgium, 11–14 September 2017; pp. 275–278. [Google Scholar]

- Gomes, L.M.G. Power Reduction of a CMOS High-Speed Interface Using Power Gating. 2013.

- Seçkiner, S.; Köse, S. Exploiting On-Chip Voltage Regulators for Leakage Reduction in Hardware Masking. Sensors 2022, 22, 7028. [Google Scholar] [CrossRef] [PubMed]

| ASIC/FPGA | Implementation | Minimum Number of Traces for the Leakage (Higher Is Better) | |

|---|---|---|---|

| [7] | ASIC | PDN | 1 k |

| [20] | ASIC | PDN | 18 k |

| [21] | ASIC | X | X |

| [30] | ASIC | PDN | 80 k |

| This work | ASIC | PDN | >100 k |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Seçkiner, S.; Köse, S. A Methodology to Distribute On-Chip Voltage Regulators to Improve the Security of Hardware Masking. Information 2024, 15, 488. https://doi.org/10.3390/info15080488

Seçkiner S, Köse S. A Methodology to Distribute On-Chip Voltage Regulators to Improve the Security of Hardware Masking. Information. 2024; 15(8):488. https://doi.org/10.3390/info15080488

Chicago/Turabian StyleSeçkiner, Soner, and Selçuk Köse. 2024. "A Methodology to Distribute On-Chip Voltage Regulators to Improve the Security of Hardware Masking" Information 15, no. 8: 488. https://doi.org/10.3390/info15080488

APA StyleSeçkiner, S., & Köse, S. (2024). A Methodology to Distribute On-Chip Voltage Regulators to Improve the Security of Hardware Masking. Information, 15(8), 488. https://doi.org/10.3390/info15080488