Cybersecurity Comparison of Brain-Based Automotive Electrical and Electronic Architectures

Abstract

:1. Introduction

- This work explores the existing traditional, one-brain, two-brain, and three-brain E/E architectures available in the automotive industry;

- The authors addressed the gap in the literature by providing a generic comparison between the architectures;

- The four architectures are further analyzed in terms of vulnerability and the associated risks, according to the ISO/SAE 21434 standard Joint collaboration [11];

- TARA methods are explored and analyzed the studied architectures with the MS Threat Modeling Tool - STRIDE and Ansys Medini Analyze tool [12];

- The results of the analysis are presented through tables titled “Comparison Representation of Different E/E Architectures” and “Comparison of Cybersecurity Against the Number of Threats”.

2. Methodology

3. Background

3.1. ISO/SAE 21434

- Item definition

- Cybersecurity goals

- Threat Analysis and Risk Assessment (TARA) Method

- Threat Agent Library (TAL)—lists all relevant threat agents and their corresponding attributes;

- Methods and Objectives Library (MOL)—lists methods that each threat agent might employ along with a corresponding impact level;

- Common Exposure Library (CEL)—lists areas of the greatest exposure and vulnerability.

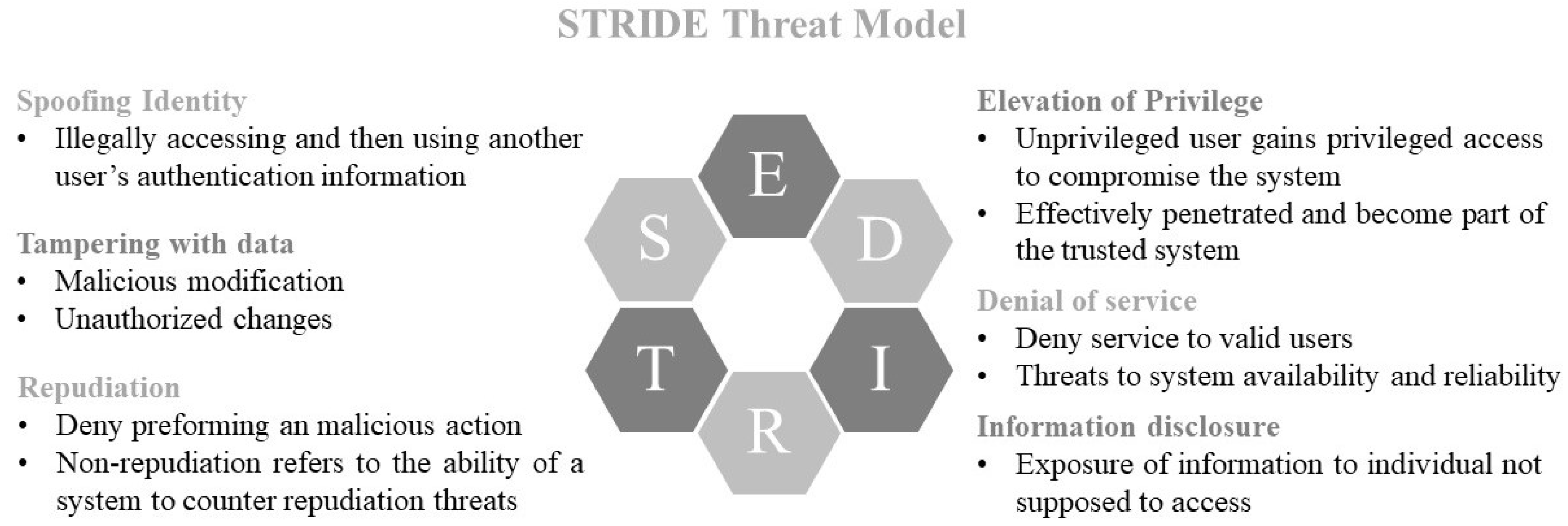

3.2. STRIDE

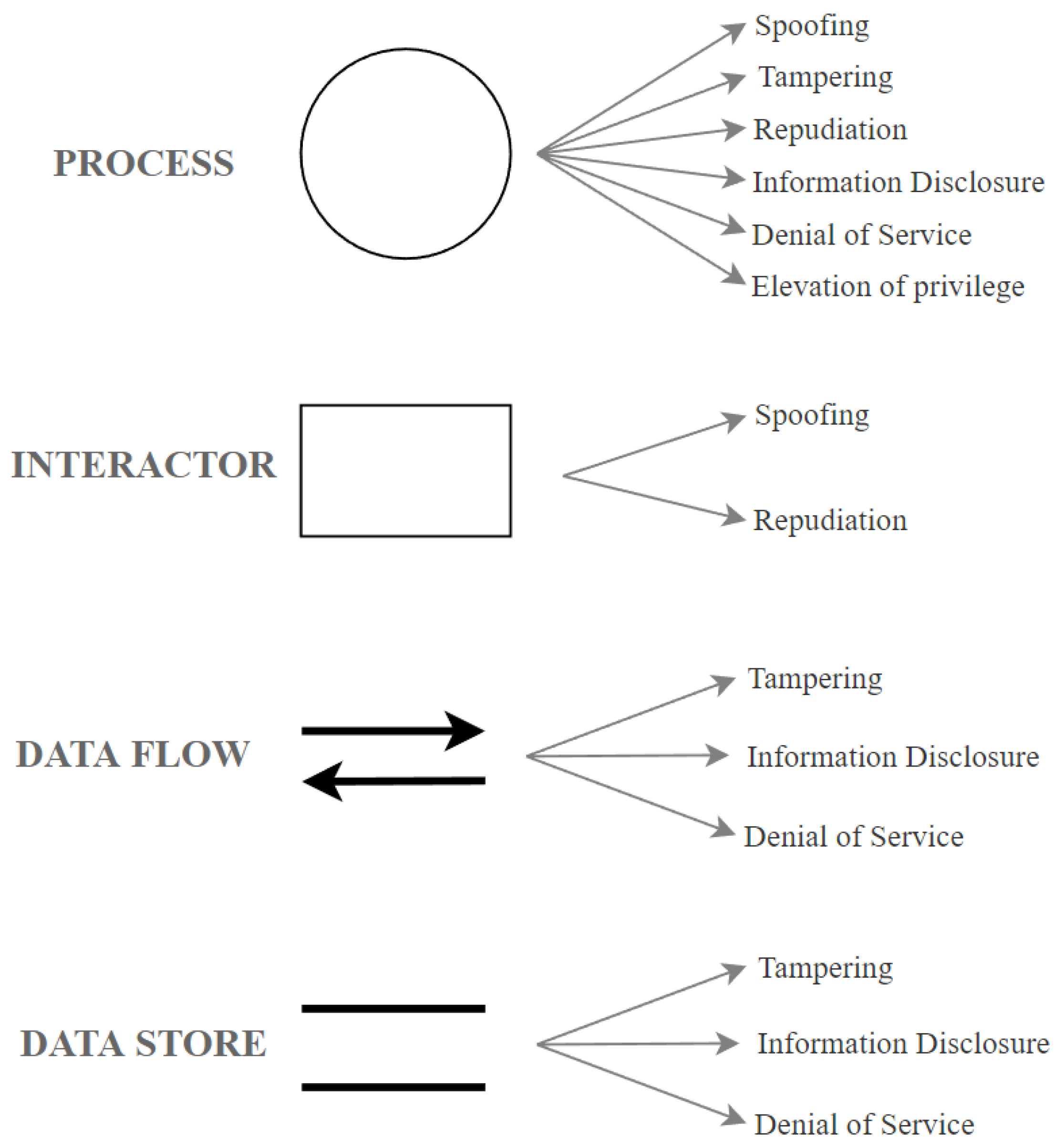

3.3. Model and Associated Threats

4. Architectures

4.1. Traditional E/E Architecture

- Use Case:

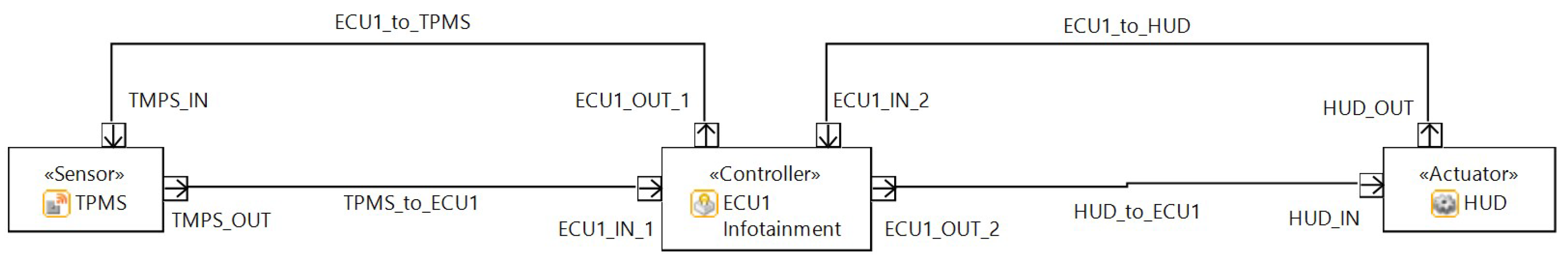

- Tire Pressure Monitoring System

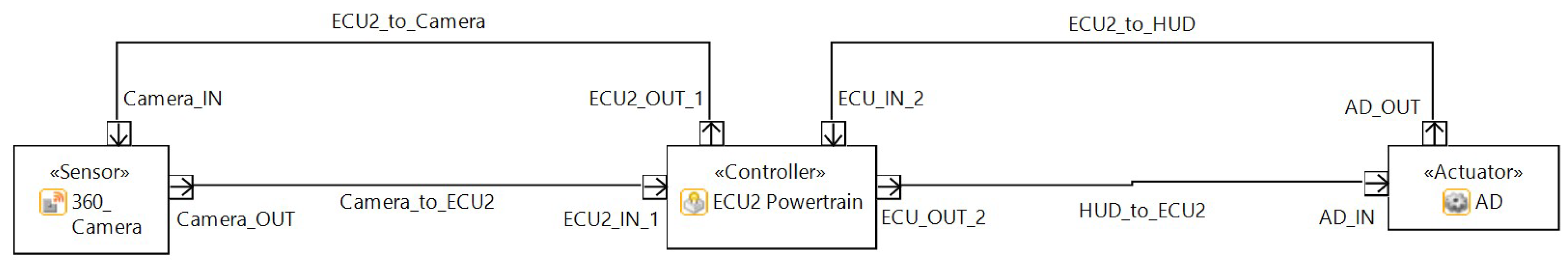

- Advanced Driver Assistance System (ADAS)

- Remote Keyless Entry System (RKE)

- Advantages of the low performance Electronic Control Unit (ECU) in a traditional architecture:

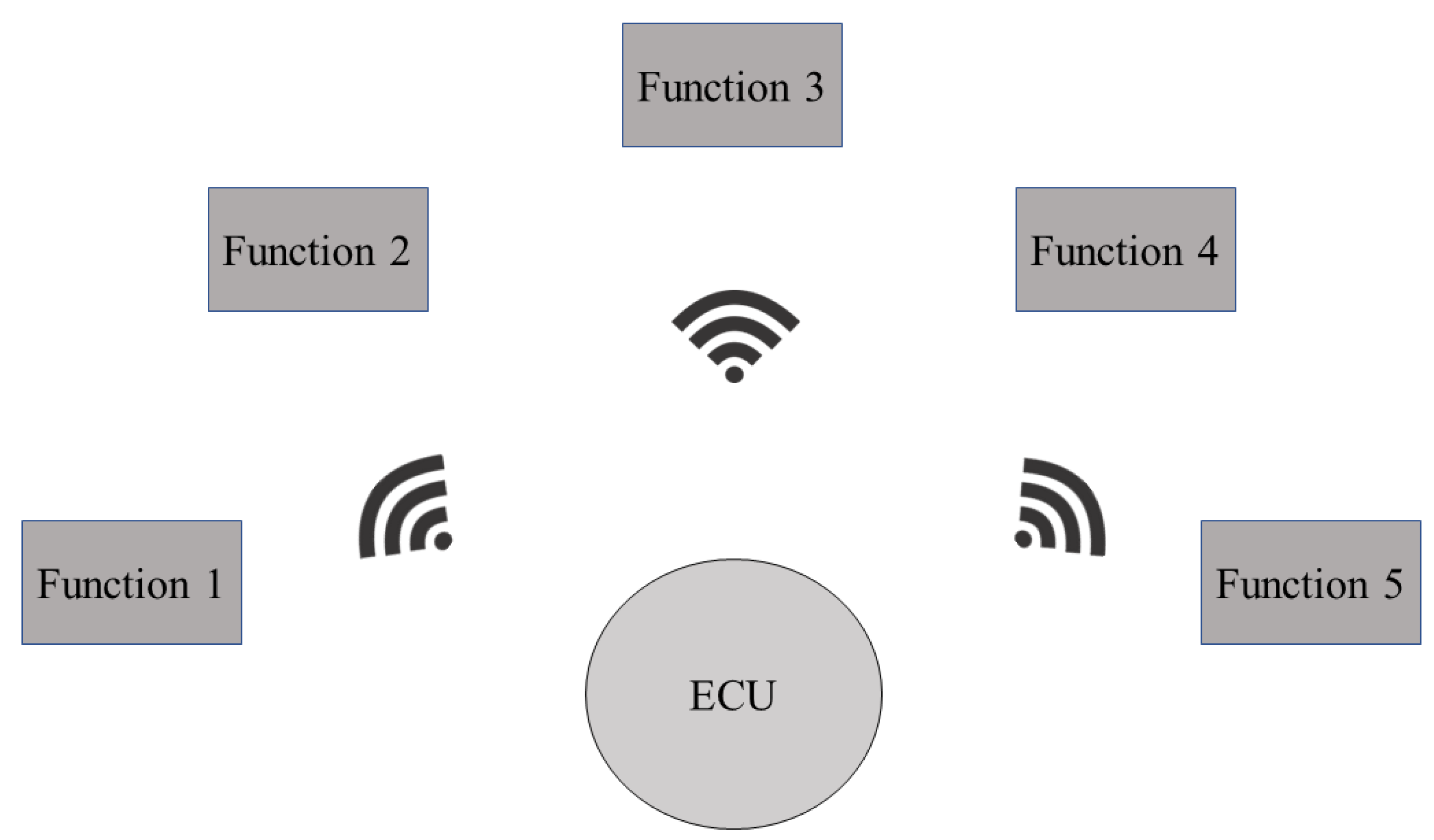

- If one ECU is attacked, the functions hosted by that particular ECU are affected where the number of functions is low. However, in case of an attack on HPCs, as many functions are involved, the damage is more serious.

- ECU is easy to develop and maintain as it usually has low performance and hosts few functions.

- In case of a damage of an ECU, it is easier to replace due to its low-performance capability.

- Drawbacks of an Electronic Control Unit (ECU) in a traditional architecture:

- The performance is very low (100 or 1000 times) compared to high performance computing devices like HPCs and host few functions.

- When low-performance ECUs are used, many ECUs are required to provide all the functions necessary for a car, which are difficult to maintain.

- Connecting so many ECUs requires wires. Therefore, wiring harness in a high end car is around 10 km long when connecting all cables one after another, producing high energy consumption to carry the heavy cables. In addition, the complex topology of the cable connectivity makes it difficult to maintain and repair in case of a connection failure.

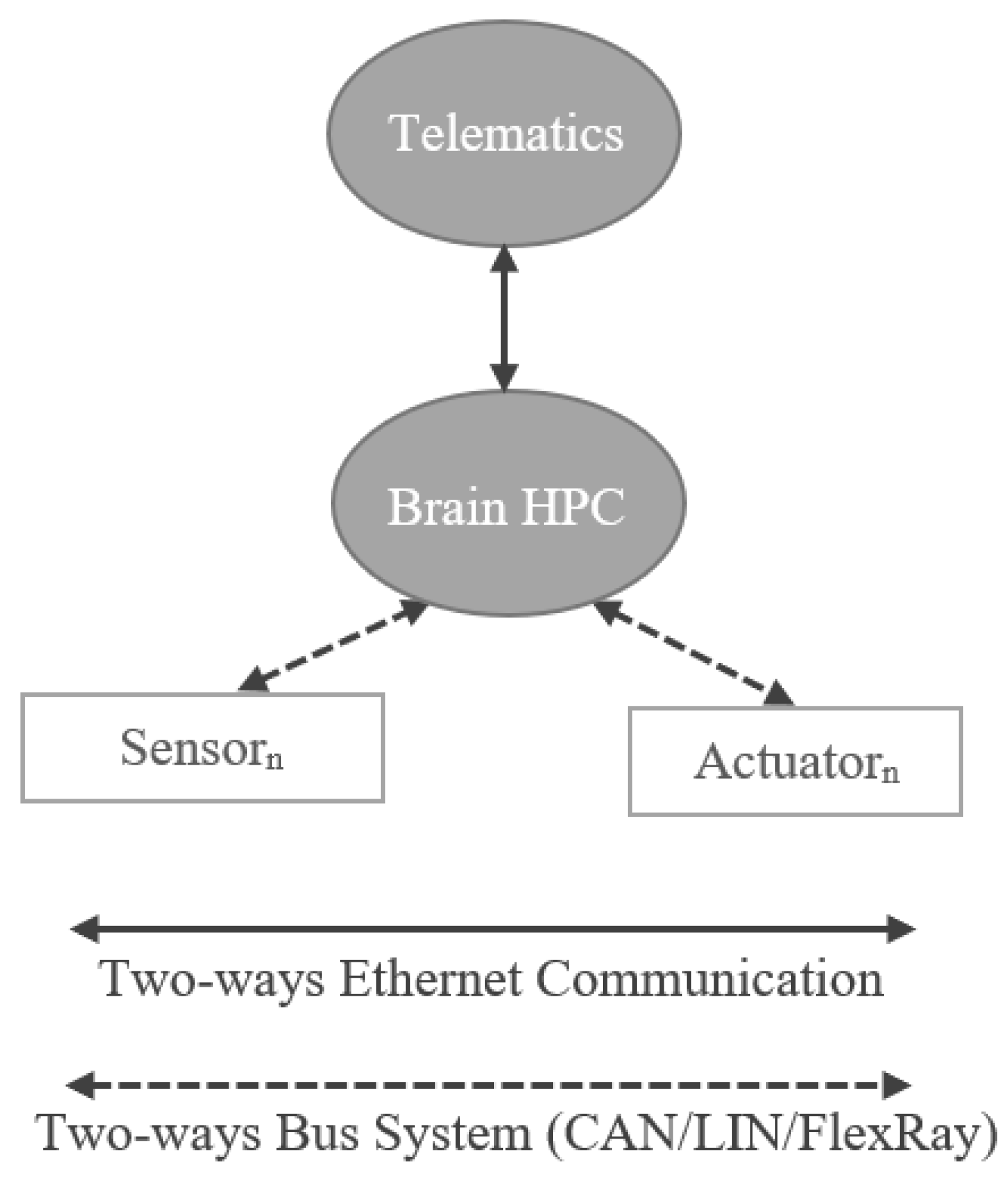

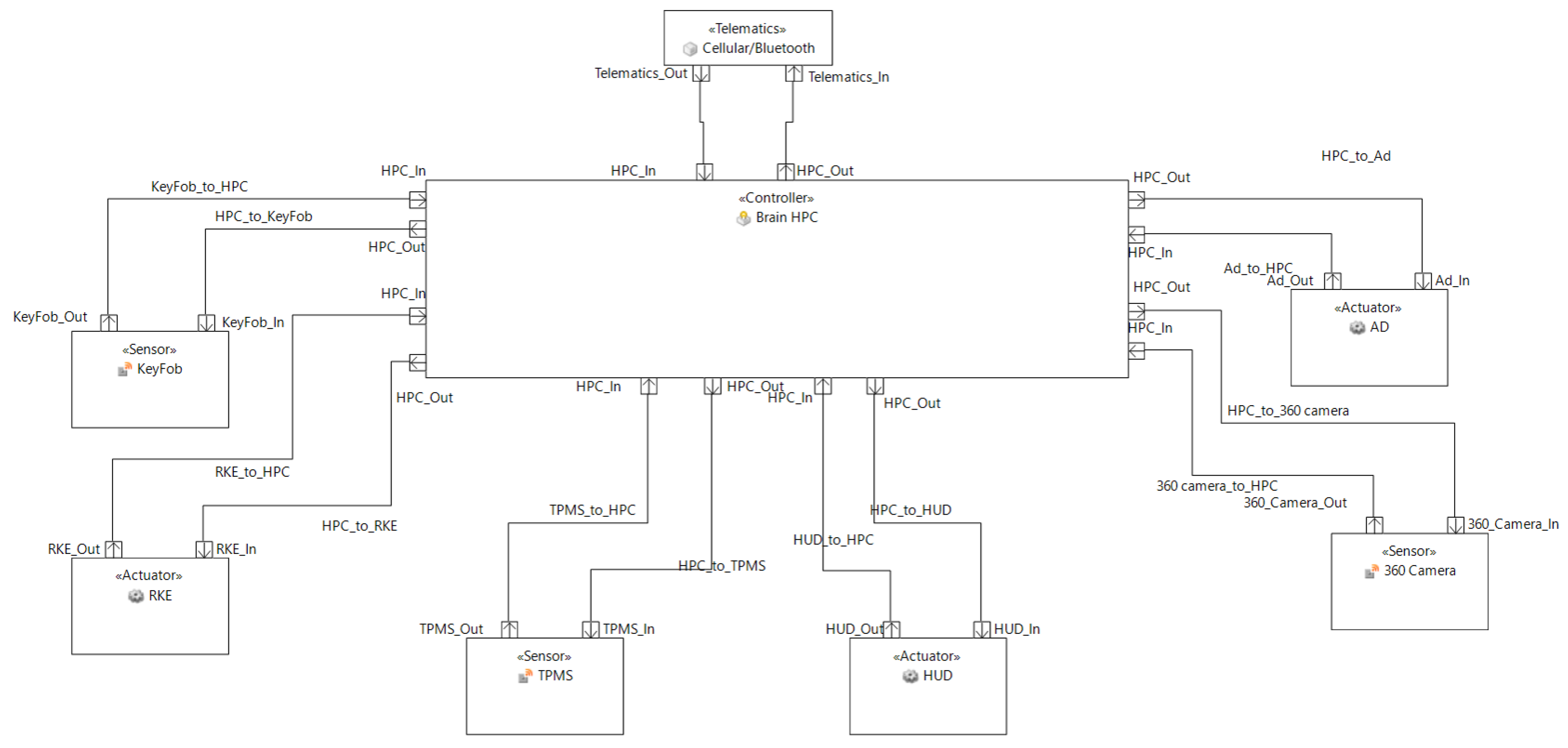

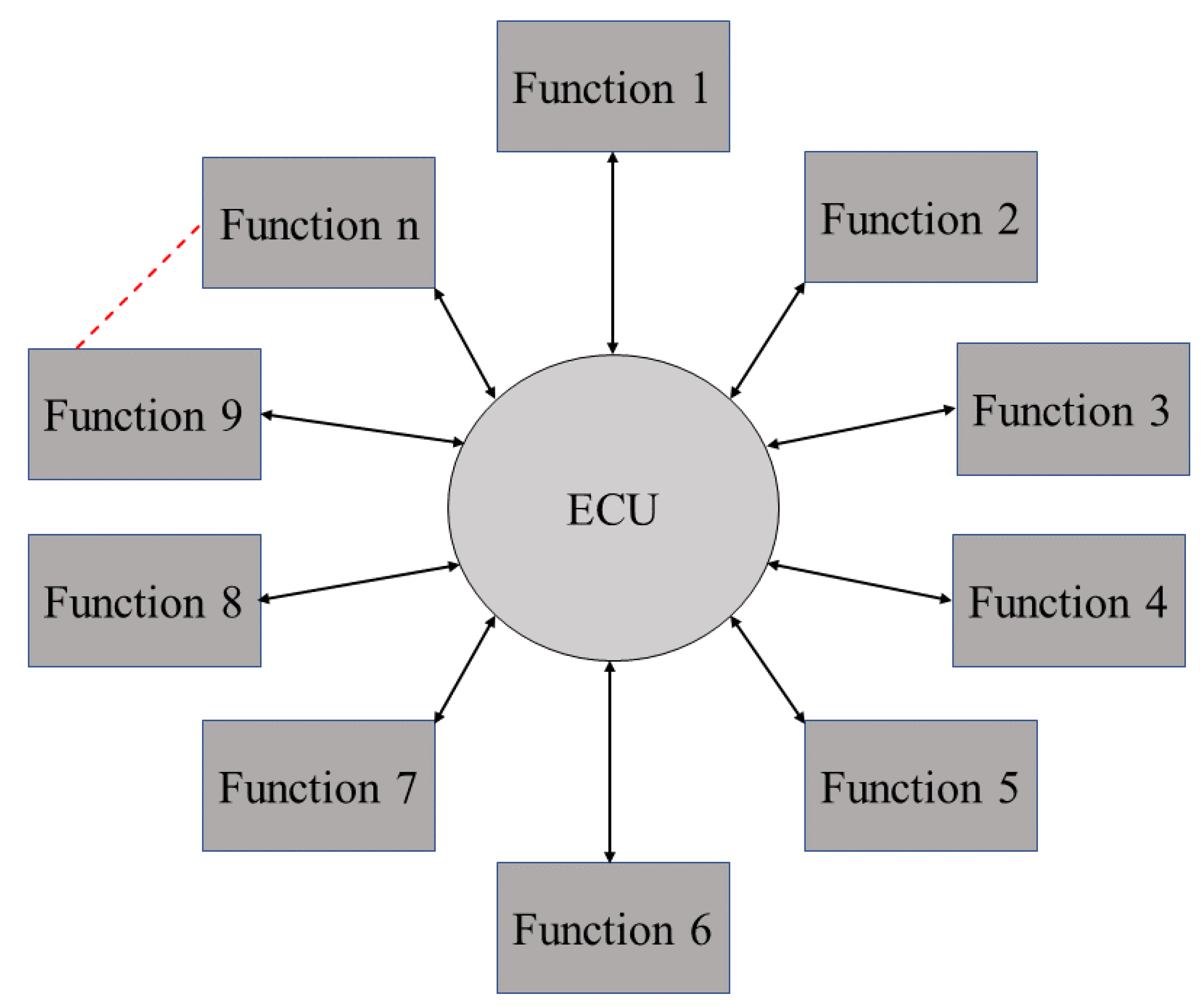

4.2. One-Brain (Centralized) E/E Architecture

- Use Case:

- Advantages of One-Brain Architecture:

- It is cheaper than multiple individual ECUs when the price of Brain-HPC is cheaper than the cost of all the ECUs and the funtions hosted on those ECUs.

- The complexity of the whole in-vehicle E/E architecture is reduced due to centralization of the functionalities.

- It can handle high computing, which is required for ADAS, IoT, and other high-computing applications.

- Since such a Brain-HPC has several high and low performance cores, each of the cores is able to host one vertical stack representing an Virtualization layer, Operating System (OS) layer, Middleware, and applications.

- Able to provide decoupling of functionalities. For example, safety cores (which are able to host safety functions) are separated from the high performance cores (providing Infotainment functionalities).

- Disadvantages of One-Brain Architecture:

- Earlier handling of the hardware/software architecture is required. The hardware and software architecture should be defined during the concept phase of the vehicle. For example, the performance requirement of the HPC (Memory Capacity, Number of Cores, Number of Boards, etc.) needs to be calculated considering the number of functions to be hosted on the HPC in the future, which is sometimes difficult to predict.

- Since this is new type of architecture, all of the stakeholders (OEM, Tier1 Supplier, Tier2 Supplier) who are involved in the development of the architecture need to understand the architecture in detail. This requires a huge communication overhead.

- The failure of the centralized Brain will lead to the whole vehicle to be non-functional.

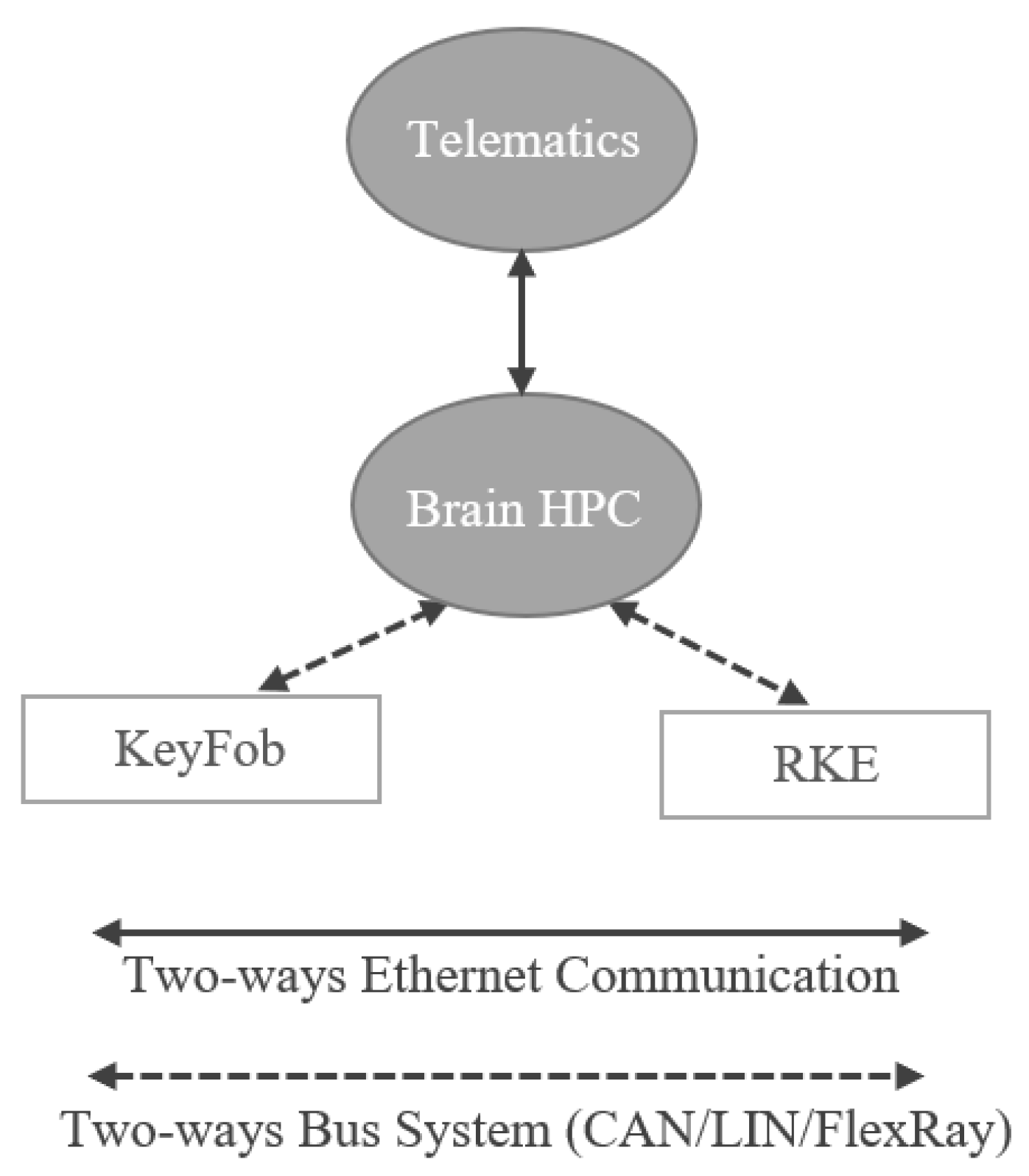

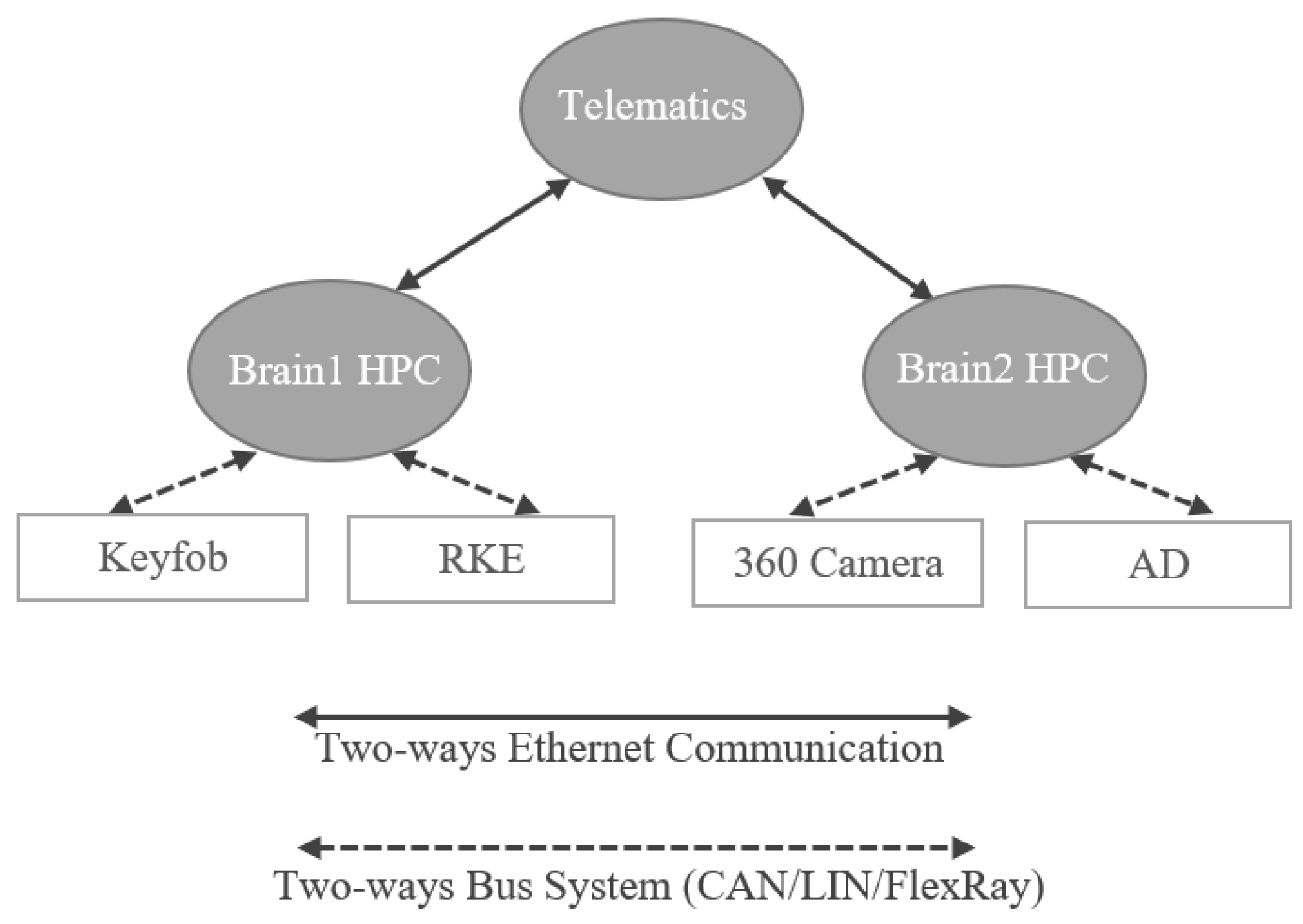

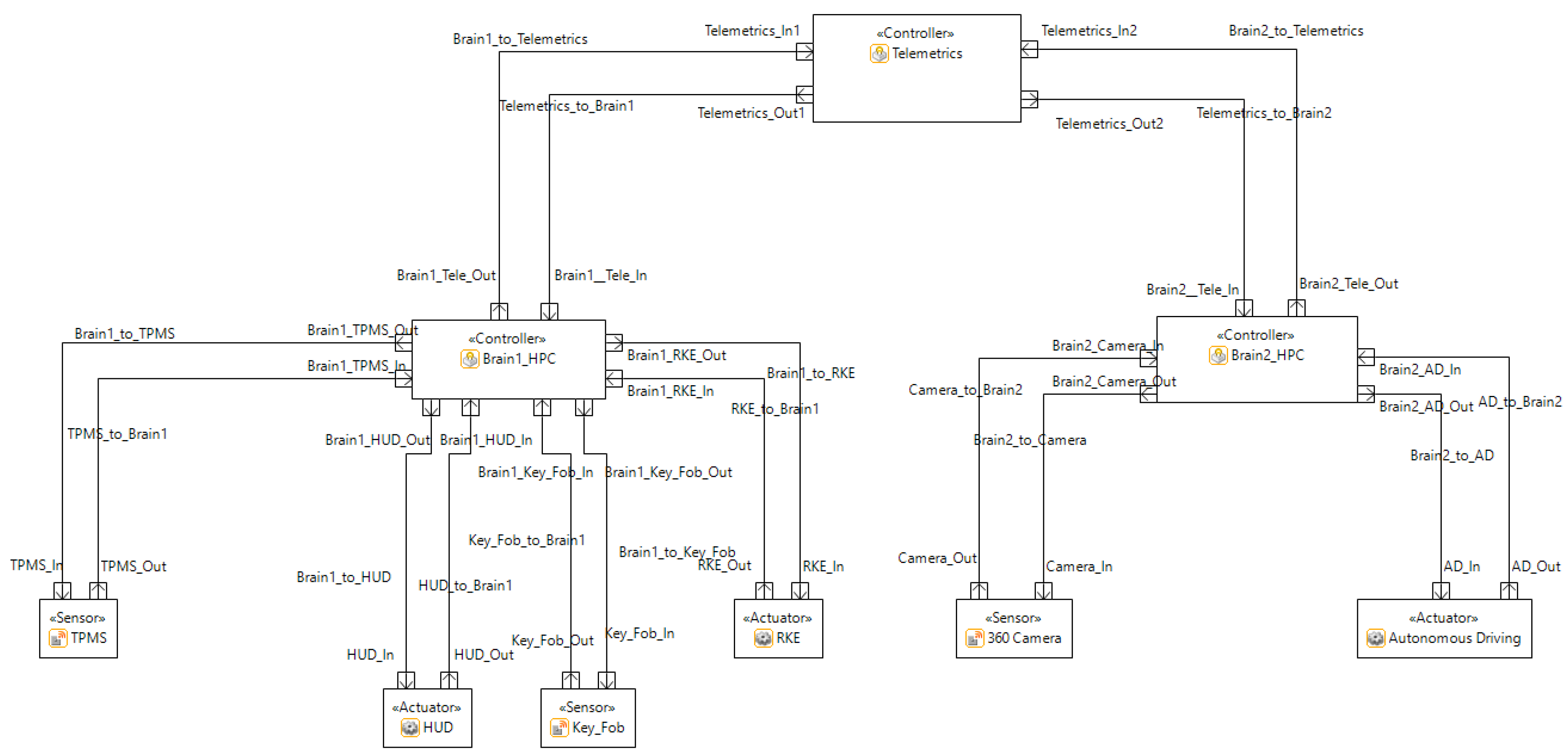

4.3. Two-Brain (Zonal) E/E Architecture

- Use Case:

- Advantages of the Two-Brain Architecture:

- It provides redundancy to the one-brain architecture. If the same functions are hosted in both HPCs, then the failure of one HPC will not make the vehicle non-functional. If different functions are hosted in both HPCs, then the failure of one HPC will make the vehicle probably partially non-functional.

- It has a higher performance and efficiency compared to the one-brain architecture.

- It provides the possibility for load-balancing, which provides redundancy of the functions which are safety and security critical.

- When two heterogeneous HPCs are deployed, the vulnerabilities of one HPC might not be available in the other HPC, thereby, it makes the architecture more secure than the one-brain architecture.

- Two HPCs allow more software run-time environments to functions. Therefore, it is easier to design homogeneous and heterogeneous functions.

- The architecture can be cost effective compared to the one-brain architecture when two HPCs with lower configuration are used, rather than having higher configuration in one HPC.

- Disadvantages of the Two-Brain Architecture:

- Increased complexity in the network due to the interconnection of brains.

- More communication nodes and cables due to the additional HPC.

- Independent functionalities of the ECU can lead to the partial failure of functions.

- An additional power requirement to power the additional HPC.

- Additional HPC will lead to extra initial investment, which leads to overall vehicle costs. This implies higher short-term investments, which may conduct to a higher overall vehicle cost.

- Hardware and software architecture is more complex than one-brain and traditional architecture when heterogeneous hardware/software architectures are deployed.

- Having two brains gives the attackers more attack surface than the one-brain and traditional architecture.

- Having redundant functions means keeping and running redundant codes which takes memory and CPU cycles.

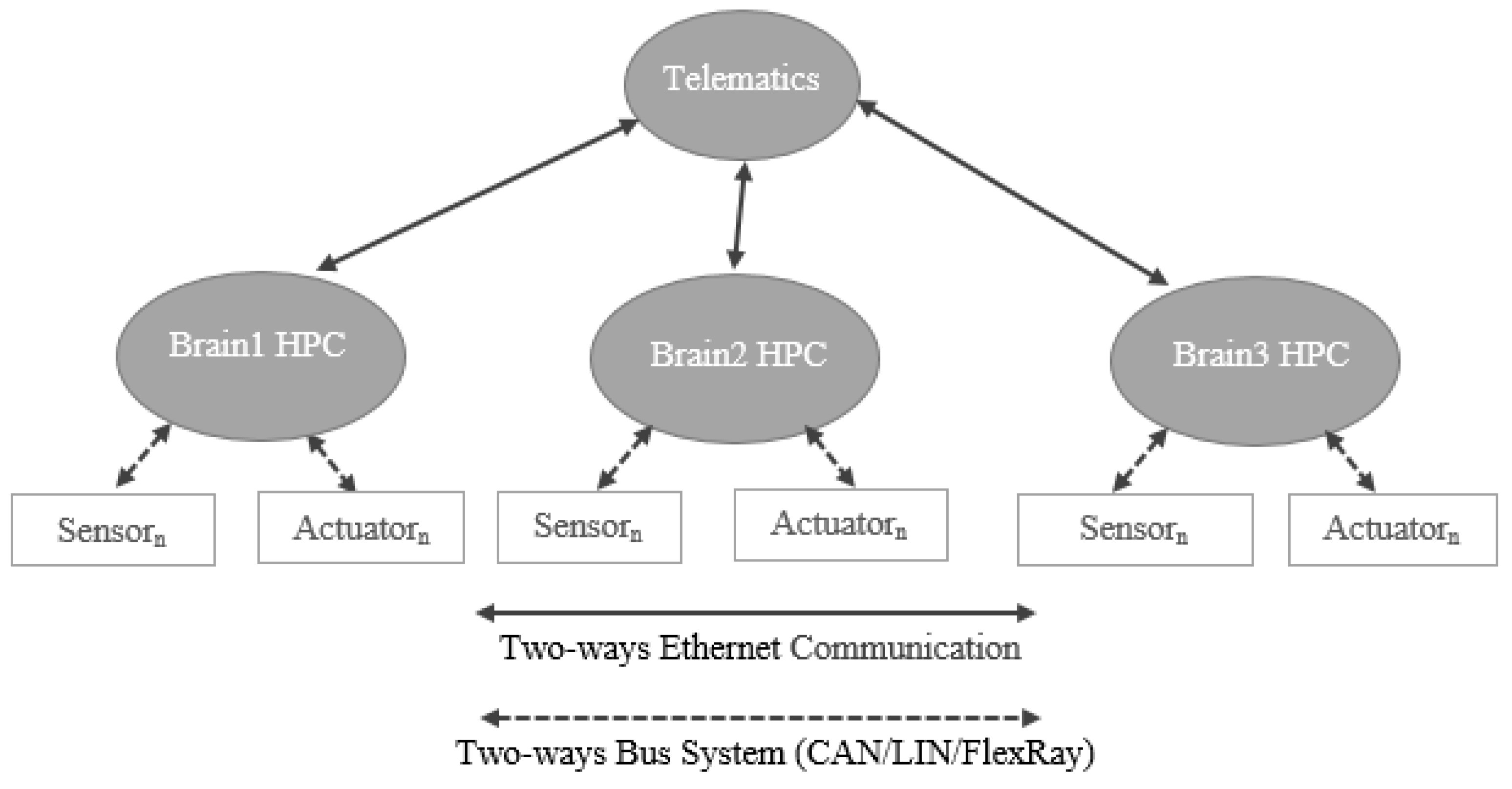

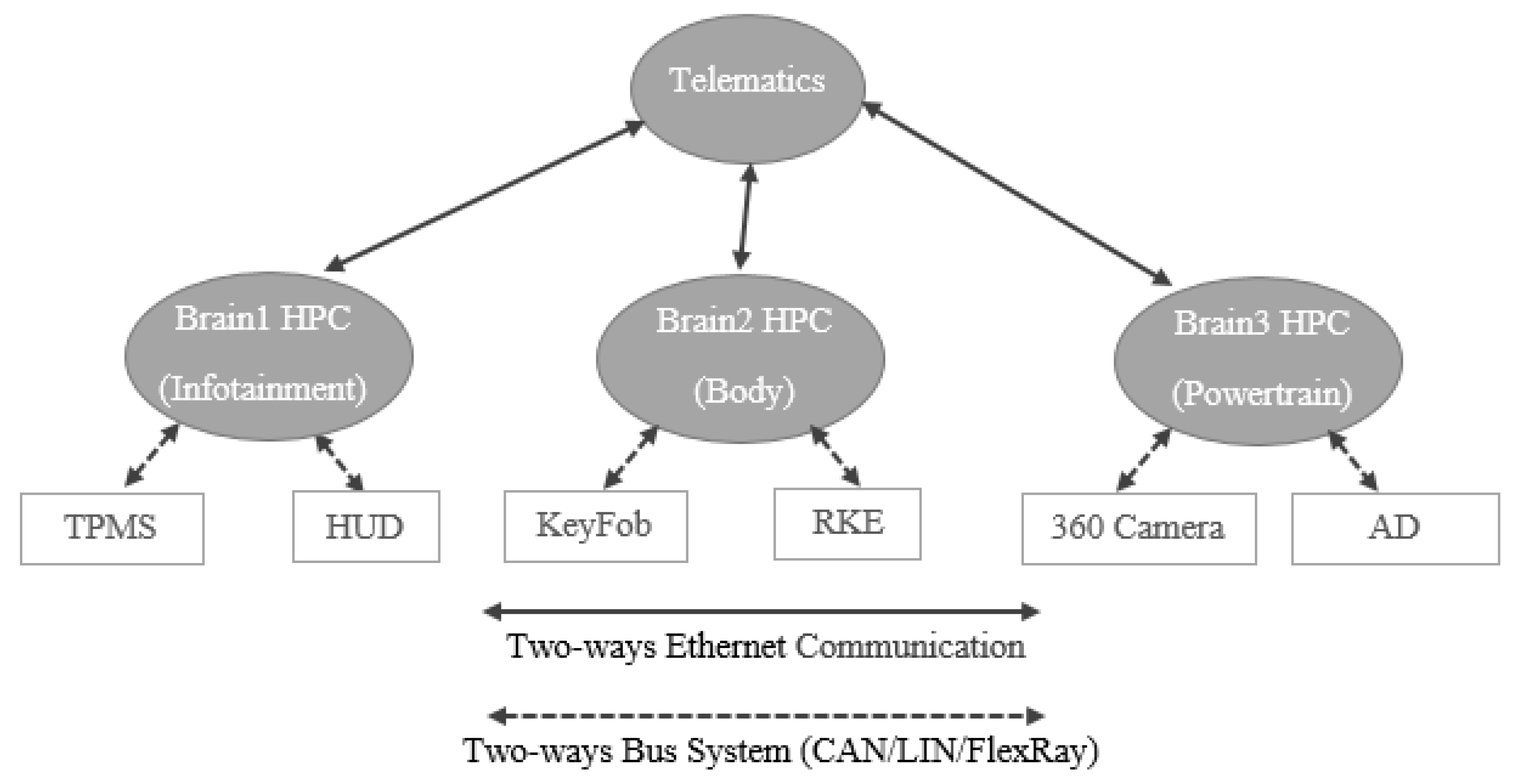

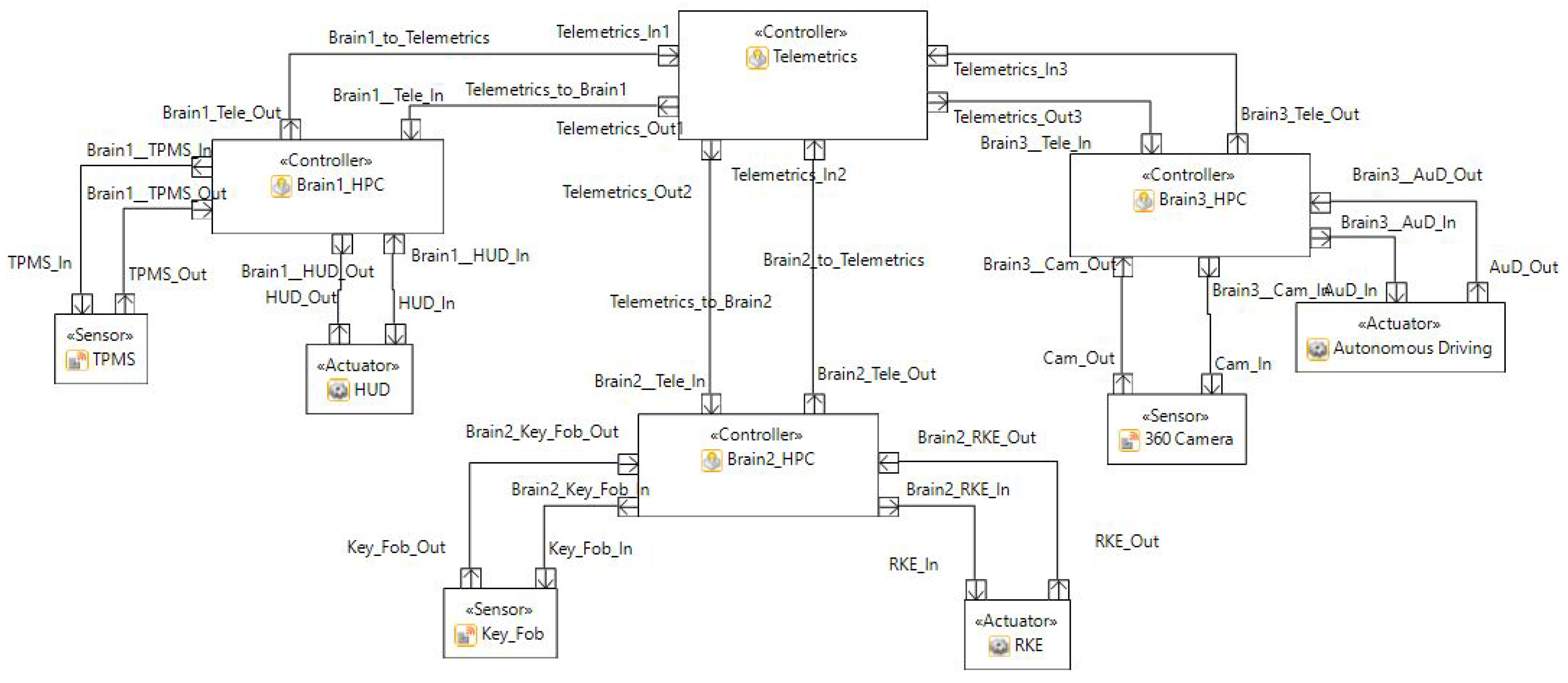

4.4. Three-Brain E/E Architecture

- Use Case:

- Advantages of the Three-Brain Architecture:

- As three HPCs are networked together, this architecture will be better-performing than the one- and two-brain architectures.

- Balancing the load is much easier with the division of the functions.

- Able to ensure data integrity (the accuracy and consistency of data stored in a database) with redundant systems.

- Easy to maintain and modify the HPCs in the architecture.

- Scalable—each item can be scaled independently with higher memory and processing power.

- Disadvantages of the Three-Brain Architecture:

- Increased complexity in the network due to the interconnection of brains.

- More communication nodes and cables due to additional HPCs.

- Independent functionalities of the ECU can lead to the partial failure of functions.

- An additional power requirement to power the additional HPCs.

- Additional HPCs will lead to extra initial investment, which leads to overall vehicle costs. This implies higher short-term investments, which may conduct to a higher overall vehicle cost.

- Hardware and software architecture is more complex than one-brain, two-brain and traditional architecture when heterogeneous hardware/software architectures are deployed.

- Having three brains gives the attackers more attack surface than the one-brain and two-brain architecture.

- Having redundant functions means keeping and running redundant codes which takes memory and CPU cycles.

5. Security Analysis Using STRIDE

- Telematics Unit/ECU/HPC/Function = six threats, one threat for each threat category;

- Sensor = two threats, one from spoofing and another from repudiation category;

- Actuator = two threats, one from spoofing and another from repudiation category;

- Connection port = three threats, one from tampering, another from information disclosure, and one from the denial of service category;

- Data flow line = three threats, one from tampering, another from information disclosure, and one from the denial of service category;

- = number of threat category per process = 6;

- = number of threat category per sensor or actuator = 2;

- = number of threat category per port or data flow direction = 3;

- = number of telematics unit, which is normally 1 in a vehicle;

- = number of traditional ECU in the architecture which is 0 for the brain-based architectures;

- = number of brains/HPCs;

- = number of features/functions;

- = number of sensors;

- = number of actuators;

- = number of ports;

- = number of data flow lines;

- = number of databases = 0;

- T = total number of threats.

6. Risk Analysis and Security Comparison of the Architectures

6.1. Security Threats and Damage Scenarios for Sensors

- Spoofing of sensor: The threat agent spoofs the identity of a sensor and sends malicious data to the ECU. Considering the example of TPMS, an attacker is able to spoof the tire pressure monitoring sensor and send the false data of the tire pressure to the display. This may result in a damage scenario such as the driver is panicked by seeing the very high/low tire pressure and goes to the workshop for it.

- Repudiation of a sensor: The threat agent deletes or manipulates the data which are logged in the sensor and this results in the loss of data traceability, which is sent from the sensor to the ECU. This threat may lead to the operational damage of the vehicle, as the data stored in the TPMS (sensor) are manipulated or deleted by the attacker.

6.2. Security Threats and Damage Scenarios for Actuators

- Spoofing of actuators: The threat agent spoofs the identity of actuators and sends malicious data to the ECU. Considering the example of the head up display (HUD), an attacker can spoof the HUD which may result in the improper functioning of the HUD. An HUD has important parameters to display, which guide the driver while driving, and the false information of these parameters may lead to fatal accidents.

- Repudiation of actuators: The threat agent deletes or manipulates the data which are logged into actuators and this results in the loss of data traceability, which is sent from the actuator to the ECU. This threat may lead to the operational damage of the vehicle, as the stored data in the HUD (actuator) is manipulated or deleted by the attacker.

6.3. Security Threats and Damage Scenarios for Telematics Unit

- Spoofing of telematics: The threat agent spoofs the identity of telematics and sends malicious data to HUD or to any other interactor. This threat will mislead the owner of the vehicle, for example, by showing the wrong speed in the HUD.

- Tampering of telematics: The threat agent tampers with the data of the telematics to manipulate the data or corrupt its operation.

- Repudiation of telematics: The threat agent accesses the telematics unit and denies access to it afterwards. After accessing the system, attackers may change the configuration in the telematics unit which prevents the right users accessing the system. In addition, the attacker may try to access other functions and may modify the privileges to access the functions.

- Information disclosure of telematics: The threat agent extracts sensible data/information from the telematics unit, such as Hardware/Software Configuration of the Device and sells the data to the competitors of the OEM/Supplier.

- Denial of service (DoS) of telematics: The threat agent may cause the telematics to crash, halt, stop, or execute slowly by consuming or blocking resources, in all cases violating an availability metric. Attackers may try to flood the telematics with a huge number of requests, which results in the crashing of the system. Telematics may stop showing the data to the display unit.

- Elevation of privilege of telematics: The threat agent executes telematics functions not available at the agent’s default privileges level. Attackers may try to access the functions which they are not authorized to use.

6.4. Security Threats and Damage Scenarios for Data Flows

- Tampering the data flow: The threat agent tampers with the state/data of the data flow to manipulate the data during the transfer. The tampered sensor/actuation signal causes the loss of the integrity, which may cause life-threatening events, financial and operational damages.

- Information disclosure: The threat agent intercepts the data flow and extracts sensitive data/information by tapping the signal. Then, the stolen data is used for the further misuse cases (e.g., stealing the key and unlocking the sequence from the KeyFob).

- DoS: The threat agent floods or blocks the data flow, limiting its performance, throughput, or availability. An actuator can be made unavailable by damaging the signal wires or the network cables between the controller (HPC or ECU) and the actuator if the wires or cables are compromised. Thus, the actuator will not be available for the actuation. This may lead to life-threatening events, financial, and operational damage.

6.5. Security Threats and Damage Scenarios for HPCs

- Spoofing of HPCs: The threat agent spoofs the identity of an HPC and sends malicious data to the interactors. This threat may result in fatal accidents, as the some of the actuators directly control the speed and acceleration of a vehicle.

- Tampering of HPCs: The threat agent tampers with the process and/or data of the HPCs in order to manipulate the process and/or data and corrupt the functions to make the vehicle partially/fully non-functional.

- Repudiation of HPCs: The threat agent makes use of an HPC and denies it’s access afterwards by deleting the access logs in the HPC. In case of an accident due to this malicious activity, it is not possible to detect the attacker.

- Information disclosure of HPCs: The threat agent extracts sensible data/information from the HPC by accessing and reading its buffer/RAM/flash storage. Afterwards, the attacker might misuse the confidential information such as car logs, safety critical data, and device ID.

- DoS of HPCs: The threat agent causes an HPC to crash, halt, stop, or execute slowly by consuming or blocking resources. In all cases, this means violating an availability metric. Attackers may try to flood the HPCs with a huge number of requests, which will increase the load to the HPCs and later, this results in crashing the system. HPCs may stop receiving data from sensors and sending data to actuators, which can cause a disruption to the vehicle operations. If this happens while on the road, this threat may lead to fatalities.

- Elevation of privilege of HPCs: The threat agent executes HPC’s functions not available at the agent’s default privileges level. After accessing an HPC, attackers may try to access other functions for which they do not have access. The attackers may modify the privileges to access/close access to functions for them and for the other users.

7. Recommended Security Controls for the Architectures

7.1. Security Controls for the Overall Architecture

- Firewall: A firewall is a network security component which keeps track of the network devices/interfaces and filters requests based on its security policies. In vehicle communication, a lot of communications take place in in-vehicle and V2X scenarios. These communications are target for the attackers, therefore, in order to mitigate the risks, a firewall should be able to block illegitimate communication to an ECU or to the entire in-vehicle network.

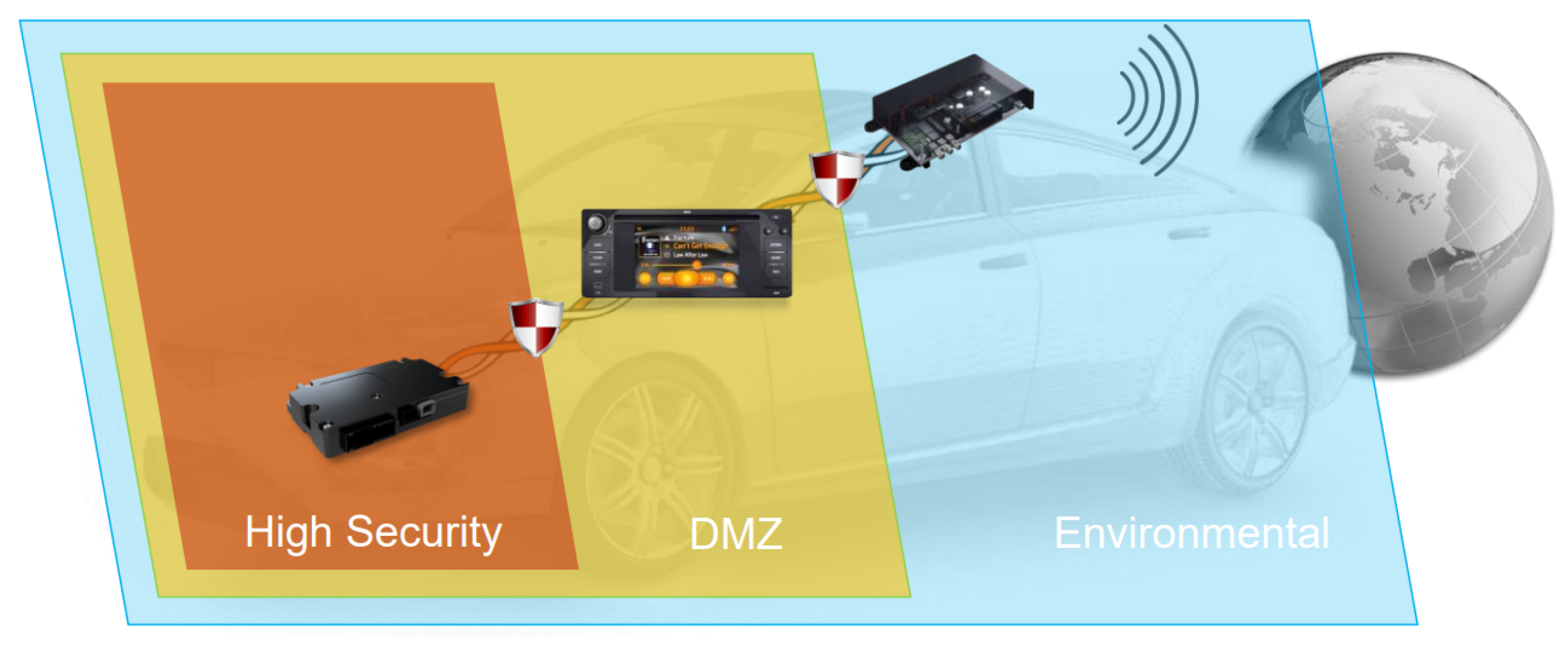

- SEIS Zone Model: SEIS —“Sicherheit in Eingebetteten IP-basierten Systemen/Security for embedded IP-based systems” is a zone-based in-vehicle architecture considering cybersecurity risks [13]. There are three zones in the SEIS zone model, as shown in Figure 19. These are: the environmental zone, the demilitarized zone (DMZ), and the high secure zone.

- Identity & Access Management (IAM): The IAM refers to the processes that manage digital identities and user access to data, systems, and resources. IAM security includes the policies, programs, and technologies that restricts identity-related access. In order to mitigate risks related to authentication and authorization in an automotive system, an IAM must be implemented.

- Intrusion Detection System (IDS)/Intrusion Prevention System (IPS): An IDS is used to detect an intrusion to an automotive system. There are IDS sensors inserted in different components within the in-vehicle which identify security incidents at the host and network levels. IDS sensors send data to the Intrusion Detection System Manager (IDSM), which filters the requests and generates qualified security events. Based on these events, security experts or Intrusion Prevention System (IPS) system located in the vehicle or in the cloud decide mitigation techniques. IDS uses pattern matching and machine learning techniques for the detection of the attacks.

7.2. Security Controls on Telematics

- Bluetooth protection: One good example of how Bluetooth-enabled devices are kept safe from different types of attacks is through installing the latest version of the Bluetooth -driver and continuously updating the security patches.

- WiFi protection: One good way of protecting the WiFi connection is by securing the network through strong passwords. This means that only those users possessing the password will have access to the network. To secure the WiFi, a series of security standards, such as the WiFi Protected Access (WPA) and WPA2 systems, have been introduced. The WPA2 uses the Advanced Encryption System (AES) and has been introduced in order to replace the more vulnerable Temporal Key Integrity Protocol (TKIP)-based WPA [15]. Furthermore, one of the most secure ways of preventing someone accessing a network is by using a virtual private network (VPN), as a method that may actually secure and encrypt certain types of communications. In addition, the vehicle and the legitimate devices should contain the latest version of the WiFi driver.

- 2G protection: 2G is the second generation of mobile communications. It is an old technology created in 1991 that has many vulnerabilities along with the Signaling System 7—SS7. One of the most critical problems of the 2G was the weak encryption between the tower and the device. Therefore, hackers could easily attack the device intercepting calls and messages. Moreover, anyone may easily impersonate a real 2G tower. Security aspects of 2G are detailed in the Technical Specifications, TS 02.09 and 03.20, published by 3GPP. In addition, 3GPP published specification of GSM-MILENAGE algorithm (TS 55.205) and several other encryption algorithms (TS 55.216–55.218, TS 55.226, TS 55.919).

- 3G protection: Mutual authentication is one of the priorities for 3G communication. Furthermore, the assurance regarding the authentication information and the keys that are not being re-used is required. Security architecture (TS 33.102), integration guidelines (TS 33.103), requirements for cryptographic algorithms (33.105), lawful inspection requirements and functions (TS 33.106–33.108), network domain security (TS 33.200, TS 33.310), Mobile Application Part - MAP application layer security (TS 33.210), security of multimedia broadcast/multicast services (TS TS 33.246), and other related cybersecurity related specifications are documented by 3GPP.

- 4G/5G protection: Some of the technical security requirements and specifications of 2G/3G are also valid for the subsequent generations of mobile communication technologies including 4G and 5G. For example, the security architecture specification numbered as TS 33.102 is also valid for 4G and 5G.

- DoS protection (rate-limiting): Denial of Service (DoS) attacks cause blocking of services and resources, so that the user cannot access and use these services/resources. This attack can be launched to the telematics unit as well. Attackers flood to the API endpoint of the telematics unit with a number of requests, so that legitimate users will not be able to use the services. This risk can be mitigated by using various filtering algorithms, such as upstream filtering and rate limiting. Rate limiting is the practice of restricting the number of requests to a service. This limit is defined by the service provider.

7.3. Security Controls on HPC/Brain Unit

- Secure boot: A method to protect the HPC is to make sure that the device only uses software trusted by the OEM. Basically, the signatures of the firmware are checked against the signature stored in the secure area of a hardware security module (HSM) or in other secure storage. If the signatures match, the software is considered secure and the operating system is allowed to boot on the device. It uses a chain of trust to make sure the next file in the list for booting is legitimate and has not been tampered.

- Secure debug: During debugging, using the On-Board Diagnostics (OBD) or Diagnostic Trouble Code (DTC), the system of the vehicle is checked for the software/hardware problems. The diagnostic performed while the vehicle is running should be stored securely using encryption and/or signature mechanisms. These diagnostic messages are mainly related to emissions. On the other hand, when diagnostics are performed in a workshop, all the ECUs are checked and the focus is on other aspects including functionality and reprogramming.

- Secure logging: Logs stored in the secondary storage (SSD) are used for many helpful intentions, such as intrusion and anomaly detection. They contain sensitive data such as privacy related info. Therefore, it becomes necessary to secure the logs. This can be achieved by using encryption mechanisms to store the log data after the encryption and limit the access to the logs for the right users/workshops. The users/workshops should be authenticated and authorized before accessing the logs.

- Secure storage: HPC should deploy one or more Hardware Security Modules, in short HSM [16], to store, generate, and protect cryptographic keys. In addition, such a module is able to fulfill the safety and timing requirements of a service (for example, airbag) due to its higher performance compared to the software implementation of executing a cryptographic function.

- Core pinning: Different security/security critical functions should run in separate area within the HPC. One way to separate it using so called core pinning, where each core of the micro-processors has its own vertical software stacks. Assuming that, a processor with 16 cores will have 16 separate operating systems, middlewares, and applications. Having each OS has its own computing and memory resources enables higher separation of resources.

- OS separation (virtualization): The next level of separation is achieved using virtualization techniques, where both bare metal hypervisor (when higher performance is required) or hosted hypervisor can be deployed. Bare metal hypervisor, such as VmWare, ESX, Hyper-V, and Xen contains device drivers which are able to run several operating systems by giving them own memory and computing resources. Hosted hypervisor such as VmWare Workstation, VirtualBox, does not contain device drivers, and are run on top of the host operating systems. The hypervisor is then able to host several guest operating systems by allocated them memory and computing resources.

- Application/process separation (containerization, docker): Containerization is the process of creating a single executable package of the software (including application code, libraries, and dependencies) of providing one or more vehicle functions. Contrary to the virtualization using VMs, the containerization process does not include a copy of the OS in the package, instead, it installs the run-time engine on the host OS. The docker is the platform that may be used for the containerization process.

7.4. Security Controls for the Ethernet

- MACSec: MACsec is commonly used in IT network, however, it is one of the new security controls for in-vehicle communication. One of the characteristics of the MACsec is that it protects data communication in the lower level (Ethernet) of the protocol stack. However, MACsec alone cannot ensure end-to-end security. Several reasons against deploying MACsec for the in-vehicle communication are higher cost, performance degradation, and very few providers offer MACsec features in their SoC (System on Chip).

- IPSec: It is an approach to secure data communication which uses IP protocols and is able to offer end-to-end (IP-to-IP) security. IPSec was originally designed for IPv6, but it is also used for IPv4. Some relevant references of IPSec are RFC3686, RFC4302, RFC4303, and RFC5996. IPSec is able to ensure authenticity, confidentiality, integrity of the messages between two ECUs having unique IP addresses. Virtual Private Network (VPN) uses IPSec protocols.

- Transport Layer Security (TLS): It is the successor of the secure socket layer (SSL) and this protocol is supported by the AUTOSAR architecture. TLS supports application-to-application (Port-to-Port) security. TLS is able to ensure authenticity, confidentiality, integrity of the messages between two applications running on two ECUs having unique port numbers. It is recommended to use the latest version of TLS protocol which is version 3 in 2022.

- Virtual Local Area Network (VLAN): It allows to create multiple logical networks in the in-vehicle architecture to separate one network from another, thereby, the service provider such as OEM and Tier1/Tier2 supplier is able to implement individual security policies in each of those networks.

7.5. Security Controls for CAN/LIN/FlexRay

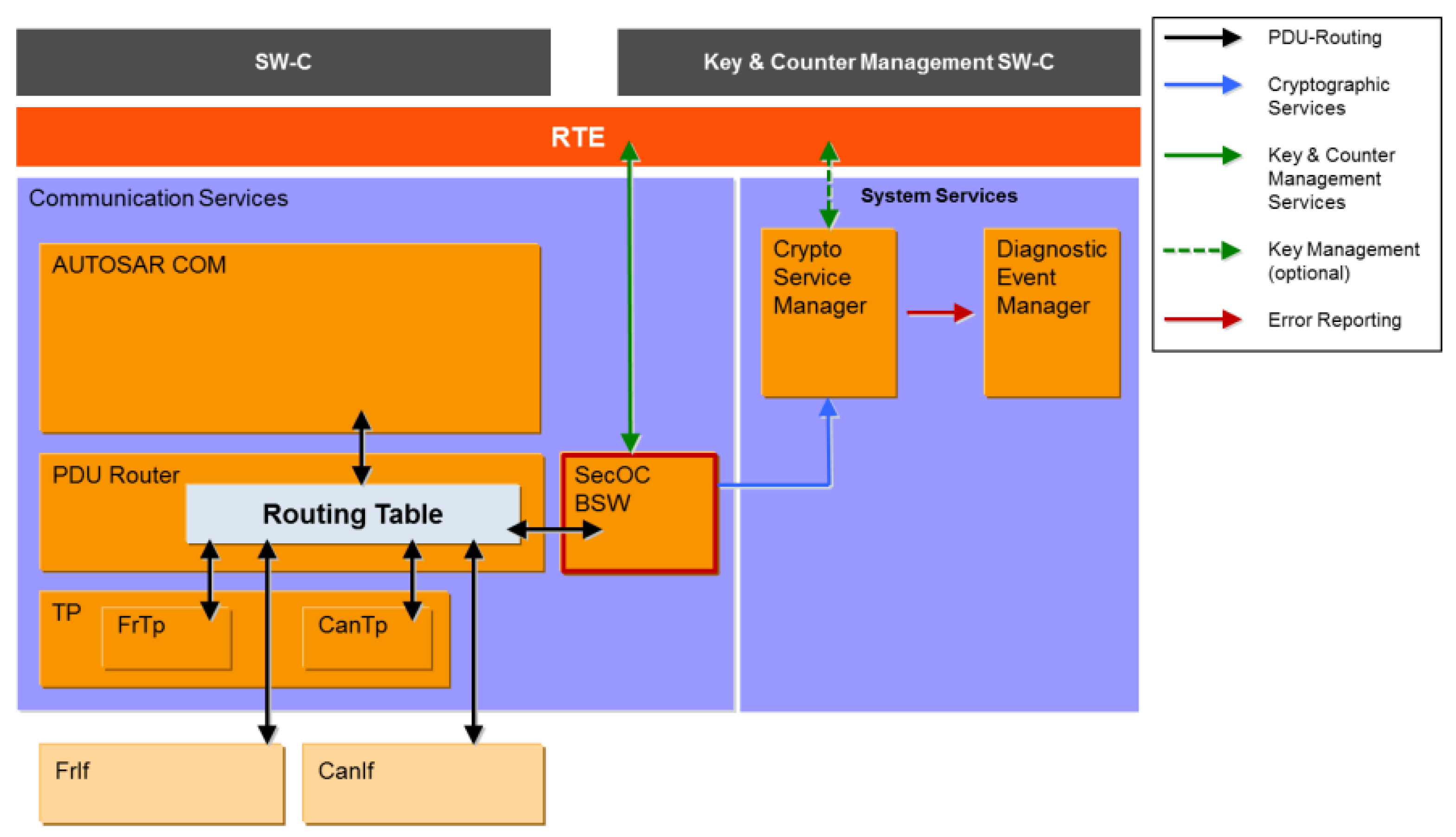

- Secure Onboard Communication (SecOC): To protect the in-vehicle communication that utilizes bus systems (CAN/LIN/FlexRay), AutoSAR [17] introduced the concept of SecOC (see Figure 20), which is used to validate the authenticity of the single transmitted protocol data unit. It also helps detecting attacks such as replay, spoofing, and tampering.

7.6. Security Controls on Sensors and Actuators

- Authentication: Sensors and actuators should be authenticated before initiating the communication to protect from spoofing threat categories.

- Logging: The logging information of the sensors and actuators should be encrypted and kept in a secure memory storage, and given only the legitimate users the access to the data.

8. Related Work

- Level 0: No automation;

- Level 1: Driver assistance;

- Level 2: Partial automation;

- Level 3: Conditional automation;

- Level 4: High automation;

- Level 5: Full automation.

- Cybersecurity automotive E/E architecture (CSAEEA);

- Motivation hacking E/E architecture (MHEEA);

- Autonomous vehicle SAE level (AVSAEL);

- Cybersecurity related to distributed architecture (CSRDA);

- E/E architecture for automotive security (EEAAS).

9. Results

Comparison of Automotive E/E Architectures

- Architecture: In the traditional architecture, the ECUs are located in different areas of the vehicle, and these ECUs (fully/partially) are able to communicate via a communication network to achieve a specific objective or goal. Thus, the architecture is distributed. In a one-brain architecture, there is only one brain that has control over the entire network and components connected to it. Thus, the one-brain architecture is centralized. Zone architecture means that depending on how many HPCs we have and their location, there can be two zones, as in the two-brain architecture, or three zones, as in the three-brain architecture. However, a zone-based architecture offers the advantage of having control of the vehicle functions on specific zones. To do this task, sometimes additional ECUs are connected to the brain architectures between the HPCs and the sensors/actuators.

- Performance: The term performance is defined as the qualitative level of a critical property at any considered point in time [11]. Therefore, in the vehicle architecture performance is one of the most important parameters, and can be measured in terms of cache size, memory size, and processing power. The performance in a traditional architecture is low, since it possesses low performance ECUs to host very few functions. The performance of a one-brain architecture is more than traditional architecture as it has one HPC and is able to host more functions than the traditional architecture with many ECUs. The performance of a vehicle with two-brain architecture is more than a vehicle with one HPC. The performance of a vehicle with three-brain architecture is more than the performance of a vehicle with two-brain architectures. By adding more HPCs, it is possible to increase the performance of a vehicle.

- Cost: The cost considered here is the expenditure required to realize a vehicle architecture. The cost to implement the traditional architecture is low because the ECUs are not expensive as compared to HPCs. Even though one hundred ECUs are used, the overall cost will be lower when compared to a single HPC. In a one-brain architecture, the cost is medium, since it has only one HPC. Similarly, in the two-brain system and three-brain system, the cost is high and higher, since these architectures have two HPCs and three HPCs, respectively. The functions are hosted accordingly to each HPC and the cost of the vehicle increases when it has more HPCs and more functions.

- Wiring complexity: The wiring complexity is very high in a traditional system, since it does not have HPCs. The traditional system has numerous ECUs and each ECU needs a set of wires to interface the different sensors and actuators connected to it. In a one-brain architecture, the wiring complexity is low, since there is only one brain and centralized wiring requires less interconnections. In a two-brain architecture, the complexity increases to medium, as compared to one-brain because of the two brains (two zones). Similarly, in the three-brain system, the complexity for the connection of wires is high as compared to the other architectures. To conclude, the complexity is the highest in the traditional architecture.

- Scalability: Scalability is defined as the setting of the scope of capabilities of a system, as determined by its functionality [11]. In the traditional architecture, ECUs are limited to a set of functions and therefore, the scalability is very limited. Coming to one-brain architecture, since all the functions are already assigned to a single HPC, there is no scalability. In two-brain and three-brain architectures, there is a possibility of scaling, since these architectures have multiple HCPs and each HPC will still have sufficient computational power to compensate the added functionalities.

- Redundancy: Redundancy is one of the most critical parameters which is required in the case of a particular system failure. In the traditional architecture, the possibility of having redundancy for safety critical features is possible, but it is very low. The redundancy is possible in the traditional architecture using redundant ECUs to host the same function. The redundancy, however, cannot be implemented using core pinning or virtualization techniques which are possible in the HPC-based architectures. In a one-brain architecture, since there is only one brain, in the case of the failure of that brain, there is no possibility of redundancy unless a second brain is introduced. When vertical software stacks are implemented on top of processor-cores and core pinning, redundant functions can be hosted on top of multiple cores. Implementing virtualization techniques, redundancy can also be realized on a HPC. Since two-brain and three-brain architectures have more memory and computing resources, it is possible to implement the redundancy mechanisms. Human lives are of the utmost importance and being able to make sure that the systems in a vehicle are more fail safe due to additional functions that could save a life.

- Load-balancing: Load-balancing means that the system is able to balance the workload and share it among processes. The traditional architecture is not made for load balancing. However, it is possible to implement mechanisms to do this. The load-balancing of different cores in the SoC of a one-brain (HPC) can be implemented. However, load-balancing is easier to implement by decoupled hardware devices such as two-brain and three-brain architectures.

- Vulnerability: The topic of vulnerability is a widely-discussed one, as it plays a major role in determining the risk levels of an asset/component. Vulnerability includes the weakness of an asset or group of assets which can be exploited by a threat of an attacker [11]. Threats will always exist, but by managing the level of vulnerability, greater levels of security can be ensured and the probability of an attack drops significantly. In this field, the traditional architecture shines, as if even one ECU gets hacked, the design ensures that the others are safe. On the other hand, this architecture imposes severe limitations on other fields, so we need to reach a compromise. Adding HPCs in the design increases the grade of vulnerability, because if the brain is hacked, the vehicle may be prone to an accident. With three brains, we have a higher level of vulnerability. However, by deploying appropriate security controls such as IDS/IPS/firewall, the attacks can be minimized even though there are vulnerabilities in the system/architecture.

- Troubleshooting: Vehicles are made to be driven; systems are made to be used and eventually parts are bound to become worn out or damaged. Furthermore, sometimes these damages are not easy to diagnose in complex vehicle architectures. When speaking about the criteria for troubleshooting a vehicle, we are referring to the efforts needed to detect a problem. Troubleshooting in a traditional architecture takes the most effort since it has higher complexity and many ECUs. The troubleshooting process can be considerably shortened by introducing HPCs in the architecture. Although the number of efforts increases with every brain added, overall traditional architectures have the most effort required for troubleshooting.

- Repairability: Repairability measures the efforts needed to repair a component or asset in an architecture. Repairing the ECU of a vehicle can be a tedious process, especially when dealing with the traditional architecture, because of its wiring complexity and distributed architecture which have hundred of ECUs. By introducing the one-brain architecture, the difficulty of the process drops significantly and steadily increases with every extra HPC that is added.

- Memory management: It is a method for coordinating and controlling the computer’s main memory. Thus, in the case of the traditional architecture, memory management is not an important topic as the ECU has very few functions (typically, one or two functions). However, in the other three architectures, memory management is a must, so HPCs are needed to properly manage the space and the allocation of files, so that the operating system, applications, and other running processes have enough memory to perform the operations.

- Weight: The weight of a vehicle is a key parameter when talking about speed, acceleration, environmental liability, or fuel consumption. In the current state, wires, cables, and other parts needed for the traditional architecture make the vehicles heavier than they should be. Switching to an HPCs-based architecture could lower the weight and thus improve other parameters such as those mentioned above. However, with each additional HPC comes more weight added to the vehicle.

- Software update: In the traditional architecture, with few exceptions, the software update is done manually. This means that the user has to take the vehicle to the OEM/distributor and the update is done by connecting the vehicle physically. In one-, two-, and three-brain architectures, the software update can be automated using over-the-air (OTA) update, whenever there is new software/update available.

10. Limitations and Future Scope

- Traditional Architecture

- One-Brain Architecture

- Two-Brain Architecture

- Three-Brain Architecture

11. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Wu, W.; Kurachi, R.; Zeng, G.; Wang, Y.; Takada, H.; Li, K. Intelligent Connected Vehicles. In Cybersecurity and High-Performance Computing Environments; Chapman and Hall/CRC: London, UK, 2022; pp. 285–308. [Google Scholar]

- Electrical/Electronic (E/E) Architecture; Automotive World Special Report: Penarth, UK, 2021; p. 1. Available online: https://www.automotiveworld.com/special-reports/electrical-electronic-e-e-architecture/ (accessed on 2 October 2022).

- Sukhija, N.; Bautista, E.; Champaneri, K. Cybersecurity and High-Performance Computing Ecosystems. In Cybersecurity and High-Performance Computing Environments: Integrated Innovations, Practices, and Applications; Chapman and Hall/CRC: London, UK, 2022; p. 1. [Google Scholar]

- Limbasiya, T.; Ghosal, A.; Conti, M. AutoSec: Secure Automotive Data Transmission Scheme for In-Vehicle Networks. In Proceedings of the ICDCN 2022: 23rd International Conference on Distributed Computing and Networking, Delhi, India, 4–7 January 2022; Association for Computing Machinery: New York, NY, USA, 2022; pp. 208–216. [Google Scholar] [CrossRef]

- Ayres, N.; Deka, L.; Paluszczyszyn, D. Continuous Automotive Software Updates through Container Image Layers. Electronics 2021, 10, 739. [Google Scholar] [CrossRef]

- Shon, T. In-Vehicle Networking/Autonomous Vehicle Security for Internet of Things/Vehicles. Electronics 2021, 10, 637. [Google Scholar] [CrossRef]

- Xie, Y.; Zhou, Y.; Xu, J.; Zhou, J.; Chen, X.; Xiao, F. Cybersecurity protection on in-vehicle networks for distributed automotive cyber-physical systems: State-of-the-art and future challenges. Softw. Pract. Exp. 2021, 51, 2108–2127. [Google Scholar] [CrossRef]

- Khatri, N.; Shrestha, R.; Nam, S.Y. Security Issues with In-Vehicle Networks, and Enhanced Countermeasures Based on Blockchain. Electronics 2021, 10, 893. [Google Scholar] [CrossRef]

- Microsoft Threat Modeling Tool 2016; Microsoft: Redmond, WA, USA, 2015; p. 1. Available online: https://www.microsoft.com/en-us/download/details.aspx?id=49168 (accessed on 2 October 2022).

- STRIDE Reference Sheets; OWASP—Open Web Application Security Project: Wakefield, MA, USA, 2022; p. 1. Available online: https://owasp.org/www-pdf-archive/STRIDE_Reference_Sheets.pdf (accessed on 2 October 2022).

- ISO/SAE 21434:2021; Road Vehicles—Cybersecurity Engineering. Technical Committee: ISO/TC 22/SC 32 Electrical and electronic components and general system aspects; ISO: Geneva, Switzerland, 2021. Available online: https://www.iso.org/obp/ui/#iso:std:iso-sae:21434:ed-1:v1:en (accessed on 2 October 2022).

- Ansys Medini Analyze for Cybersecurity; Ansys. Available online: https://www.ansys.com/products/safety-analysis/ansys-medini-analyze-for-cybersecurity (accessed on 2 October 2022).

- Glas, B. Sicherheit in Eingebetteten IP-Basierten Systemen, TP-4 Security. Available online: http://docplayer.org/6211994-Sicherheit-in-eingebetteten-ip-basierten-systemen-tp-4-security-dr-benjamin-glas-robert-bosch-gmbh-seite-1.html (accessed on 2 October 2022).

- Evolution of Mobile Technology. p. 1. Available online: https://iot.telenor.com/technologies/evolution-mobile-technology/ (accessed on 2 October 2022).

- Keep Your Home Wi-Fi Safe in 7 Simple Steps; Norton: Tempe, AZ, USA, 2022; Available online: https://us.norton.com/blog/iot/keep-your-home-wifi-safe (accessed on 2 October 2022).

- AVI. Hardware Security Module. Available online: https://avinetworks.com/glossary/hardware-security-modules/ (accessed on 2 October 2022).

- AutoSAR. Specification of Secure Onboard Communication. 2017. Available online: https://www.autosar.org/fileadmin/user_upload/standards/classic/4-3/AUTOSAR_SWS_SecureOnboardCommunication.pdf (accessed on 2 October 2022).

- On-Road Automated Driving (ORAD) Committee. Taxonomy and Definitions for Terms Related to Driving Automation Systems for On-Road Motor Vehicles; SAE International: Warrendale, PA, USA, 2021. [Google Scholar] [CrossRef]

- Davi, L.; Hatebur, D.; Heisel, M.; Wirtz, R. Combining Safety and Security in Autonomous Cars Using Blockchain Technologies. In Proceedings of the Computer Safety, Reliability, and Security, Turku, Finland, 11–13 September 2019; Romanovsky, A., Troubitsyna, E., Gashi, I., Schoitsch, E., Bitsch, F., Eds.; Springer International Publishing: Cham, Switzerland, 2019; pp. 223–234. [Google Scholar]

- Dang, Q.A.; Khondoker, R.; Wong, K.; Shunsuke, K. Threat Analysis of an Autonomous Vehicle Architecture. In Proceedings of the 2nd International Conference on Sustainable Technologies for Industry 4.0, STI 2020, Dhaka, Bangladesh, 19–20 December 2020. [Google Scholar]

- Koopman, P.; Wagner, M. Autonomous Vehicle Safety: An Interdisciplinary Challenge. IEEE Intell. Transp. Syst. Mag. 2017, 9, 90–96. [Google Scholar] [CrossRef]

- Cascetta, E.; Cartenì, A.; Di Francesco, L. Do autonomous vehicles drive like humans? A Turing approach and an application to SAE automation Level 2 cars. Transp. Res. Part C Emerg. Technol. 2022, 134, 103499. [Google Scholar] [CrossRef]

- Joubert, N.; Reid, T.G.R.; Noble, F. Developments in Modern GNSS and Its Impact on Autonomous Vehicle Architectures. In Proceedings of the 2020 IEEE Intelligent Vehicles Symposium (IV), Las Vegas, NV, USA, 19 October–13 November 2020; pp. 2029–2036. [Google Scholar] [CrossRef]

- Csikszentmihalyi, M. Flow: The Psychology of Optimal Experience; Harper & Row: New York, NY, USA, 1990. [Google Scholar]

- Beveren, J.V. A Conceptual Model of Hacker Development and Motivation. J. E-Bus. Int. Acad. E-Bus. 2001, 1, 1–9. [Google Scholar]

- Waszecki, P.; Mundhenk, P.; Steinhorst, S.; Lukasiewycz, M.; Karri, R.; Chakraborty, S. Automotive Electrical and Electronic Architecture Security via Distributed In-Vehicle Traffic Monitoring. IEEE Trans.-Comput.-Aided Des. Integr. Circuits Syst. 2017, 36, 1790–1803. [Google Scholar] [CrossRef]

- Plappert, C.; Fenzl, F.; Rieke, R.; Matteucci, I.; Costantino, G.; De Vincenzi, M. SECPAT: Security Patterns for Resilient Automotive E/E Architectures. In Proceedings of the 2022 30th Euromicro International Conference on Parallel, Distributed and Network-based Processing (PDP), Valladolid, Spain, 9–11 March 2022; pp. 255–264. [Google Scholar] [CrossRef]

- Schmittner, C.; Dobaj, J.; Macher, G.; Brenner, E. A Preliminary View on Automotive Cyber Security Management Systems. In Proceedings of the 2020 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 9–13 March 2020; pp. 1634–1639. [Google Scholar] [CrossRef]

- Mundhenk, P.; Steinhorst, S.; Lukasiewycz, M.; Fahmy, S.A.; Chakraborty, S. Security analysis of automotive architectures using probabilistic model checking. In Proceedings of the 2015 52nd ACM/EDAC/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 8–12 June 2015; pp. 1–6. [Google Scholar]

- Rumez, M.; Grimm, D.; Kriesten, R.; Sax, E. An overview of automotive service-oriented architectures and implications for security countermeasures. IEEE Access 2020, 8, 221852–221870. [Google Scholar] [CrossRef]

- Sagstetter, F.; Lukasiewycz, M.; Steinhorst, S.; Wolf, M.; Bouard, A.; Harris, W.R.; Jha, S.; Peyrin, T.; Poschmann, A.; Chakraborty, S. Security challenges in automotive hardware/software architecture design. In Proceedings of the 2013 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 18–22 March 2013; pp. 458–463. [Google Scholar]

- Scalas, M.; Giacinto, G. Automotive cybersecurity: Foundations for next-generation vehicles. In Proceedings of the 2019 2nd International Conference on new Trends in Computing Sciences (ICTCS), Amman, Jordan, 9–11 October 2019; pp. 1–6. [Google Scholar]

- Zhang, Y.; Shi, P.; Dong, C.; Liu, Y.; Shao, X.; Ma, C. Test and evaluation system for automotive cybersecurity. In Proceedings of the 2018 IEEE International Conference on Computational Science and Engineering (CSE), Bucharest, Romania, 29–31 October 2018; pp. 201–207. [Google Scholar]

- Marksteiner, S.; Marko, N.; Smulders, A.; Karagiannis, S.; Stahl, F.; Hamazaryan, H.; Schlick, R.; Kraxberger, S.; Vasenev, A. A process to facilitate automated automotive cybersecurity testing. In Proceedings of the 2021 IEEE 93rd Vehicular Technology Conference (VTC2021-Spring), Helsinki, Finland, 25–28 April 2021; pp. 1–7. [Google Scholar]

- Soni, P.; Pradhan, J.; Pal, A.K.; Islam, S.H. Cybersecurity Attack-resilience Authentication Mechanism for Intelligent Healthcare System. IEEE Trans. Ind. Inform. 2022. [Google Scholar] [CrossRef]

- Zelle, D.; Krauß, C.; Strauß, H.; Schmidt, K. On using TLS to secure in-vehicle networks. In Proceedings of the Proceedings of the 12th International Conference on Availability, Reliability and Security, Reggio Calabria, Italy, 29 August–1 September 2017; pp. 1–10. [Google Scholar]

- Plappert, C.; Zelle, D.; Gadacz, H.; Rieke, R.; Scheuermann, D.; Krauß, C. Attack Surface Assessment for Cybersecurity Engineering in the Automotive Domain. In Proceedings of the 2021 29th Euromicro International Conference on Parallel, Distributed and Network-Based Processing (PDP), Valladolid, Spain, 10–12 March 2021. [Google Scholar] [CrossRef]

- Messnarz, R.; Kreiner, C.; Riel, A. Integrating Automotive SPICE, Functional Safety, and Cybersecurity Concepts: A Cybersecurity Layer Model. Softw. Qual. Prof. 2016, 18, 13. [Google Scholar]

- Özarpa, C.; Kara, S.A.; ArapoĞLu, S. Development of a new architecture model for autonomous automobiles against syber attacks. In Proceedings of the 6nd International Conference on Material Science and Technology in Cappadocia (IMSTEC’21), Cappadocia, Turkey, 26–28 November 2021. [Google Scholar]

- Bandur, V.; Selim, G.; Pantelic, V.; Lawford, M. Making the case for centralized automotive e/e architectures. IEEE Trans. Veh. Technol. 2021, 70, 1230–1245. [Google Scholar] [CrossRef]

- Parmar, M.R.; Kumari, M.U.; Ramesh, S. Cyber Security in vehicle Communication. In Proceedings of the 2020 IEEE International Conference for Innovation in Technology (INOCON), Bangaluru, India, 6–8 November 2020; pp. 1–5. [Google Scholar]

- Bucaioni, A.; Patrizio, P. Technical Architectures for Automotive Systems; IEEE: Piscataway, NJ, USA, 2020. [Google Scholar]

- Traub, M.; Maier, A.; Kai, L.B. Future Automotive Architecture and the Impact of IT Trends. IEEE Softw. 2017, 34, 27–32. [Google Scholar] [CrossRef]

- Reinhardt, D.; Dannebaum, U.; Scheffer, M.; Traub, M. High Performance Processor Architecture for Automotive Large Scaled Integrated Systems within the European Processor Initiative Research Project; SAE Technical Paper 2019-01-0118; SAE International: Warrendale, PA, USA, 2019. [Google Scholar]

- Alcaide, S.; Kosmidis, L.; Hernandez, C.; Abella, J. Software-only based Diverse Redundancy for ASIL-D Automotive Applications on Embedded HPC Platforms. In Proceedings of the 2020 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), Frascati, Italy, 19–21 October 2020. [Google Scholar] [CrossRef]

- Hafeez, A.; Mohan, J.; Girdhar, M.; Awad, S.S. Machine Learning based ECU Detection for Automotive Security. In Proceedings of the 2021 17th International Computer Engineering Conference (ICENCO), Cairo, Egypt, 29–30 December 2021; pp. 73–81. [Google Scholar] [CrossRef]

- Zhang, H.; Pan, Y.; Lu, Z.; Wang, J.; Liu, Z. A Cyber Security Evaluation Framework for In-Vehicle Electrical Control Units. IEEE Access 2021, 9, 149690–149706. [Google Scholar] [CrossRef]

| Traditional | One-Brain | Two-Brain | Three-Brain | |

|---|---|---|---|---|

| 0 | 1 | 1 | 1 | |

| 100 | 0 | 0 | 0 | |

| 0 | 1 | 2 | 3 | |

| 800 | 800 | 800 | 800 | |

| 800 | 800 | 800 | 800 | |

| 800 | 800 | 800 | 800 | |

| 6400 | 6404 | 6408 | 6412 | |

| 3200 | 3202 | 3204 | 3206 | |

| 0 | 0 | 0 | 0 | |

| Total number of threats (T) | 37,400 | 36,830 | 36,854 | 36,878 |

| Keywords | Scopus | Web of Science | IEEE | Science Direct | Google Scholar |

|---|---|---|---|---|---|

| CSAEEA | 0 | 0 | 0 | 21 | 2980 |

| MHEEA | 0 | 0 | 0 | 78 | 8860 |

| AVSAELD | 204 | 122 | 70 | 1743 | 44,700 |

| CSRDA | 74 | 80 | 51 | 8237 | 363,000 |

| EEAAS | 114 | 0 | 16 | 4571 | 8890 |

| Attributes | Traditional | One-Brain | Two-Brain | Three-Brain |

|---|---|---|---|---|

| Architecture | Distributed | Centralized | Zonal | Zonal |

| Performance | Low | Medium | High | Higher |

| Cost | Low | Medium | High | Higher |

| Wiring Complexity | Higher | Low | Medium | High |

| Scalability | No | No | Yes | Yes |

| Redundancy | Very Low possibility | Low possibility | Medium possibility | High possibility |

| Load-Balancing | Very Low possibility | Low possibility | Medium possibility | High possibility |

| Vulnerability | Low | Medium | High | Higher |

| Trouble Shooting | Higher effort | Lowest effort | Medium effort | High effort |

| Repairability | Highest effort | Lowest effort | Medium effort | High effort |

| Memory Management | No specific management required | Yes | Yes | Yes |

| Weight | Heaviest | Lightest | Heavy | Heavier |

| Software Update | Mostly Manual | Automated (OTA) | Automated (OTA) | Automated (OTA) |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tany, N.S.; Suresh, S.; Sinha, D.N.; Shinde, C.; Stolojescu-Crisan, C.; Khondoker, R. Cybersecurity Comparison of Brain-Based Automotive Electrical and Electronic Architectures. Information 2022, 13, 518. https://doi.org/10.3390/info13110518

Tany NS, Suresh S, Sinha DN, Shinde C, Stolojescu-Crisan C, Khondoker R. Cybersecurity Comparison of Brain-Based Automotive Electrical and Electronic Architectures. Information. 2022; 13(11):518. https://doi.org/10.3390/info13110518

Chicago/Turabian StyleTany, Nadera Sultana, Sunish Suresh, Durgesh Nandan Sinha, Chinmay Shinde, Cristina Stolojescu-Crisan, and Rahamatullah Khondoker. 2022. "Cybersecurity Comparison of Brain-Based Automotive Electrical and Electronic Architectures" Information 13, no. 11: 518. https://doi.org/10.3390/info13110518

APA StyleTany, N. S., Suresh, S., Sinha, D. N., Shinde, C., Stolojescu-Crisan, C., & Khondoker, R. (2022). Cybersecurity Comparison of Brain-Based Automotive Electrical and Electronic Architectures. Information, 13(11), 518. https://doi.org/10.3390/info13110518