Design and Implementation of Ternary Logic Integrated Circuits by Using Novel Two-Dimensional Materials

Abstract

1. Introduction

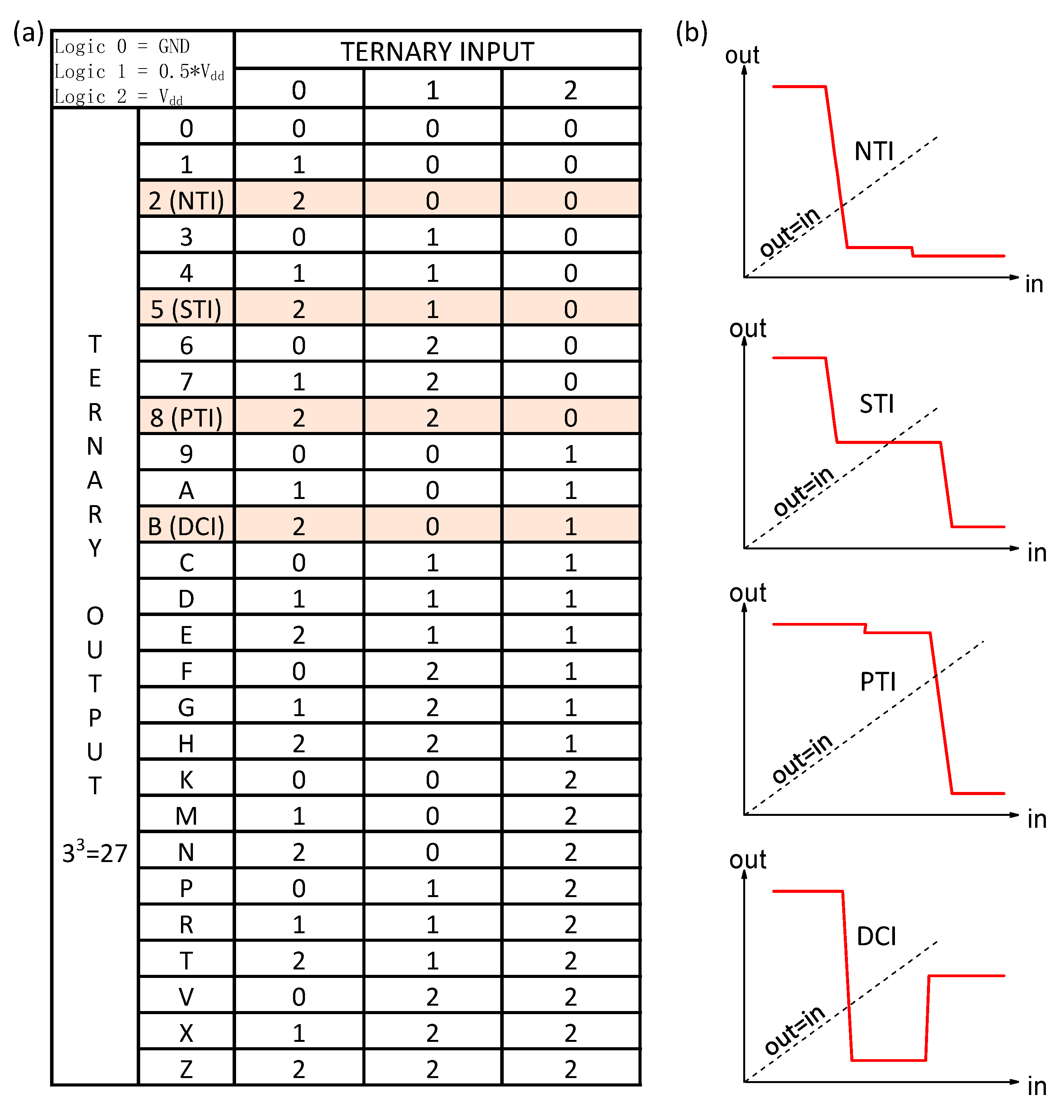

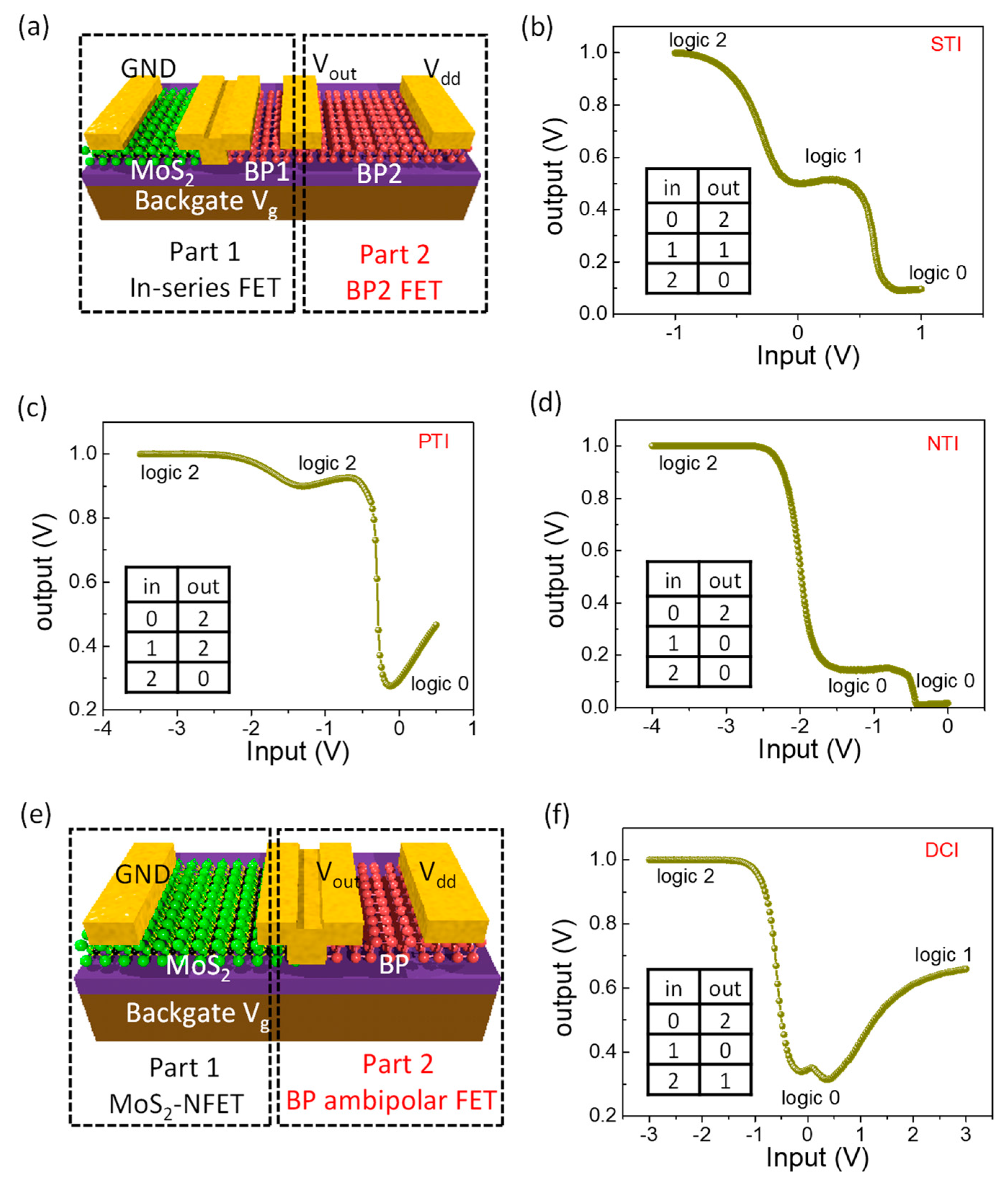

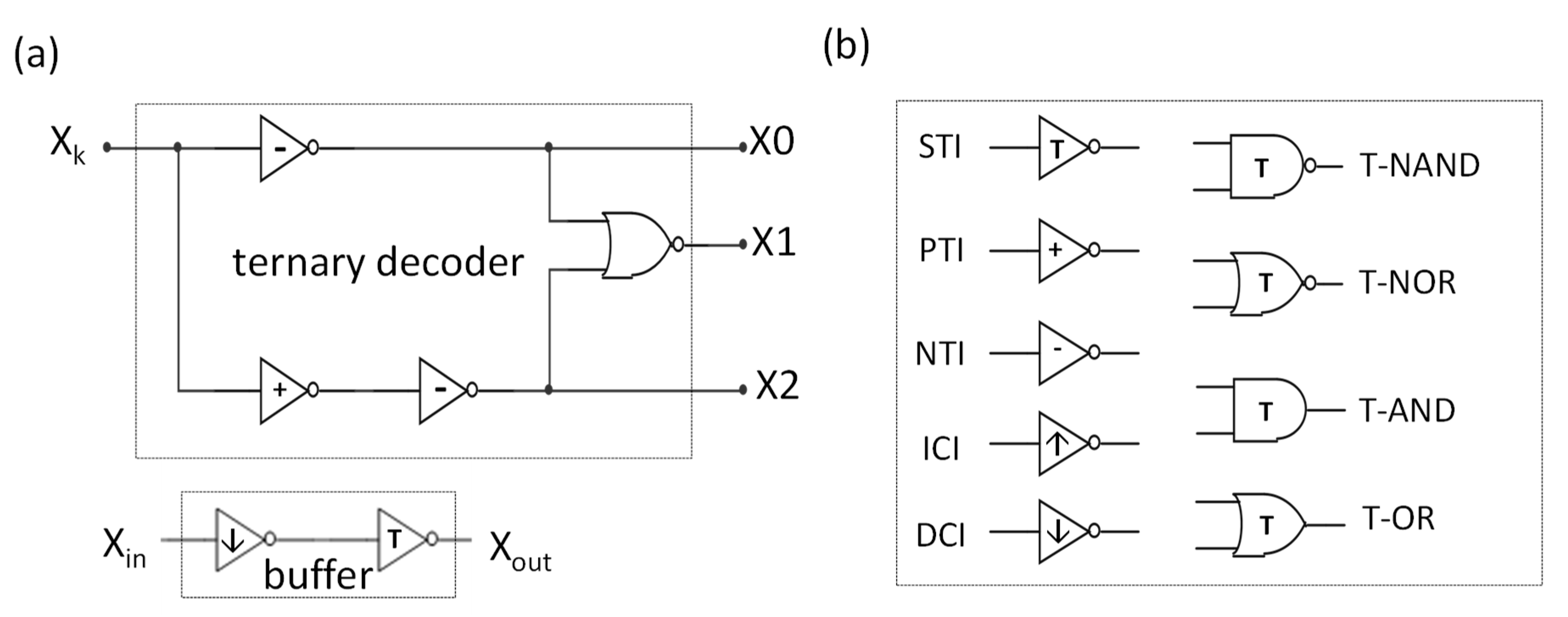

2. Demonstration of Ternary Logic Gates

3. Design of Ternary Logic Circuits

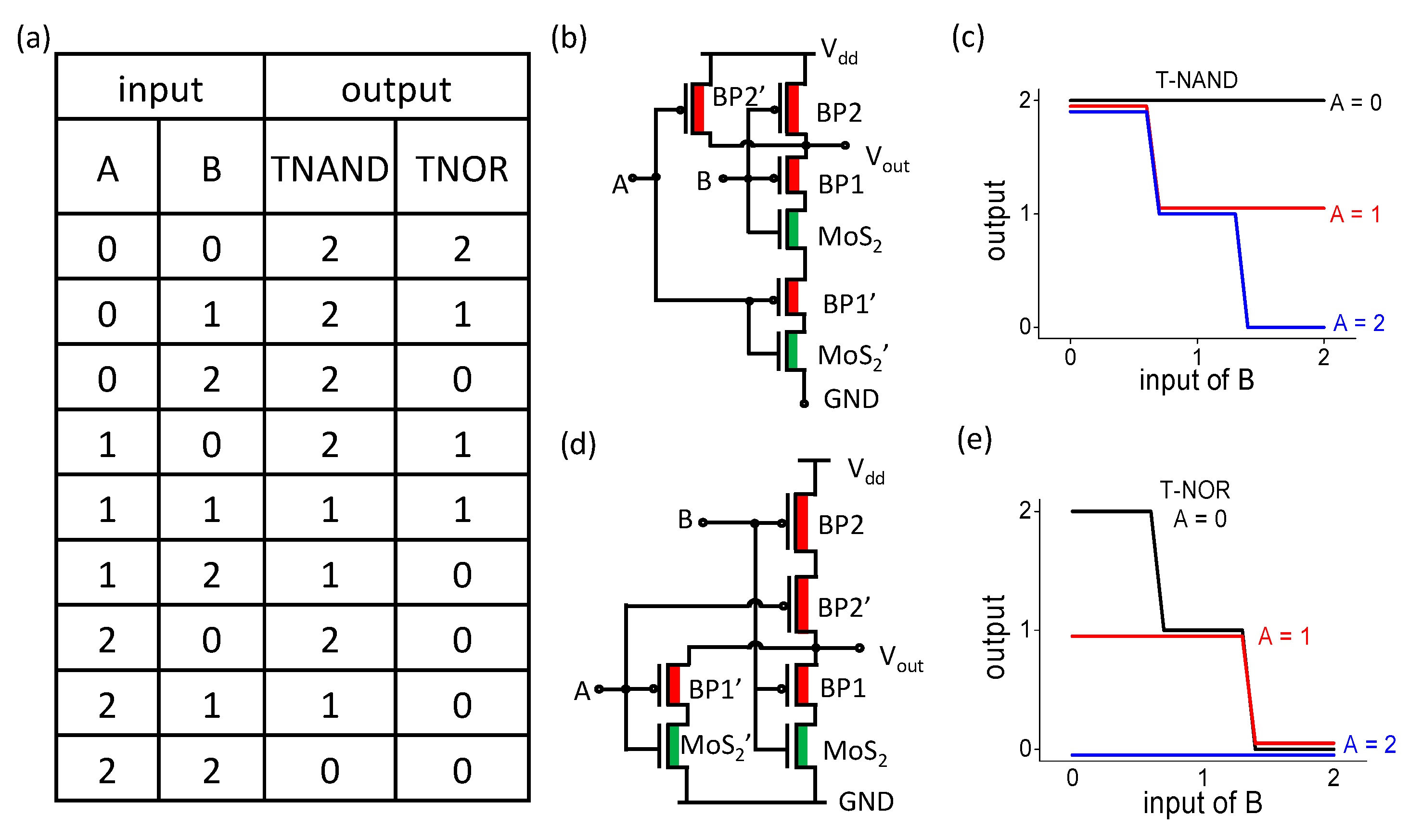

3.1. Functional Ternary Logic Gates

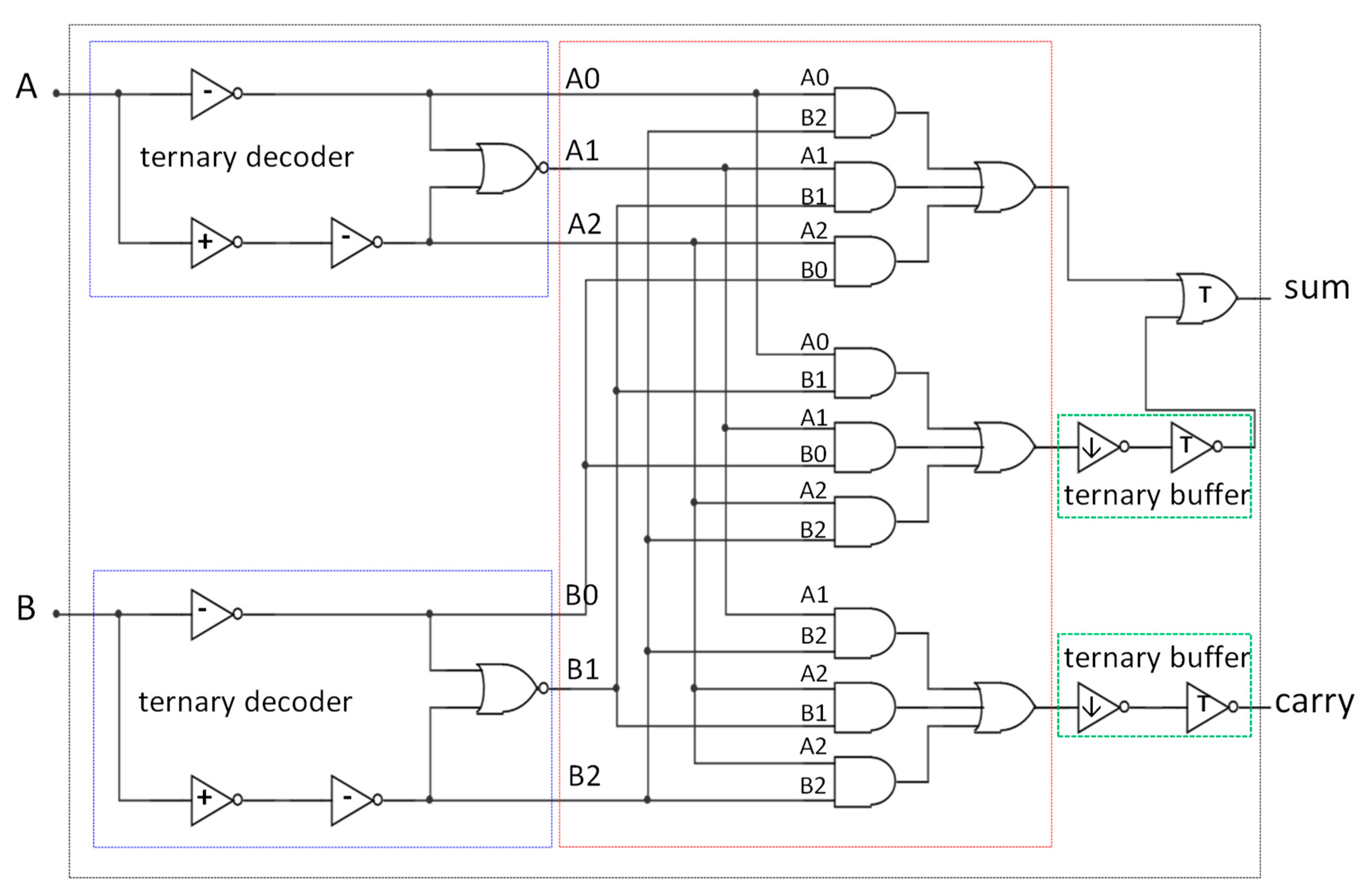

3.2. Conventional Design of Ternary Adder

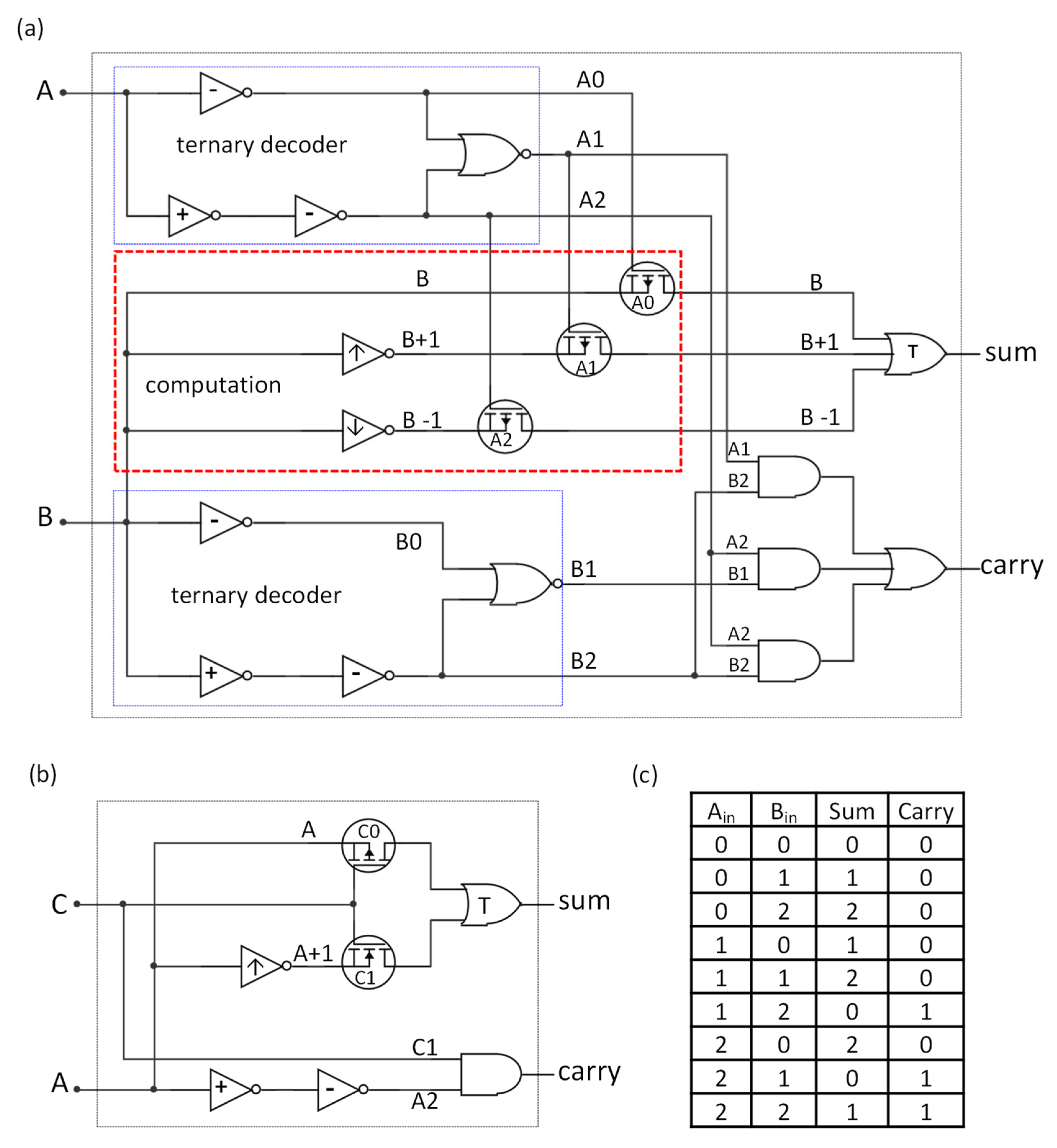

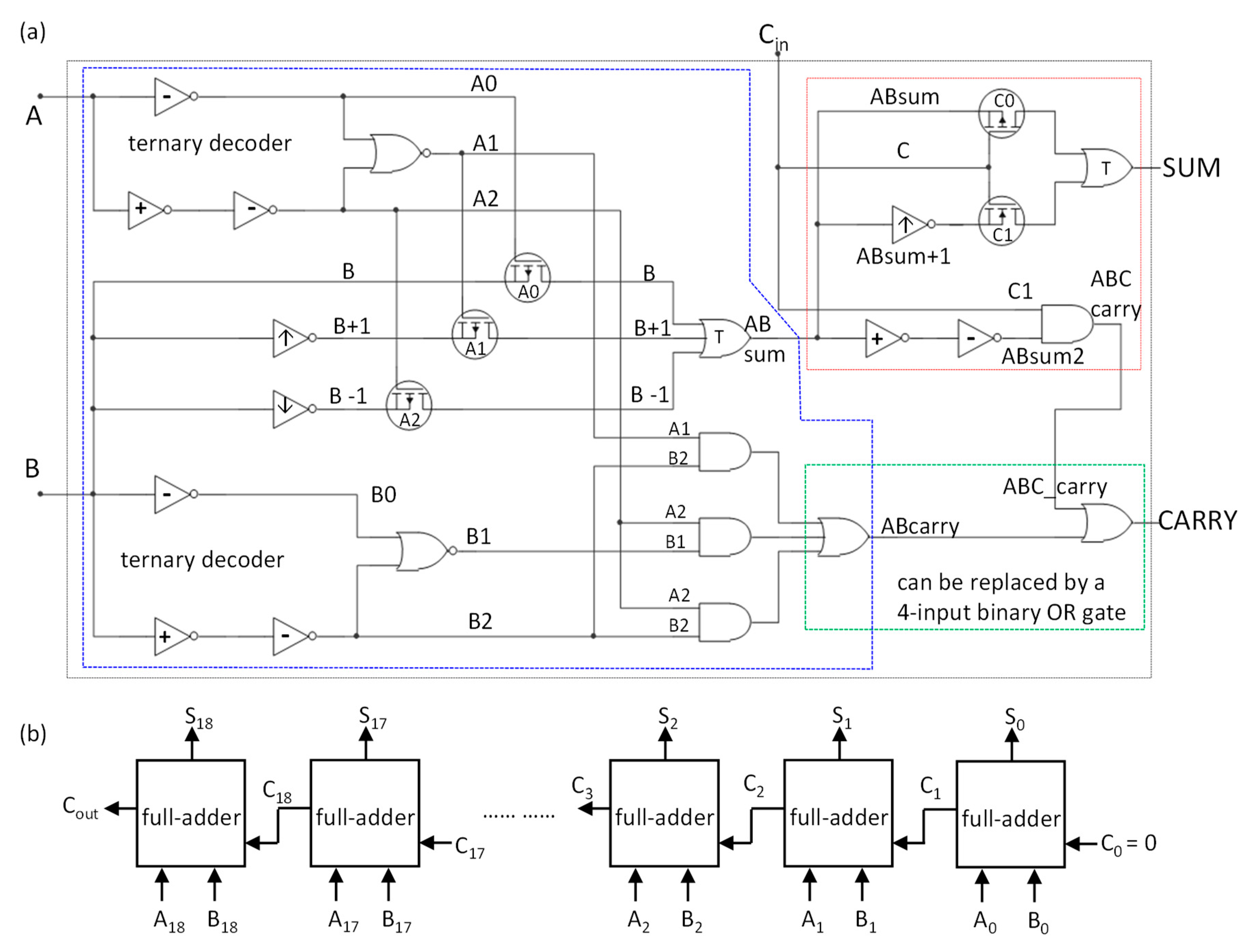

3.3. Our Optimized Design of Ternary Adder

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Hurst, S.L. Multiple-valued logic? Its status and its future. IEEE Trans. Comput. 1984, 33, 1160–1179. [Google Scholar] [CrossRef]

- Smith, K.C. A multiple valued logic: A tutorial and appreciation. Computer 1988, 21, 17–27. [Google Scholar] [CrossRef]

- Tirumalai, P.P.; Butler, J.T. Minimization algorithms for multiple-valued programmable logic arrays. IEEE Trans. Comput. 1991, 40, 167–177. [Google Scholar] [CrossRef]

- Miller, D.M. Multiple-valued logic design tools. In Proceedings of the Twenty-Third International Symposium on Multiple-Valued Logic, Sacramento, CA, USA, 24–27 May 1993; pp. 2–11. [Google Scholar]

- Srivastava, A.; Venkatapathy, K. Design and implementation of a low power ternary full adder. VLSI Des. 1996, 4, 75–81. [Google Scholar] [CrossRef][Green Version]

- Miller, D.M.; Thornton, M.A. Multiple valued logic: Concepts and representations. Synth. Lect. Digit. Circuits Syst. 2007, 2, 1–127. [Google Scholar] [CrossRef]

- Iijima, S.; Ichihashi, T. Single-shell carbon nanotubes of 1-nm diameter. Nature 1993, 363, 603. [Google Scholar] [CrossRef]

- Thess, A.; Lee, R.; Nikolaev, P.; Dai, H.; Petit, P.; Robert, J.; Xu, C.; Lee, Y.H.; Kim, S.G.; Rinzler, A.G.; et al. Crystalline ropes of metallic carbon nanotubes. Science 1996, 273, 483–487. [Google Scholar] [CrossRef]

- Raychowdhury, A.; Roy, K. A novel multiple-valued logic design using ballistic carbon nanotube FETs. In Proceedings of the 34th International Symposium on Multiple-Valued Logic, Toronto, ON, Canada, 22–22 May 2004; pp. 14–19. [Google Scholar]

- Raychowdhury, A.; Roy, K. Carbon-nanotube-based voltage-mode multiple-valued logic design. IEEE Trans. Nanotechnol. 2005, 4, 168–179. [Google Scholar] [CrossRef]

- Lin, S.; Kim, Y.B.; Lombardi, F. CNTFET-based design of ternary logic gates and arithmetic circuits. IEEE Trans. Nanotechnol. 2011, 10, 217–225. [Google Scholar] [CrossRef]

- Keshavarzian, P.; Sarikhani, R. A novel CNTFET-based ternary full adder. Circuits Syst. Signal Process. 2014, 33, 665–679. [Google Scholar] [CrossRef]

- Liang, J.; Chen, L.; Han, J.; Lombardi, F. Design and evaluation of multiple valued logic gates using pseudo N-type carbon nanotube FETs. IEEE Trans. Nanotechnol. 2014, 13, 695–708. [Google Scholar] [CrossRef]

- Das, D.; Banerjee, A.; Prasad, V. Design of ternary logic circuits using CNTFET. In Proceedings of the 2018 International Symposium on Devices, Circuits and Systems (ISDCS), Howrah, India, 29–31 March 2018; pp. 1–6. [Google Scholar]

- Firouzi, S.; Tabrizchi, S.; Sharifi, F.; Badawy, A.H. High performance, variation-tolerant CNFET ternary full adder a process, voltage, and temperature variation-resilient design. Comput. Electr. Eng. 2019, 77, 205–216. [Google Scholar] [CrossRef]

- Jeong, J.W.; Choi, Y.E.; Kim, W.S.; Park, J.H.; Kim, S.; Shin, S.; Lee, K.; Chang, J.; Kim, S.J.; Kim, K.R. Tunnelling-based ternary metal–oxide–semiconductor technology. Nat. Electron. 2019, 2, 307–312. [Google Scholar] [CrossRef]

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 2011, 6, 147. [Google Scholar] [CrossRef] [PubMed]

- Splendiani, A.; Sun, L.; Zhang, Y.; Li, T.; Kim, J.; Chim, C.Y.; Galli, G.; Wang, F. Emerging photoluminescence in monolayer MoS2. Nano Lett. 2010, 10, 1271–1275. [Google Scholar] [CrossRef] [PubMed]

- Das, S.; Chen, H.Y.; Penumatcha, A.V.; Appenzeller, J. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett. 2012, 13, 100–105. [Google Scholar] [CrossRef]

- Li, X.; Yang, L.; Si, M.; Li, S.; Huang, M.; Ye, P.; Wu, Y. Performance potential and limit of MoS2 transistors. Adv. Mater. 2015, 27, 1547–1552. [Google Scholar] [CrossRef]

- Li, L.; Yu, Y.; Ye, G.J.; Ge, Q.; Ou, X.; Wu, H.; Feng, D.; Chen, X.H.; Zhang, Y. Black phosphorus field-effect transistors. Nat. Nanotechnol. 2014, 9, 372. [Google Scholar] [CrossRef]

- Xia, F.; Wang, H.; Jia, Y. Rediscovering black phosphorus as an anisotropic layered material for optoelectronics and electronics. Nat. Commun. 2014, 5, 4458. [Google Scholar] [CrossRef]

- Liu, H.; Neal, A.T.; Zhu, Z.; Luo, Z.; Xu, X.; Tománek, D.; Ye, P.D. Phosphorene: An unexplored 2D semiconductor with a high hole mobility. ACS Nano 2014, 8, 4033–4041. [Google Scholar] [CrossRef]

- Su, Y.; Kshirsagar, C.U.; Robbins, M.C.; Haratipour, N.; Koester, S.J. Symmetric complementary logic inverter using integrated black phosphorus and MoS2 transistors. 2D Mater. 2016, 3, 011006. [Google Scholar] [CrossRef]

- Perello, D.J.; Chae, S.H.; Song, S.; Lee, Y.H. High-performance n-type black phosphorus transistors with type control via thickness and contact-metal engineering. Nat. Commun. 2015, 6, 7809. [Google Scholar] [CrossRef] [PubMed]

- Nourbakhsh, A.; Zubair, A.; Dresselhaus, M.S.; Palacios, T. Transport properties of a MoS2/WSe2 heterojunction transistor and its potential for application. Nano Lett. 2016, 16, 1359–1366. [Google Scholar] [CrossRef] [PubMed]

- Shim, J.; Oh, S.; Kang, D.H.; Jo, S.H.; Ali, M.H.; Choi, W.Y.; Heo, K.; Jeon, J.; Lee, S.; Kim, M.; et al. Phosphorene/rhenium disulfide heterojunction-based negative differential resistance device for multi-valued logic. Nat. Commun. 2016, 7, 13413. [Google Scholar] [CrossRef] [PubMed]

- Huang, M.; Li, S.; Zhang, Z.; Xiong, X.; Li, X.; Wu, Y. Multifunctional high-performance van der Waals heterostructures. Nat. Nanotechnol. 2017, 12, 1148. [Google Scholar] [CrossRef] [PubMed]

- Shim, J.; Jo, S.H.; Kim, M.; Song, Y.J.; Kim, J.; Park, J.H. Light-triggered ternary device and inverter based on heterojunction of van der waals materials. ACS Nano 2017, 11, 6319–6327. [Google Scholar] [CrossRef] [PubMed]

- Kobashi, K.; Hayakawa, R.; Chikyow, T.; Wakayama, Y. Multi-Valued Logic Circuits Based on Organic Anti-ambipolar Transistors. Nano Lett. 2018, 18, 4355–4359. [Google Scholar] [CrossRef] [PubMed]

- Kim, J.B.; Li, J.; Choi, Y.; Whang, D.; Hwang, E.; Cho, J.H. Photosensitive Graphene P–N Junction Transistors and Ternary Inverters. ACS Appl. Mater. Interfaces 2018, 10, 12897–12903. [Google Scholar] [CrossRef] [PubMed]

| CMOS Binary | CMOS Ternary | CNT Ternary Circuits | 2D Ternary | ||||

|---|---|---|---|---|---|---|---|

| Circuits | ref.5 | ref.11 | ref.12 | ref.15 | (This Work) | ||

| Circuit structures | XOR, AND, OR gates | Decoder Binary logic gates | Decoder Binary logic gates | Transistor networks | 1.capacitive circuits 2.decoder 3.transistor networks | 1. Decoder 2. Ternary logic gates 3. Binary logic gates | |

| Description | Classical design | Classical design | Classical design Similar to CMOS ternary | Optimized design with networks. Reduced delay | Optimized design with capacitors. High speed and energy-efficient | Optimized design with ternary gate. Reduced circuits area | |

| number of FETs in half adder | 28 | 114 | 118 | - | - | design1: 72 design2: 25 | |

| number of FETs in full adder | 62 | 234 | 242 | 114 | 2 capacitors2 decoders44 transistors | 99 | |

| computation steps per bit/trit | 10 | 22 | 22 | - | - | 12 | |

| ~1G data size | serial levels | 30 | 19 | 19 | 19 | 19 | 19 |

| number of FETs | 62 × 30 = 1860 | 234 × 19 = 4446 | 242 × 19 = 4598 | 114 × 19 = 2166 | - | 99 × 19 = 1881 | |

| computation steps | 300 | 418 | 418 | - | - | 228 | |

| Normalized required computation steps | 100% | 129% | 129% | - | - | 70% | |

| Normalized required transistors | 100% | 221% | 228% | 107% | - | 93% | |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, M.; Wang, X.; Zhao, G.; Coquet, P.; Tay, B. Design and Implementation of Ternary Logic Integrated Circuits by Using Novel Two-Dimensional Materials. Appl. Sci. 2019, 9, 4212. https://doi.org/10.3390/app9204212

Huang M, Wang X, Zhao G, Coquet P, Tay B. Design and Implementation of Ternary Logic Integrated Circuits by Using Novel Two-Dimensional Materials. Applied Sciences. 2019; 9(20):4212. https://doi.org/10.3390/app9204212

Chicago/Turabian StyleHuang, Mingqiang, Xingli Wang, Guangchao Zhao, Philippe Coquet, and Bengkang Tay. 2019. "Design and Implementation of Ternary Logic Integrated Circuits by Using Novel Two-Dimensional Materials" Applied Sciences 9, no. 20: 4212. https://doi.org/10.3390/app9204212

APA StyleHuang, M., Wang, X., Zhao, G., Coquet, P., & Tay, B. (2019). Design and Implementation of Ternary Logic Integrated Circuits by Using Novel Two-Dimensional Materials. Applied Sciences, 9(20), 4212. https://doi.org/10.3390/app9204212