Design and Investigation of a Dual Material Gate Arsenic Alloy Heterostructure Junctionless TFET with a Lightly Doped Source

Abstract

1. Introduction

2. Methods

3. Results and Discussion

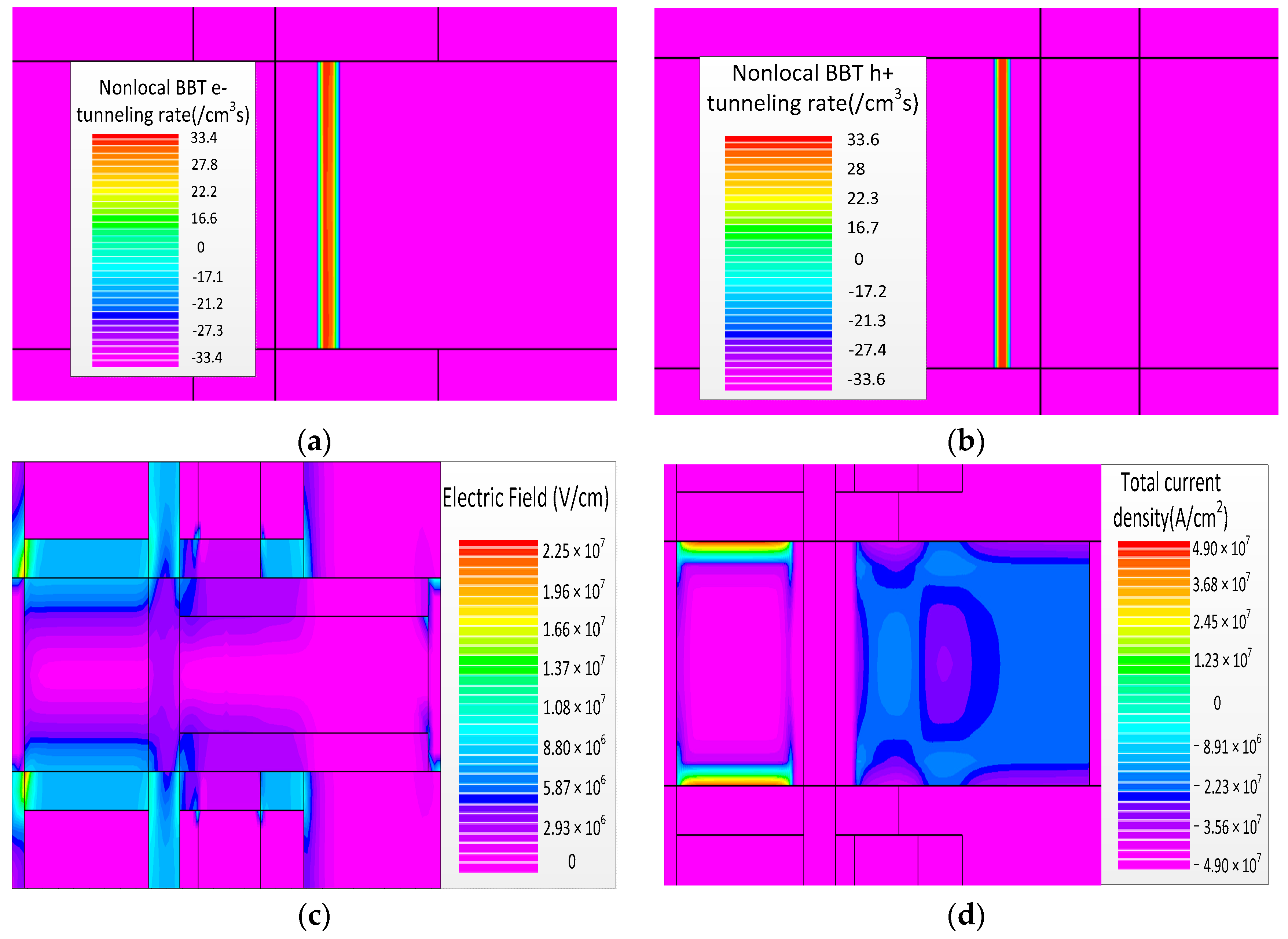

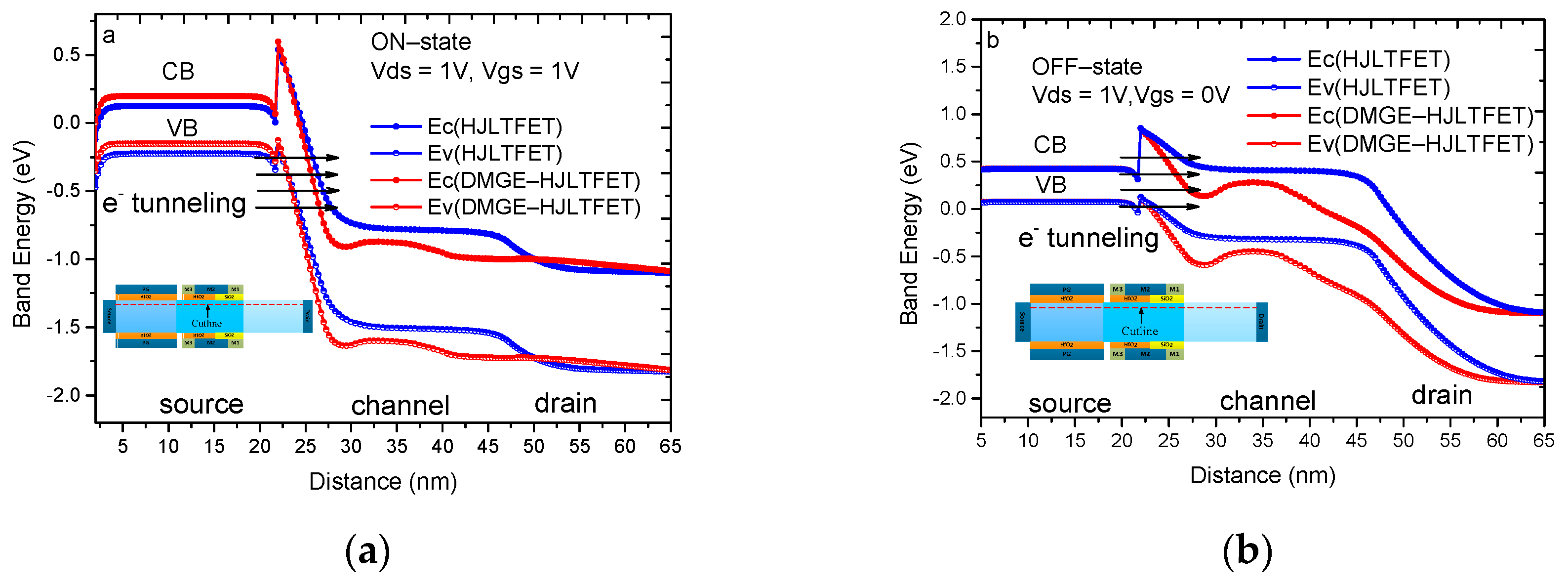

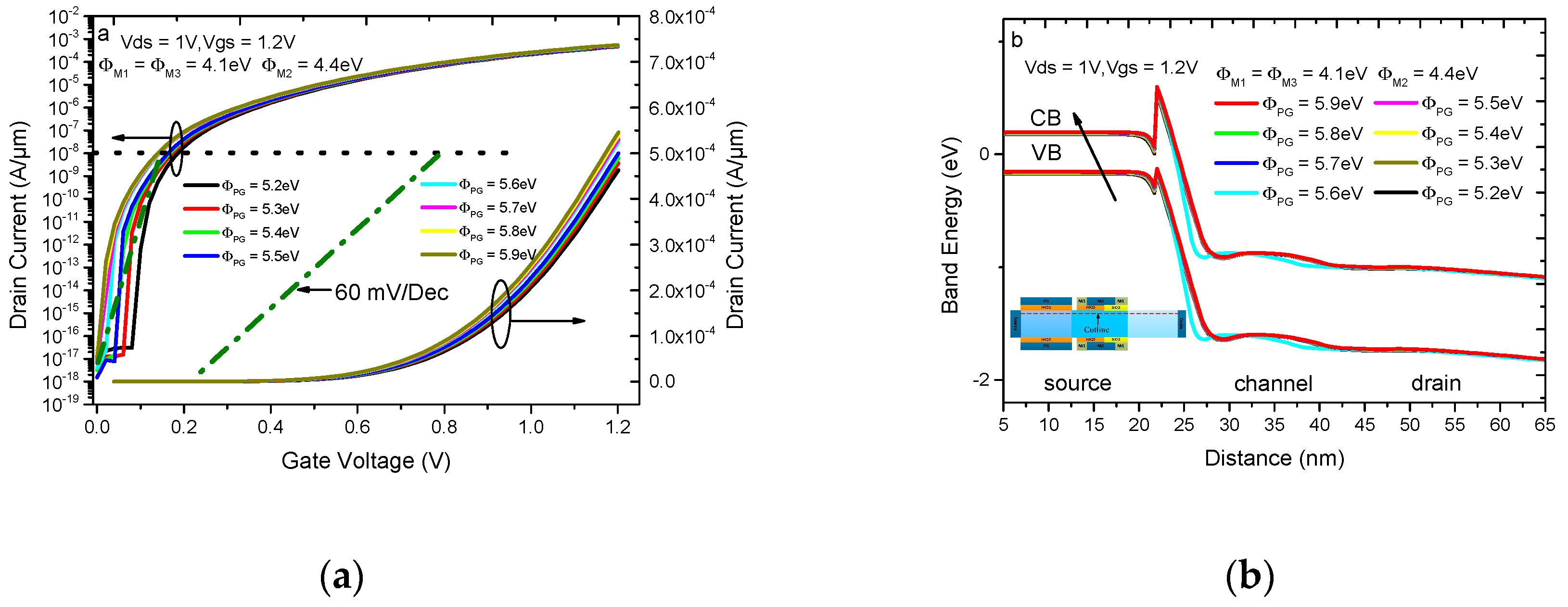

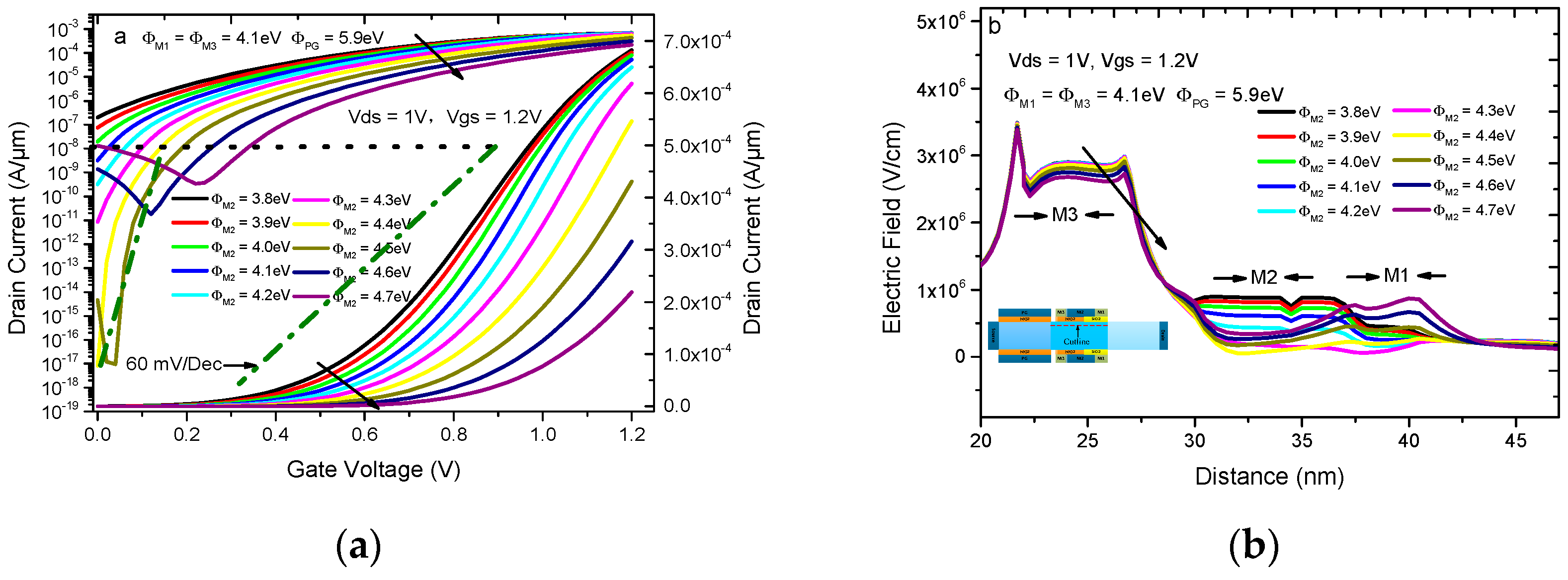

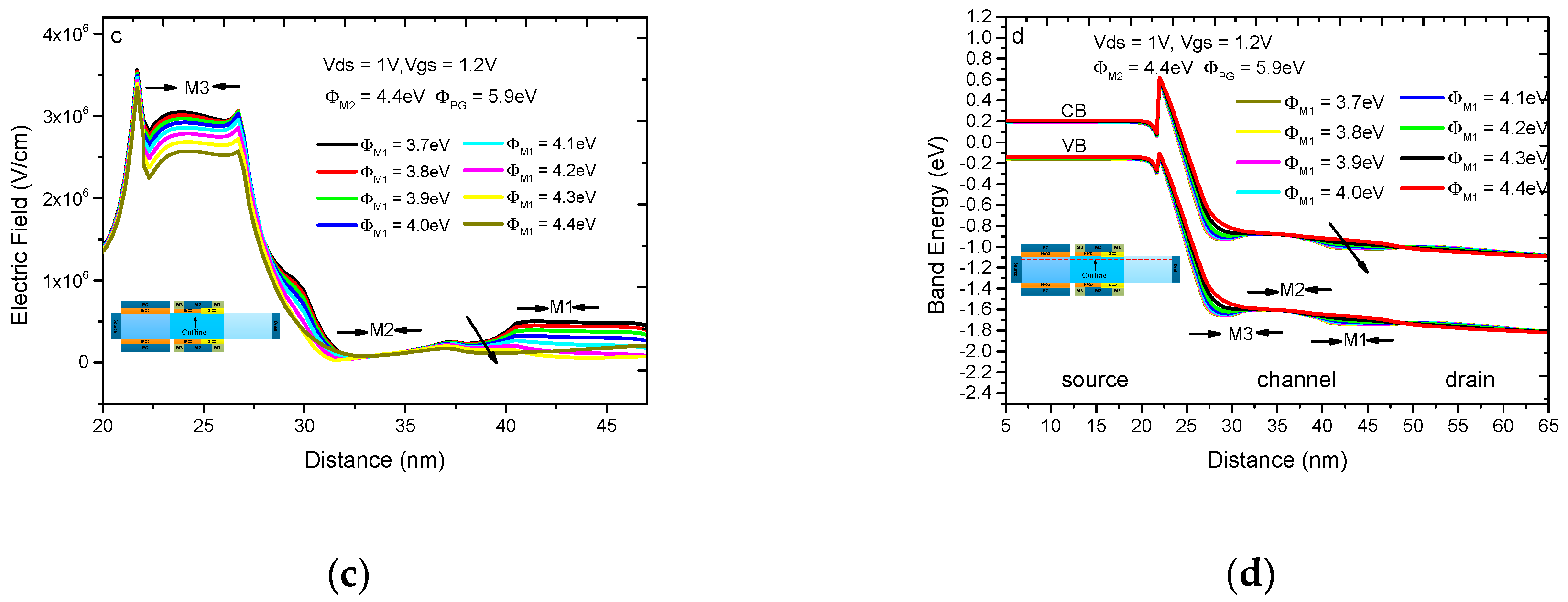

3.1. The Physical Mechanism of dual material gate-engineered heterostructure junctionless tunnel field-effect transistor (DMGE-HJLTFET)

3.2. The Input Characteristics

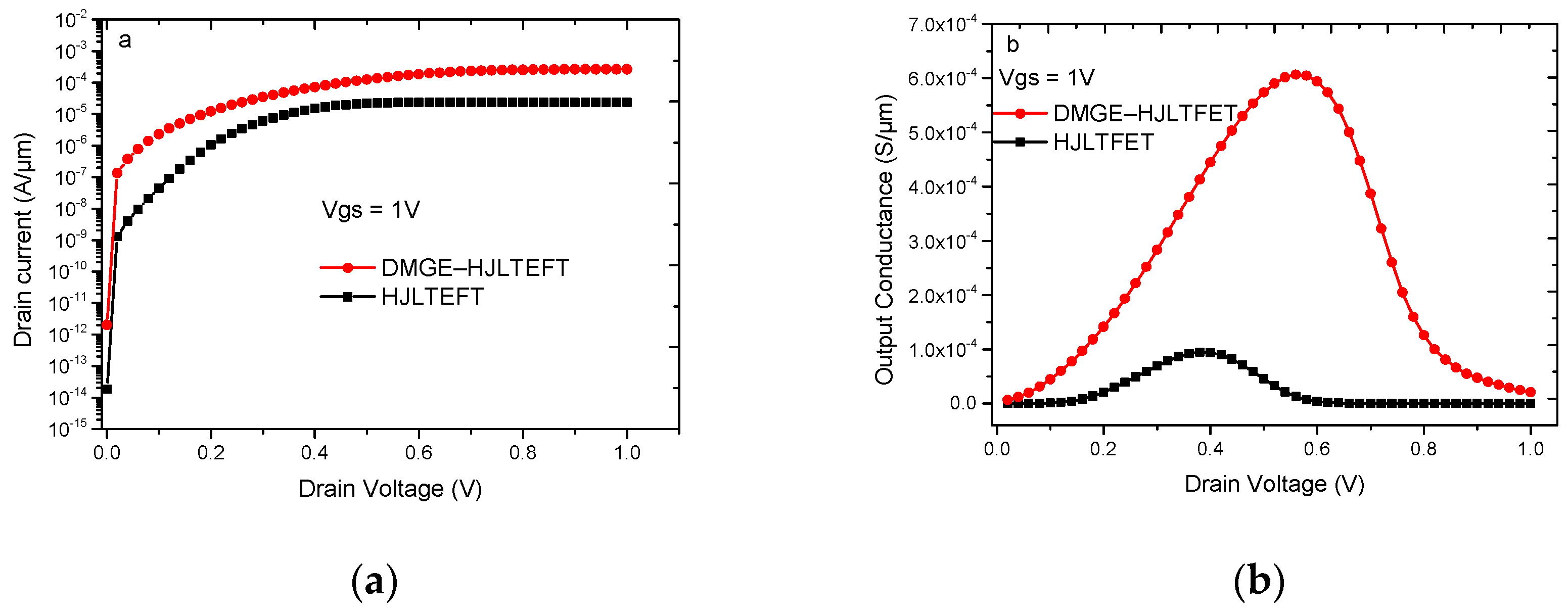

3.3. The Output Characteristics

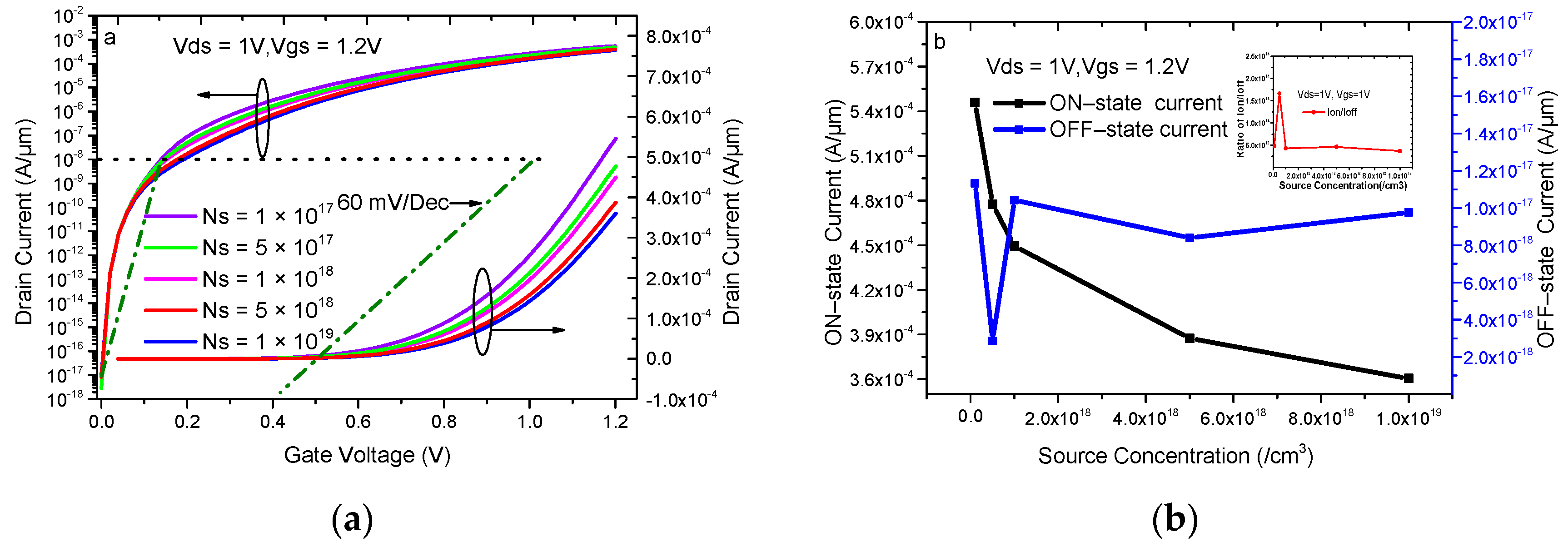

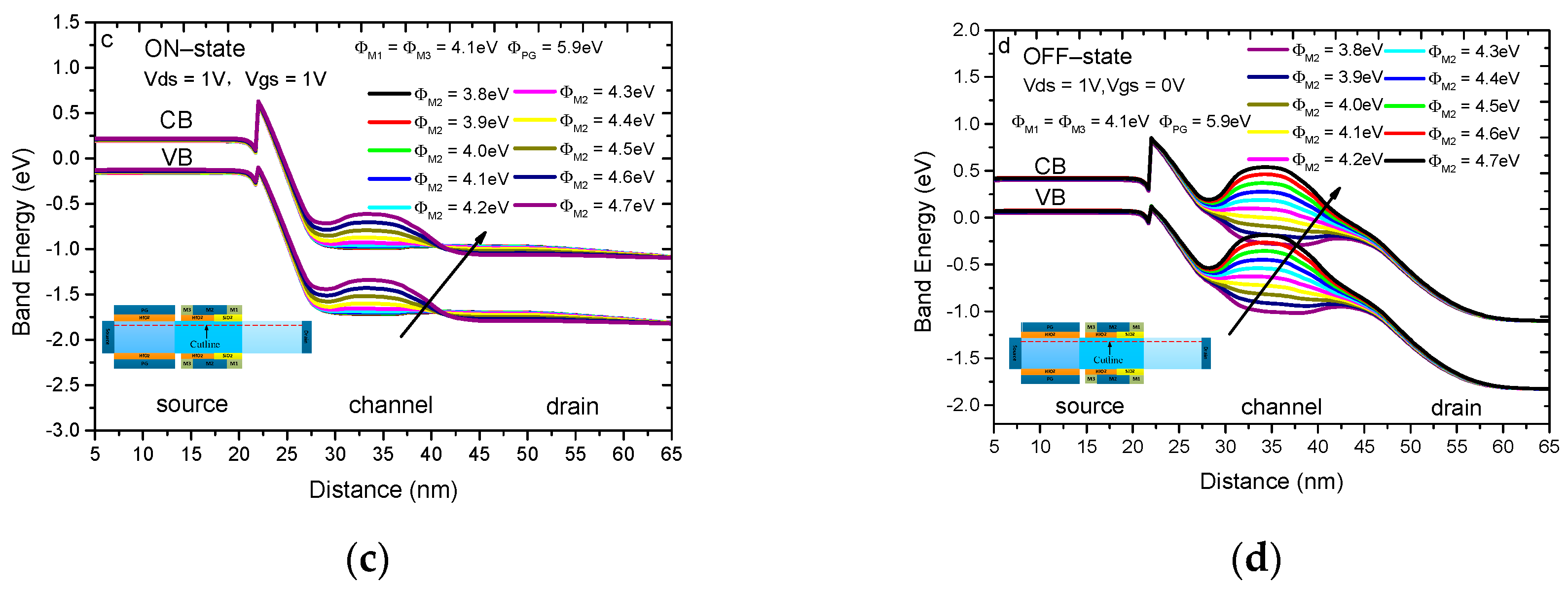

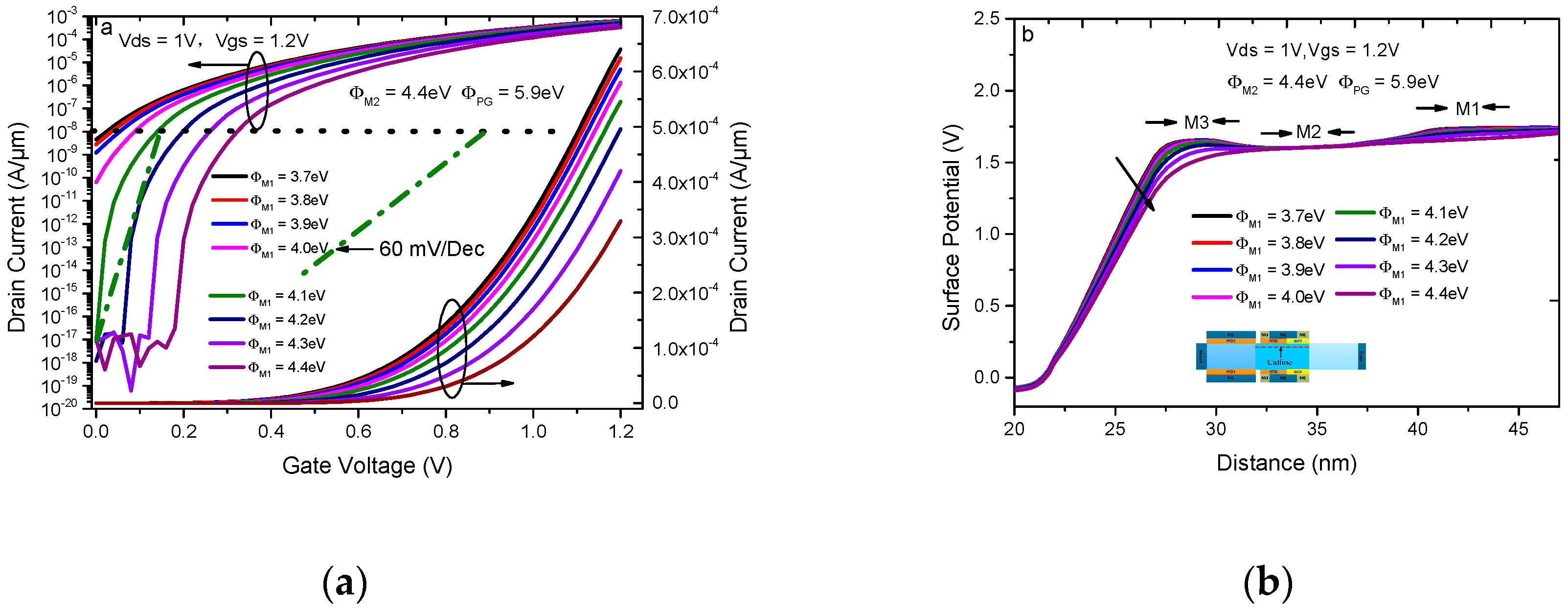

3.4. Effect of Device Parameters on the Transfer Characteristics

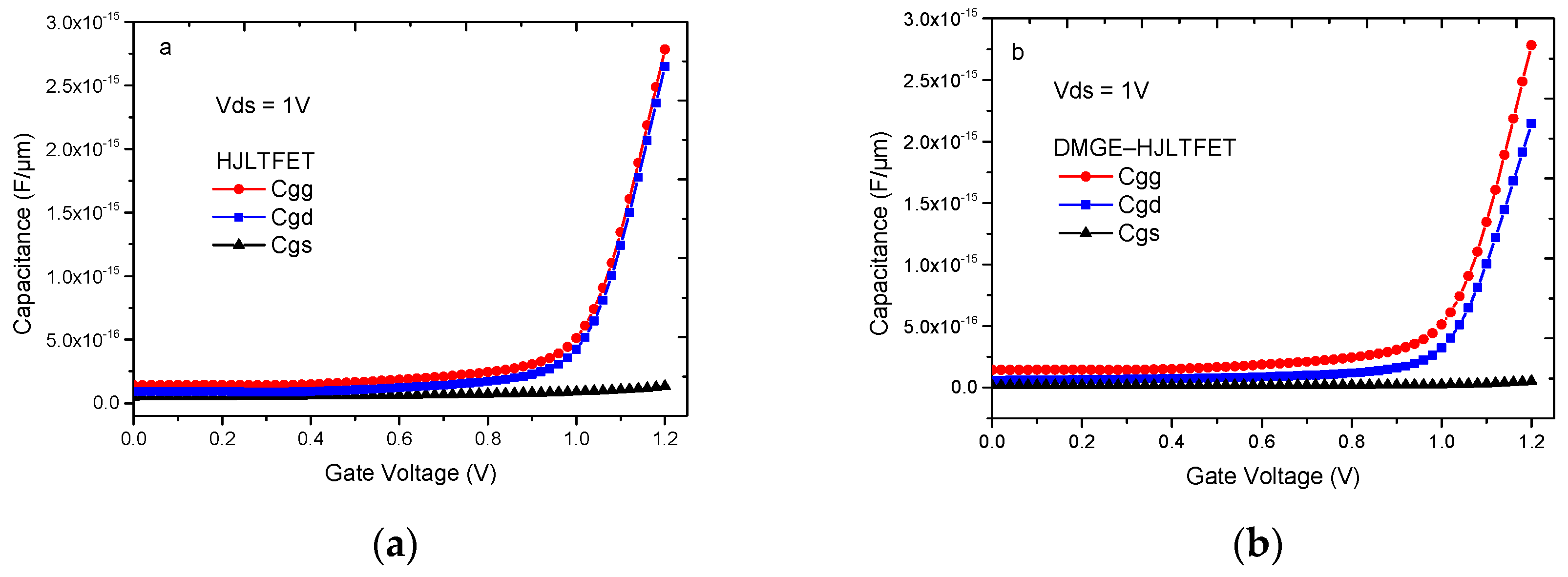

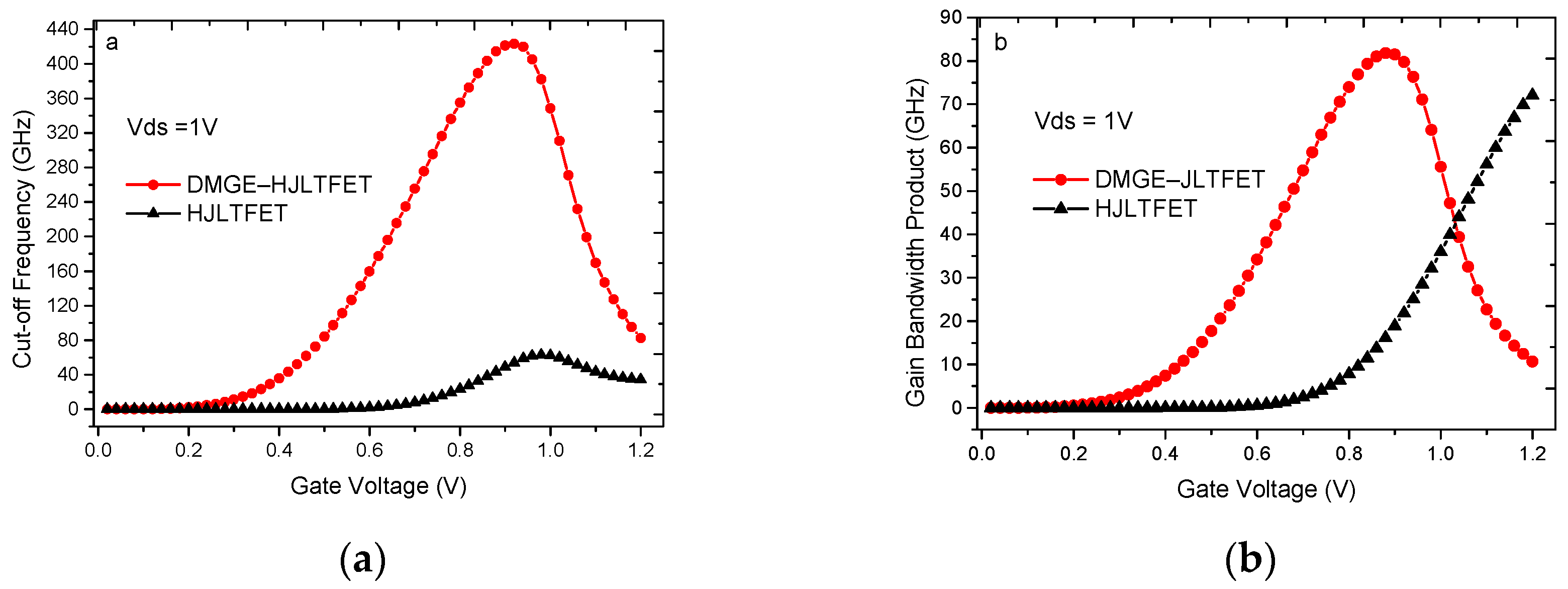

3.5. Comparison in Terms of Analog/RF Performance

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Choi, W.Y.; Park, B.-G.; Lee, J.D.; Liu, T.-J.K. Tunneling Field-Effect Transistors (TFETs) With Subthreshold Swing (SS) Less Than 60 mV/dec. IEEE Electron. Device Lett. 2007, 28, 743–745. [Google Scholar] [CrossRef]

- Anghel, C.; Gupta, A.; Amara, A.; Vladimirescu, A. 30-nm Tunnel FET with Improved Performance and Reduced Ambipolar Current. IEEE Trans. Electron. Devices 2011, 58, 1649–1654. [Google Scholar] [CrossRef]

- Kim, J.H.; Kim, S.; Park, B.-G. Double-Gate TFET with Vertical Channel Sandwiched by Lightly Doped Si. IEEE Trans. Electron. Devices 2019, 66, 1656–1661. [Google Scholar] [CrossRef]

- Shaikh, M.R.U.; Loan, S.A. Drain-Engineered TFET with Fully Suppressed Ambipolarity for High-Frequency Application. IEEE Trans. Electron. Devices 2019, 66, 1628–1634. [Google Scholar] [CrossRef]

- Yang, Z. Tunnel Field-Effect Transistor with an L-Shaped Gate. IEEE Electron. Device Lett. 2016, 37, 1. [Google Scholar] [CrossRef]

- Kim, S.W.; Kim, J.H.; Liu, Ts.K.; Choi, W.Y.; Park, B.-G. Demonstration of L-Shaped Tunnel Field-Effect Transistors. IEEE Trans. Electron. Devices 2016, 63, 1. [Google Scholar] [CrossRef]

- Faraz, N.; Seop, Y.Y. Impact of Quantum Confinement on Band-to-Band Tunneling of Line-Tunneling Type L-Shaped Tunnel Field-Effect Transistor. IEEE Trans. Electron. Devices 2019, 66, 2010–2016. [Google Scholar]

- Kim, J.H.; Kim, S.; Park, B.-G. Symmetric U-Shaped Gate Tunnel Field-Effect Transistor. IEEE Trans. Electron. Devices 2017, 64, 1343–1349. [Google Scholar]

- Wang, W.; Wang, Pe.; Zhang, Ch.; Lin, X.; Liu, Xi.; Sun, Qi.; Zhou, P.; Zhang, D.W. Design of U-Shape Channel Tunnel FETs with SiGe Source Regions. IEEE Trans. Electron. Devices 2014, 61, 193–197. [Google Scholar] [CrossRef]

- Nam, H.; Cho, M.H.; Shin, C. Symmetric tunnel field-effect transistor (S-TFET). Curr. Appl. Phys. 2015, 15, 71–77. [Google Scholar] [CrossRef]

- Lee, H.; Park, S.; Lee, Y.; Nam, H.; Shin, C. Random variation analysis and variation-aware design of symmetric tunnel field-effect transistor. IEEE Trans. Electron. Devices 2015, 62, 1778–1783. [Google Scholar]

- Jiang, Z.; Zhuang, Y.; Li, C.; Wang, P. Dual Sources U-shape Gate Tunnel FETs with High On-current and Steep SS. In Proceedings of the 2016 16th International Workshop on Junction Technology (IWJT), Shanghai, China, 9–10 May 2015; pp. 25–27. [Google Scholar]

- Sola, W.; Sangsig, K. Covered Source–Channel Tunnel Field-Effect Transistors with Trench Gate Structures. IEEE Trans. Nanotechnol. 2018, 18, 114–118. [Google Scholar]

- Li, W.; Liu, H.; Wang, S.; Chen, S.; Yang, Z. Design of High Performance Si/SiGe Heterojunction Tunneling FETs with a T-Shaped Gate. Nanoscale Res. Lett. 2017, 12, 198. [Google Scholar] [CrossRef] [PubMed]

- Szabo, A.; Koester, S.J.; Luisier, M. Ab-Initio Simulation of van der Waals MoTe2–SnS2. Heterotunneling FETs for Low-Power Electronics. IEEE Electron. Device Lett. 2015, 36, 514–516. [Google Scholar] [CrossRef]

- Cao, J.; Logoteta, D.; Özkaya, S.; Biel, B.; Cresti, A.; Pala, M.G.; Esseni, D. Operation and Design of van der Waals Tunnel Transistors: A 3-D Quantum Transport Study. IEEE Trans. Electron. Devices 2016, 63, 4388–4394. [Google Scholar] [CrossRef]

- Raad, B.R.; Tirkey, S.; Sharma, D.; Kondekar, P. A New Design Approach of Dopingless Tunnel FET for Enhancement of Device Characteristics. IEEE Trans. Electron. Devices 2017, 64, 1830–1836. [Google Scholar] [CrossRef]

- Singh, D.; Pandey, S.; Nigam, K.; Sharma, D.; Yadav, D.S.; Kondekar, P. A Charge-Plasma-Based Dielectric-Modulated Junctionless TFET for Biosensor Label-Free Detection. IEEE Trans. Electron. Devices 2017, 64, 271–277. [Google Scholar] [CrossRef]

- Kumar, M.J.; Janardhanan, S. Doping-Less Tunnel Field Effect Transistor: Design and Investigation. IEEE Trans. Electron. Devices 2013, 60, 3285–3290. [Google Scholar] [CrossRef]

- Aslam, M.; Sharma, D.; Yadav, S.; Soni, D.; Sharma, N.; Gedam, A. A comparative investigation of low work-function metal implantation in the oxide region for improving electrostatic characteristics of charge plasma TFET. Micro Nano Lett. 2019, 14, 123–128. [Google Scholar] [CrossRef]

- Ameen, T.A.; Ilatikhameneh, H.; Fay, P.; Seabaugh, A.; Rahman, R.; Klimeck, G. Alloy Engineered Nitride Tunneling Field Effect Transistor: A Solution for the Challenge of Heterojunction TFETs. IEEE Trans. Electron. Devices 2019, 66, 736–742. [Google Scholar] [CrossRef]

- Hoda, T.S.; Saleh, G.S.; Yousefi, R.; Aderang, H. A computational study of a carbon nanotube junctionless tunneling field-effect transistor (CNT-JLTFET) based on the charge plasma concept. Superlattices Microstruct. 2019, 125, 168–176. [Google Scholar]

- Ghosh, B.; Bal, P.; Mondal, P. A junctionless tunnel field effect transistor with low subthreshold slope. J. Comput. Electron. 2013, 12, 428–436. [Google Scholar] [CrossRef]

- Aghandeh, H.; Ziabari, S.A.S. Gate engineered heterostructure junctionless TFET with Gaussian doping profile for ambipolar suppression and electrical performance improvement. Superlattices Microstruct. 2017, 111, 103–134. [Google Scholar] [CrossRef]

- Abadi, R.M.I.; Ziabari, S.A.S. Improved performance of nanoscale junctionless tunnel field-effect transistor based on gate engineering approach. Appl. Phys. A 2016, 122, 988. [Google Scholar] [CrossRef]

- Rahimian, M.; Fathipour, M. Improvement of electrical performance in junctionless nanowire TFET using hetero-gate-dielectric. Mater. Sci. Semicond. Process. 2017, 63, 142–152. [Google Scholar] [CrossRef]

- Tirkey, S.; Nigam, K.; Pandey, S.; Sharma, D.; Kondekar, P. Investigation of gate material engineering in junctionless TFET to overcome the trade-off between ambipolarity and RF/linearity metrics. Superlattices Microstruct. 2017, 109, 307–315. [Google Scholar]

- Basak, S.; Asthana, P.K.; Goswami, Y. Leakage current reduction in junctionless tunnel FET using a lightly. doped source. Appl. Phys. 2015, 118, 1527–1533. [Google Scholar] [CrossRef]

- Bal, P.; Akram, M.W.; Mondal, P.; Ghosh, B. Performance estimation of sub-30 nm junctionless tunnel FET (JLTFET). J. Comput. Electron. 2013, 12, 782–789. [Google Scholar] [CrossRef]

- Lee, J.C.; Ahn, T.J.; Yu, Y.S. Si/Ge Hetero Tunnel Field-Effect Transistor with Junctionless Channel Based on Nanowire. J. Nanosci. Nanotechnol. 2019, 19, 6750–6754. [Google Scholar] [CrossRef]

- Leung, G.; Chui, C.O. Variability Impact of Random Dopant Fluctuation on Nanoscale Junctionless FinFETs. IEEE Electron. Device Lett. 2012, 33, 767–769. [Google Scholar] [CrossRef]

- Ahangari, Z. Design and analysis of energy efficient semi-junctionless n+n+p heterojunction p-channel tunnel field effect transistor. Mater. Res. Express 2019, 6, 6750–6754. [Google Scholar] [CrossRef]

- Vanlalawmpuia, K.; Rajesh, S.; Brinda, B. Performance evaluation of hetero-stacked TFET for variation in lateral straggle and its application as digital inverter. Appl. Phys. A Mater. Sci. Process. 2018, 124, 1–8. [Google Scholar] [CrossRef]

- Biswas, A.; Luong, G.V.; Chowdhury, M.F.; Alper, C.; Zhao, Qi.; Udrea, F. Benchmarking of Homojunction Strained-Si NW Tunnel FETs for Basic Analog Functions. IEEE Trans. Electron. Devices 2017, 64, 1441–1448. [Google Scholar] [CrossRef]

- Chakraborty, A.; Sarkar, A. Investigation of analog/RF performance of staggered heterojunctions based nanowire tunneling field-effect transistors. Superlattices Microstruct. 2015, 80, 125–135. [Google Scholar] [CrossRef]

- Biswal, S.M.; Baral, B.; De, D.; Sarkar, A. Simulation and comparative study on analog/RF and linearity performance of III–V semiconductor-based staggered heterojunction and InAs nanowire(nw) Tunnel FET. Superlattices Microstruct. 2019, 25, 1855–1861. [Google Scholar] [CrossRef]

- Kr, M.S.; Brinda, B. Impact of interface traps on performance of Gate-on-Source/Channel SOI TFET. Microelectron. Reliab. 2019, 94, 1–12. [Google Scholar]

- Sarkar, A.; Sarkar, C.K. RF and analogue performance investigation of DG tunnel FET. Electron. Lett. 2010, 1, 210–217. [Google Scholar] [CrossRef]

- Chen, S.; Liu, H.; Wang, S.; Li, W.; Wang, X.; Zhao, L. Analog/RF Performance of T-Shape Gate Dual-Source Tunnel Field-Effect Transistor. Nanoscale Res. Lett. 2018, 13, 321. [Google Scholar] [CrossRef]

- Narwal, S.; Chauhan, S.S. Investigation of RF and linearity performance of electrode work-function engineered HDB vertical TFET. Micro Nano Lett. 2019, 14, 17–21. [Google Scholar] [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xie, H.; Liu, H.; Chen, S.; Han, T.; Wang, S. Design and Investigation of a Dual Material Gate Arsenic Alloy Heterostructure Junctionless TFET with a Lightly Doped Source. Appl. Sci. 2019, 9, 4104. https://doi.org/10.3390/app9194104

Xie H, Liu H, Chen S, Han T, Wang S. Design and Investigation of a Dual Material Gate Arsenic Alloy Heterostructure Junctionless TFET with a Lightly Doped Source. Applied Sciences. 2019; 9(19):4104. https://doi.org/10.3390/app9194104

Chicago/Turabian StyleXie, Haiwu, Hongxia Liu, Shupeng Chen, Tao Han, and Shulong Wang. 2019. "Design and Investigation of a Dual Material Gate Arsenic Alloy Heterostructure Junctionless TFET with a Lightly Doped Source" Applied Sciences 9, no. 19: 4104. https://doi.org/10.3390/app9194104

APA StyleXie, H., Liu, H., Chen, S., Han, T., & Wang, S. (2019). Design and Investigation of a Dual Material Gate Arsenic Alloy Heterostructure Junctionless TFET with a Lightly Doped Source. Applied Sciences, 9(19), 4104. https://doi.org/10.3390/app9194104