Influence of Substrate Modification with Dipole Monolayers on the Electrical Characteristics of Short-Channel Polymer Field-Effect Transistors

Abstract

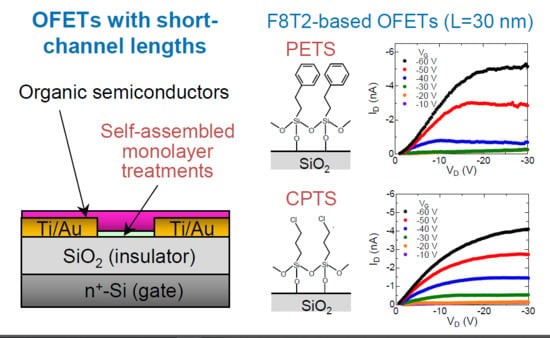

1. Introduction

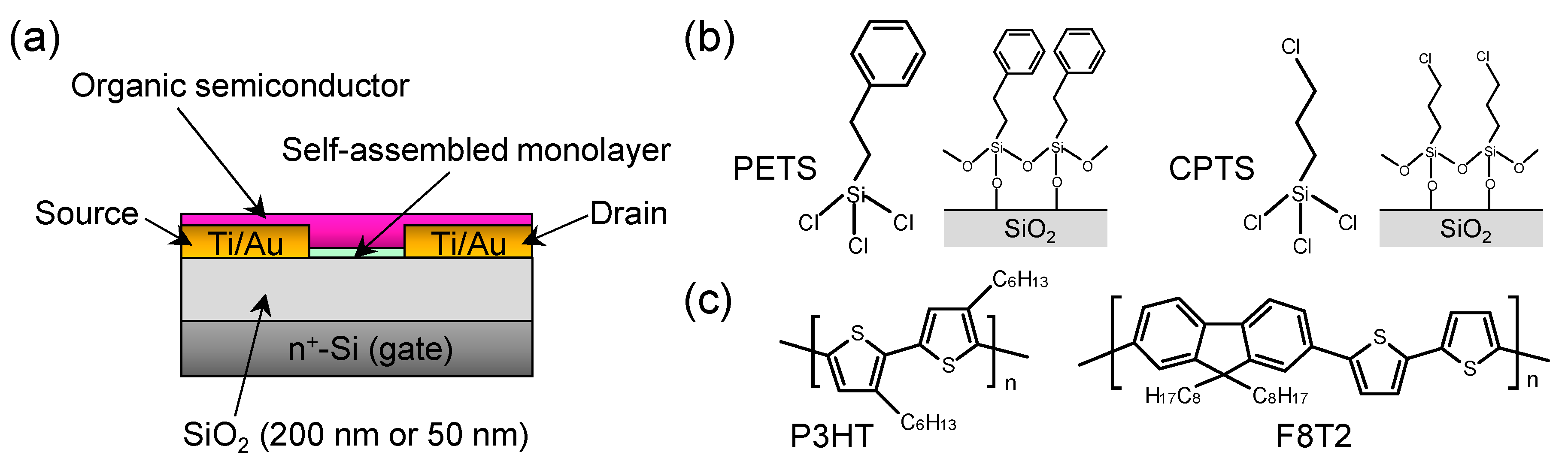

2. Experimental

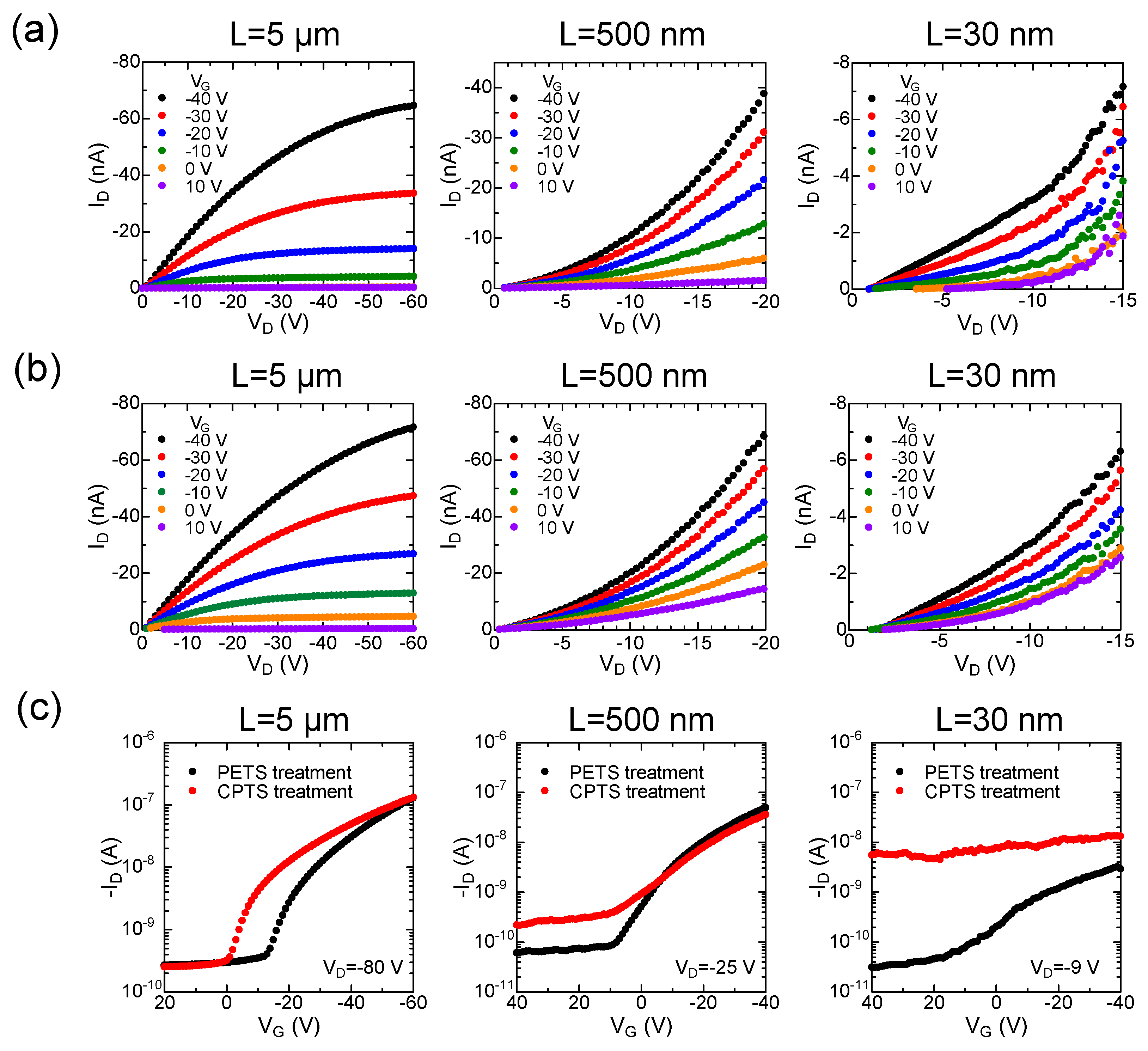

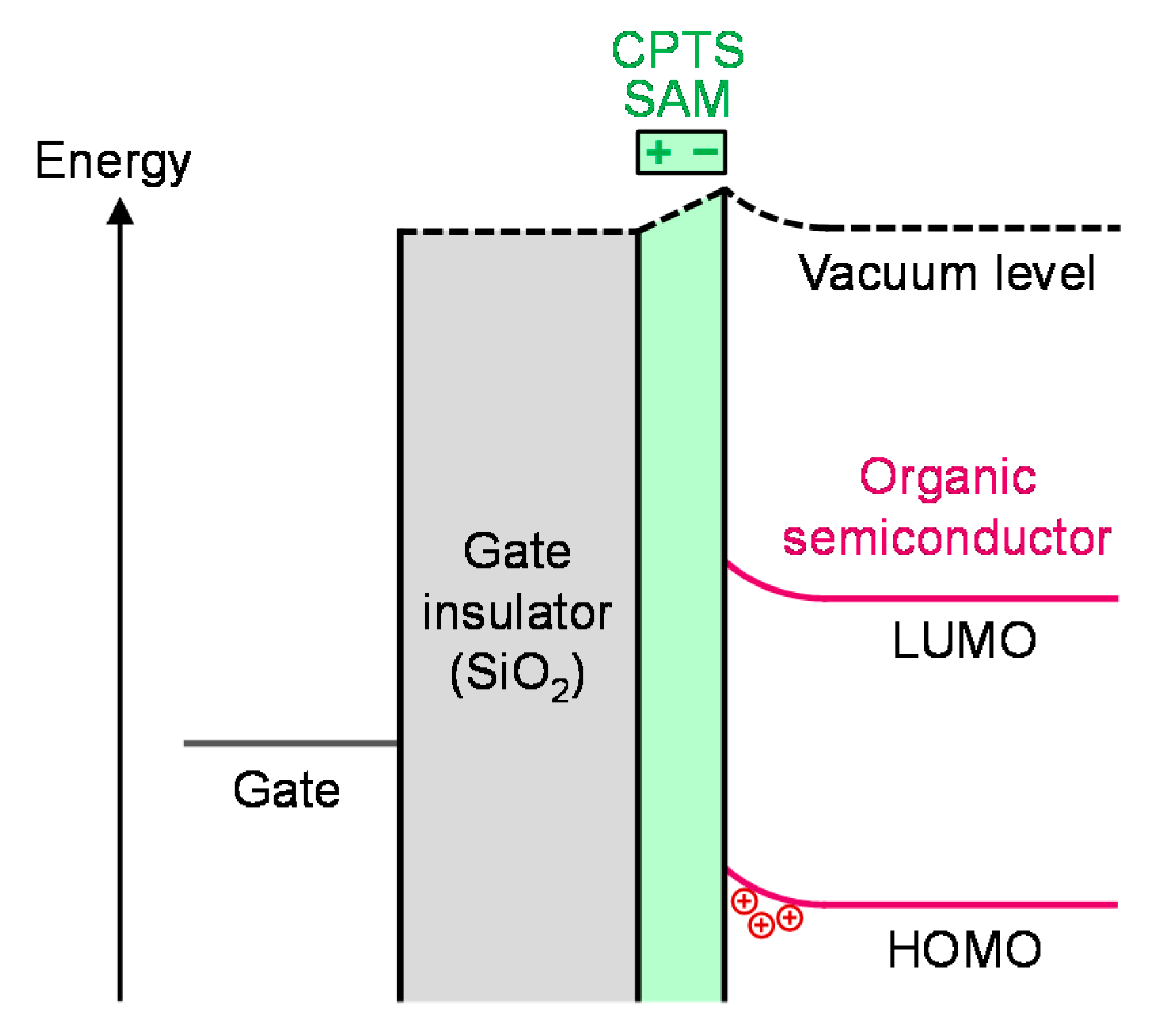

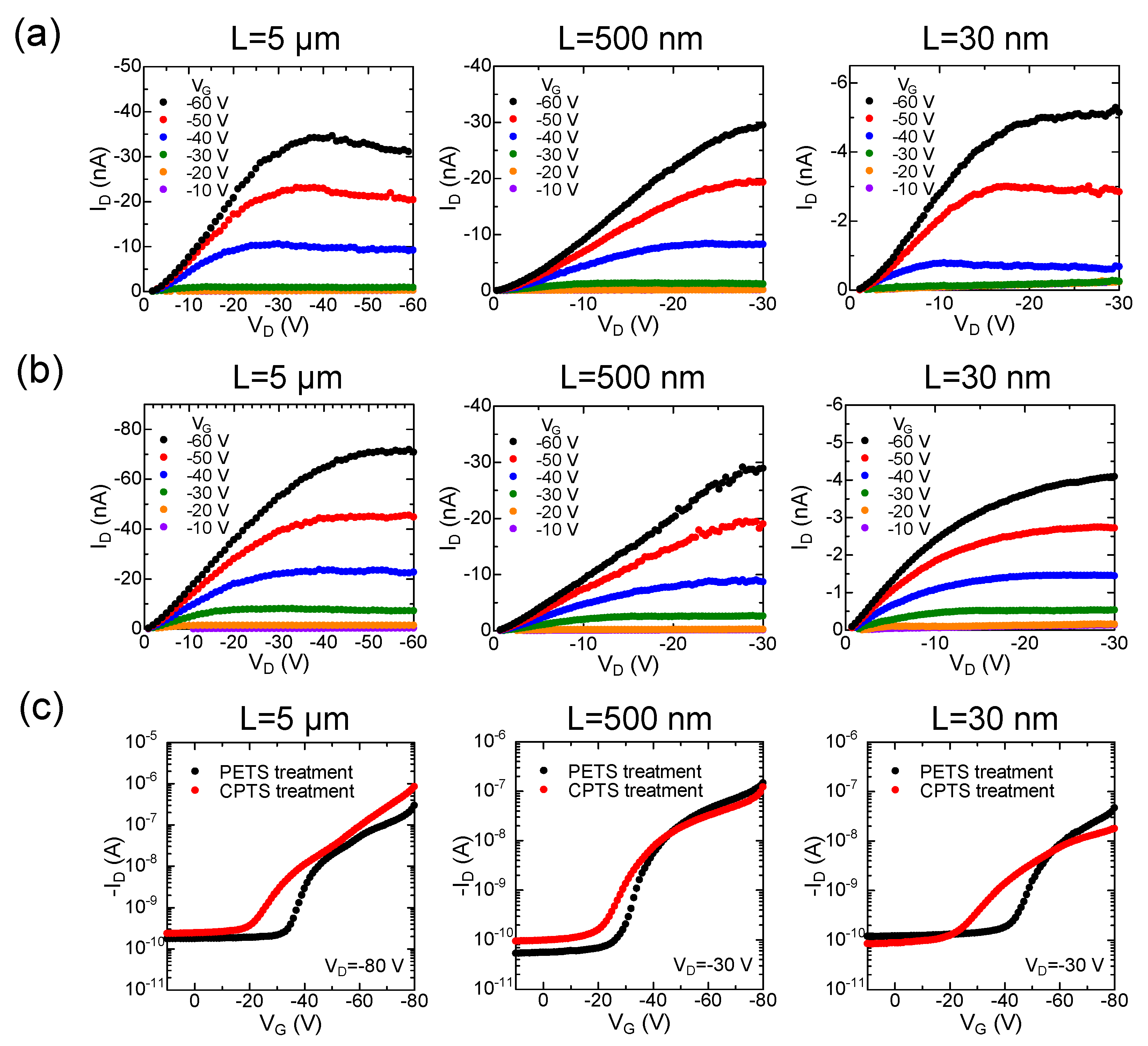

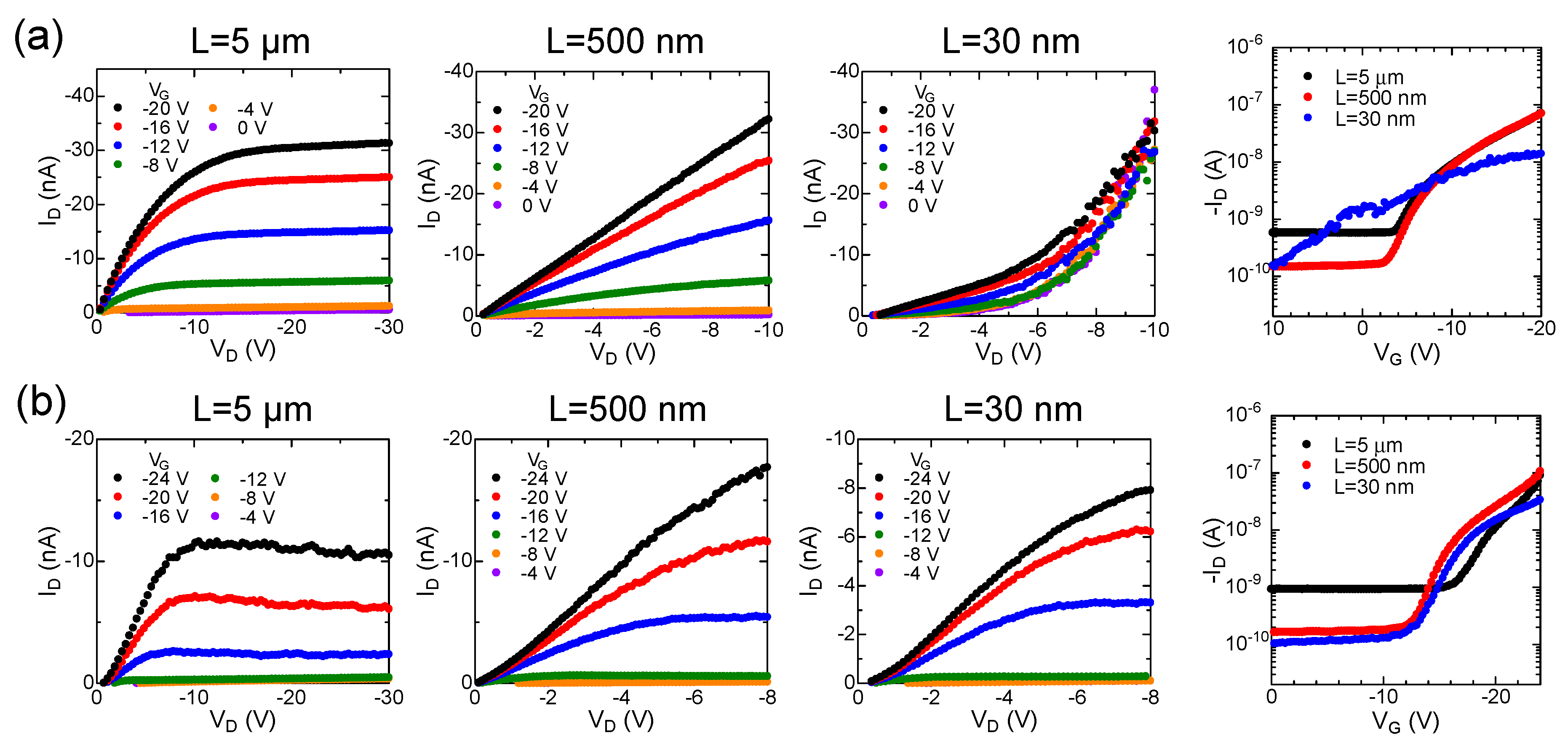

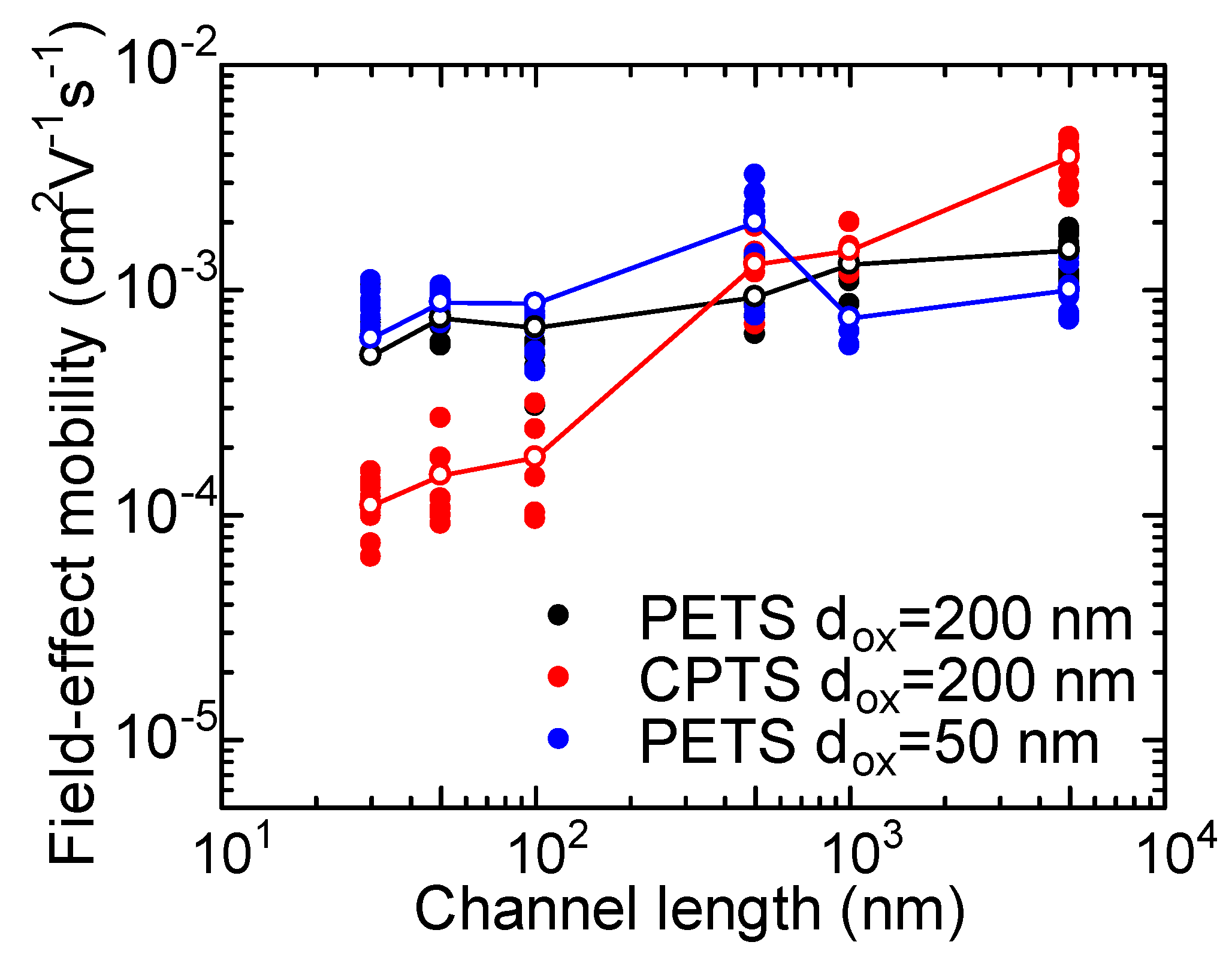

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Sirringhaus, H. Organic field-effect transistors: The path beyond amorphous silicon. Adv. Mater. 2014, 26, 1319–1335. [Google Scholar] [CrossRef] [PubMed]

- Klauk, H. Organic thin-film transistors. Chem. Soc. Rev. 2010, 39, 2643–2666. [Google Scholar] [CrossRef] [PubMed]

- Sekitani, T.; Someya, T. Stretchable, large-area organic electronics. Adv. Mater. 2010, 22, 2228–2246. [Google Scholar] [CrossRef] [PubMed]

- Zaumseil, J.; Sirringhaus, H. Electron and ambipolar transport in organic field-effect transistors. Chem. Rev. 2007, 107, 1296–1323. [Google Scholar] [CrossRef] [PubMed]

- Collet, J.; Tharaud, O.; Chapoton, A.; Vuillaume, D. Low-voltage, 30 nm channel length, organic transistors with a self-assembled monolayer as gate insulating films. Appl. Phys. Lett. 2010, 76, 1941–1943. [Google Scholar] [CrossRef]

- Austin, M.D.; Chou, S.Y. Fabrication of 70 nm channel length polymer organic thin-film transistors using nanoimprint lithography. Appl. Phys. Lett. 2002, 81, 4431–4433. [Google Scholar] [CrossRef]

- Wang, L.; Fine, D.; Dodabalapur, A. Nanoscale chemical sensor based on organic thin-film transistors. Appl. Phys. Lett. 2004, 85, 6386–6388. [Google Scholar] [CrossRef]

- Fujimori, F.; Shigeto, K.; Hamano, T.; Minari, T.; Miyadera, T.; Tsukagoshi, K.; Aoyagi, Y. Current transport in short channel top-contact pentacene field-effect transistors investigated with the selective molecular doping technique. Appl. Phys. Lett. 2007, 90, 193507. [Google Scholar] [CrossRef]

- Tsukagoshi, K.; Fujimori, F.; Minari, T.; Miyadera, T.; Hamano, T.; Aoyagi, Y. Suppression of short channel effect in organic thin film transistors. Appl. Phys. Lett. 2007, 91, 113508. [Google Scholar] [CrossRef]

- Sze, S.M.; Ng, K.K. Physics of Semiconductor Devices, 3rd ed.; John Wiley & Sons, Inc.: New York, NY, USA, 2007; ISBN 978-0-471-14323-9. [Google Scholar]

- Hirose, T.; Nagase, T.; Kobayashi, T.; Ueda, R.; Otomo, A.; Naito, H. Device characteristics of short-channel polymer field-effect transistors. Appl. Phys. Lett. 2010, 97, 083301. [Google Scholar] [CrossRef]

- Horowitz, G.; Hajlaoui, R.; Bouchriha, H.; Bourguiga, R.; Hajlaoui, M. The concept of “threshold voltage” in organic field-effect transistors. Adv. Mater. 1998, 10, 923–927. [Google Scholar] [CrossRef]

- Suemori, K.; Uemura, S.; Yoshida, M.; Hoshino, S.; Kodzasa, T.; Kamata, T. Reduction of threshold voltage fluctuation for organic field effect transistors by increase of insulator capacitance. Thin Solid Films 2008, 516, 2739–2742. [Google Scholar] [CrossRef]

- Kobayashi, S.; Nishikawa, T.; Takenobu, T.; Mori, S.; Shimoda, T.; Mitani, T.; Shimotani, H.; Yoshimoto, N.; Ogawa, S.; Iwasa, Y. Control of carrier density by self-assembled monolayers in organic field-effect transistors. Nat. Mater. 2004, 3, 317–322. [Google Scholar] [CrossRef] [PubMed]

- Pernstich, K.P.; Goldmann, C.; Krellner, C.; Oberhoff, D.; Gundlach, D.J.; Batlogg, B. Shifted transfer characteristics of organic thin film and single crystal FETs. Synth. Met. 2004, 146, 325–328. [Google Scholar] [CrossRef]

- Pernstich, K.P.; Haas, S.; Oberhoff, D.; Goldmann, C.; Gundlach, D.J.; Batlogg, B.; Rashid, A.N.; Schitteret, G. Threshold voltage shift in organic field effect transistors by dipole monolayers on the gate insulator. J. Appl. Phys. 2004, 96, 6431–6438. [Google Scholar] [CrossRef]

- Takeya, J.; Nishikawa, T.; Takenobu, T.; Kobayashi, S.; Iwasa, Y.; Mitani, T.; Goldmann, C.; Krellner, C.; Batlogg, B. Effects of polarized organosilane self-assembled monolayers on organic single-crystal field-effect transistors. Appl. Phys. Lett. 2004, 85, 5078–5080. [Google Scholar] [CrossRef]

- Jang, Y.; Cho, J.H.; Kim, D.H.; Park, Y.D.; Hwang, M.; Cho, K. Effects of the permanent dipoles of self-assembled monolayer-treated insulator surfaces on the field-effect mobility of a pentacene thin-film transistor. Appl. Phys. Lett. 2007, 90, 132104. [Google Scholar] [CrossRef]

- Vasudevan, S.; Kapur, N.; He, T.; Neurock, M.; Tour, J.M.; Ghosh, A.W. Controlling transistor threshold voltages using molecular dipoles. J. Appl. Phys. 2009, 105, 093703. [Google Scholar] [CrossRef]

- Celle, C.; Suspène, C.; Ternisien, M.; Lenfant, S.; Guérin, D.; Smaali, K.; Lmimouni, K.; Simonato, J.P.; Vuillaume, D. Interface dipole: Effects on threshold voltage and mobility for both amorphous and poly-crystalline organic field effect transistors. Org. Electron. 2014, 15, 729–737. [Google Scholar] [CrossRef]

- Nomoto, K.; Hirai, N.; Yoneya, N.; Kawashima, N.; Noda, M.; Wada, M.; Kasahara, J. A high-performance short-channel bottom-contact OTFT and its application to AM-TN-LCD. IEEE Trans. Electron. Dev. 2005, 52, 1519–1526. [Google Scholar] [CrossRef]

- Jee, S.H.; Kim, S.H.; Ko, J.H.; Yoon, Y.S. Study on work function change of ITO modified by using a self-assembled monolayer for organic based devices. J. Korean Phys. Soc. 2006, 49, 2034–2039. [Google Scholar]

- Jiang, J.; Lima, O.V.; Pei, Y.; Zeng, X.C.; Tan, L.; Forsythe, E. Dipole-induced, thermally stable lamellar structure by polar aromatic silane. J. Am. Chem. Soc. 2009, 131, 900–901. [Google Scholar] [CrossRef] [PubMed]

- Yun, D.-J.; Rhee, S.-W. Self-assembled monolayer formation on molybdenum with octadecyltrichlorosilane and phenethyltrichlorosilane and measurement of molybdenum–pentacene interface properties. J. Electrochem. Soc. 2008, 155, H357–H362. [Google Scholar] [CrossRef]

- Chua, L.-L.; Zaumseil, J.; Chang, J.-F.; Ou, E.C.-W.; Ho, P.K.-H.; Sirringhaus, H.; Friend, R.H. General observation of n-type field-effect behaviour in organic semiconductors. Nature 2005, 434, 194–199. [Google Scholar] [CrossRef] [PubMed]

- Torres, I.; Taylor, D.M. Interface states in polymer metal-insulator-semiconductor devices. J. Appl. Phys. 2005, 98, 073710. [Google Scholar] [CrossRef]

- Mattis, B.A.; Chang, P.C.; Subramanian, V. Performance recovery and optimization of poly(3-hexylthiophene) transistors by thermal cycling. Synth. Met. 2006, 156, 1241–1248. [Google Scholar] [CrossRef]

- Chabinyc, M.L.; Lu, J.-P.; Street, R.A.; Wu, Y.; Liu, P.; Ong, B.S. Short channel effects in regioregular poly(thiophene) thin film transistors. J. Appl. Phys. 2004, 96, 2063–2070. [Google Scholar] [CrossRef]

- Bürgi, L.; Richards, T.J.; Friend, R.H.; Sirringhaus, H. Close look at charge carrier injection in polymer field-effect transistors. J. Appl. Phys. 2003, 94, 6129–6137. [Google Scholar] [CrossRef]

- Veres, J.; Ogier, S.; Lloyd, G. Gate insulators in organic field-effect transistors. Chem. Mater. 2004, 16, 4543–4555. [Google Scholar] [CrossRef]

- Horii, Y.; Ikawa, M.; Sakaguchi, K.; Chikamatsu, M.; Yoshida, Y.; Azumi, R.; Mogi, H.; Kitagawa, M.; Konishi, H.; Yase, K. Investigation of self-assembled monolayer treatment on SiO2 gate insulator of poly(3-hexylthiophene) thin-film transistors. Thin Solid Films 2009, 518, 642–646. [Google Scholar] [CrossRef]

- Campbell, I.H.; Rubin, S.; Zawodzinski, T.A.; Kress, J.D.; Martin, R.L.; Smith, D.L.; Barashkov, N.N.; Ferraris, J.P. Controlling Schottky energy barriers in organic electronic devices using self-assembled monolayers. Phys. Rev. B 1996, 54, R14321. [Google Scholar] [CrossRef]

- Sugimura, H.; Hayashi, K.; Saito, N.; Nakagiri, N.; Takai, O. Surface potential microscopy for organized molecular systems. Appl. Surf. Sci. 2002, 188, 403–410. [Google Scholar] [CrossRef]

- Zaumseil, J.; Baldwin, K.W.; Rogers, J.A. Contact resistance in organic transistors that use source and drain electrodes formed by soft contact lamination. J. Appl. Phys. 2003, 93, 6117–6124. [Google Scholar] [CrossRef]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nagase, T.; Hirose, T.; Kobayashi, T.; Ueda, R.; Otomo, A.; Naito, H. Influence of Substrate Modification with Dipole Monolayers on the Electrical Characteristics of Short-Channel Polymer Field-Effect Transistors. Appl. Sci. 2018, 8, 1274. https://doi.org/10.3390/app8081274

Nagase T, Hirose T, Kobayashi T, Ueda R, Otomo A, Naito H. Influence of Substrate Modification with Dipole Monolayers on the Electrical Characteristics of Short-Channel Polymer Field-Effect Transistors. Applied Sciences. 2018; 8(8):1274. https://doi.org/10.3390/app8081274

Chicago/Turabian StyleNagase, Takashi, Takeshi Hirose, Takashi Kobayashi, Rieko Ueda, Akira Otomo, and Hiroyoshi Naito. 2018. "Influence of Substrate Modification with Dipole Monolayers on the Electrical Characteristics of Short-Channel Polymer Field-Effect Transistors" Applied Sciences 8, no. 8: 1274. https://doi.org/10.3390/app8081274

APA StyleNagase, T., Hirose, T., Kobayashi, T., Ueda, R., Otomo, A., & Naito, H. (2018). Influence of Substrate Modification with Dipole Monolayers on the Electrical Characteristics of Short-Channel Polymer Field-Effect Transistors. Applied Sciences, 8(8), 1274. https://doi.org/10.3390/app8081274