An Enhancing Fault Current Limitation Hybrid Droop/V-f Control for Grid-Tied Four-Wire Inverters in AC Microgrids

Abstract

1. Introduction

2. System Definition

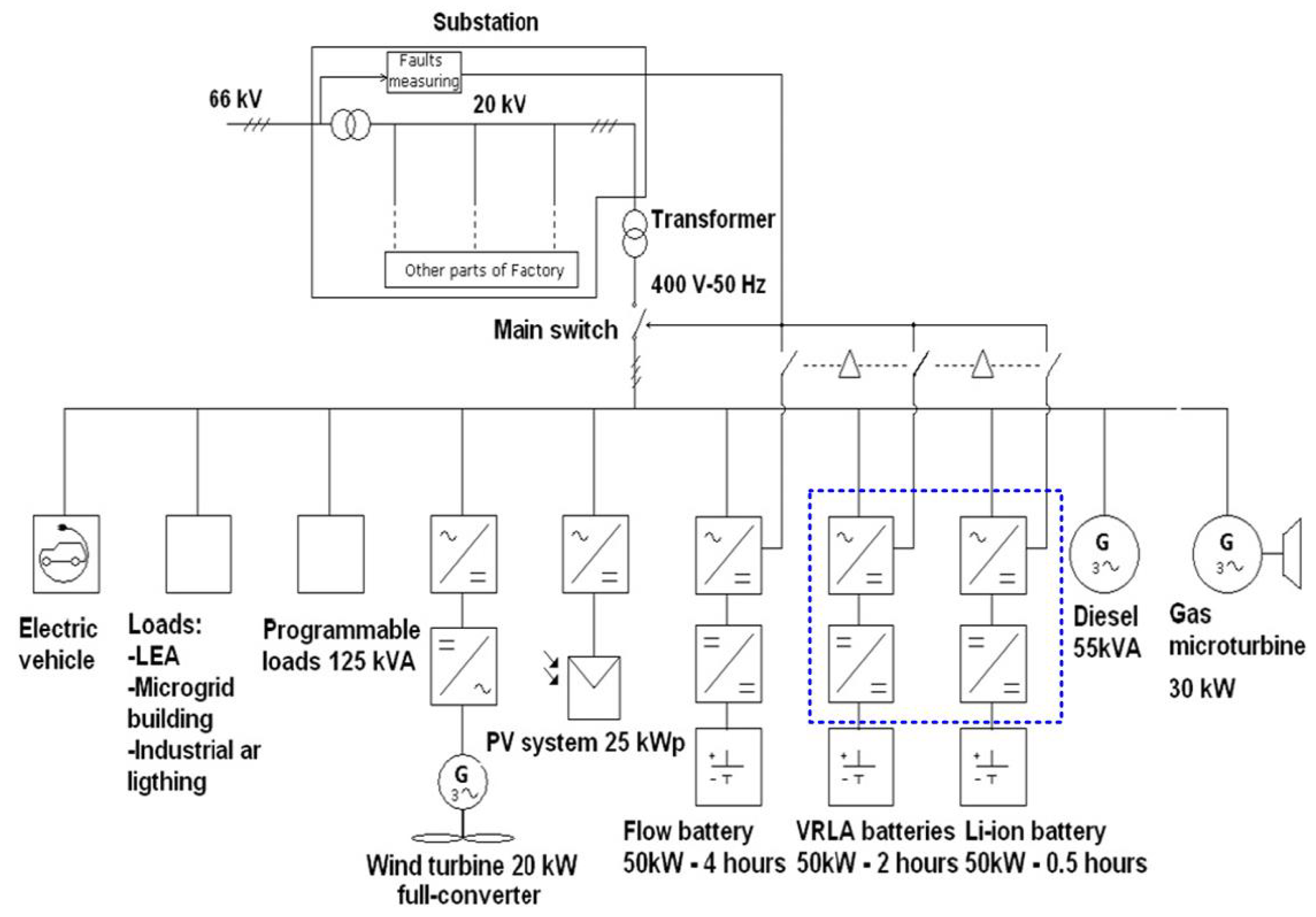

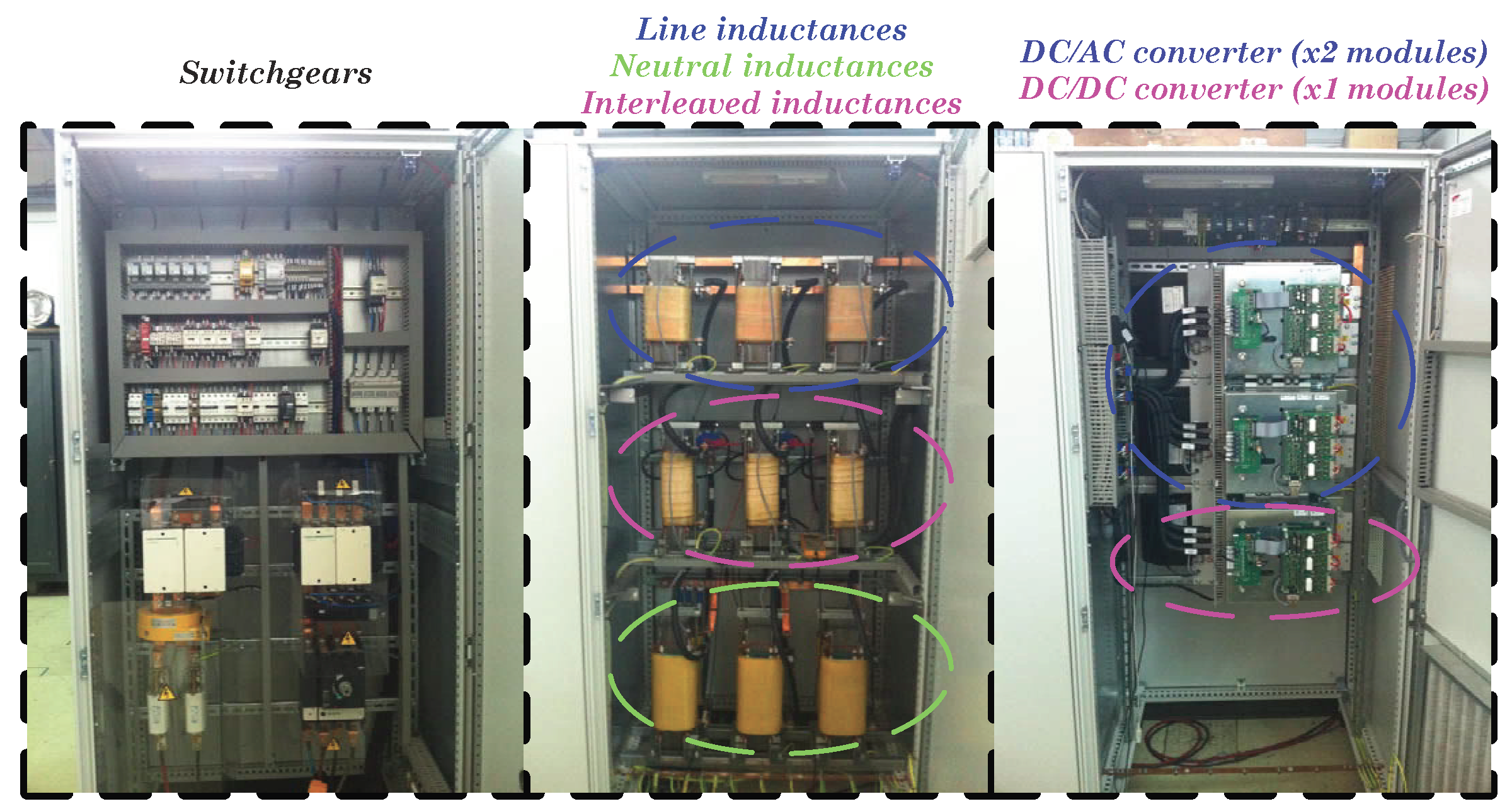

2.1. The Experimental ATENEA Microgrid

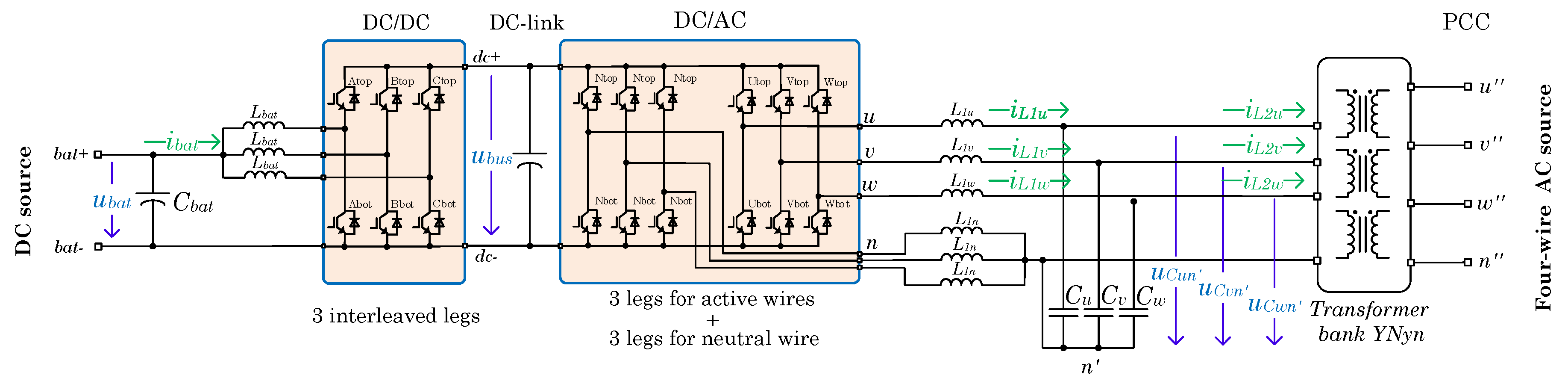

2.2. The Converter

3. Control Strategies

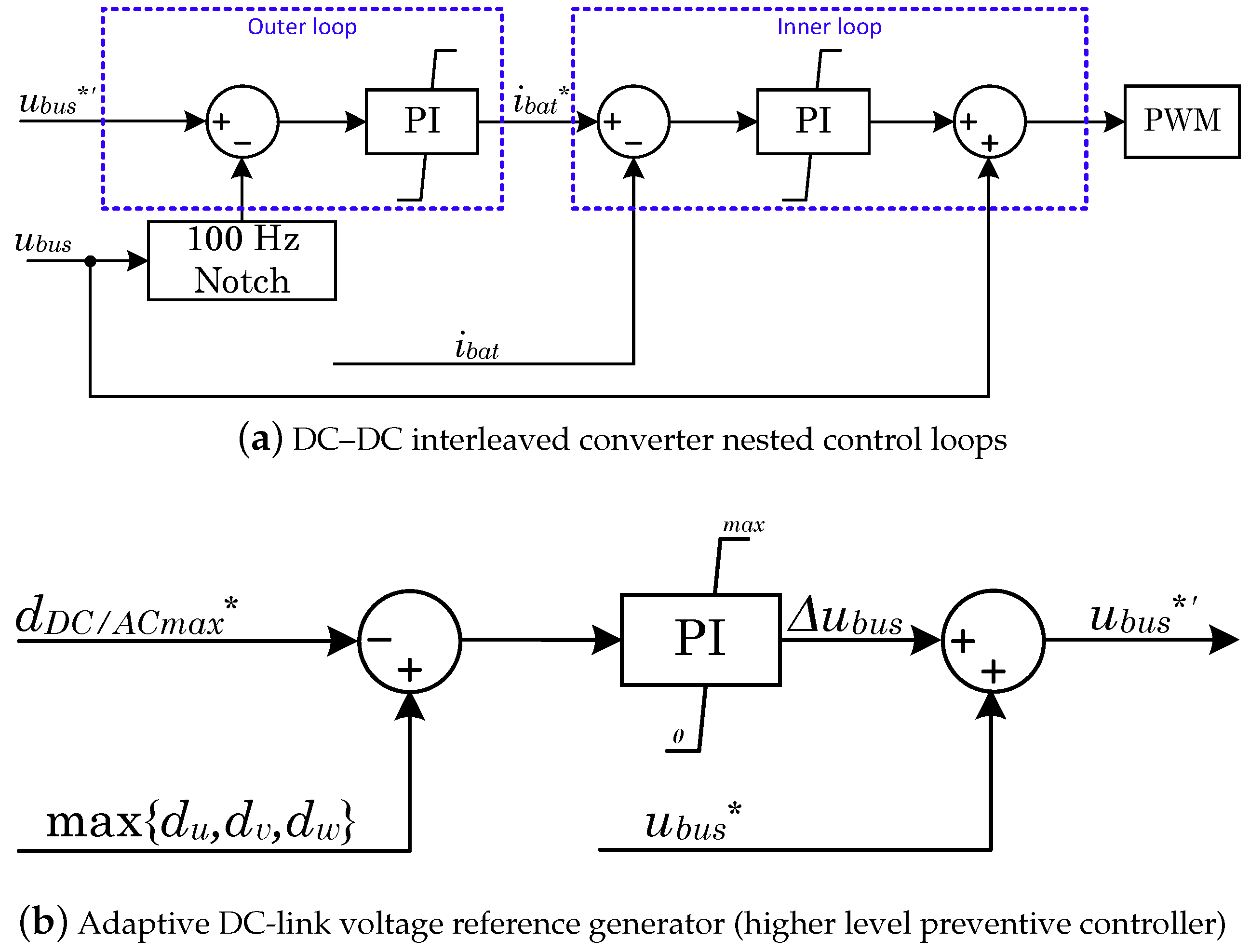

3.1. DC–DC Interleaved Converter Control

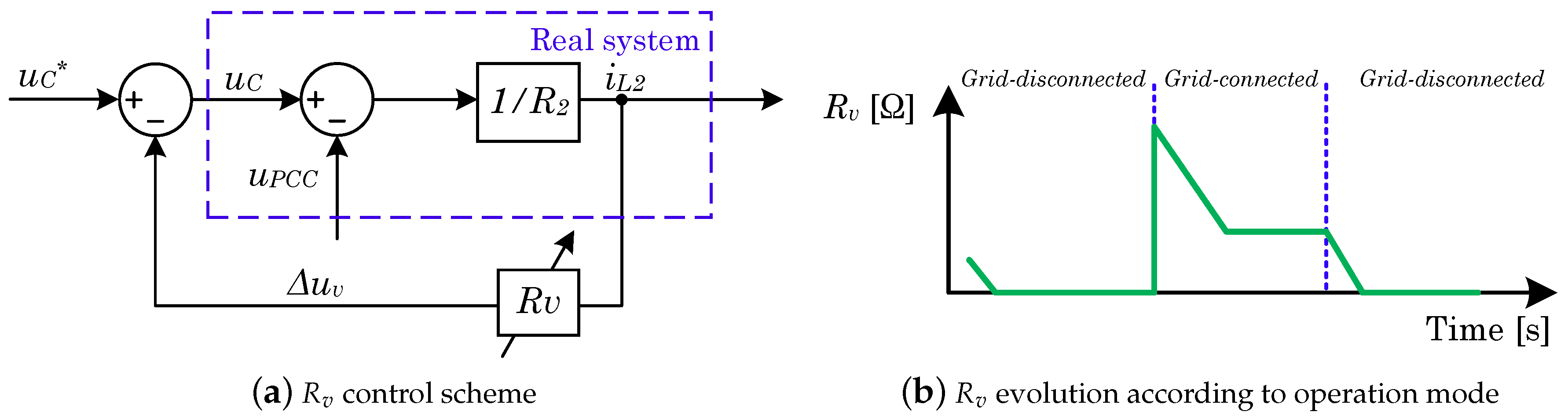

3.2. DC–AC Four-Leg Converter Control

3.2.1. Control Assumptions

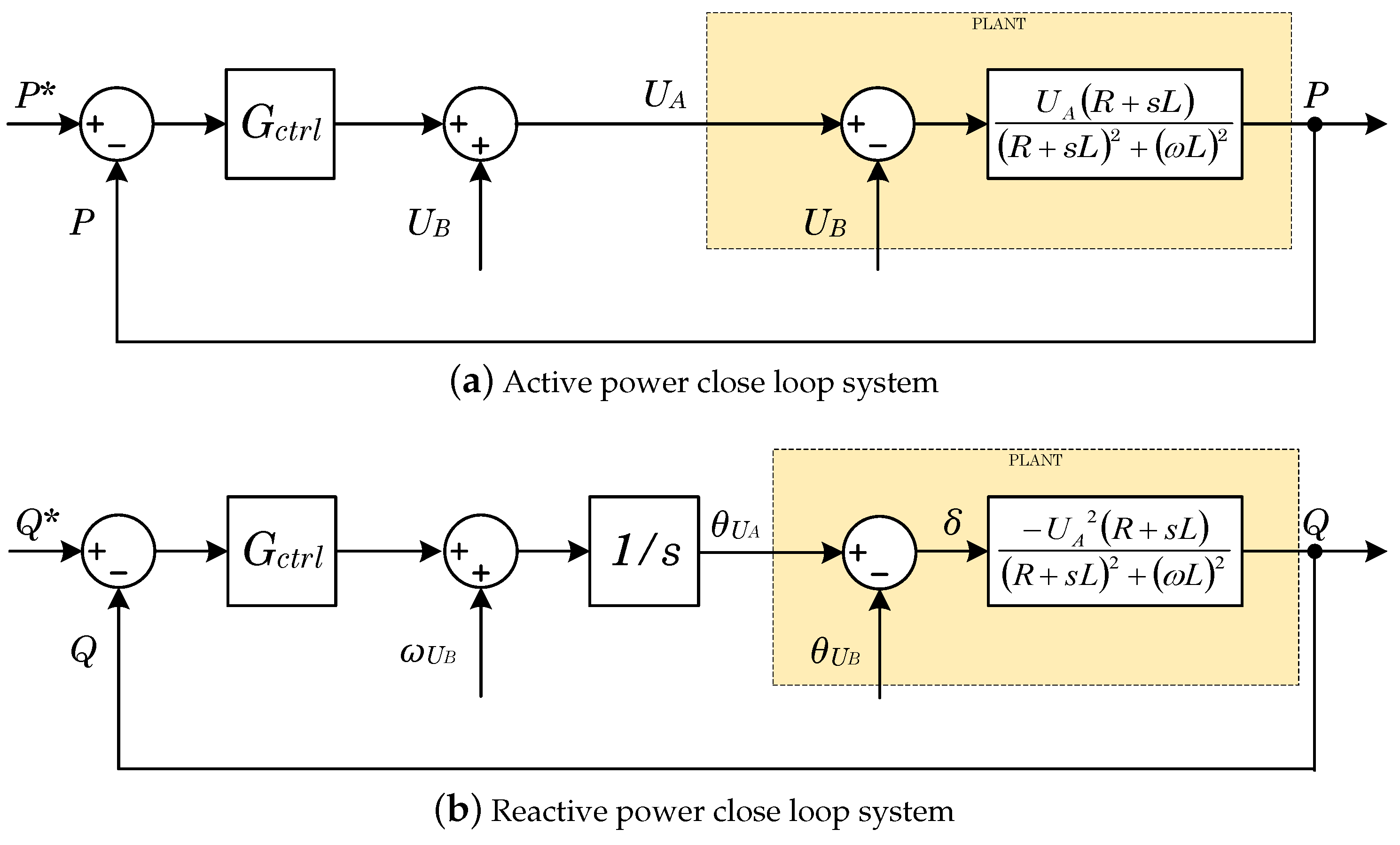

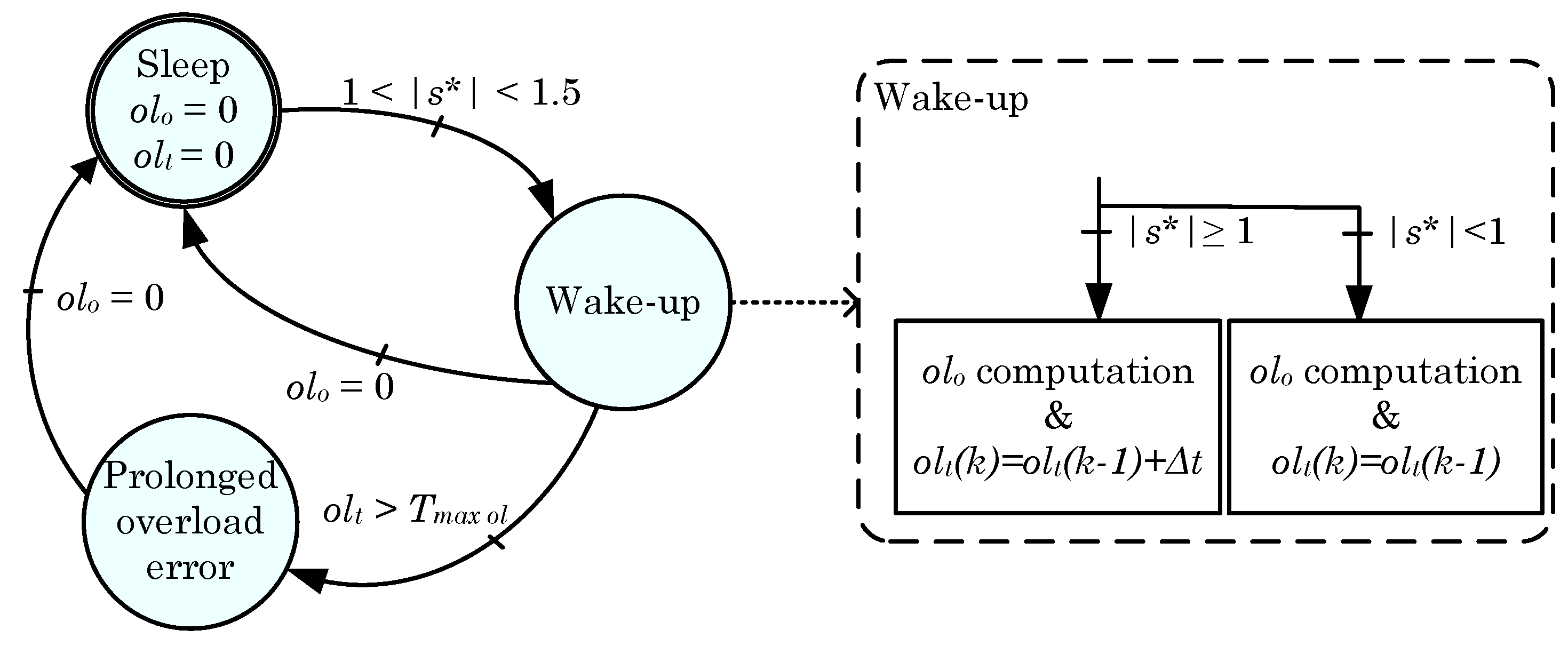

3.2.2. Power Over-Load Supervisor for the Grid-Connected Mode

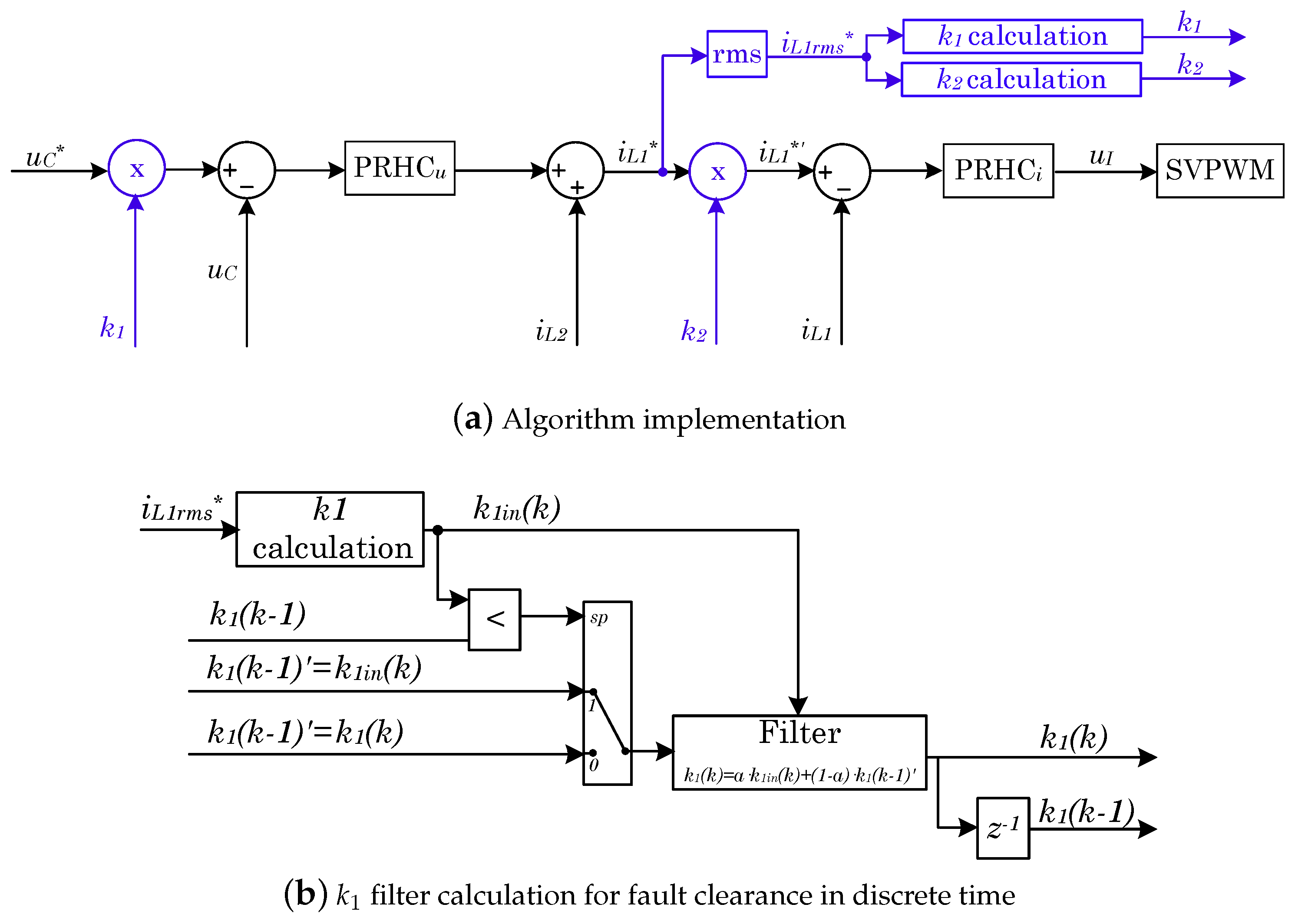

3.3. Short-Circuit Proof Algorithm for Grid-Disconnected Mode

4. Results

4.1. The Converter Set-Up

4.2. Simulated Results

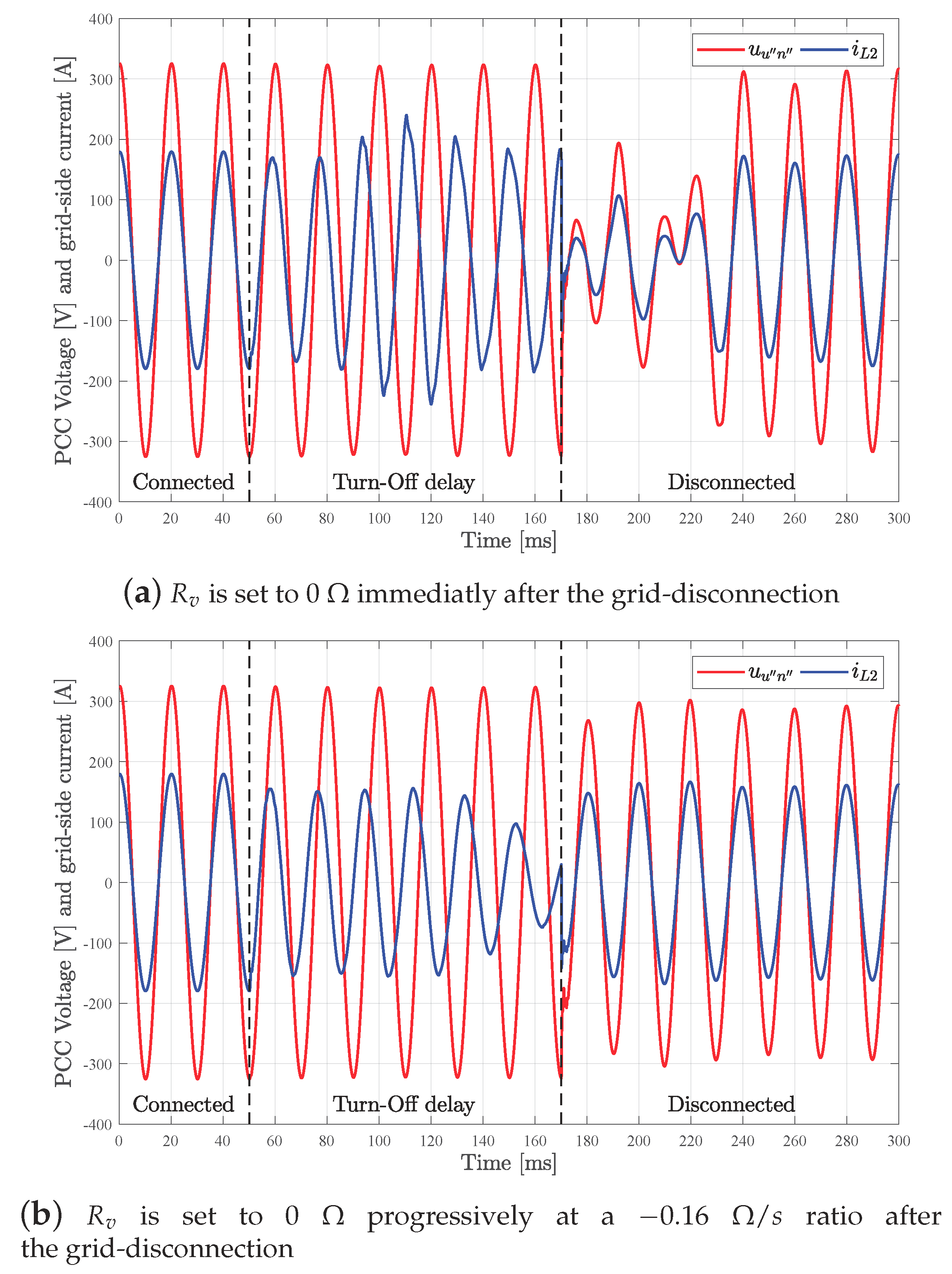

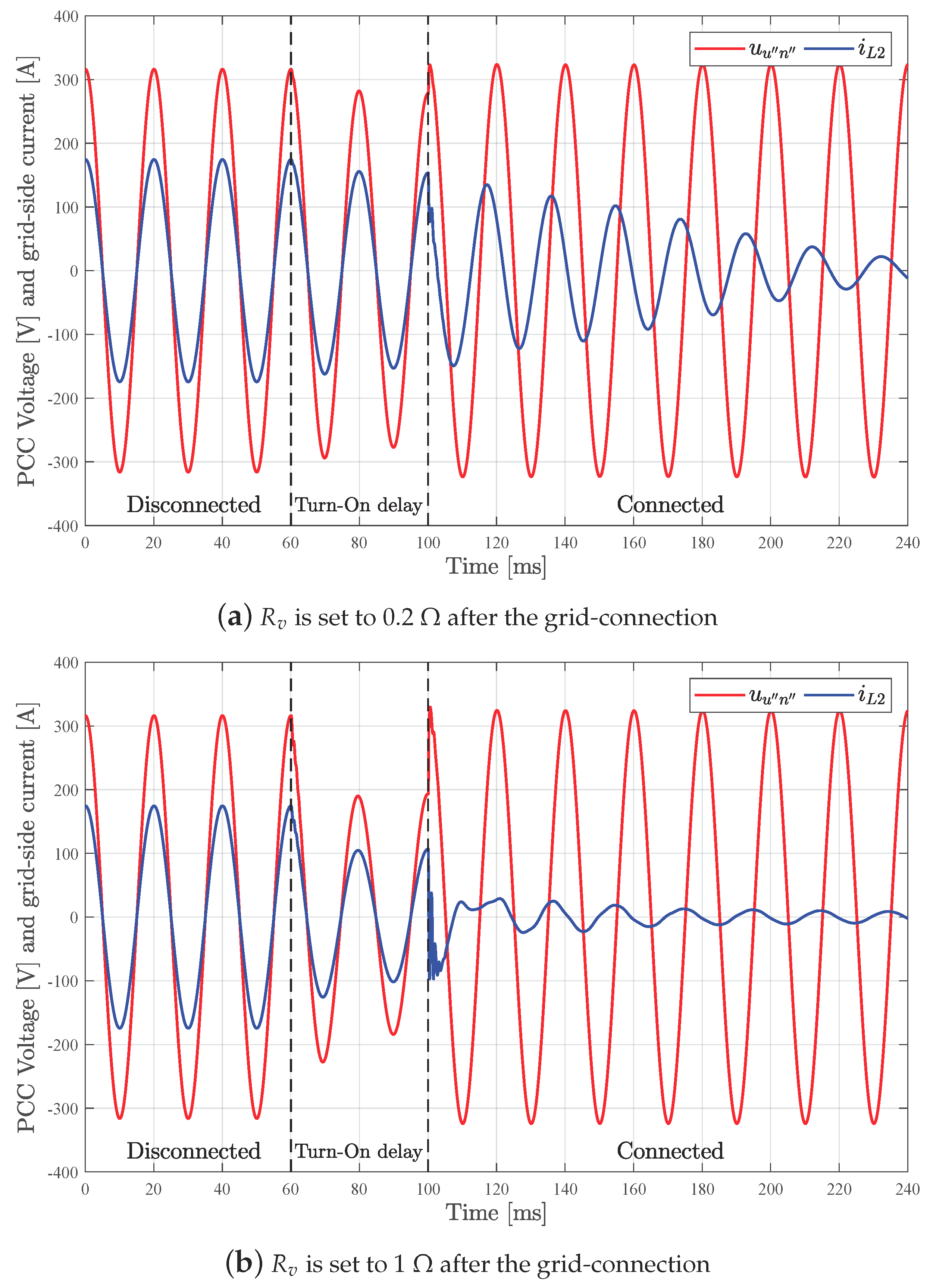

4.2.1. Virtual Resistance Effect on the Transference

4.2.2. Power Over-Load Supervisor

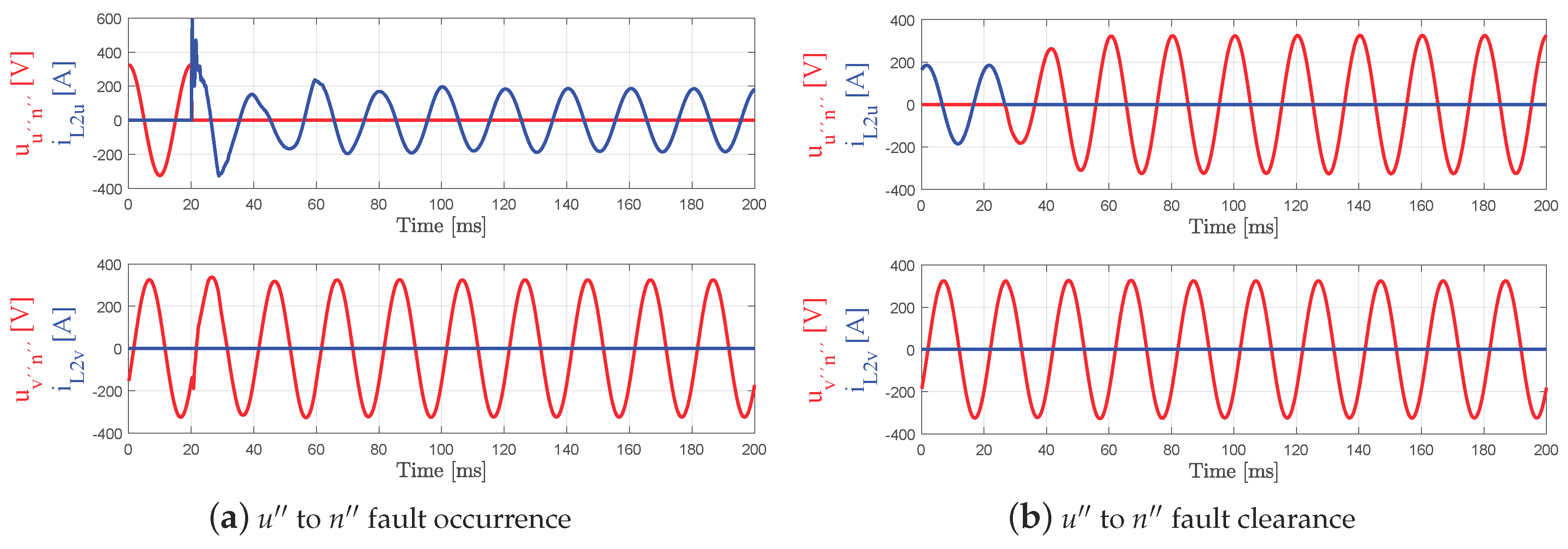

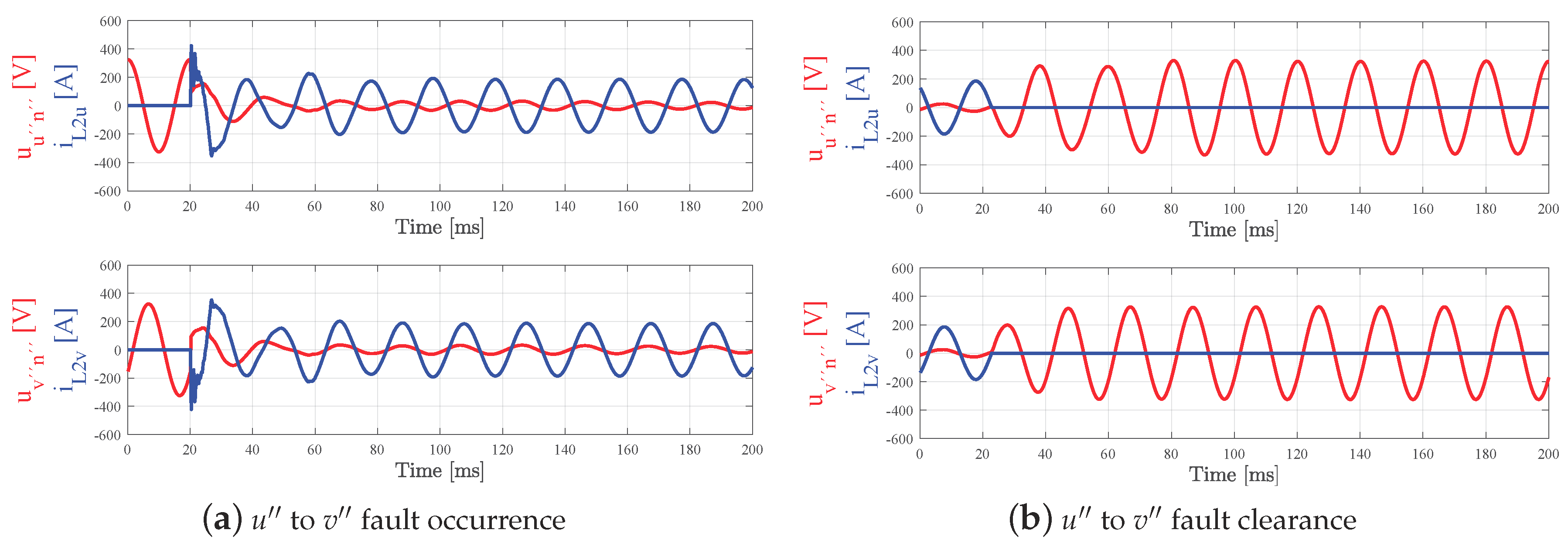

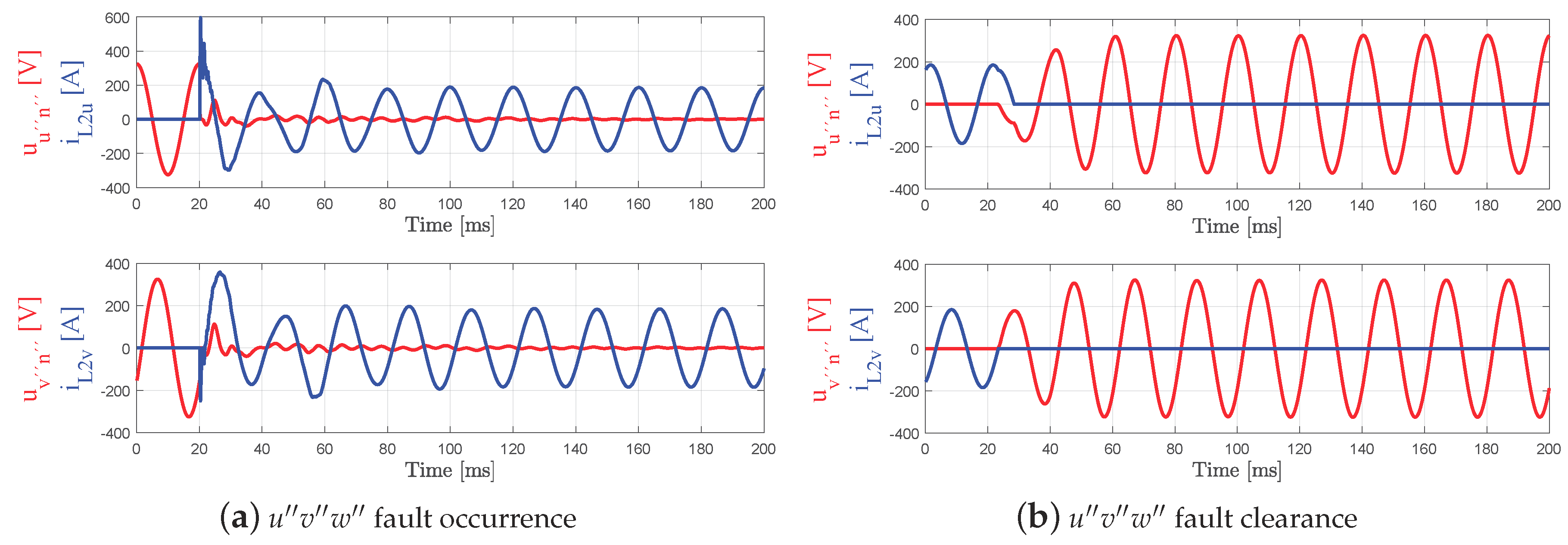

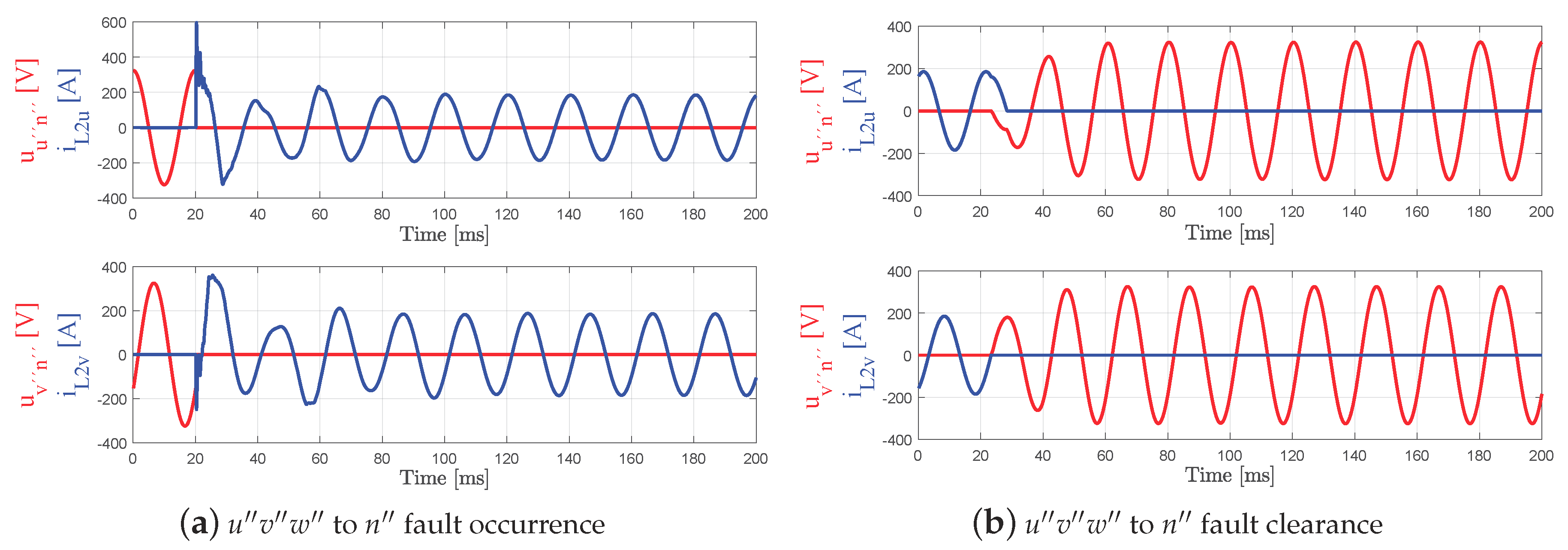

4.2.3. Short-Circuit Proof Algorithm

4.3. Experimental Results

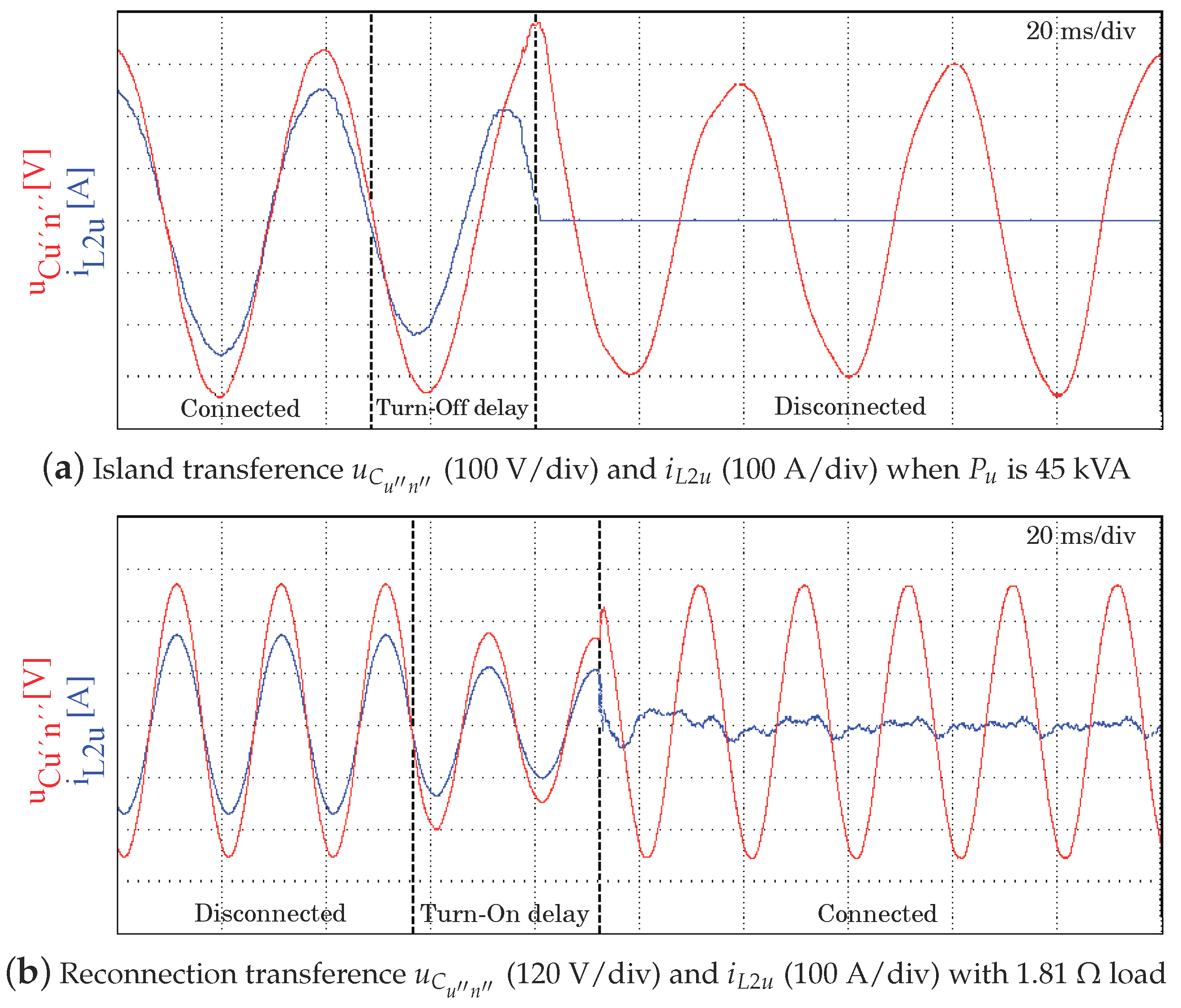

4.3.1. Virtual Resistance Effect on the Transference

4.3.2. Four Quadrant Control Capability

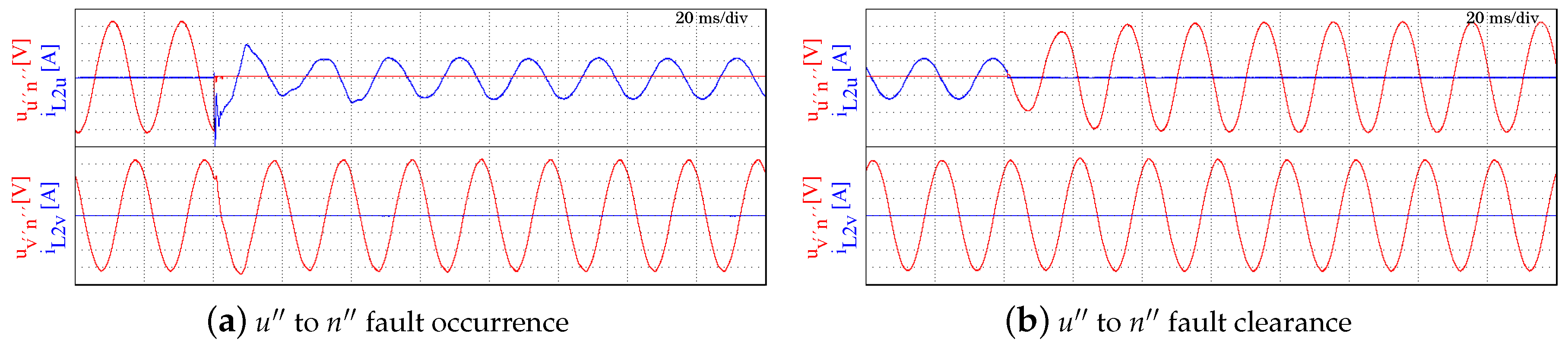

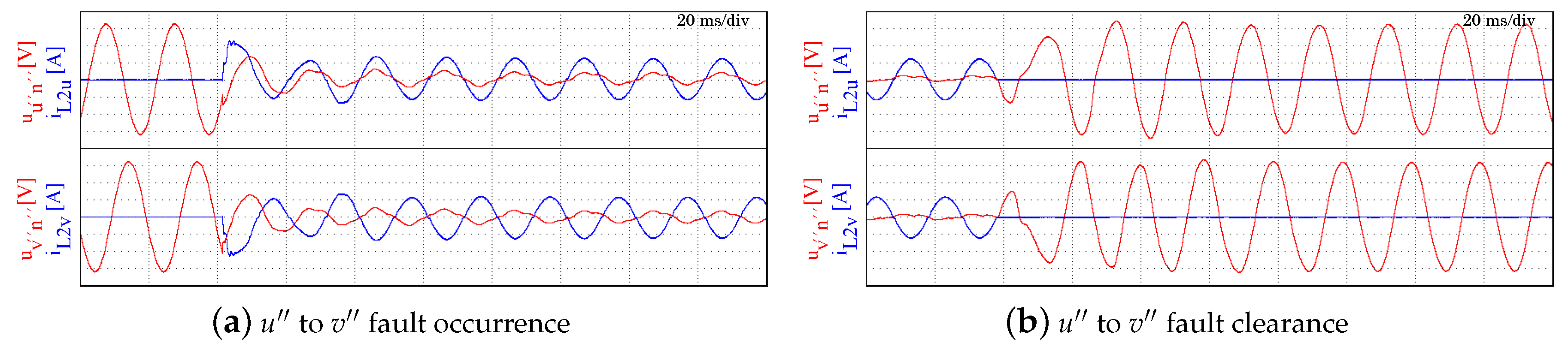

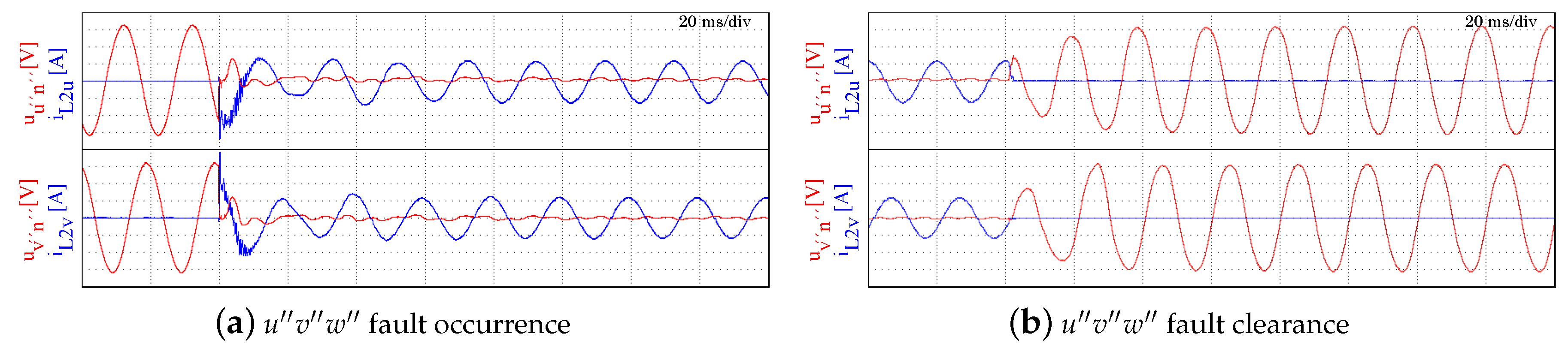

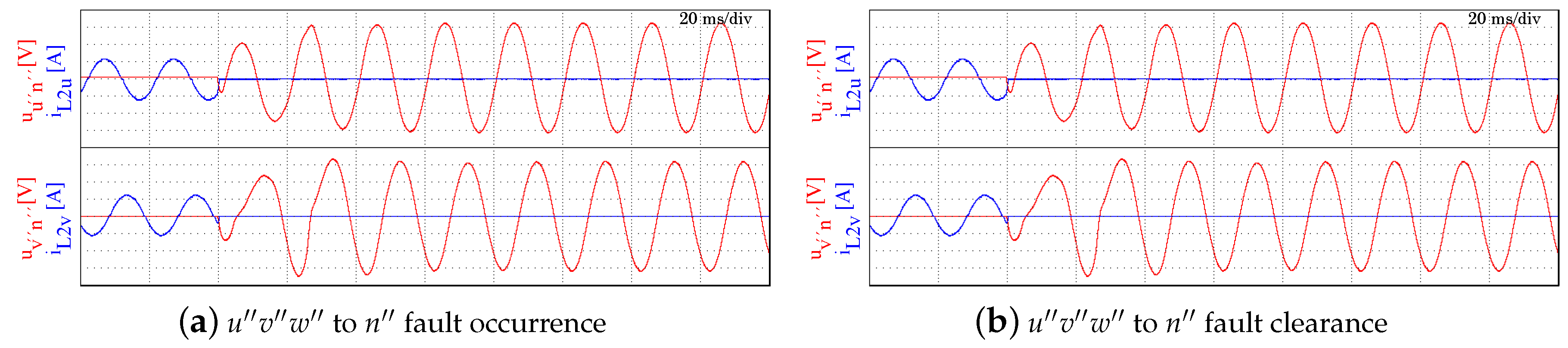

4.3.3. Short-Circuit Proof Algorithm

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Hatziargyriou, N. The Microgrids Concept. In Microgrids: Architectures and Control; IEEE: Piscataway, NJ, USA, 2014. [Google Scholar] [CrossRef]

- Bevrani, H.; Watanabe, M.; Mitani, Y. Microgrid Control: Concepts and Classification. In Power System Monitoring and Control; IEEE: Piscataway, NJ, USA, 2014. [Google Scholar] [CrossRef]

- Hartono, B.S.; Budiyanto, Y.; Setiabudy, R. Review of microgrid technology. In Proceedings of the 2013 International Conference on QiR (Quality in Research), Yogyakarta, Indonesia, 25–28 June 2013; pp. 127–132. [Google Scholar] [CrossRef]

- Cecati, C.; Khalid, H.A.; Tinari, M.; Adinolfi, G.; Graditi, G. DC nanogrid for renewable sources with modular DC–DC LLC converter building block. IET Power Electron. 2017, 10, 536–544. [Google Scholar] [CrossRef]

- Zubieta, L.E. Are Microgrids the Future of Energy?: DC Microgrids from Concept to Demonstration to Deployment. IEEE Electrif. Mag. 2016, 4, 37–44. [Google Scholar] [CrossRef]

- Guerrero, J.; Vasquez, J.; Teodorescu, R. Hierarchical control of droop controlled DC and AC microgrids. In Proceedings of the the 35th Annual Conference of the IEEE Industrial Electronics Society, Porto, Portugal, 3–5 November 2009. [Google Scholar]

- Guo, F.; Wen, C.; Mao, J.; Song, Y. Distributed Secondary Voltage and Frequency Restoration Control of Droop-Controlled Inverter-Based Microgrids. IEEE Trans. Ind. Electron. 2015, 62, 4355–4364. [Google Scholar] [CrossRef]

- Che, L.; Shahidehpour, M.; Alabdulwahab, A.; Al-Turki, Y. Hierarchical Coordination of a Community Microgrid With AC and DC Microgrids. IEEE Trans. Smart Grid 2015, 6, 3042–3051. [Google Scholar] [CrossRef]

- Dehkordi, N.M.; Sadati, N.; Hamzeh, M. Robust tuning of transient droop gains based on Kharitonov’s stability theorem in droop-controlled microgrids. IET Gener. Transm. Distrib. 2018, 12, 3495–3501. [Google Scholar] [CrossRef]

- Han, Y.; Shen, P.; Zhao, X.; Guerrero, J.M. Control Strategies for Islanded Microgrid Using Enhanced Hierarchical Control Structure With Multiple Current-Loop Damping Schemes. IEEE Trans. Smart Grid 2017, 8, 1139–1153. [Google Scholar] [CrossRef]

- He, J.; Li, Y.W.; Blaabjerg, F. Flexible Microgrid Power Quality Enhancement Using Adaptive Hybrid Voltage and Current Controller. IEEE Trans. Ind. Electron. 2014, 61, 2784–2794. [Google Scholar] [CrossRef]

- Lim, K.; Choi, J. PR control based cascaded current and voltage control for seamless transfer of microgrid. In Proceedings of the 2015 IEEE 2nd International Future Energy Electronics Conference (IFEEC), Taipei, Taiwan, 1–4 November 2015; pp. 1–6. [Google Scholar] [CrossRef]

- Rahmani-Andebili, M. Cooperative Distributed Energy Scheduling in Microgrids. In Electric Distribution, Network Management and Control; Springer: Singapore, 2018; pp. 235–254. [Google Scholar] [CrossRef]

- Han, Y.; Zhang, K.; Li, H.; Coelho, E.A.A.; Guerrero, J.M. MAS-Based Distributed Coordinated Control and Optimization in Microgrid and Microgrid Clusters. A Comprehensive Overview. IEEE Trans. Power Electron. 2018, 33, 6488–6508. [Google Scholar] [CrossRef]

- Marzband, M.; Sumper, A.; Dominguez-Garcia, J.L.; Gumara-Ferreta, R. Experimental validation of a real time energy management system for microgrids in islanded mode using a local day-ahead electricity market and MINLP. Energy Convers. Manag. 2013, 76, 314–322. [Google Scholar] [CrossRef]

- Marzband, M.; Azarinejadian, F.; Savaghebi, M.; Pouresmaeil, E.; Guerrero, J.M.; Lightbody, G. Smart transactive energy framework in grid-connected multiple home microgrids under independent and coalition operations. Renew. Energy 2018, 126, 95–106. [Google Scholar] [CrossRef]

- Marzband, M.; Fouladfar, M.H.; Akoredei, M.F.; Pouresmaeil, E.; Lightbody, G. Framework for Smart Transactive Energy in Home-Microgrids Considering Coalition Formation and Demand Side Management. Sustain. Cities Soc. 2018, 40, 136–154. [Google Scholar] [CrossRef]

- Tavakoli, M.; Shokridehaki, F.; Marzband, M.; Godinac, R.; Pouresmaeil, E. A two stage hierarchical control approach for the optimal energy management in commercial building microgrids based on local wind power and PEVs. Sustain. Cities Soc. 2018, 41, 332–340. [Google Scholar] [CrossRef]

- Hatziargyriou, N. Microgrid Protection. In Microgrids: Architectures and Control; IEEE: Piscataway, NJ, USA, 2014. [Google Scholar] [CrossRef]

- Sharkh, S.M.; Abu-Sara, M.A.; Orfanoudakis, G.I.; Hussain, B. Microgrid Protection. In Power Electronic Converters for Microgrids; IEEE: Piscataway, NJ, USA, 2014. [Google Scholar] [CrossRef]

- Carpio-Huayllas, T.E.D.; Ramos, D.S.; Vasquez-Arnez, R.L. Microgrid transition to islanded modes: Conceptual background and simulation procedures aimed at assessing its dynamic performance. In Proceedings of the Transmission and Distribution Conference and Exposition (T D), Orlando, FL, USA, 7–10 May 2012; pp. 1–6. [Google Scholar] [CrossRef]

- Heredero-Peris, D.; Chillón-Antón, C.; Pagès-Giménez, M.; Gross, G.; Montesinos-Miracle, D. Implementation of grid-connected to/from off-grid transference for micro-grid inverters. In Proceedings of the IECON 2013—39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013; pp. 840–845. [Google Scholar] [CrossRef]

- Liu, Z.; Liu, J. Unified control based seamless transfer of microgrids. In Proceedings of the 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Seoul, Korea, 1–5 June 2015; pp. 1477–1482. [Google Scholar] [CrossRef]

- Shen, Z.J. Ultrafast Solid-State Circuit Breakers: Protecting Converter-Based ac and dc Microgrids Against Short Circuit Faults [Technology Leaders]. IEEE Electrif. Mag. 2016, 4, 70–72. [Google Scholar] [CrossRef]

- Laaksonen, H.J. Protection Principles for Future Microgrids. IEEE Trans. Power Electron. 2010, 25, 2910–2918. [Google Scholar] [CrossRef]

- Zhang, J.; Wu, P.; Hong, J. Control strategy of microgrid inverter operation in Grid-connected and Grid-disconnected modes. In Proceedings of the International Conference on Electric Information and Control Engineering (ICEICE), Wuhan, China, 25–27 March 2011; pp. 1257–1260. [Google Scholar] [CrossRef]

- Shan, W.C.; Lin, L.X.; Li, G.; Wei, L.Y. A seamless operation mode transition control strategy for a microgrid based on master–slave control. In Proceedings of the 2012 31st Chinese Control Conference, Hefei, China, 25–27 July 2012; pp. 6768–6775. [Google Scholar]

- Brabandere, K.D. Voltage and Frequency Droop Control in Low Voltage Grids by Distributed Generators with Inverter Front-End. Ph.D. Thesis, Katholieke Universiteit Leuven, Leuven, Belgium, 2006. [Google Scholar]

- Wessels, C.; Dannehl, J.; Fuchs, F. Active damping of LCL-filter resonance based on virtual resistor for PWM rectifiers; stability analysis with different filter parameters. In Proceedings of the 2008 IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008; pp. 3532–3538. [Google Scholar] [CrossRef]

- Kim, J.; Guerrero, J.; Rodríguez, P.; Teodorescu, R.; Nam, K. Mode Adaptive Droop Control with Virtual Output Impedances for an Inverter-Based Flexible AC Microgrid. IEEE Trans. Power Electron. 2011, 26, 689–701. [Google Scholar] [CrossRef]

- Guo, X.; Lu, Z.; Wang, B.; Sun, X.; Wang, L.; Guerrero, J. Dynamic Phasors-Based Modeling and Stability Analysis of Droop-Controlled Inverters for Microgrid Applications. IEEE Trans. Smart Grid 2014, 5, 2980–2987. [Google Scholar] [CrossRef]

- Bayindir, R.; Irmak, E.; Issi, F.; Guler, N. Short-circuit fault analysis on microgrid. In Proceedings of the 2015 International Conference on Renewable Energy Research and Applications (ICRERA), Palermo, Italy, 22–25 November 2015; pp. 1248–1252. [Google Scholar] [CrossRef]

- Almutairy, I. A review of coordination strategies and techniques for overcoming challenges to microgrid protection. In Proceedings of the 2016 Saudi Arabia Smart Grid (SASG), Jeddah, Saudi Arabia, 6–8 December 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Lai, X.; Liu, F.; Deng, K.; Gao, Q.; Zha, X. A short-circuit current calculation method for low-voltage DC microgrid. In Proceedings of the 2014 International Power Electronics and Application Conference and Exposition, Shanghai, China, 5–8 November 2014; pp. 365–371. [Google Scholar] [CrossRef]

- Ouaida, R.; Berthou, M.; Tournier, D.; Depalma, J. State of art of current and future technologies in current limiting devices. In Proceedings of the 2015 IEEE First International Conference on DC Microgrids (ICDCM), Atlanta, GA, USA, 7–10 June 2015; pp. 175–180. [Google Scholar] [CrossRef]

- Balasreedharan, S.S.; Thangavel, S. An adaptive fault identification scheme for DC microgrid using event based classification. In Proceedings of the 2016 3rd International Conference on Advanced Computing and Communication Systems (ICACCS), Coimbatore, India, 22–23 January 2016; Volume 1, pp. 1–7. [Google Scholar] [CrossRef]

- Cairoli, P.; Rodrigues, R.; Zheng, H. Fault current limiting power converters for protection of DC microgrids. In Proceedings of the SoutheastCon 2017, Charlotte, NC, USA, 30 March–2 April 2017; pp. 1–7. [Google Scholar] [CrossRef]

- Pei, X.; Chen, Z.; Wang, S.; Kang, Y. Overcurrent protection for inverter-based distributed generation system. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 2328–2332. [Google Scholar] [CrossRef]

- Babqi, A.J.; Etemadi, A.H. MPC-based microgrid control with supplementary fault current limitation and smooth transition mechanisms. IET Gener. Transm. Distrib. 2017, 11, 2164–2172. [Google Scholar] [CrossRef]

- Beheshtaein, S.; Savaghebi, M.; Guerrero, J.M.; Cuzner, R.; Vasquez, J.C. A secondary-control based fault current limiter for four-wire three phase inverter-interfaced DGs. In Proceedings of the IECON 2017—43rd Annual Conference of the IEEE Industrial Electronics Society, Beijing, China, 29 October–1 November 2017; pp. 2363–2368. [Google Scholar] [CrossRef]

- Rahmatian, M.; Sanjari, M.J.; Gholami, M.; Gharehpetian, G.B. Optimal control of distribution line series compensator in microgrid considering fault current limitation function. In Proceedings of the 2012 17th Conference on Electrical Power Distribution, Tehran, Iran, 2–3 May 2012; pp. 1–5. [Google Scholar]

- Sadeghkhani, I.; Golshan, M.E.H.; Mehrizi-Sani, A.; Guerrero, J.M. Low-voltage ride-through of a droop-based three-phase four-wire grid-connected microgrid. IET Gener. Transm. Distrib. 2018, 12, 1906–1914. [Google Scholar] [CrossRef]

- Li, Y.; Vilathgamuwa, D.M.; Loh, P.C. Microgrid power quality enhancement using a three-phase four-wire grid-interfacing compensator. IEEE Trans. Ind. Appl. 2005, 41, 1707–1719. [Google Scholar] [CrossRef]

- Kim, G.H.; Hwang, C.; Jeon, J.H.; Byeon, G.S.; Ahn, J.B.; Jo, C.H. Characteristic analysis of three-phase four-leg inverter based load unbalance compensator for stand-alone microgrid. In Proceedings of the 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Seoul, Korea, 1–5 June 2015; pp. 1491–1496. [Google Scholar] [CrossRef]

- Liu, Y.-H.; Yang, J.; Li, H.; Wang, C. The research of three phase four wire active power filter on small independent micro-grid. In Proceedings of the 2016 China International Conference on Electricity Distribution (CICED), Xi’an, China, 10–13 August 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Lee, W.; Han, B.M.; Cha, H. Battery ripple current reduction in a three-phase interleaved dc-dc converter for 5 kW battery charger. In Proceedings of the 2011 IEEE Energy Conversion Congress and Exposition, Phoenix, AZ, USA, 17–22 September 2011; pp. 3535–3540. [Google Scholar] [CrossRef]

- Khosroshahi, A.; Abapour, M.; Sabahi, M. Reliability Evaluation of Conventional and Interleaved DC–DC Boost Converters. IEEE Trans. Power Electron. 2015, 30, 5821–5828. [Google Scholar] [CrossRef]

- Llonch-Masachs, M.; Heredero-Peris, D.; Montesinos-Miracle, D.; Rull-Duran, J. Understanding the three and four-leg inverter Space Vector. In Proceedings of the 2016 18th European Conference on Power Electronics and Applications (EPE’16 ECCE Europe), Karlsruhe, Germany, 5–9 September 2016; pp. 1–10. [Google Scholar] [CrossRef]

- Heredero-Peris, D.; Pagès-Giménez, M.; Montesinos-Miracle, D. Inverter design for four-wire microgrids. In Proceedings of the 2015 17th European Conference on Power Electronics and Applications (EPE’15 ECCE-Europe), Geneva, Switzerland, 8–10 September 2015; pp. 1–10. [Google Scholar] [CrossRef]

- Rivas, H.A.; Bergas, J. Frequency Determination in a Single-Phase Voltage Signal using Adaptative Notch Filters. In Proceedings of the 2007 9th International Conference on Electrical Power Quality and Utilisation, Barcelona, Spain, 9–11 October 2007; pp. 1–7. [Google Scholar] [CrossRef]

- Yepes, A.G. Digital Resonant Current Controllers for Voltage Source Converters. Ph.D. Thesis, Universidad de Vigo, Pontevedra, Spain, 2011. [Google Scholar]

- Rodríguez, F.; Bueno, E.; Aredes, M.; Rolim, L.; Neves, F.; Cavalcanti, M. Discrete-time implementation of second order generalized integrators for grid converters. In Proceedings of the 2008 34th Annual Conference of IEEE Industrial Electronics, Orlando, FL, USA, 10–13 November 2008; pp. 176–181. [Google Scholar]

- Balaras, C.A. The role of thermal mass on the cooling load of buildings. An overview of computational methods. Energy Build. 1996, 24, 1–10. [Google Scholar] [CrossRef]

- Mjallal, I.; Farhat, H.; Hammoud, M.; Ali, S.; Assi, I. Improving the Cooling Efficiency of Heat Sinks through the Use of Different Types of Phase Change Materials. Technologies 2018, 6, 5. [Google Scholar] [CrossRef]

- ITI (CBEMA) Curve Application Note; Techreport; Information Technology Industry Council: Washington, DC, USA, 2000.

| Parameter | Value | Units | |

|---|---|---|---|

| Adaptive DC-link PI controller | 0.043 | ||

| 1.43 | |||

| Adaptive 100 Hz filter [50] | Adaptive coefficient | 0.05 | |

| Attenuate B coefficient of cut-off frequency | 4 | ||

| PI Voltage controller | 3.5 | ||

| 70 | |||

| PI Current controller | 0.16 | ||

| 33.75 | |||

| DC–DC converter | Switching & control frequency | 8 | kHz |

| (each interleaved inductance) | 400 | H | |

| 420 | F | ||

| 7.2 | mF |

| Parameter | Value | Units | |

|---|---|---|---|

| Droop controller | m for active power loop | 0.000003 | s |

| n for reactive power loop | 0.000004 | ||

| for reactive power loop | 0.0009 | ||

| Low-pass filter (LPF) constant | 0.1 | ||

| PRHC Voltage controller | 0.27 | ||

| 0.26 | |||

| 0.001 | |||

| 0.001 | |||

| PRHC Current controller | 0.7468 | ||

| 3.93 | |||

| 0.1 | |||

| 0.04 | |||

| Fault current limiters | K | 0.9 | A |

| I | 130 | ||

| (over-load filter parameter) | 0.01 | ||

| Virtual impedances | (initial-state grid-connected) | 1.0 | |

| (steady-state grid-connected) | 0.2 | ||

| (steady-state grid-disconnected) | 0 | ||

| change ratio | −0.16 | ||

| DC–AC converter | Switching & control frequency | 8 | kHz |

| (active phases & neutral wire) | 250 | H | |

| C (star connected) | 350 | F | |

| (leakage transformer inductance) | 70 | H |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Heredero-Peris, D.; Chillón-Antón, C.; Pagès-Giménez, M.; Montesinos-Miracle, D.; Santamaría, M.; Rivas, D.; Aguado, M. An Enhancing Fault Current Limitation Hybrid Droop/V-f Control for Grid-Tied Four-Wire Inverters in AC Microgrids. Appl. Sci. 2018, 8, 1725. https://doi.org/10.3390/app8101725

Heredero-Peris D, Chillón-Antón C, Pagès-Giménez M, Montesinos-Miracle D, Santamaría M, Rivas D, Aguado M. An Enhancing Fault Current Limitation Hybrid Droop/V-f Control for Grid-Tied Four-Wire Inverters in AC Microgrids. Applied Sciences. 2018; 8(10):1725. https://doi.org/10.3390/app8101725

Chicago/Turabian StyleHeredero-Peris, Daniel, Cristian Chillón-Antón, Marc Pagès-Giménez, Daniel Montesinos-Miracle, Mikel Santamaría, David Rivas, and Mónica Aguado. 2018. "An Enhancing Fault Current Limitation Hybrid Droop/V-f Control for Grid-Tied Four-Wire Inverters in AC Microgrids" Applied Sciences 8, no. 10: 1725. https://doi.org/10.3390/app8101725

APA StyleHeredero-Peris, D., Chillón-Antón, C., Pagès-Giménez, M., Montesinos-Miracle, D., Santamaría, M., Rivas, D., & Aguado, M. (2018). An Enhancing Fault Current Limitation Hybrid Droop/V-f Control for Grid-Tied Four-Wire Inverters in AC Microgrids. Applied Sciences, 8(10), 1725. https://doi.org/10.3390/app8101725