High Performance MRAM with Spin-Transfer-Torque and Voltage-Controlled Magnetic Anisotropy Effects

Abstract

:Featured Application

Abstract

1. Introduction

2. MTJ Fundamental and Physical Modeling

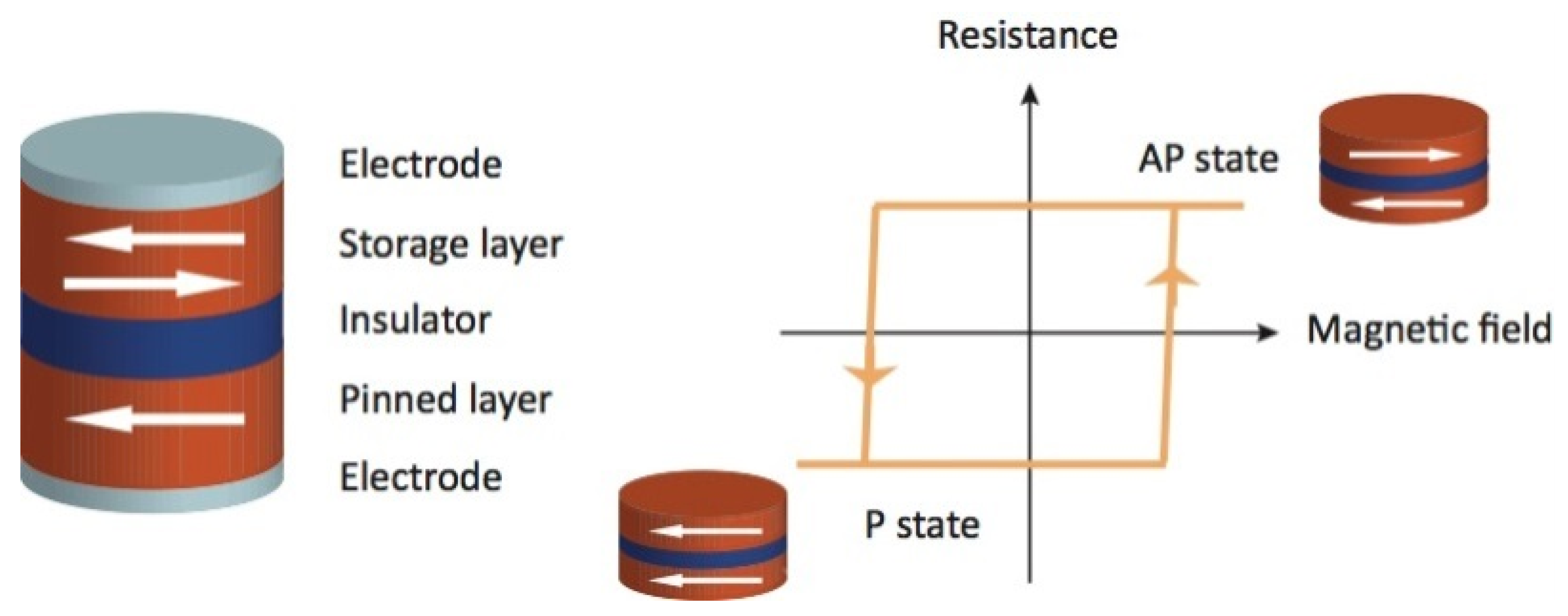

2.1. STT-MTJ

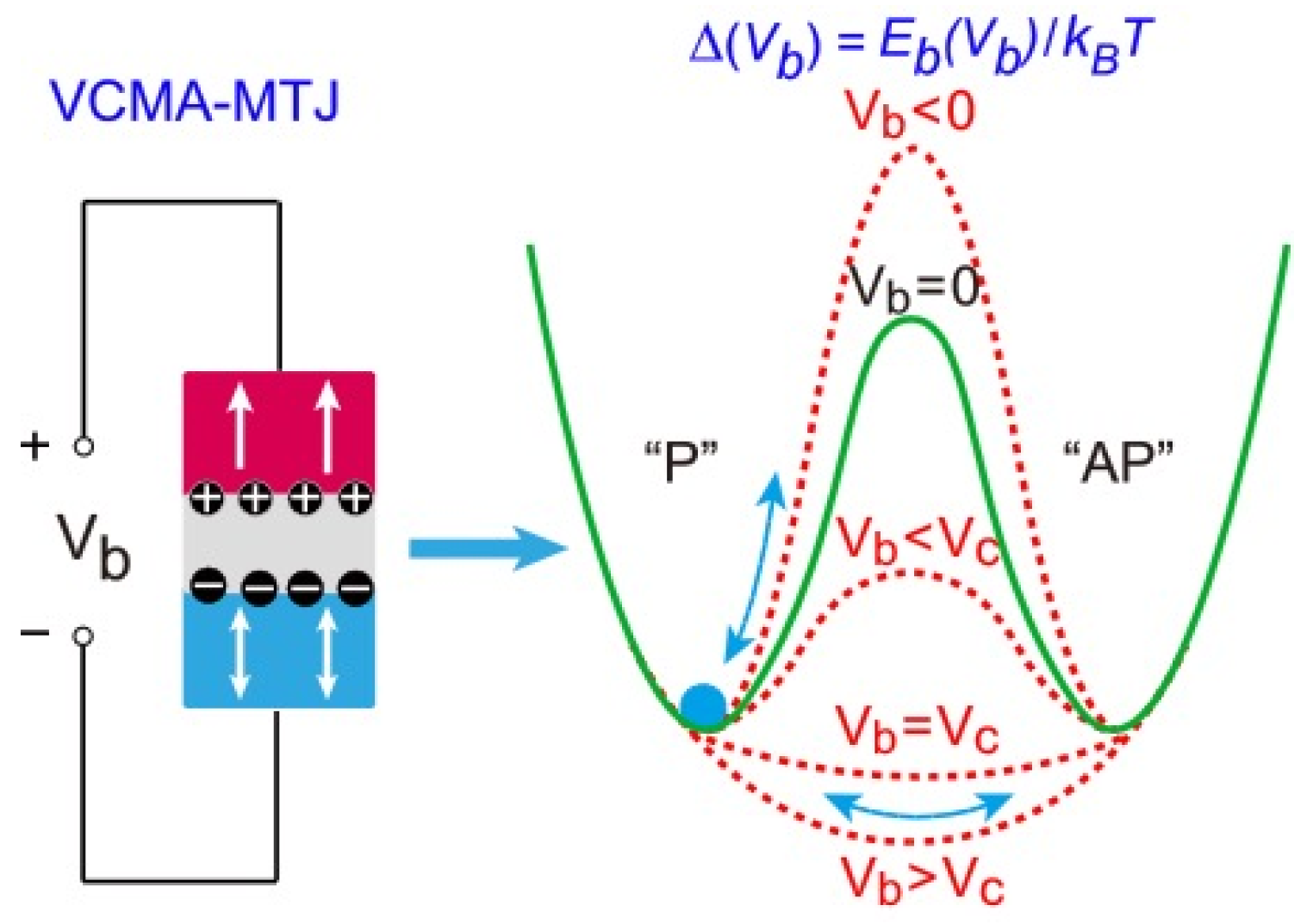

2.2. VCMA-Assisted Switching

3. High Performance MRAM Writing

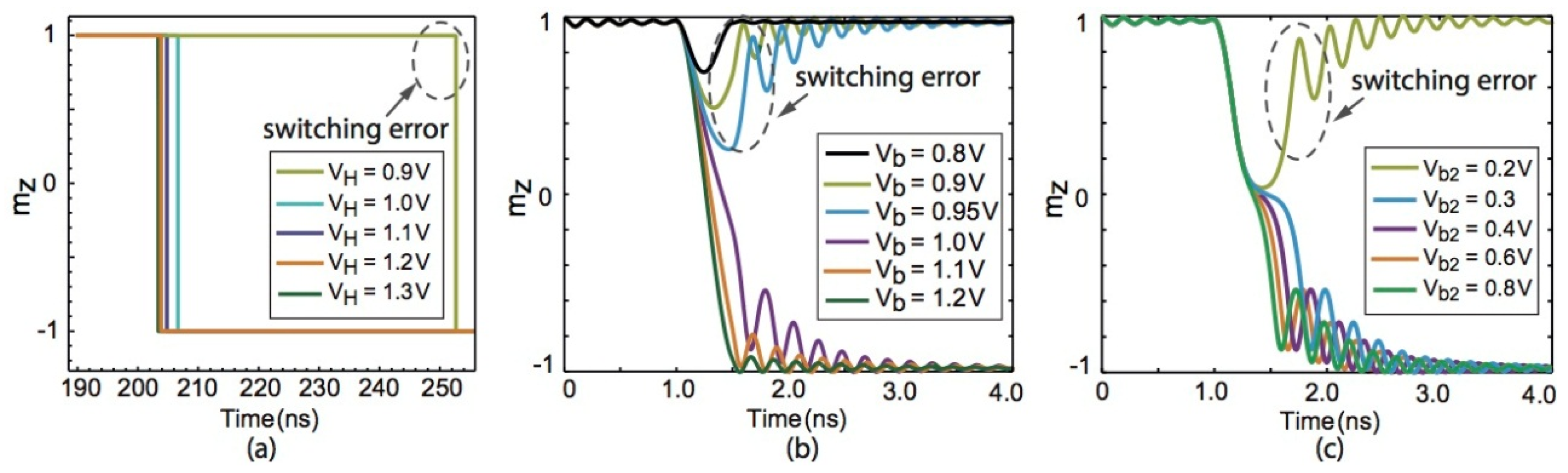

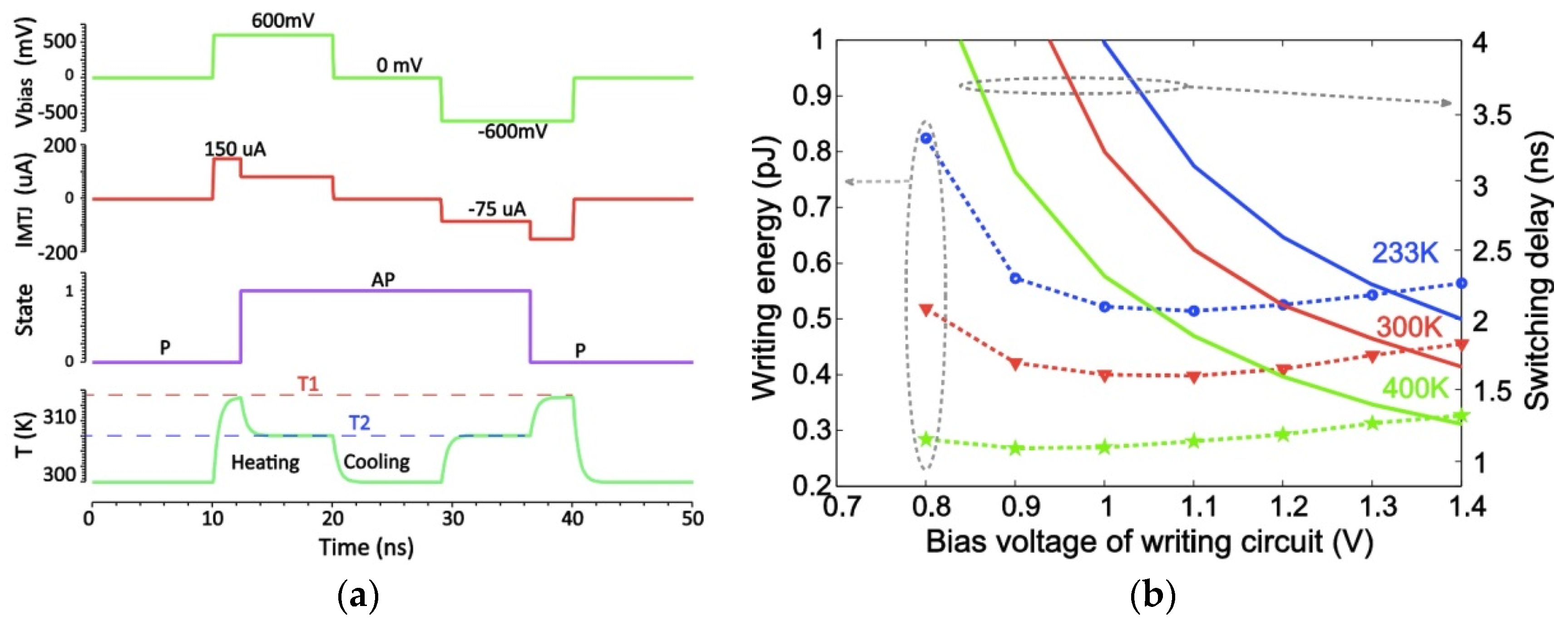

3.1. MRAM Writing

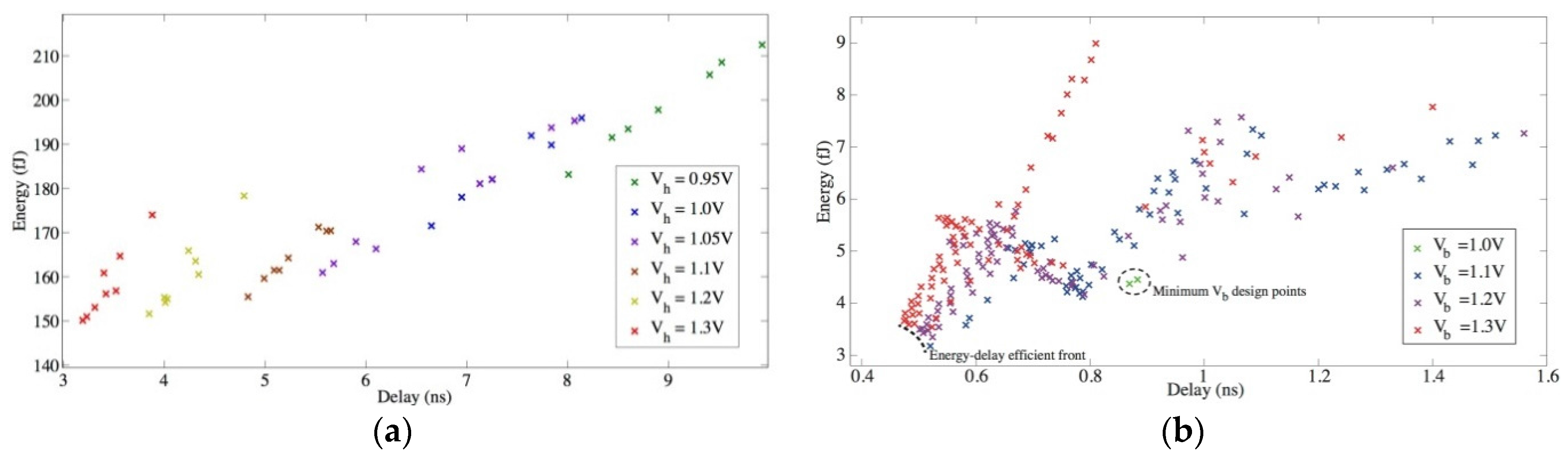

3.2. Energy Efficiency

3.3. Stochastic Effects

3.4. Reliability Issues

3.4.1. Process Variation

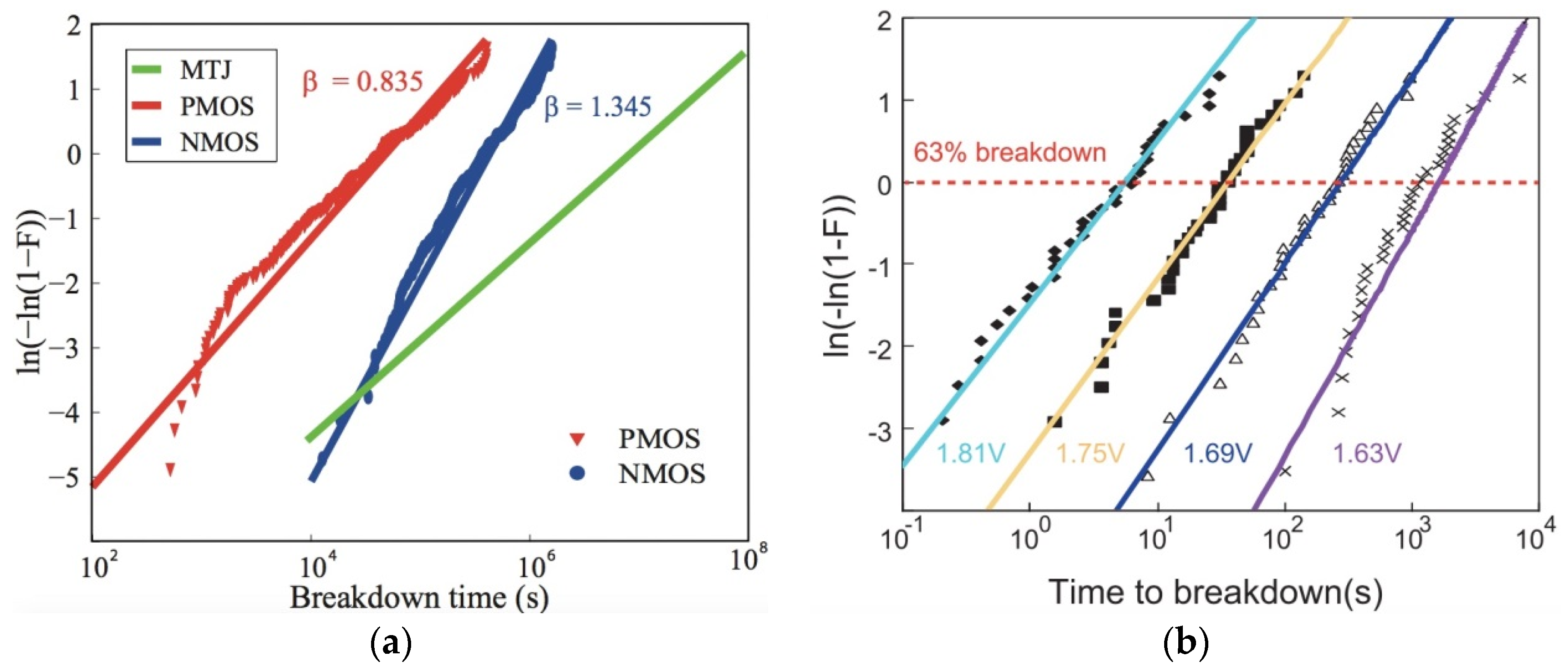

3.4.2. Dielectric Breakdown

3.4.3. MTJ Thermal Stability

4. Discussion

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Chappert, C.; Fert, A.; Van Dau, F.N. The emergence of spin electronics in data storage. Nat. Mater. 2007, 6, 813–823. [Google Scholar] [CrossRef] [PubMed]

- Baibich, M.N.; Broto, J.M.; Fert, A.; Van Dau, F.N.; Petroff, F.; Etienne, P.; Creuzet, G.; Friederich, A.; Chazelas, J. Giant magnetoresistance of (001)Fe/(001)Cr magnetic superlattices. Phys. Rev. Lett. 1988, 61, 2472–2475. [Google Scholar] [CrossRef] [PubMed]

- Binasch, G.; Grunberg, P.; Saurenbach, F.; Zinn, W. Enhanced magnetoresistance in layered magnetic structures with antiferromagnetic interlayer exchange. Phys. Rev. B 1989, 39, 4828–4830. [Google Scholar] [CrossRef]

- Julliere, M. Tunneling between ferromagnetic films. Phys. Lett. A 1975, 54, 225–226. [Google Scholar] [CrossRef]

- Gallagher, W.J.; Parkin, S.S.P. Development of the magnetic tunnel junction MRAM at IBM: From first junctions to a 16-Mb MRAM demonstrator chip. IBM J. Res. Dev. 2006, 50, 5–23. [Google Scholar] [CrossRef]

- Nozieres, J.; Dieny, B.; Redon, O.; Sousa, R.; Prejbeanu, I. Magnetic Memory with a Magnetic Tunnel Junction Written in a Thermally Assisted Manner, and Method for Writing the Same; U.S. Patent Office: Washington, DC, USA, 2005. [Google Scholar]

- Slonczewski, J.C. Current-driven excitation of magnetic multilayers. J. Magn. Magn. Mater. 1996, 159, L1–L7. [Google Scholar] [CrossRef]

- Berger, L. Emission of spin waves by a magnetic multilayer traversed by a current. Phys. Rev. B 1996, 54, 9353–9358. [Google Scholar] [CrossRef]

- Ikeda, S.; Miura, K.; Yamamoto, H.; Mizunuma, K.; Gan, H.D.; Endo, M.; Kanai, S.; Hayakawa, J.; Matsukura, F.; Ohno, H. A perpendicular anisotropy CoFeB-MgO magnetic tunnel junction. Nat. Mater. 2010, 9, 721–724. [Google Scholar] [CrossRef] [PubMed]

- Liu, L.; Lee, O.J.; Gudmundsen, T.J.; Ralph, D.C.; Buhrman, R.A. Current induced switching of perpendicularly magnetized magnetic layers using spin torque from the spin hall effect. Phys. Rev. Lett. 2012, 109, 096602. [Google Scholar] [CrossRef] [PubMed]

- Liu, L.; Pai, C.-F.; Li, Y.; Tseng, H.W.; Ralph, D.C.; Buhrman, R.A. Spin-torque switching with the giant spin hall effect of tantalum. Science 2012, 336, 555–558. [Google Scholar] [CrossRef] [PubMed]

- Yu, S.; Chen, P.Y. Emerging memory technologies: Recent trends and prospects. IEEE Solid-State Circuits Mag. 2016, 8, 43–56. [Google Scholar] [CrossRef]

- Endoh, T.; Koike, H.; Ikeda, S.; Hanyu, T.; Ohno, H. An overview of nonvolatile emerging memories-spintronics for working memories. IEEE J. Emerg. Sel. Top. Circuits Syst. 2016, 6, 109–119. [Google Scholar] [CrossRef]

- Kang, W.; Zhang, Y.; Wang, Z.; Klein, J.-O.; Chappert, C.; Ravelosona, D.; Wang, G.; Zhang, Y.; Zhao, W. Spintronics: Emerging Ultra-Low-Power Circuits and Systems beyond MOS Technology. J. Emerg. Technol. Comput. Syst. 2015, 12, 42. [Google Scholar] [CrossRef]

- Duan, C.G.; Jaswal, S.S.; Tsymbal, E.Y. Predicted magnetoelectric effect in Fe/BaTiO3 multilayers: Ferroelectric control of magnetism. Phys. Rev. Lett. 2006, 97, 047201. [Google Scholar] [CrossRef] [PubMed]

- Weisheit, M.; Fähler, S.; Marty, A.; Souche, Y.; Poinsignon, C.; Givord, D. Electric field-induced modification of magnetism in thin-film ferromagnets. Science 2007, 315, 349–351. [Google Scholar] [CrossRef] [PubMed]

- Maruyama, T.; Shiota, Y.; Nozaki, T.; Ohta, K.; Toda, N.; Mizuguchi, M.; Tulapurkar, A.A.; Shinjo, T.; Shiraishi, M.; Mizukami, S.; et al. Large voltage-induced magnetic anisotropy change in a few atomic layers of iron. Nat. Nanotechnol. 2009, 4, 158–161. [Google Scholar] [CrossRef] [PubMed]

- Endo, M.; Kanai, S.; Ikeda, S.; Matsukura, F.; Ohno, H. Electric-field effects on thickness dependent magnetic anisotropy of sputtered MgO/Co40Fe40B20/Ta structures. Appl. Phys. Lett. 2010, 96, 212503. [Google Scholar] [CrossRef]

- Wang, W.G.; Li, M.; Hageman, S.; Chien, C.L. Electric-field-assisted switching in magnetic tunnel junctions. Nat. Mater. 2012, 11, 64–68. [Google Scholar] [CrossRef] [PubMed]

- Duan, C.G.; Velev, J.P.; Sabirianov, R.F.; Zhu, Z.; Chu, J.; Jaswal, S.S.; Tsymbal, E.Y. Surface magnetoelectric effect in ferromagnetic metal films. Phys. Rev. Lett. 2008, 101, 137201. [Google Scholar] [CrossRef] [PubMed]

- Shiota, Y.; Miwa, S.; Nozaki, T.; Bonell, F.; Mizuochi, N.; Shinjo, T.; Kubota, H.; Yuasa, S.; Suzuki, Y. Pulse voltage-induced dynamic magnetization switching in magnetic tunneling junctions with high resistance-area product. Appl. Phys. Lett. 2012, 101, 102406. [Google Scholar] [CrossRef]

- Han, G.; Huang, J.; Chen, B.; Ter Lim, S.; Tran, M. Electric Field Assisted Switching in Magnetic Random Access Memory. IEEE Trans. Mag. 2015, 51, 1–7. [Google Scholar] [CrossRef]

- Alzate, J.G. Voltage-Controlled Magnetic Dynamics in Nanoscale Magnetic Tunnel Junctions. Ph.D. Thesis, University of California, Los Angeles, CA, USA, 2014. [Google Scholar]

- Grezes, C.; Ebrahimi, F.; Alzate, J.G.; Cai, X.; Katine, J.A.; Langer, J.; Ocker, B.; Khalili, A.P.; Wang, K.L. Ultra-low switching energy and scaling in electric-field-controlled nanoscale magnetic tunnel junctions with high resistance-area product. Appl. Phys. Lett. 2015, 108, 012403. [Google Scholar] [CrossRef]

- Kang, W.; Ran, Y.; Zhang, Y.; Lv, W.; Zhao, W. Modeling and Exploration of the Voltage-Controlled Magnetic Anisotropy Effect for the Next-Generation Low-Power and High-Speed MRAM Applications. IEEE Trans. Nanotechnol. 2017, 16, 387–395. [Google Scholar] [CrossRef]

- Wang, S.; Lee, H.; Li, T.; Ebrahimi, F.; Amiri, P.K.; Wang, K.L.; Gupta, P. Comparative Evaluation of Spin-Transfer-Torque and Magnetoelectric Random Access Memory. IEEE J. Emerg. Sel. Top. Circuits Syst. 2016, 6, 134–145. [Google Scholar] [CrossRef]

- Worledge, D.C.; Hu, G.; Abraham, D.W.; Sun, J.Z.; Trouilloud, P.L.; Nowak, J.; Brown, S.; Gaidis, M.C.; OSullivan, E.J.; Robertazzi, R.P. Spin torque switching of perpendicular Ta/CoFeB/MgO-based magnetic tunnel junctions. Appl. Phys. Lett. 2011, 98, 022501. [Google Scholar] [CrossRef]

- Ikeda, S.; Hayakawa, J.; Ashizawa, Y.; Lee, Y.M.; Miura, K.; Hasegawa, H.; Tsunoda, M.; Matsukura, F.; Ohno, H. Tunnel magnetoresistance of 604% at 300 K by suppression of ta diffusion in CoFeB/MgO/CoFeB pseudo-spin-valves annealed at high temperature. Appl. Phys. Lett. 2008, 93, 082508. [Google Scholar] [CrossRef]

- Hanyu, T.; Endoh, T.; Suzuki, D.; Koike, H.; Ma, Y.; Onizawa, N.; Natsui, M.; Ikeda, S.; Ohno, H. Standby-Power-Free Integrated Circuits Using MTJ-Based VLSI Computing. Proc. IEEE 2016, 104, 1844–1863. [Google Scholar] [CrossRef]

- Kang, W.; Zhang, L.; Klein, J.-O.; Zhang, Y.; Ravelosona, D.; Zhao, W. Reconfigurable codesign of STT-MRAM under process variations in deeply scaled technology. IEEE Trans. Electron Device 2015, 62, 1769–1777. [Google Scholar] [CrossRef]

- Cai, H.; Wang, Y.; Naviner, L.; Zhao, W. Multiplexing Sense-Amplifier-Based Magnetic Flip-Flop in a 28-nm FDSOI Technology. IEEE Trans. Nmanotechnol. 2015, 14, 761–767. [Google Scholar] [CrossRef]

- Cai, H.; Wang, Y.; Naviner, L.; Zhao, W. Novel Pulsed-Latch Replacement in Non-Volatile Flip-Flop Core. In Proceedings of the IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Bochum, Germany, 3–5 July 2017; pp. 57–61. [Google Scholar]

- Lee, H.; Alzate, J.G.; Dorrance, R.; Cai, X.Q.; Markovi, D.; Amiri, P.K.; Wang, K.L. Design of a fast and low-power sense amplifier and writing circuit for high-speed MRAM. IEEE Trans. Mag. 2015, 51, 1–7. [Google Scholar]

- Wang, Y.; Cai, H.; Naviner, L.; Zhang, Y.; Klein, J.-O.; Zhao, W. Compact thermal modeling of spin transfer torque magnetic tunnel junction. Microelectron. Rel. 2015, 55, 1649–1653. [Google Scholar] [CrossRef]

- Kang, W.; Li, Z.; Klein, J.-O.; Chen, Y.; Zhang, Y.; Ravelosona, D.; Chappert, C.; Zhao, W. Variation-tolerant and disturbance-free sensing circuit for deep nanometer STT-MRAM. IEEE. Trans. Nanotechnol. 2014, 13, 1088–1092. [Google Scholar] [CrossRef]

- Kang, W.; Zhang, L.; Zhao, W.; Klein, J.-O.; Zhang, Y.; Ravelosona, D.; Chappert, C. Yield and reliability improvement techniques for emerging nonvolatile STT-MRAM. IEEE J. Emerg. Sel. Top. Circuits Syst. 2015, 5, 28–39. [Google Scholar] [CrossRef]

- Cai, H.; Wang, Y.; Naviner, L.; Zhao, W. Low power magnetic flip-flop optimization with FDSOI technology boost. IEEE Trans. Mag. 2016, 52. [Google Scholar] [CrossRef]

- Cai, H.; Wang, Y.; Naviner, L.; Kang, W.; Zhao, W. Energy Efficient Magnetic Tunnel Junction Based Hybrid LSI Using Multi-Threshold UTBB-FD-SOI Device. In Proceedings of the Conference on Great Lakes Symposium on VLSI 2017 (GLSVLSI), Banff, AB, Canada, 10–12 May 2017; ACM: New York, NY, USA; pp. 23–28. [Google Scholar]

- Wang, K.L.; Lee, H.; Amiri, P.K. Magnetoelectric random access memory-based circuit design by using voltage-controlled magnetic anisotropy in magnetic tunnel junctions. IEEE Trans. Nanotechnol. 2015, 14, 992–997. [Google Scholar] [CrossRef]

- Devolder, T.; Hayakawa, J.; Ito, K.; Takahashi, H.; Ikeda, S.; Crozat, P.; Zerounian, N.; Kim, J.-V.; Chappert, C.; Ohno, H. Single-shot time-resolved measurements of nanosecond-scale spin-transfer induced switching: Stochastic versus deterministic aspects. Phys. Rev. Lett. 2008, 100, 057206. [Google Scholar] [CrossRef] [PubMed]

- De Castro, M.M.; Sousa, R.; Bandiera, S.; Ducruet, C.; Chavent, A.; Auffret, S.; Papusoi, C.; Prejbeanu, I.; Portemont, C.; Vila, L.; et al. Precessional spin-transfer switching in a magnetic tunnel junction with a synthetic antiferromagnetic perpendicular polarizer. J. Appl. Phys. 2012, 111, 07C912. [Google Scholar] [CrossRef]

- Wang, S.; Pal, S.; Li, T.; Pan, A.; Grezes, C.; Amiri, P.K.; Wang, K.L.; Gupta, P. Hybrid VC-MTJ/CMOS non-volatile stochastic logic for efficient computing. In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE), Lausanne, Switzerland, 27–31 March 2017; pp. 1438–1443. [Google Scholar]

- Wang, Y.; Cai, H.; Naviner, L.; Klein, J.O.; Yang, J.; Zhao, W. A novel circuit design of true random number generator using magnetic tunnel junction. In Proceedings of the 2016 IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH), Beijing, China, 18–20 July 2016; pp. 123–128. [Google Scholar]

- Qu, Y.; Han, J.; Cockburn, B.F.; Pedrycz, W.; Zhang, Y.; Zhao, W. A true random number generator based on parallel STT-MTJs. In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE), Lausanne, Switzerland, 27–31 March 2017; pp. 606–609. [Google Scholar]

- Cai, H.; Wang, Y.; Naviner, L.; Zhao, W. Robust Ultra-Low Power Non-Volatile Logic-in-Memory Circuits in FD-SOI Technology. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 847–857. [Google Scholar] [CrossRef]

- Cai, H.; Wang, Y.; Naviner, L.; Zhao, W. Breakdown Analysis of Magnetic Flip-Flop With 28-nm UTBB FDSOI Technology. IEEE Trans. Dev. Mater. Reliab. 2016, 16, 376–383. [Google Scholar] [CrossRef]

- Saliva, M.; Cacho, F.; Ndiaye, C.; Huard, V.; Angot, D.; Bravaix, A.; Anghel, L. Impact of gate oxide breakdown in logic gates from 28nm FDSOI CMOS technology. In Proceedings of the 2015 IEEE International Reliability Physics Symposium, Monterey, CA, USA, 19–23 April 2015. [Google Scholar]

- Wang, Y.; Cai, H.; Naviner, L.; Zhang, Y.; Zhao, X.; Deng, E.; Klein, J.-O.; Zhao, W. Compact Model of Dielectric Breakdown in Spin-Transfer Torque Magnetic Tunnel Junction. IEEE Trans. Electron Device 2016, 63, 1762–1767. [Google Scholar] [CrossRef]

- Zhao, W.; Moreau, M.; Deng, E.; Zhang, Y.; Portal, J.-M.; Klein, J.-O.; Bocquet, M.; Aziza, H.; Deleruyelle, D.; Muller, D.; et al. Synchronous Non-Volatile Logic Gate Design Based on Resistive Switching Memories. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 443–454. [Google Scholar] [CrossRef]

| Memory | SRAM | DRAM | NOR-Flash | NAND-flash | STT-MRAM | PCRAM | ReRAM | FeRAM 1 |

|---|---|---|---|---|---|---|---|---|

| Cell area | >100 F2 | 6 F2 | 10 F2 | 4 F2 (3D) | 6∼50 F2 | 4∼30 F2 | 4∼12 F2 | 15∼35 F2 |

| Multi bit | 1 | 1 | 2 | 3 | 1 | 2 | 2 | 1 |

| Supply | <1 V | <1 V | >10 V | >10 V | <1.5 V | <3 V | <3 V | <1.8 V |

| Read duration | ∼1 ns | ∼10 ns | ∼50 ns | ∼10 µs | <10 ns | <10 ns | <10 ns | <10 ns |

| Write latency | ∼1 ns | ∼10 ns | 10 µs–1 ms | 100 µs–1 ms | <10 ns | ∼50 ns | <10 ns | <5 ns |

| Retention | N/A | ∼64 ms | >10 y | >10 y | >10 y | >10 y | >10 y | >10 y |

| Endurance | >1016 | >1016 | >105 | >104 | >1015 | >109 | 106∼1012 | 1013 |

| Write energy | ∼fJ/bit | ∼10 fJ/bit | ∼100 pJ/bit | ∼10 fJ/bit | ∼0.1pJ/bit | ∼10 pJ/bit | ∼0.1 pJ/bit | ∼10 fJ/bit |

| Parameter | Description | STT-MTJ | VCMA-MTJ |

|---|---|---|---|

| TMR | Tunnel magnetoresistance ratio | 150% | 100% |

| Tox | MTJ oxide barrier thickness | 0.7 nm | 1.3 nm |

| Rp, Rap | MTJ resistance | 5 kΩ/12.5 kΩ | 100 kΩ/200 kΩ |

| TFL | Free layer thickness | 1.2 nm | 1.19 nm |

| z | Thermal stability | 71.6 | 73.7 |

| Area | MTJ layout surface | 24 F2 | 12 F2 |

| W/L | Access transistor width/length 1 | 300 nm/30 nm | 80 nm/30 nm |

| Design specification | [39] | [26] | [25] | This Work |

|---|---|---|---|---|

| Technology node | 32 nm CMOS 1 | 32 nm CMOS | 40 nm CMOS | 28 nm FD-SOI |

| Switching delay | 1–10 ns | 1.42 ns | 0.45 ns | 0.52 ns |

| Dynamic energy | ~100 fJ/bit | 10.1 fJ/bit | 6.14 fJ/bit | 3.18 fJ/bit |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cai, H.; Kang, W.; Wang, Y.; Naviner, L.A.D.B.; Yang, J.; Zhao, W. High Performance MRAM with Spin-Transfer-Torque and Voltage-Controlled Magnetic Anisotropy Effects. Appl. Sci. 2017, 7, 929. https://doi.org/10.3390/app7090929

Cai H, Kang W, Wang Y, Naviner LADB, Yang J, Zhao W. High Performance MRAM with Spin-Transfer-Torque and Voltage-Controlled Magnetic Anisotropy Effects. Applied Sciences. 2017; 7(9):929. https://doi.org/10.3390/app7090929

Chicago/Turabian StyleCai, Hao, Wang Kang, You Wang, Lirida Alves De Barros Naviner, Jun Yang, and Weisheng Zhao. 2017. "High Performance MRAM with Spin-Transfer-Torque and Voltage-Controlled Magnetic Anisotropy Effects" Applied Sciences 7, no. 9: 929. https://doi.org/10.3390/app7090929

APA StyleCai, H., Kang, W., Wang, Y., Naviner, L. A. D. B., Yang, J., & Zhao, W. (2017). High Performance MRAM with Spin-Transfer-Torque and Voltage-Controlled Magnetic Anisotropy Effects. Applied Sciences, 7(9), 929. https://doi.org/10.3390/app7090929