Analog Gaussian-Shaped Filter Design and Current Mode Compensation for Dot-Matrix TSP Readout Systems

Abstract

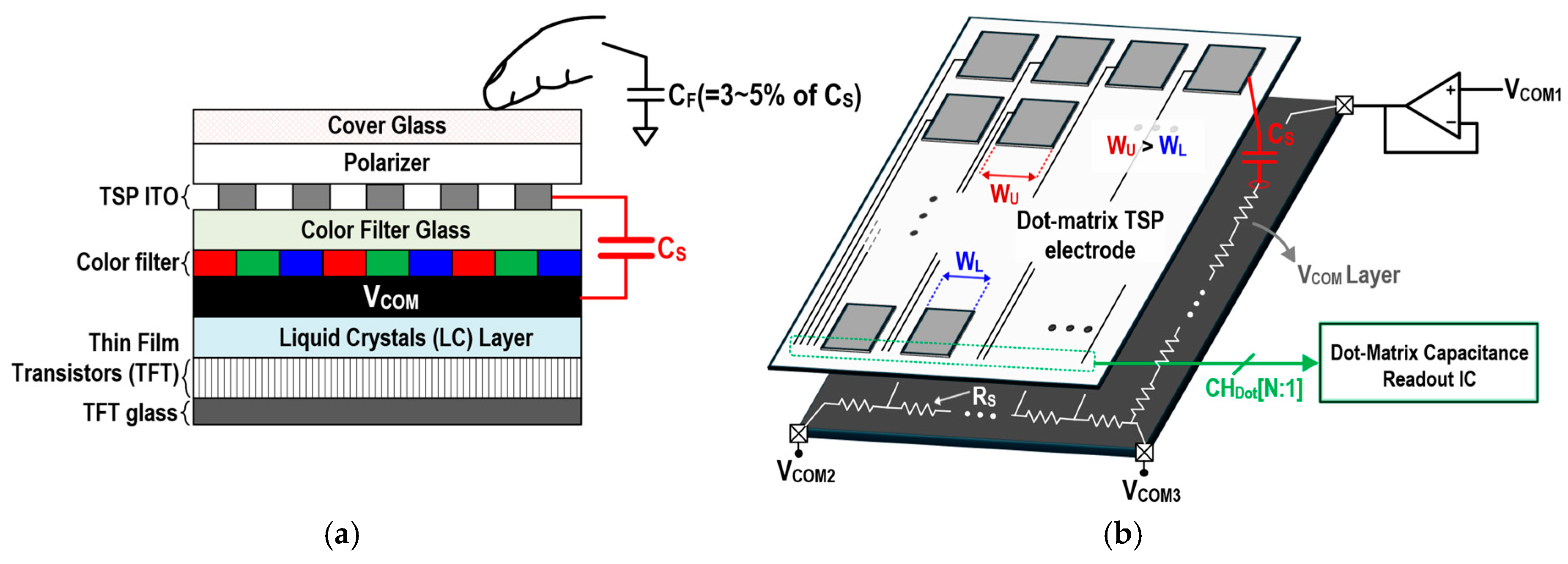

1. Introduction

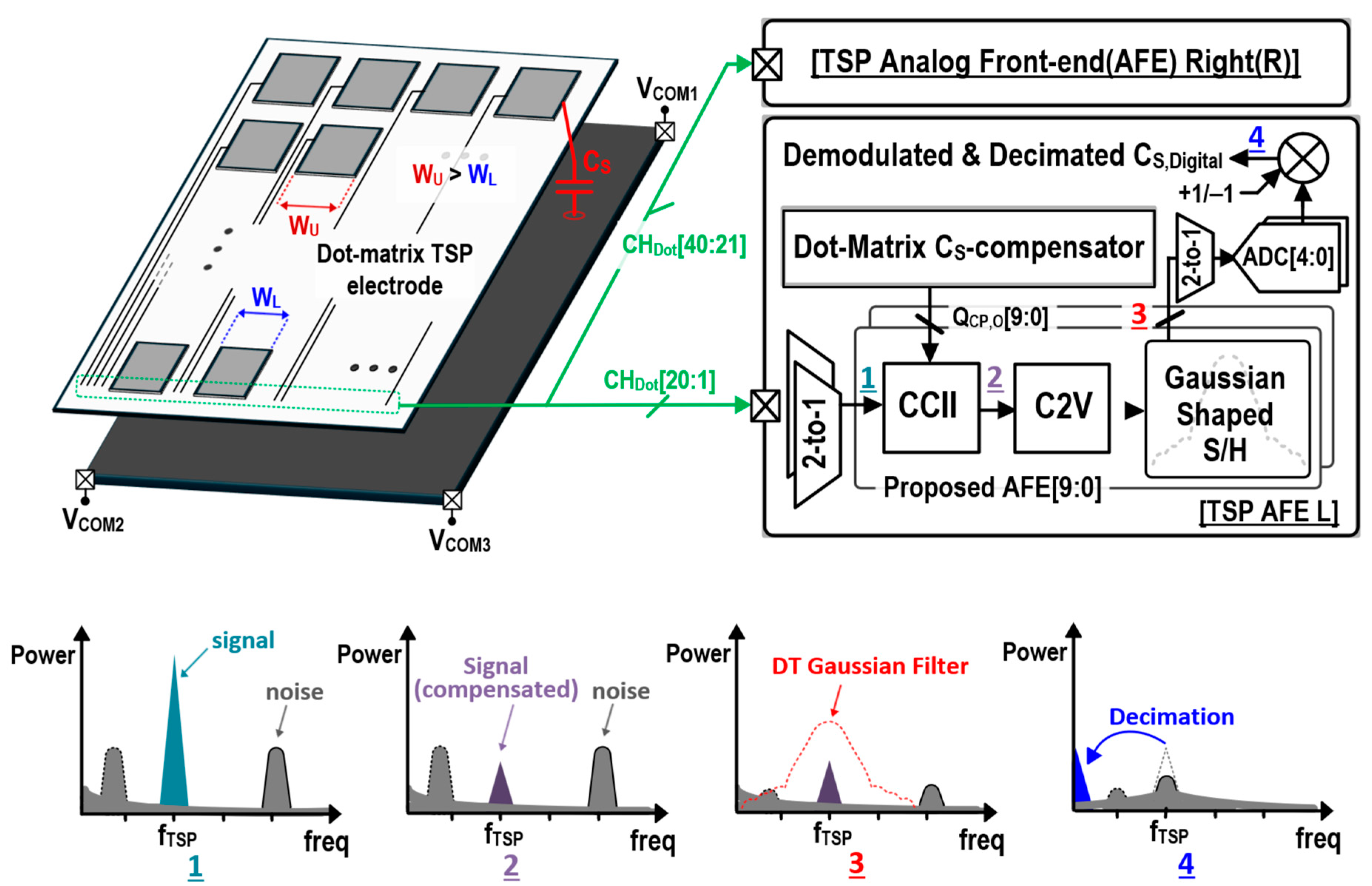

2. Proposed TSP Readout System

2.1. Whole System Architecture

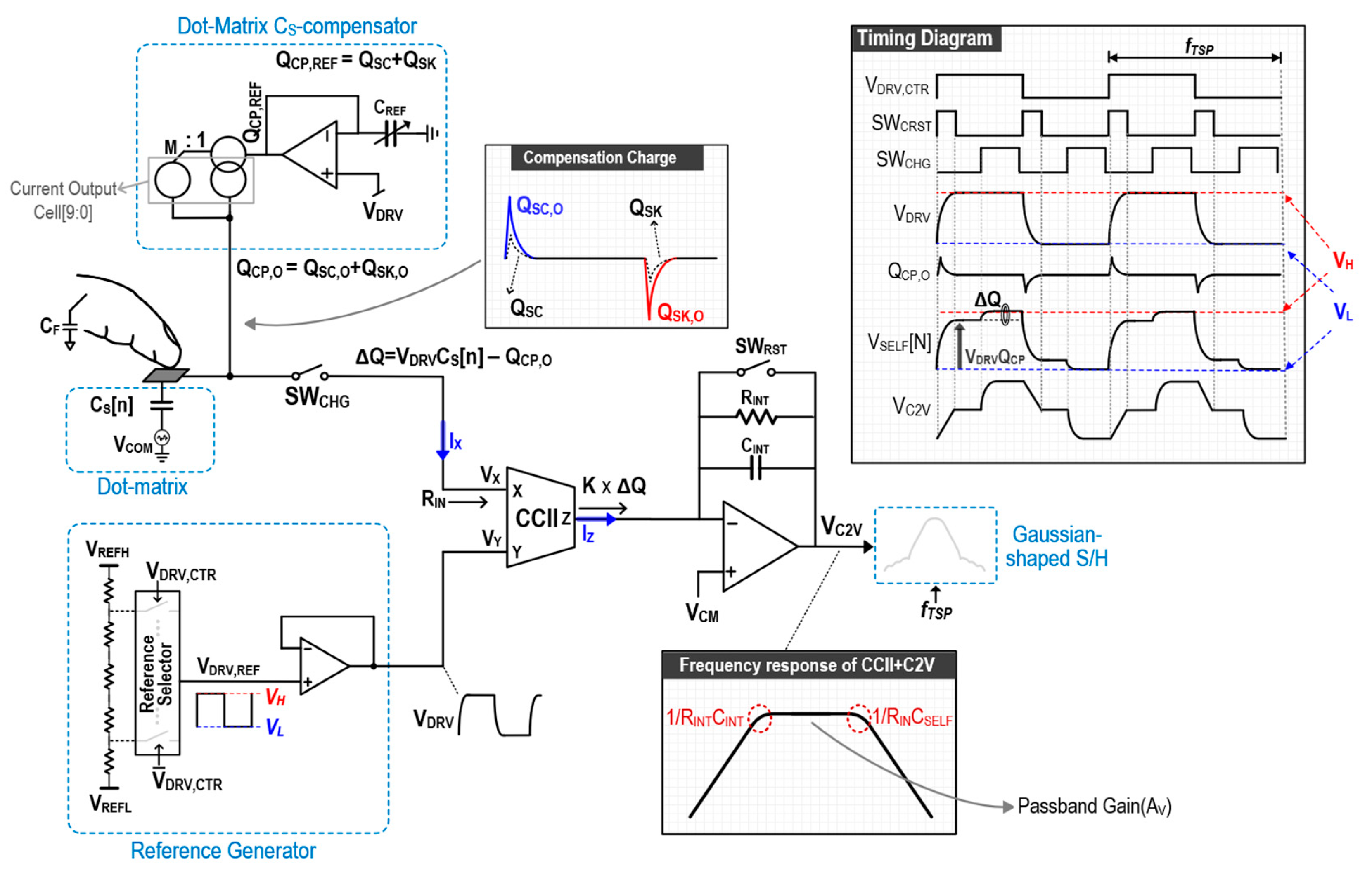

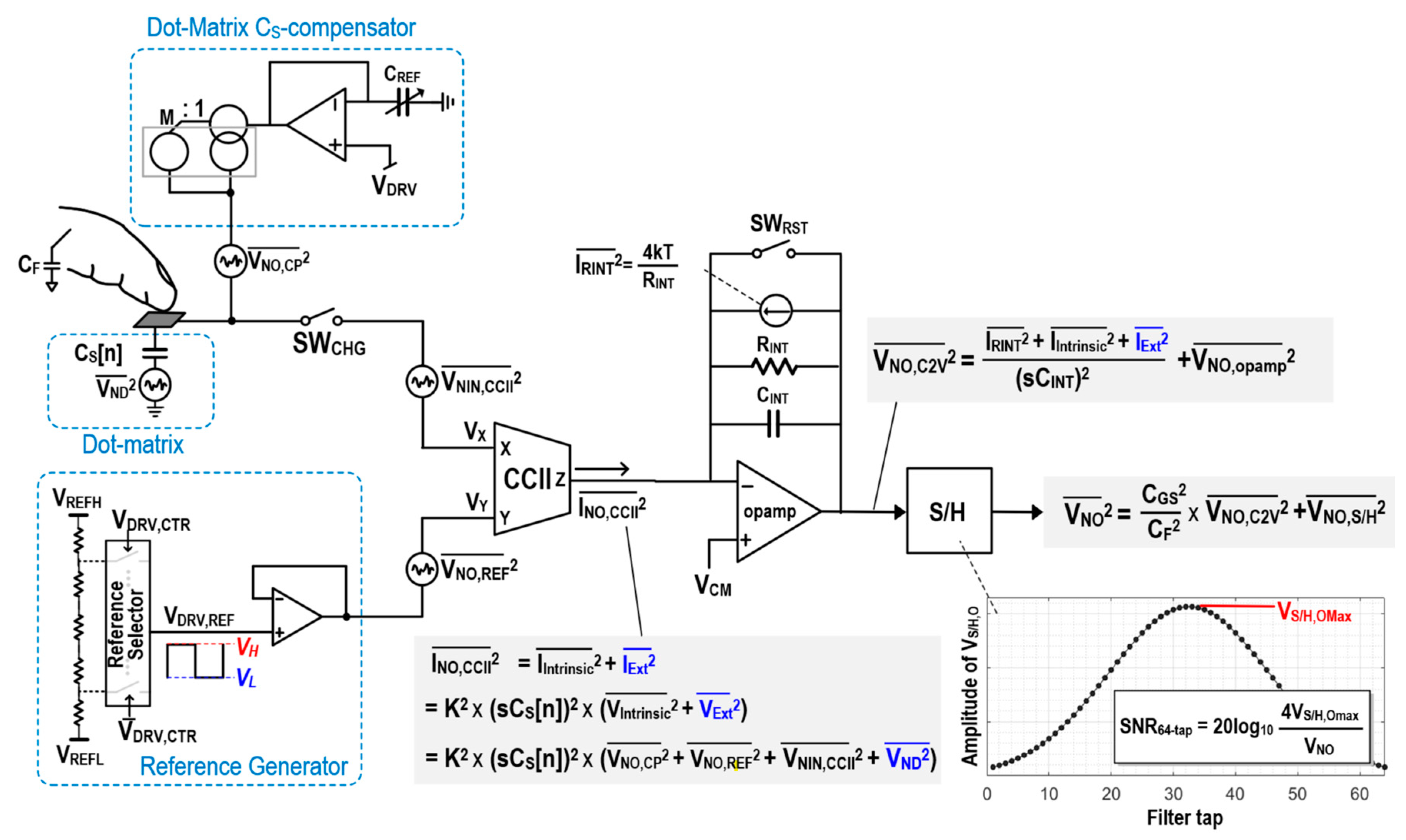

2.2. Sensing Front-End

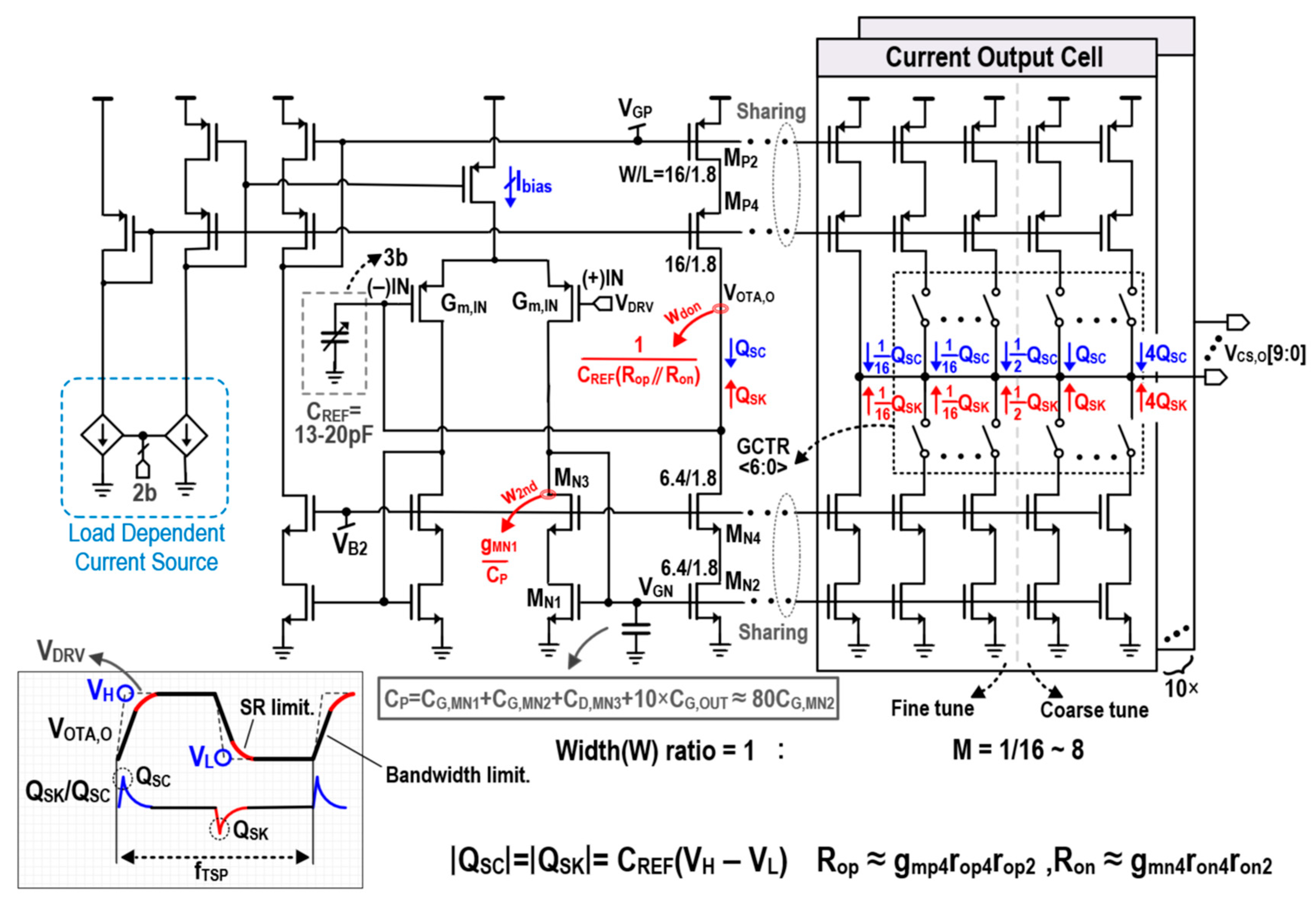

2.3. Dot-Matrix CS-Compensator

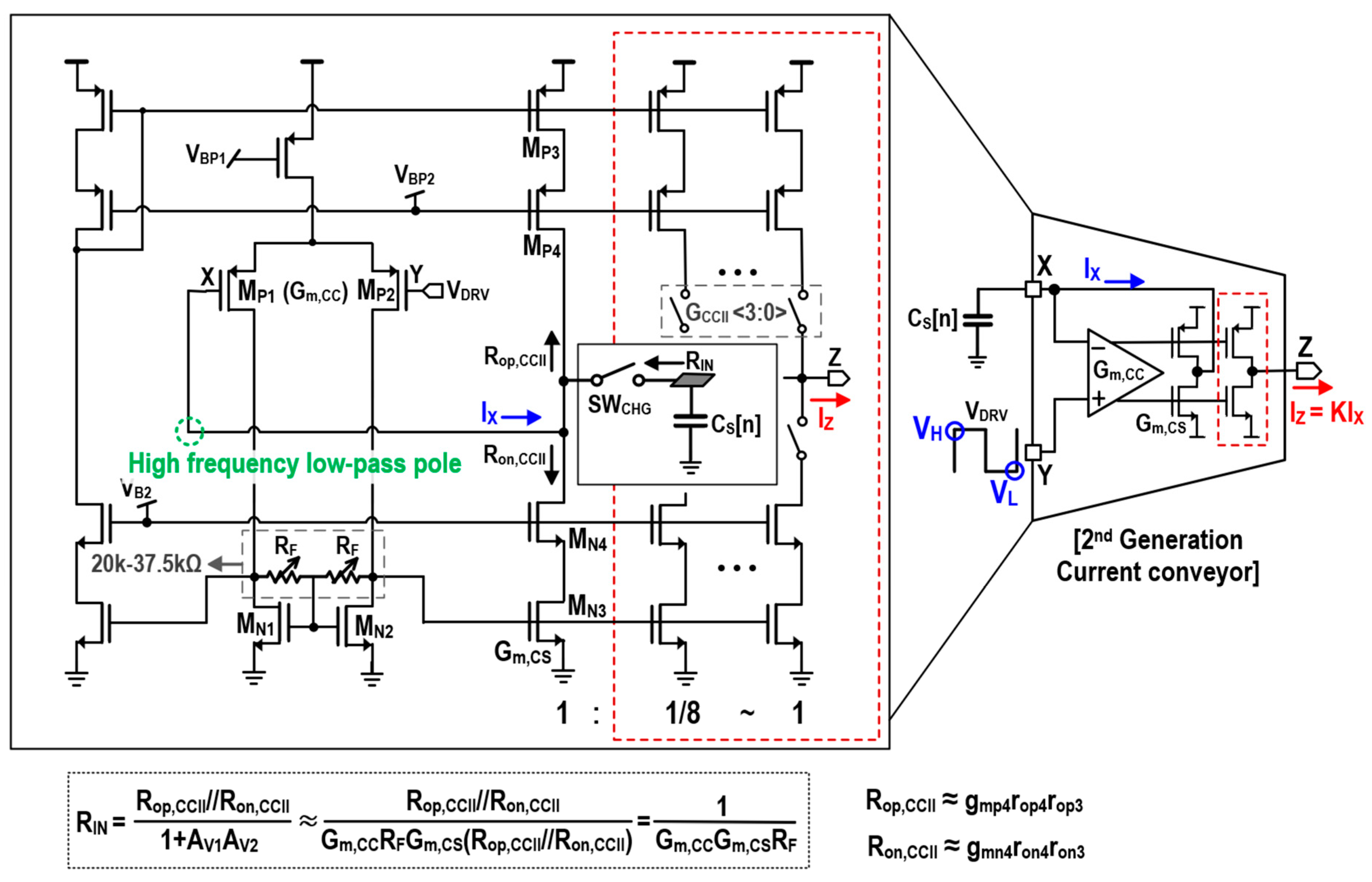

2.4. Proposed Second-Generation Current Conveyor (CCII)

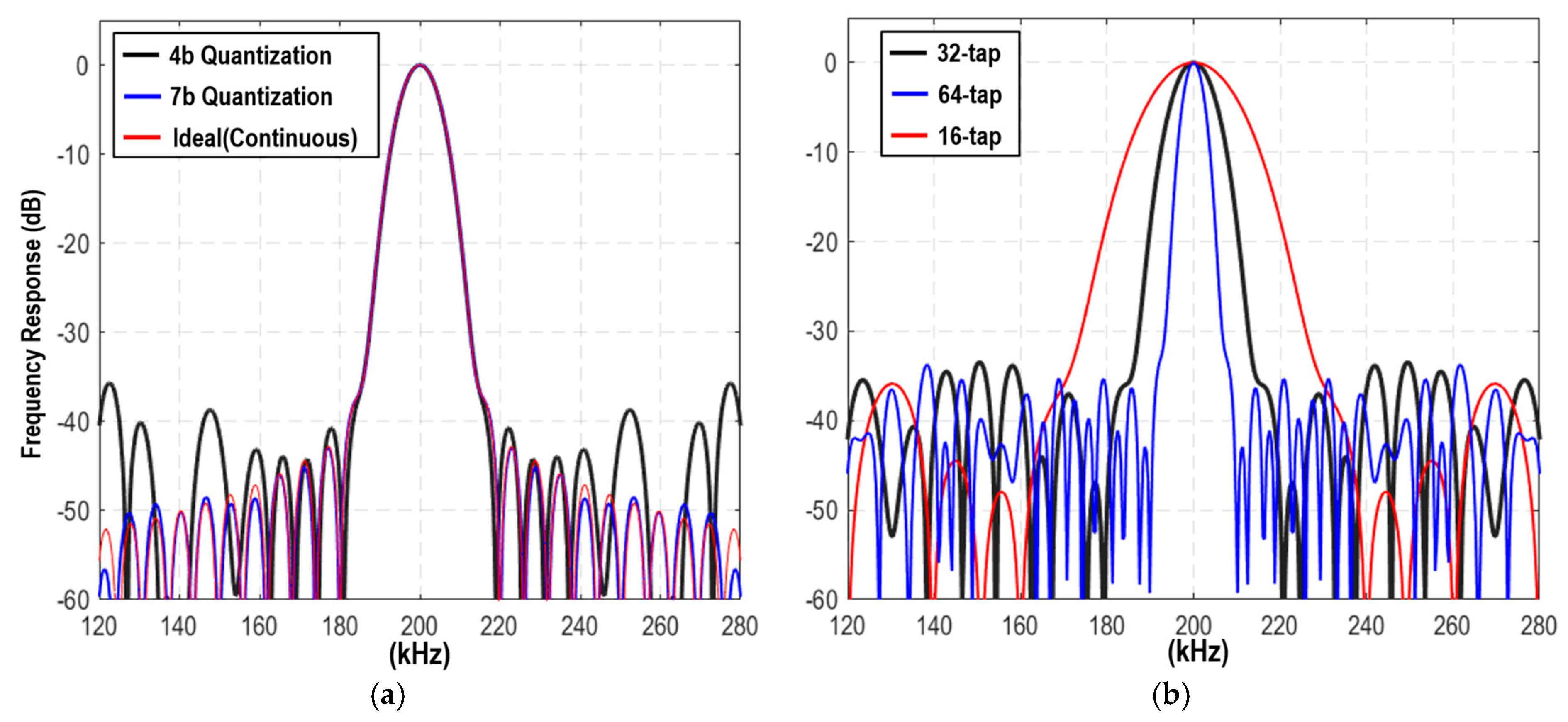

2.5. Sensing Back-End

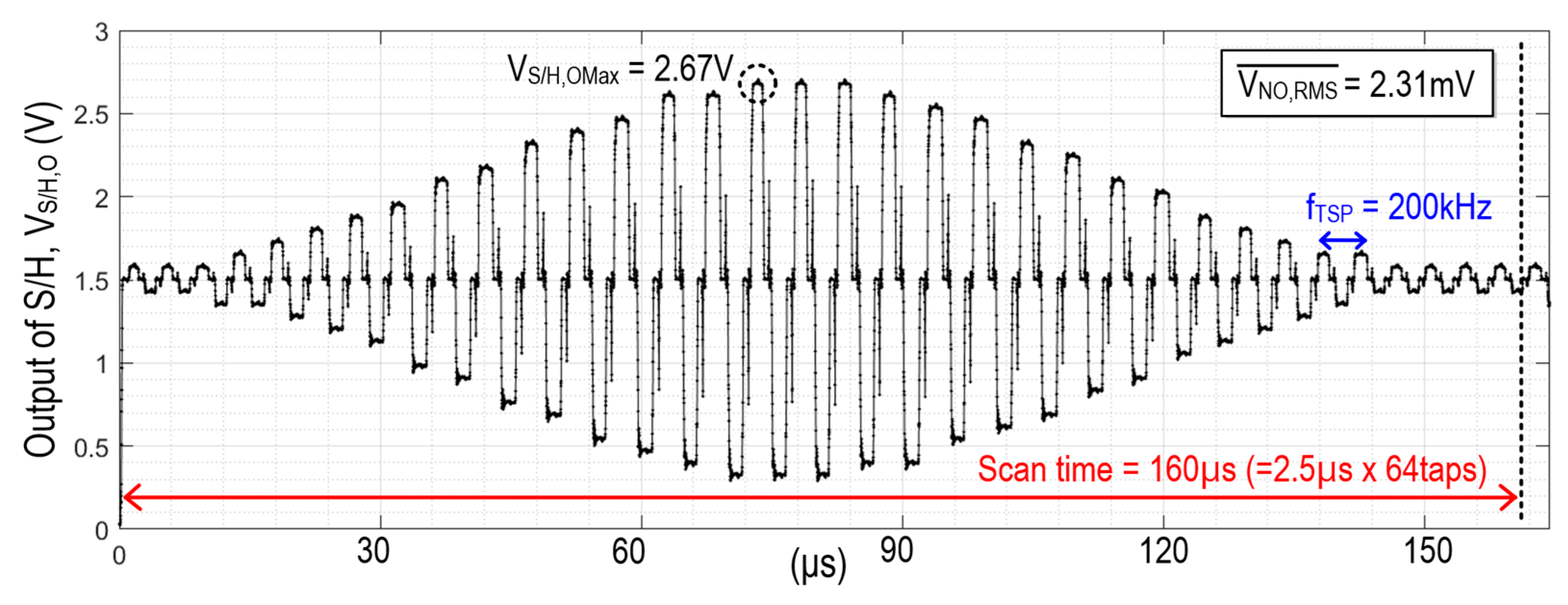

3. Simulation Results

4. Conclusions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Kim, K.D.; Byun, S.H.; Choi, Y.K.; Baek, J.H.; Cho, H.H.; Park, J.K.; Ahn, H.Y.; Lee, C.J.; Cho, M.S.; Lee, J.H.; et al. A Capacitive Touch Controller Robust to Display Noise for Ultrathin Touch Screen Displays. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012. [Google Scholar]

- Seo, J.; Nam, H. Low power and low noise shift register for in-cell touch display applications. IEEE J. Electron. Devices Soc. 2018, 6, 726–732. [Google Scholar] [CrossRef]

- Kim, C.; Lee, D.S.; Kim, J.H.; Kim, H.B.; Shin, S.R.; Jung, J.H.; Song, I.H.; Jang, C.S.; Kwon, K.S.; Kim, S.H.; et al. Advanced In-cell Touch Technology for Large Sized Liquid Crystal Displays. Dig. Tech. Pap. Int. Symp. SID 2015, 46, 895–898. [Google Scholar] [CrossRef]

- Lee, S.H.; An, J.S.; Hong, S.K.; Kwon, O.K. In-cell Capacitive Touch Panel Structures and Their Readout Circuits. In Proceedings of the International Workshop on Active-Matrix Flat panel Displays and Devices, Kyoto, Japan, 6–8 July 2016; pp. 258–261. [Google Scholar]

- Byun, S.H.; Lee, H.; Song, T.G.; Lee, J.; Baek, J.; Ha, G.; Baek, S.; Kim, Y.; Jung, W.G.; Lim, H.W.; et al. A 45.8 dB-SNR 120 fps 100 pF-Load Self-Capacitance Touch-Screen Controller with Enhanced In-Band Common Noise Immunity Using Noise Antenna Reference. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2023. [Google Scholar]

- An, J.Y.; Choi, S.H.; Kim, S.W.; Lee, J.Y.; Lee, H.M.; Choi, Y.K. Noise Immunity in Capacitive Sensing: Single-Ended AFE Design with Common-Current Subtraction for Mutual- and Self-Capacitance Sensing in 390pF Load. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2024. [Google Scholar]

- Lee, J.; Ham, J.; Lee, H.; Jang, W.; Kim, H.; So, B.; Ko, S. A 620 pF-Compensated Dual-Mode Capacitance Readout IC for Sub-Display TSP with VRR Scan. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 18–22 February 2024. [Google Scholar]

- Yang, J.-H. A highly noise-immune touch controller using filtered-delta-integration and a charge-interpolation technique for 10.1-inch capacitive touch-screen panels. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2013. [Google Scholar]

- Shin, H.; Ko, S.; Jang, H.; Yun, I.; Lee, K. A 55 dB SNR with 240Hz frame scan rate mutual capacitor 30 × 24 touch-screen panel read-out IC using code-division multiple sensing technique. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2013. [Google Scholar]

- Park, J.E.; Lim, D.H.; Jeong, D.K. A reconfigurable 40-to-67 dB SNR, 50-to-6400 Hz frame-rate, column-parallel readout IC for capacitive touch-screen panels. IEEE J. Solid-State Circuits 2014, 49, 2305–2318. [Google Scholar] [CrossRef]

- Kim, K.D.; Kang, S.; Choi, Y.K.; Lee, K.H.; Lee, C.H.; Lee, J.C.; Choi, M.; Ko, K.; Jung, J.; Park, N.; et al. A fully-differential capacitive touch controller with input common-mode feedback for symmetric display noise cancellation. In Proceedings of the 2014 Symposium on VLSI Circuits Digest of Technical Papers, Honolulu, HI, USA, 10–13 June 2014. [Google Scholar]

- SAMSUNG Display, Samsung Display Commercializes New, Variable Refresh Rate Technology for Increasing Smartphone Power Savings. Available online: https://news.samsung.com/us/samsung-display-commercializes-new-variable-refresh-rate-technology-for-increasing-smartphone-power-savings-galaxy-note20/?utm_source=chatgpt.com (accessed on 26 December 2024).

- Hotelling, S.; Christie, I.; Chaudhri, I. Multipoint Touch Surface Controller. U.S. Patent 8,279,180, 2 October 2012. Available online: https://patents.google.com/patent/US8279180B2/en (accessed on 26 December 2024).

- Hwang, H.; Lee, H.; Han, M.; Kim, H.; Chae, Y. A 1.8-V 6.9-mW 120-fps 50-Channel Capacitive Touch Readout with Current Conveyor AFE and Current-Driven ΔΣ ADC. IEEE J. Solid-State Circuits 2017, 53, 204–218. [Google Scholar] [CrossRef]

- Ko, S.H.; Yang, B.D. An Ultra-Compact Low Power Self-Capacitive Touch Screen Readout IC Embedding Reconfigurable Noise Immunity and Current-Driven Capacitance Compensation. IEEE Trans. Circuits Syst. II Express Briefs 2018, 66, 1321–1325. [Google Scholar] [CrossRef]

- Lee, J.; Ham, J.; Jang, W.; Lee, H.; Oh, J.; Goo, S.; Ko, S. A 145 − μW Always-on Touch Screen Readout and Always-on Haptic Driver IC for 1.26-Inch Circular Display of Wearable Device. In Proceedings of the 2023 IEEE SENSORS, Vienna, Austria, 29 October–1 November 2023. [Google Scholar]

- Kumar, S.; Kumar, N. Analysis of CMOS Second Generation Current Conveyors. Int. J. Eng. Res. Technol. 2014, 3, 947–953. [Google Scholar]

- Singh, P.; Sharma, A. A New CMOS Design and Analysis of Current Conveyor Second Generation (CCII). Int. J. Sci. Res. 2021, 6, 42–48. [Google Scholar]

- Minaei, S.; Yuce, E. New CMOS Current-Controlled Second Generation Current Conveyors. IEEE Trans. Circuits Syst. II Exp. Briefs 2008, 55, 1265–1269. [Google Scholar]

- Rathod, N.; Sharma, A. Design and Implementation of Different Generations of Current Conveyor Using 100 nm CMOS Technology. Int. J. Res. Dev. Eng. Technol. 2021, 2, 214–221. [Google Scholar]

- Park, S.H.; Kim, H.S.; Bang, J.S.; Cho, G.H.; Cho, G.H. A 0.26-nJ/node, 400-kHz Tx driving, filtered fully differential readout IC with parasitic RC time delay reduction technique for 65-in 169 97 capacitive-type touch screen panel. IEEE J. Solid-State Circuits 2017, 52, 528–542. [Google Scholar] [CrossRef]

- Jang, H.; Shin, H.; Lee, J.; Yoo, C.; Chun, K.; Yun, I. A 51 dB SNR 120 Hz Scan Rate 32 × 18 Segmented-VCOM LCD In Cell Touch-Display-Driver IC with 96-Channel Compact Shunt-Sensing Self-Capacitance Analog Front-End. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 16–20 February 2020. [Google Scholar]

- Lee, H.; Ham, J.; Lee, J.; Jang, W.; Ko, S. A 620-pF-Compensated Dual-Mode Capacitance Readout IC for Subdisplay Panel Applications. IEEE Solid-State Circuits Lett. 2024, 7, 195–198. [Google Scholar] [CrossRef]

| This Work | [5] | [15] | [22] | [23] | |

|---|---|---|---|---|---|

| Process | 350 nm CMOS | 1.1 V/3.3 V/8 V/20 V 45 nm | 130 nm/350 nm CMOS | 1.2 V/6 V/32 V 80 nm | 130 nm/350 nm CMOS |

| Capacitance | Dot-matrix self-capacitance | Dot-matrix self-capacitance | Dot-matrix self-capacitance | Dot-matrix self-capacitance | 2-layered self- and mutual capacitance |

| Electrode | 40 dots | N/A | 16 | 576 dots | 37 |

| Sensor | 40 | 216 | 16 | 96 | 37 |

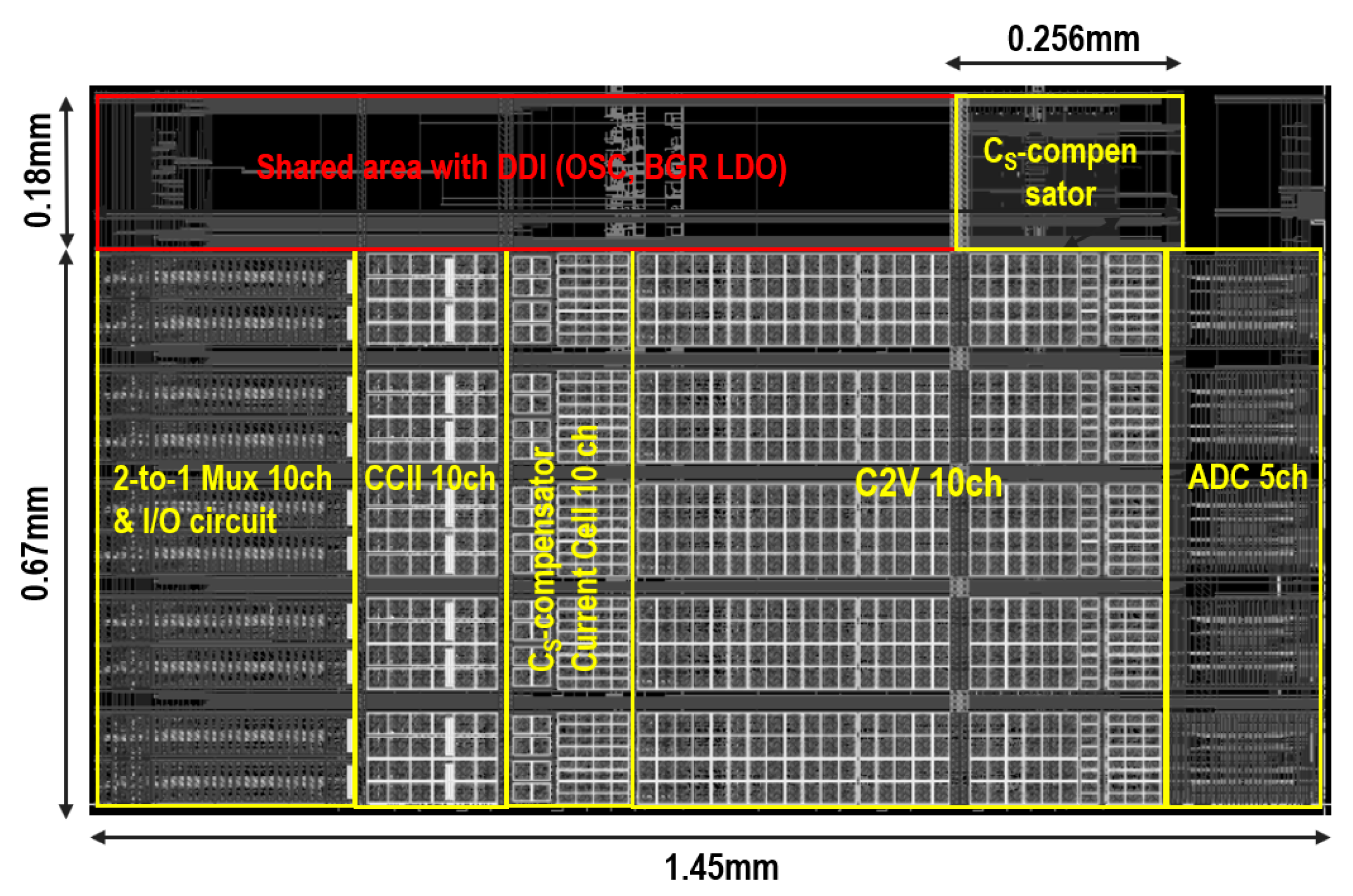

| AFE Area | 1.017 mm2 × 2 | 27.7 mm2 | 0.128 mm2 | 5 mm2 | 2.81 mm2 |

| AFE Area/Sensor | 0.05 mm2 | 0.12 mm2 | 0.08 mm2 | 0.05 mm2 | 0.086 mm2 |

| Power | 24 mW | 166 mW | 1.04 mW | 16 mW | 22.4 mW |

| Supply | 3.3 V | 1.1 V/3.3 V/5 V/6.6 V | 3.3 V | 1.2 V/6 V/32 V | 3.3 V |

| Scan Rate | 3.125 kHz | 120 Hz | 330 Hz | 120 Hz | 1.05 kHz for CS |

| Noise-removing scheme | Discrete-time Gaussian filter + BPF | Noise antenna reference | Moving average + pseudo-random spreading of orthogonal driving | Moving average scheme | Noise-monitoring scheme |

| SNR | 66 dB/1 pF (simulation) (1) | 45.8 dB/500 fF | 47.2 dB | 36.1 dB for 340 pF CS |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ko, S. Analog Gaussian-Shaped Filter Design and Current Mode Compensation for Dot-Matrix TSP Readout Systems. Appl. Sci. 2025, 15, 1845. https://doi.org/10.3390/app15041845

Ko S. Analog Gaussian-Shaped Filter Design and Current Mode Compensation for Dot-Matrix TSP Readout Systems. Applied Sciences. 2025; 15(4):1845. https://doi.org/10.3390/app15041845

Chicago/Turabian StyleKo, Seunghoon. 2025. "Analog Gaussian-Shaped Filter Design and Current Mode Compensation for Dot-Matrix TSP Readout Systems" Applied Sciences 15, no. 4: 1845. https://doi.org/10.3390/app15041845

APA StyleKo, S. (2025). Analog Gaussian-Shaped Filter Design and Current Mode Compensation for Dot-Matrix TSP Readout Systems. Applied Sciences, 15(4), 1845. https://doi.org/10.3390/app15041845