Design Assessment of Power Supply Systems for Divertor Coils in the Divertor Tokamak Test

Abstract

1. Introduction

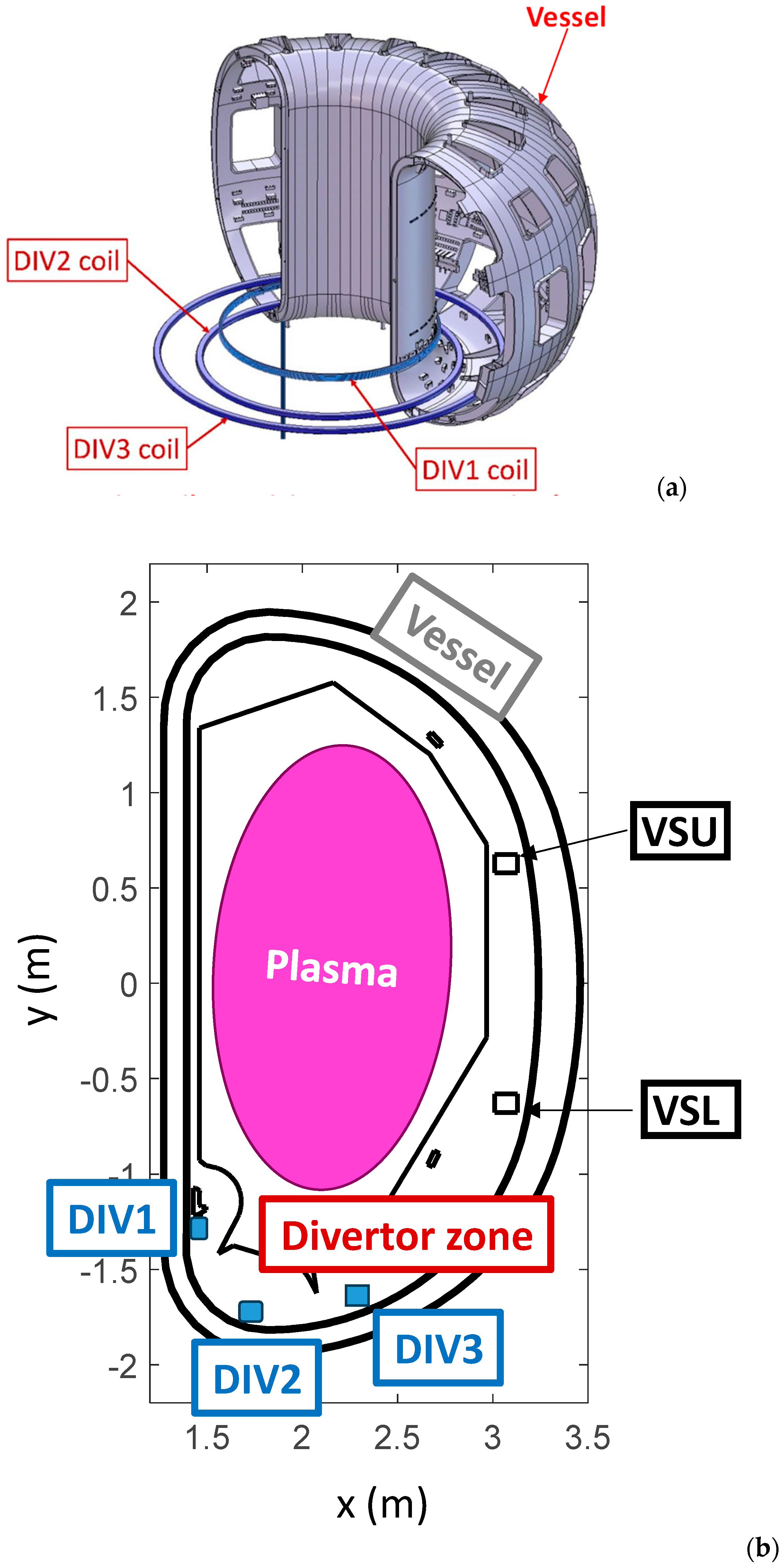

2. Overview of the DIV Coils System

2.1. Components of the DTT Magnet System

- Toroidal Field (TF) Coils: Generate the primary toroidal magnetic field.

- Poloidal Field (PF) Coils: Control plasma shape, position, and stability.

- Central Solenoid (CS): Induces the plasma current.

- Vertical Stability (VS) Coils: Provide fast vertical stabilization and radial control of the plasma.

- Divertor (DIV) Coils: Offer fine-tuning of the magnetic field in the divertor region for heat exhaust management and advanced divertor configurations.

- Non-Axisymmetric (NA) Coils: Could be used for advanced plasma control, such as Edge Localized Mode (ELM) mitigation.

2.2. Characteristics of the DIV Coils

- Even though a high number of DIV coils could increase the degrees of freedom in field shaping, a trade-off must be identified due to the space constraints in the divertor region and to the mechanical loads. In fact, the DIV4 coil and the further separated turns in the DIV1 coil, present in the previous designs, were removed, as the simulations showed a limited improvement in plasma interaction with respect to the assumed configuration [17].

- The static spread of the plasma impinging on the divertor plates may not be sufficient to achieve safe thermal loads. Therefore, strike-point sweeping (wobbling) is proposed as a strategy to further reduce them [18]. It consists of enlarging the affected area by imposing a periodic movement of the plasma at a desired frequency without significant changes of the plasma boundary. For the most probable and investigated configurations, the effect is significant up to 10 Hz, with an expected optimization around 4 Hz [17].

- As the DIV coils are placed inside the vessel, unexpected plasma instabilities, in particular those classified as plasma disruptions, can produce high induced currents in the DIV circuits [17]. In practice, such disruptions are a relevant driver for coil and PS design. Even though several solutions were studied to address this problem [19], the protection solution identified for DTT consisted in inserting additional inductances in each DIV circuit that will be in series with the original load coil [17].

- Maximum DIV coil current Imax = 5.5 kA.

- DIV coils required voltage 500 V (DIV1, DIV2); 1700 V (DIV3).

- 4-quadrant operation.

- Maximum required bandwidth of current control is below 10 Hz (typical value 4 Hz).

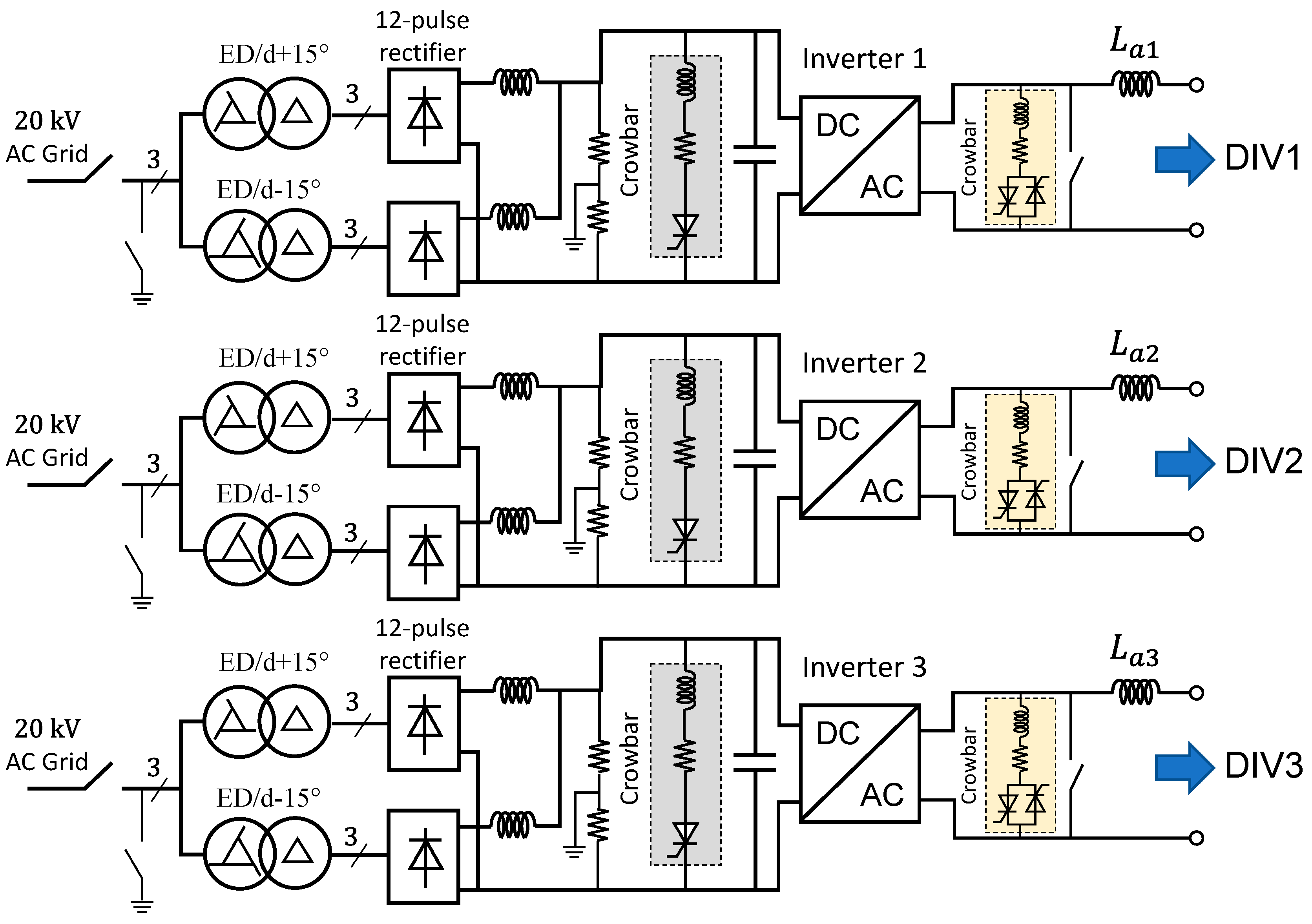

3. DIV Coil Power Supply Arrangement

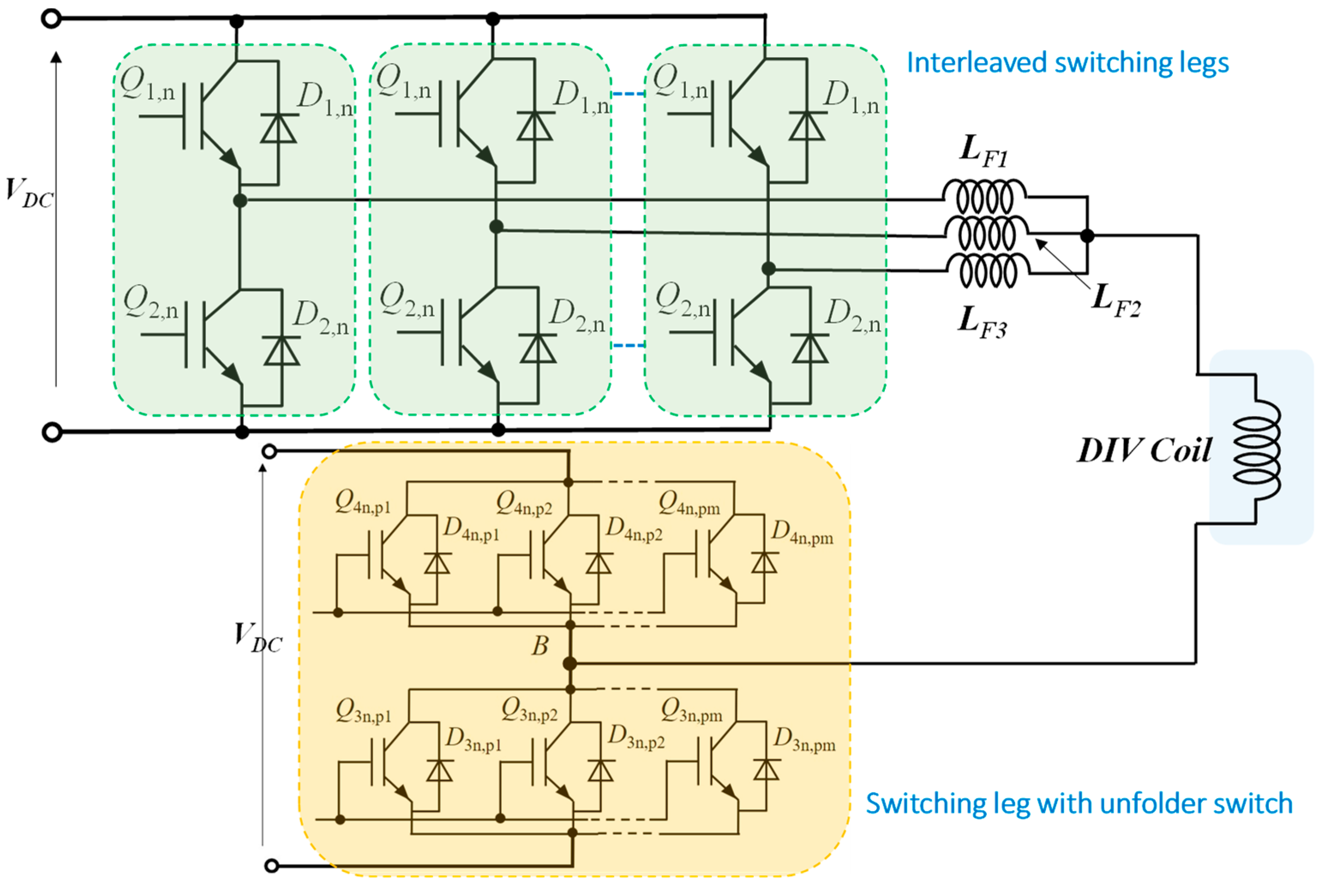

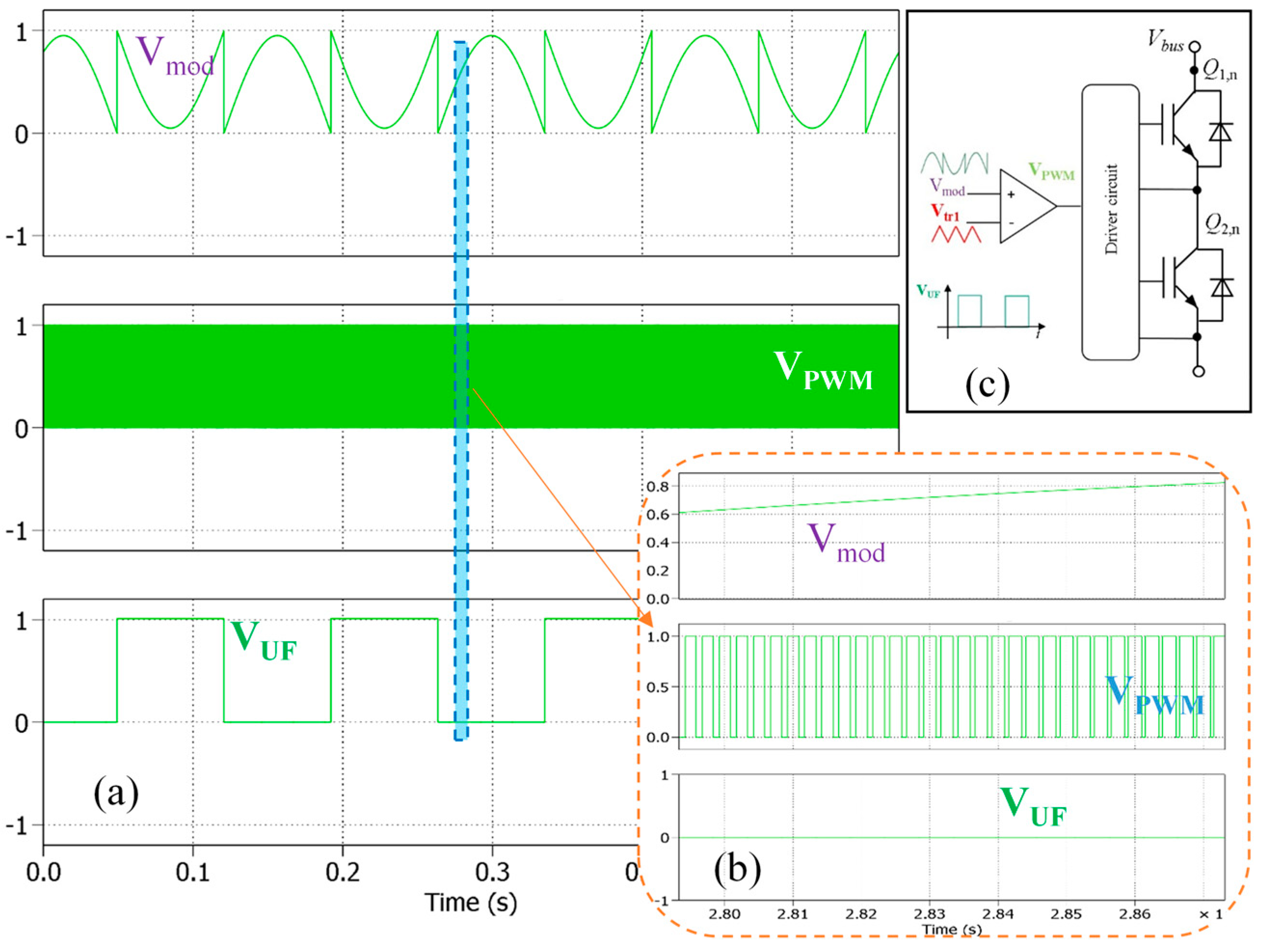

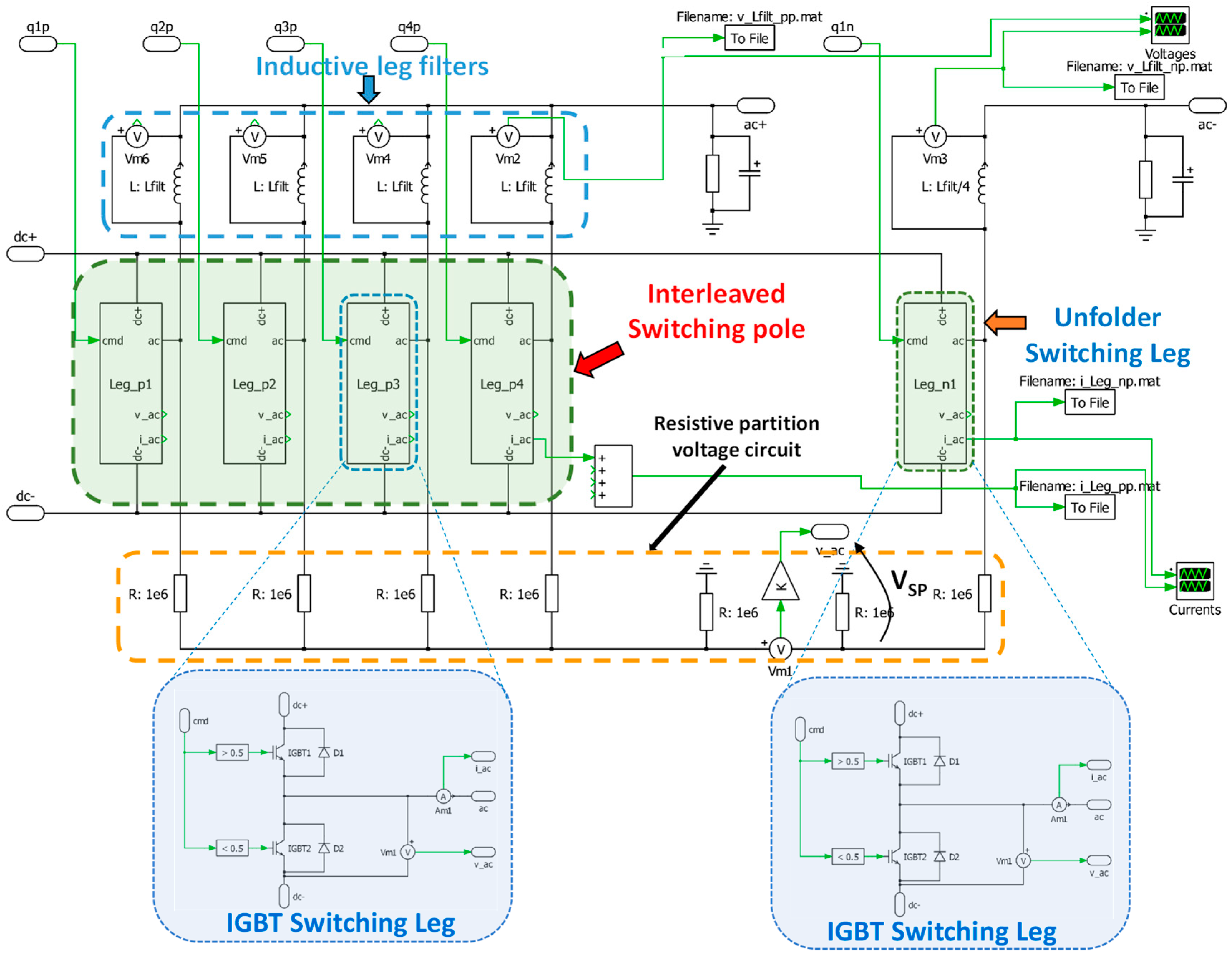

3.1. Full-Bridge IGBT-Based Solution

- Single phase DC/AC converter using IGBT technology to supply the DIV coils through additional inductors that are needed to limit the current in case of disruption. The IGBT technology allows very low response times to be obtained with respect to SCR technology. Having low response times is crucial in case of disruption, where the converter must be turned off quickly.

- Crowbars for protection both on the DC link (discharge breaker) and at the output of the DC/AC converter.

Inverter IGBT Selection

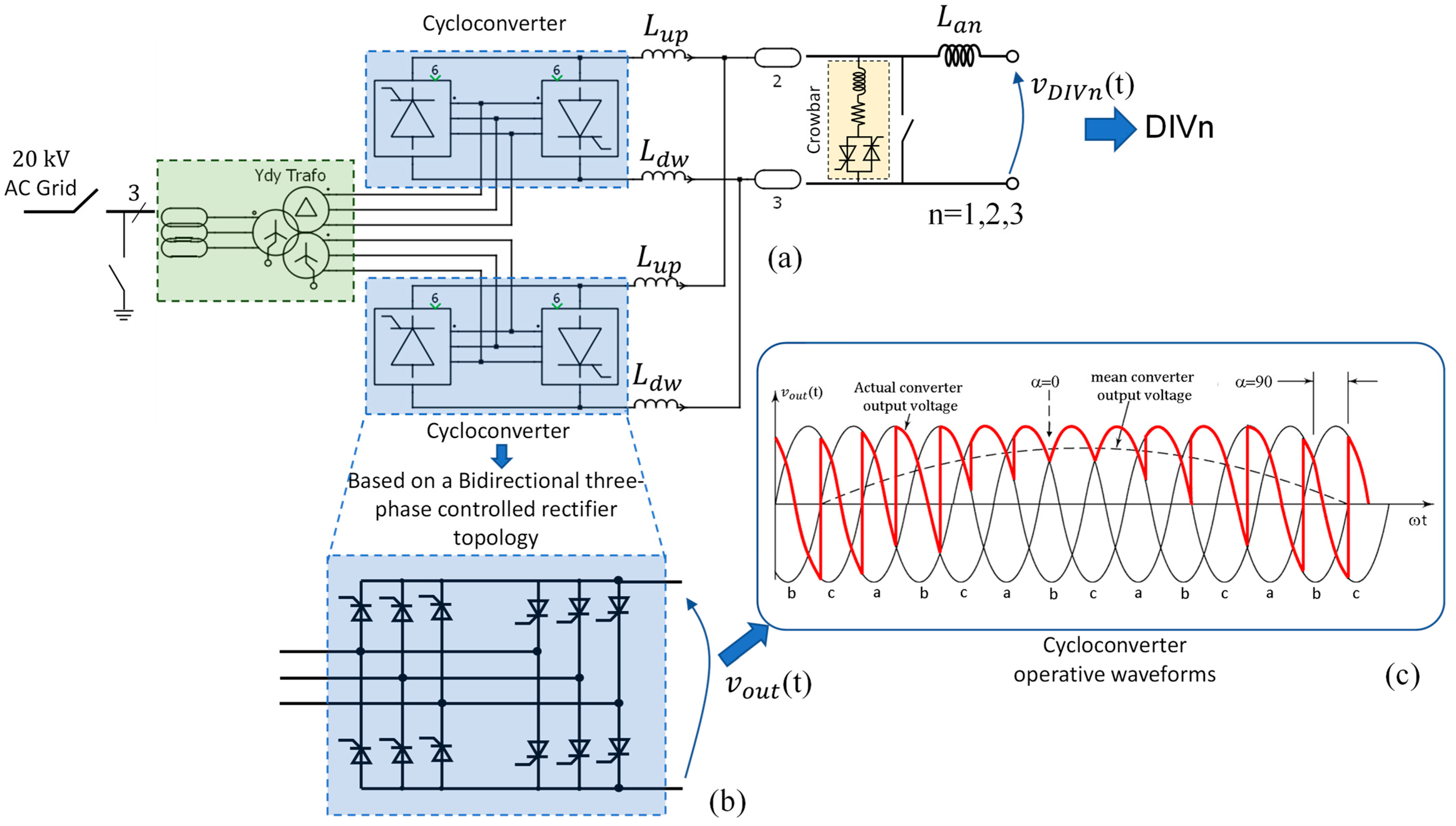

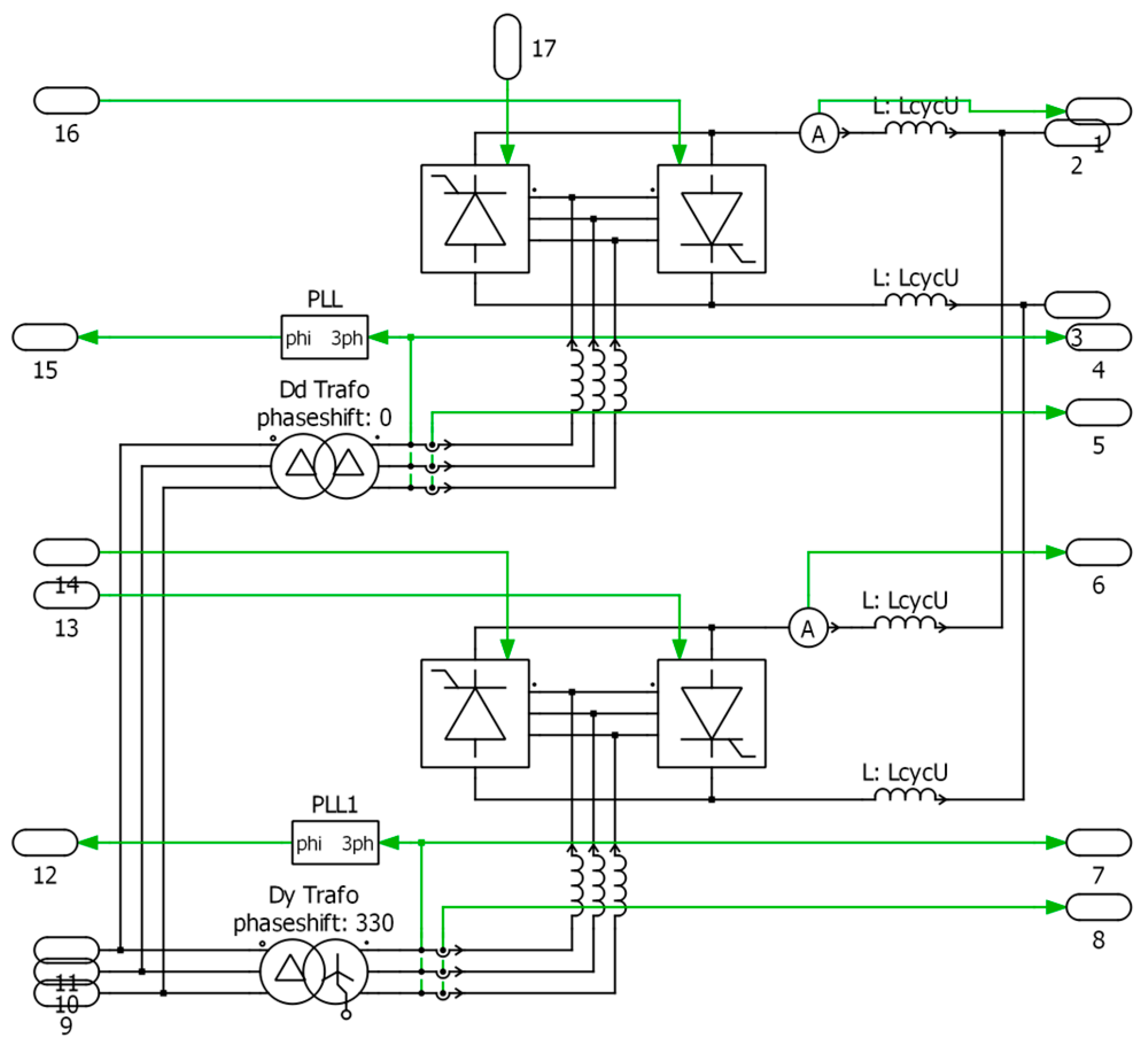

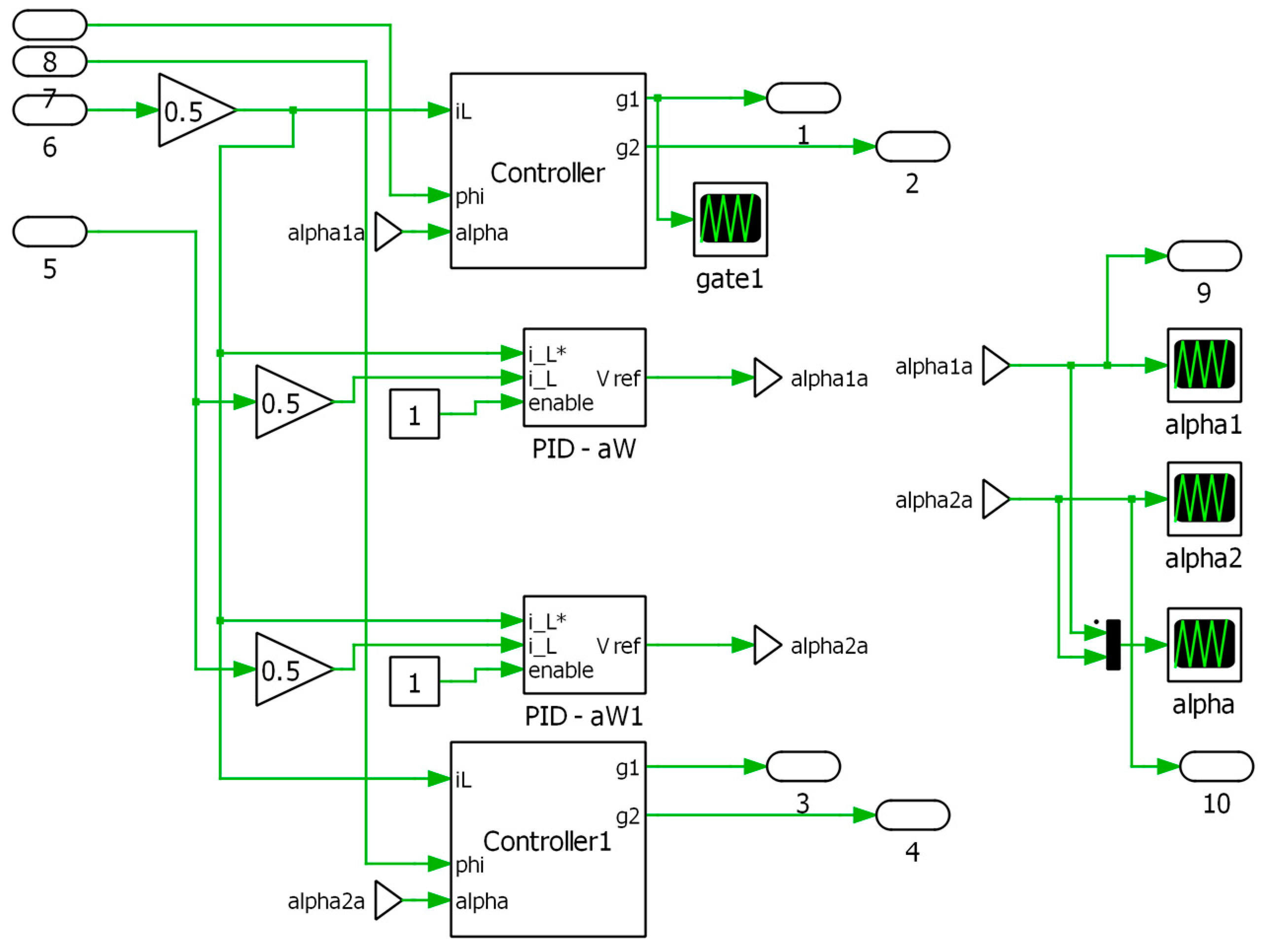

3.2. Cycloconverter Tyristor-Based Solution

- Thyristors (SCRs): These are the primary power semiconductor switches used due to their high-power handling capability and suitability for line (natural) commutation in step-down cycloconverter operations. The large number of SCRs required, especially in multi-pulse configurations, is a defining characteristic of these systems.

- Phase-Shifting Transformers: These are crucial for creating the 12-pulse input characteristic. Transformer arrangement provides the necessary phase displacement (e.g., 30 degrees) between the two sets of three-phase voltages feeding the 6-pulse converter bridges, enabling the cancellation of specific input harmonics. Additionally, they offer galvanic isolation and can step voltage up or down as required for the application.

Cycloconverter SCR Selection

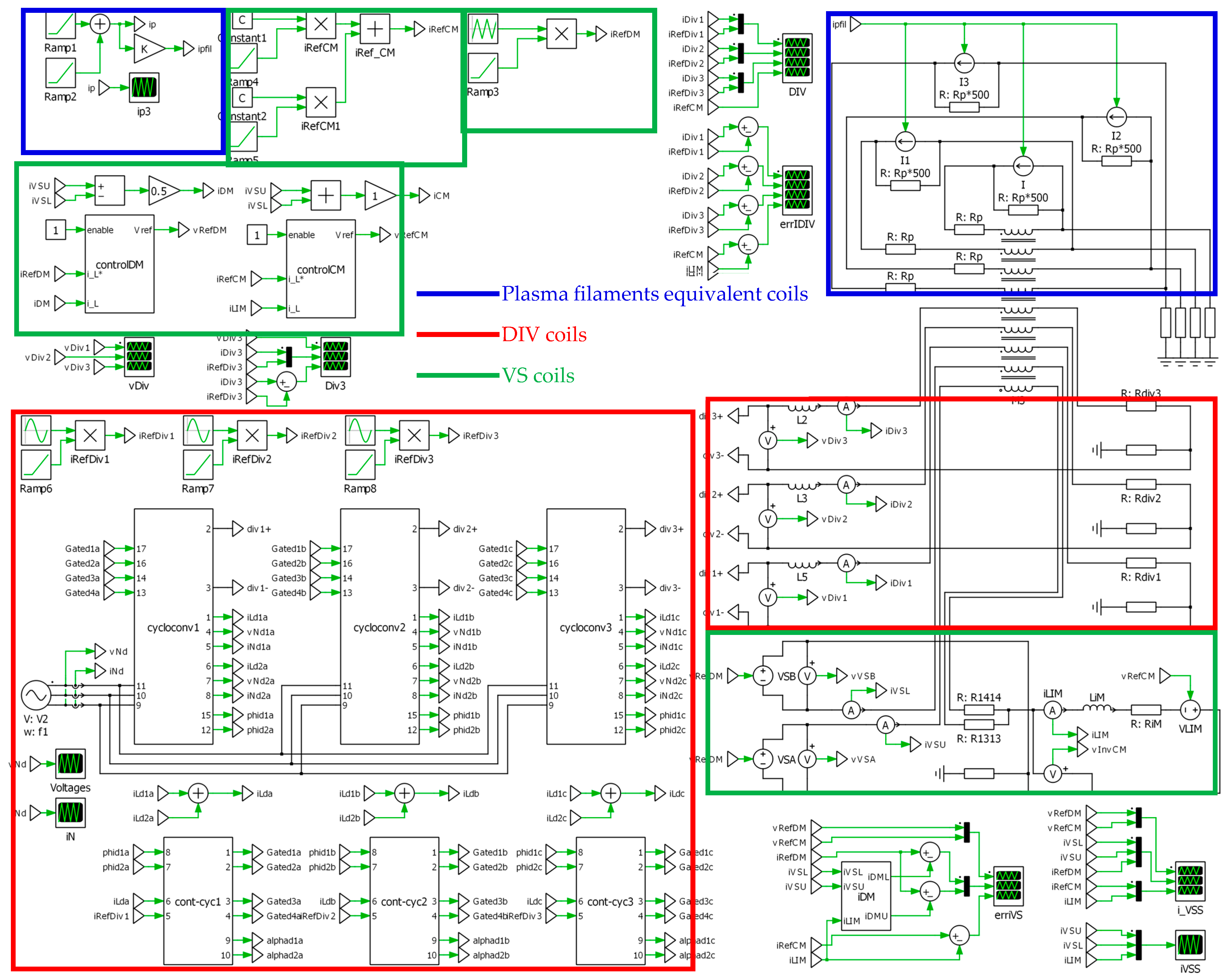

4. Power Supply Topologies Simulation Results

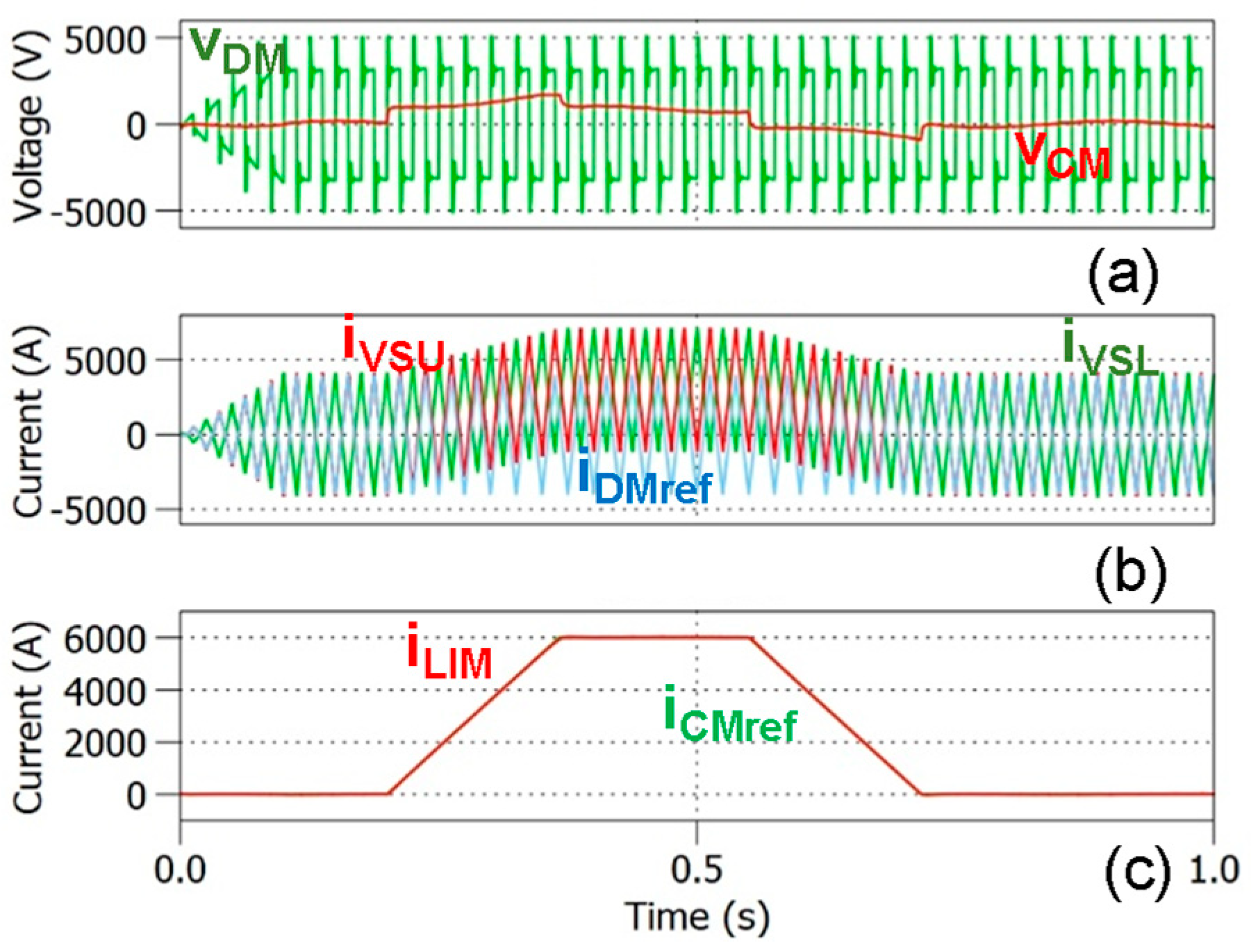

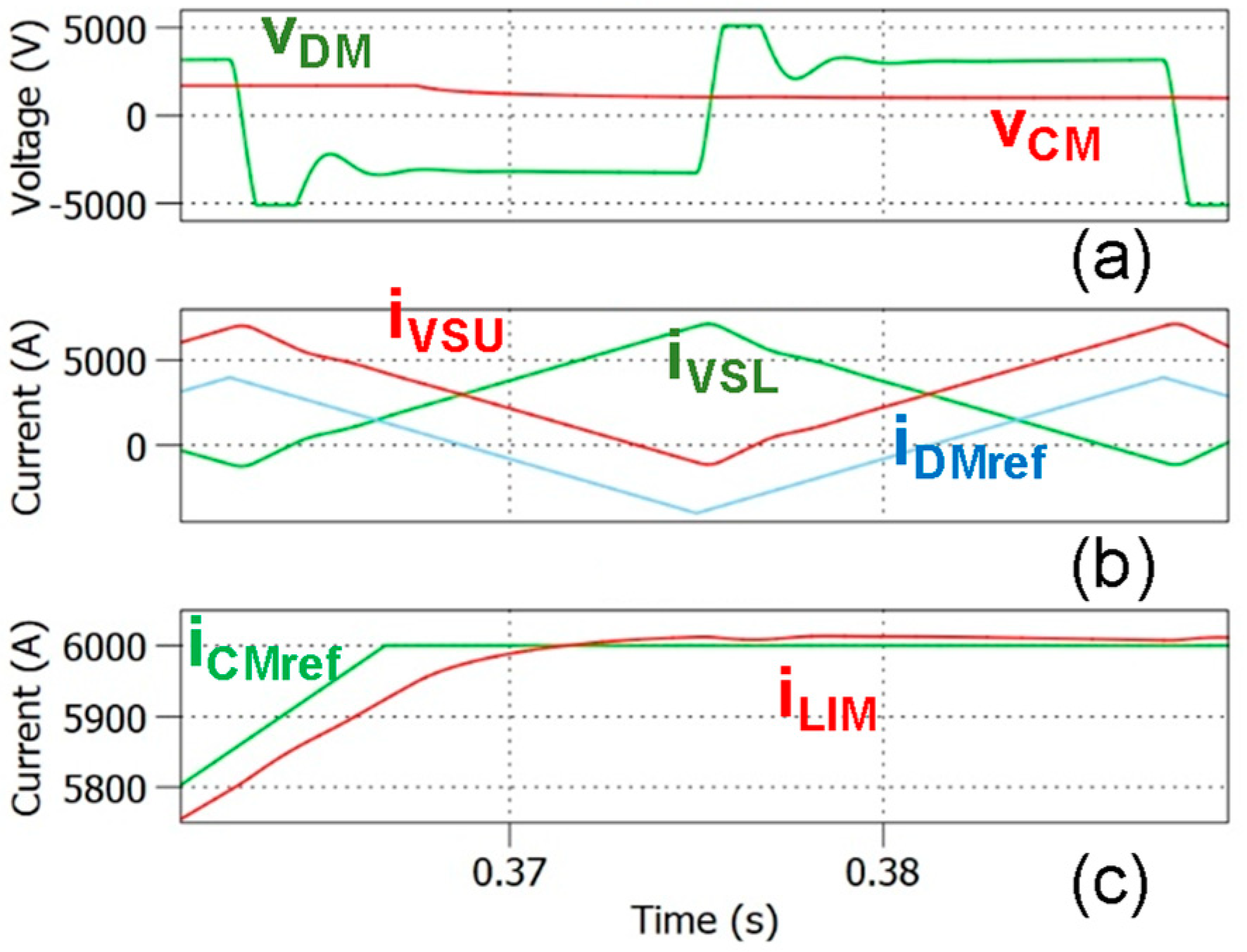

4.1. IGBT-Based Inverter Electrical Simulation Results

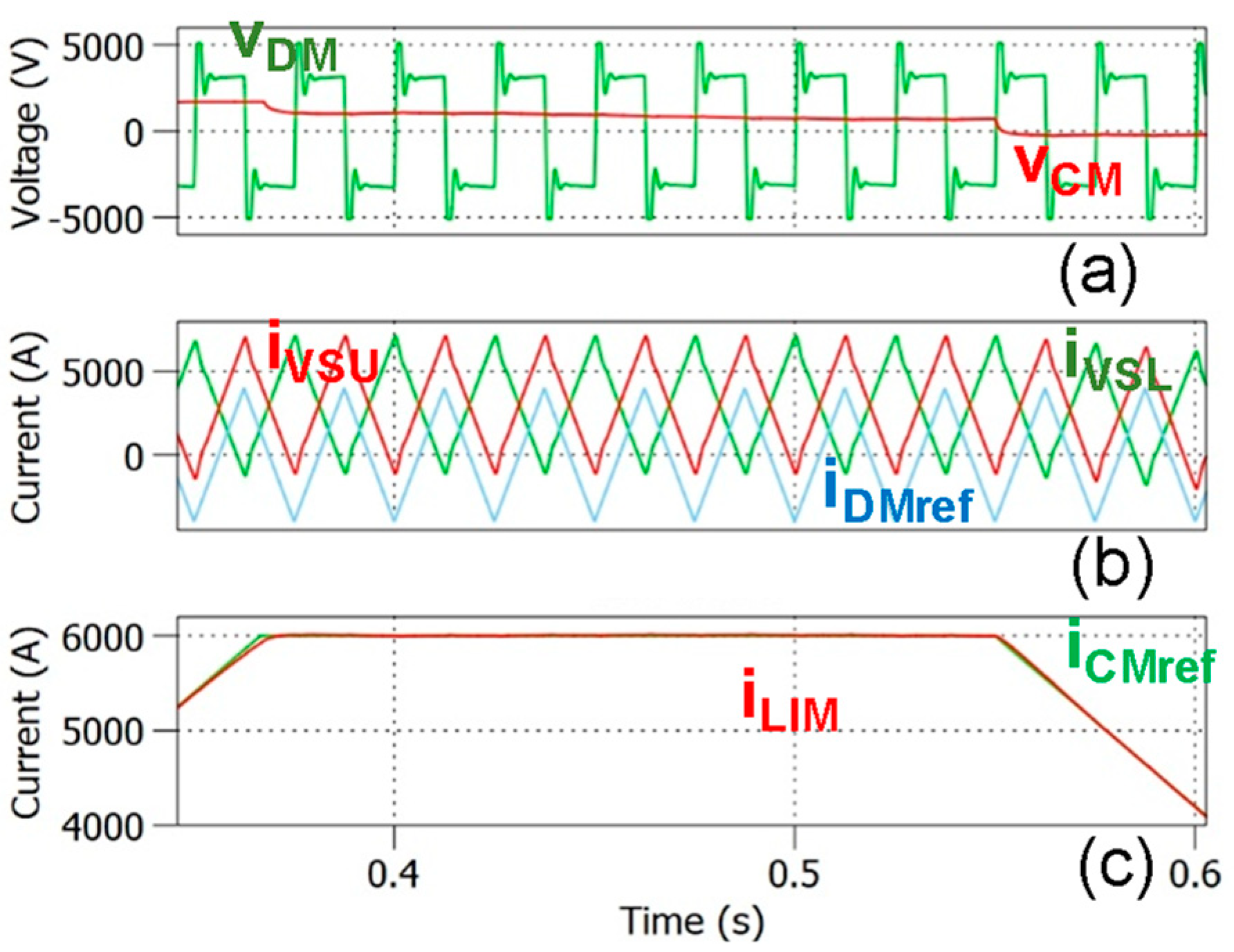

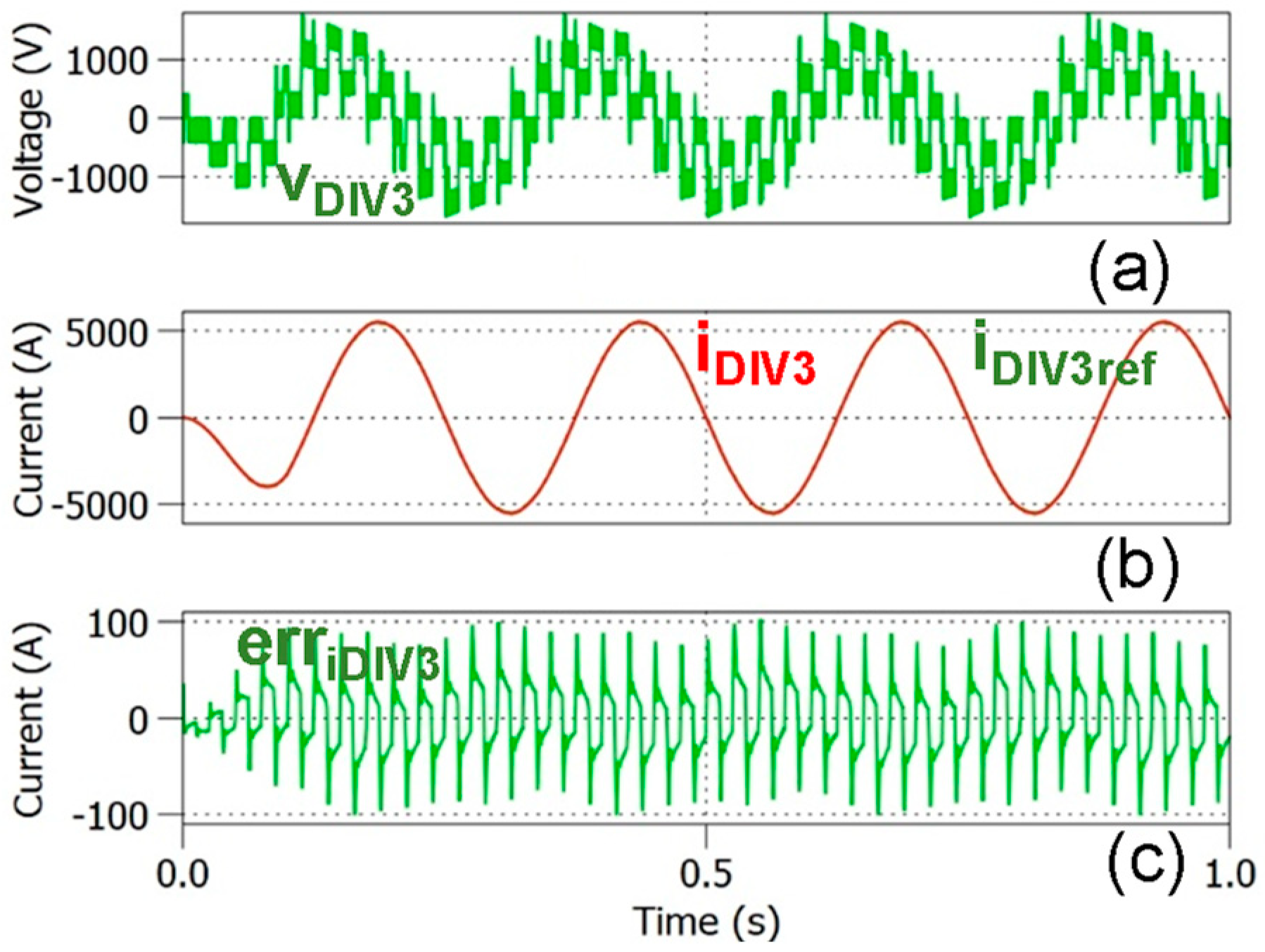

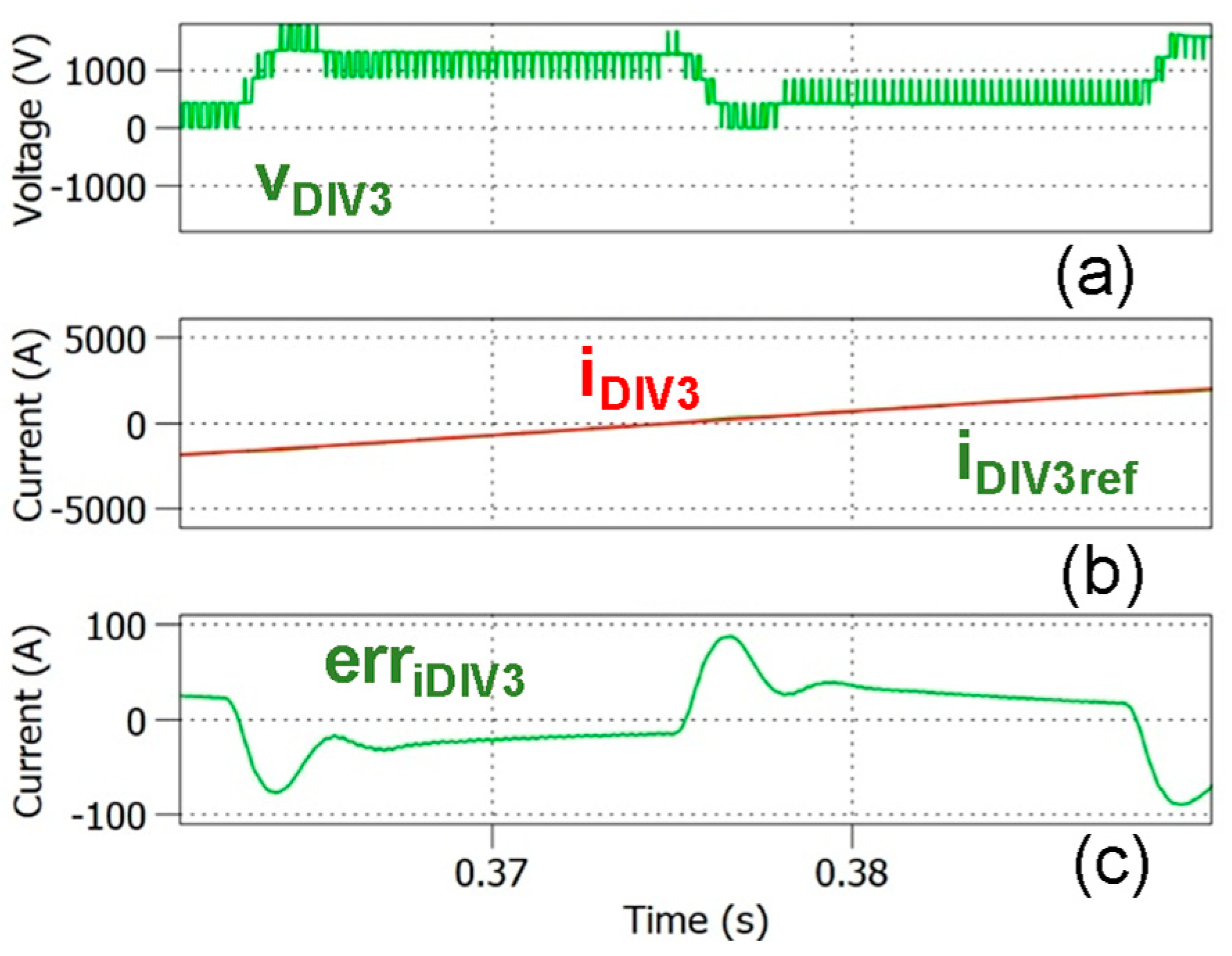

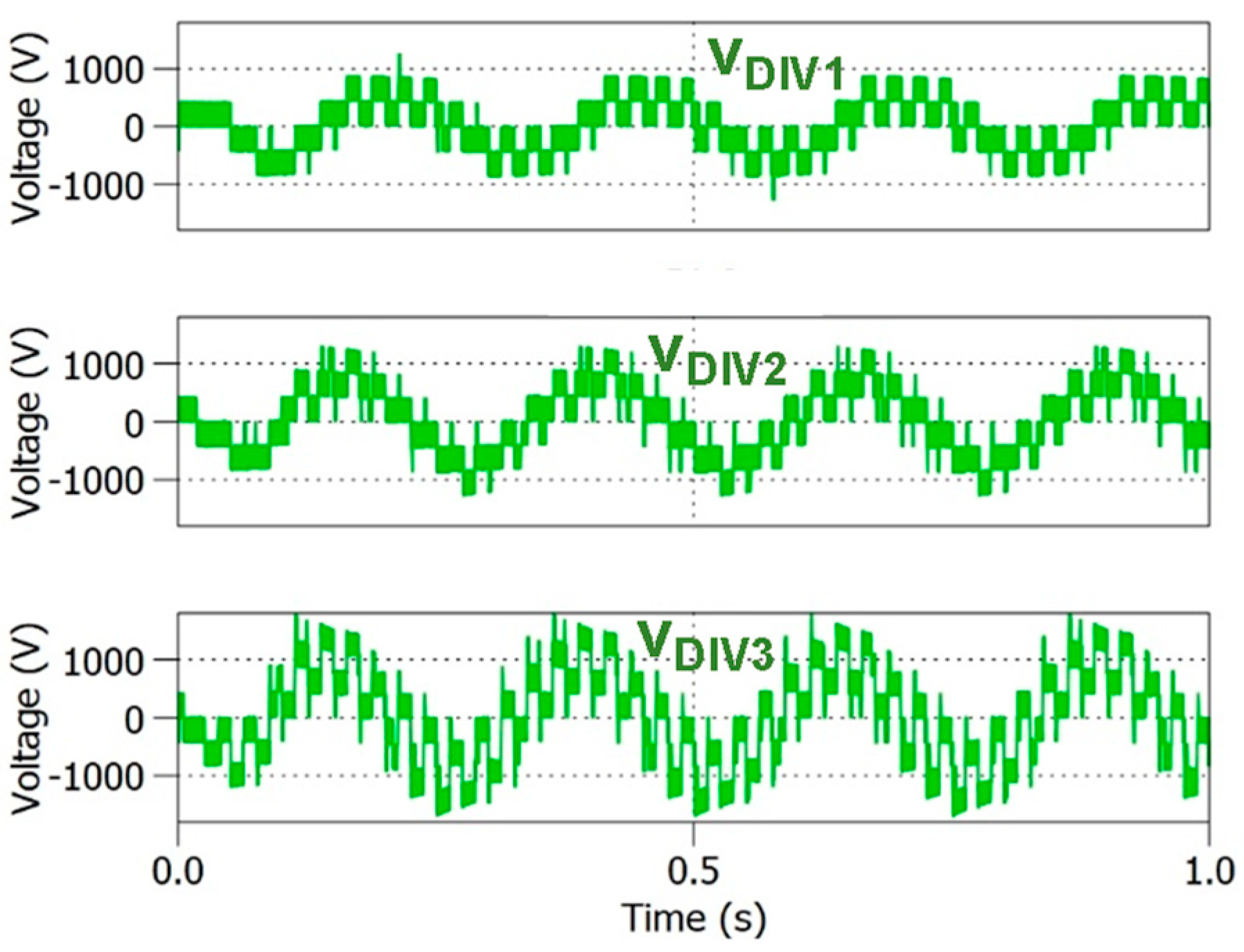

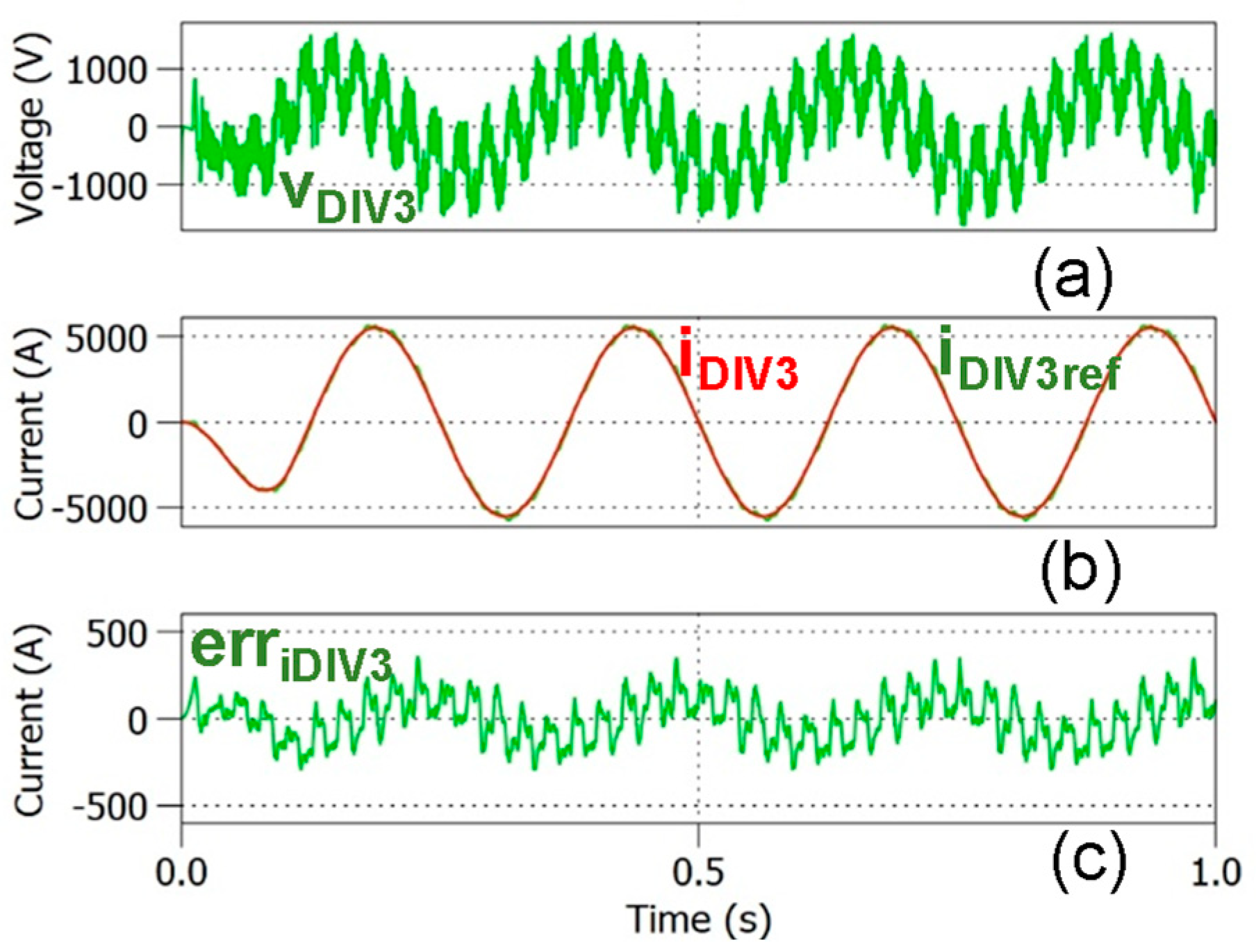

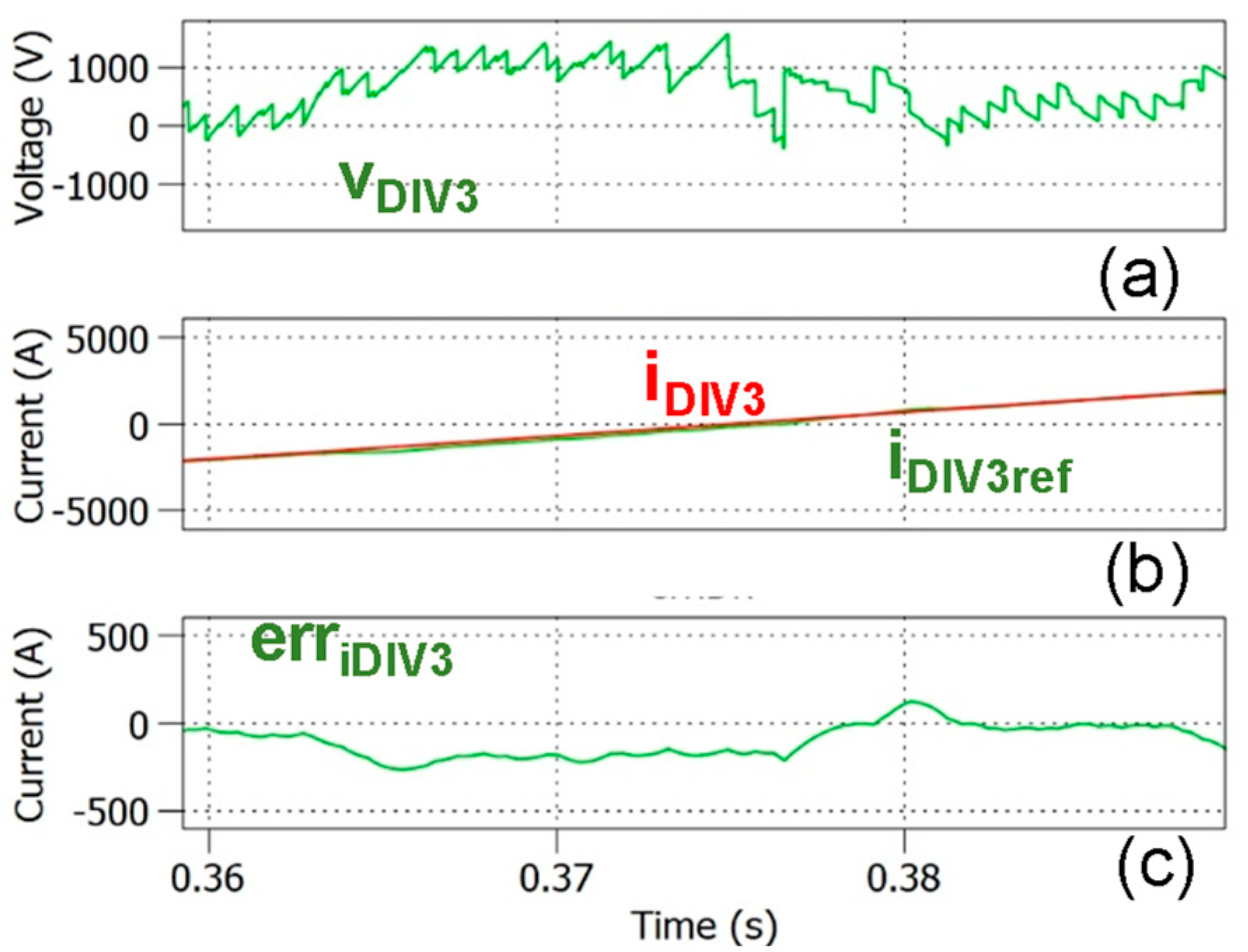

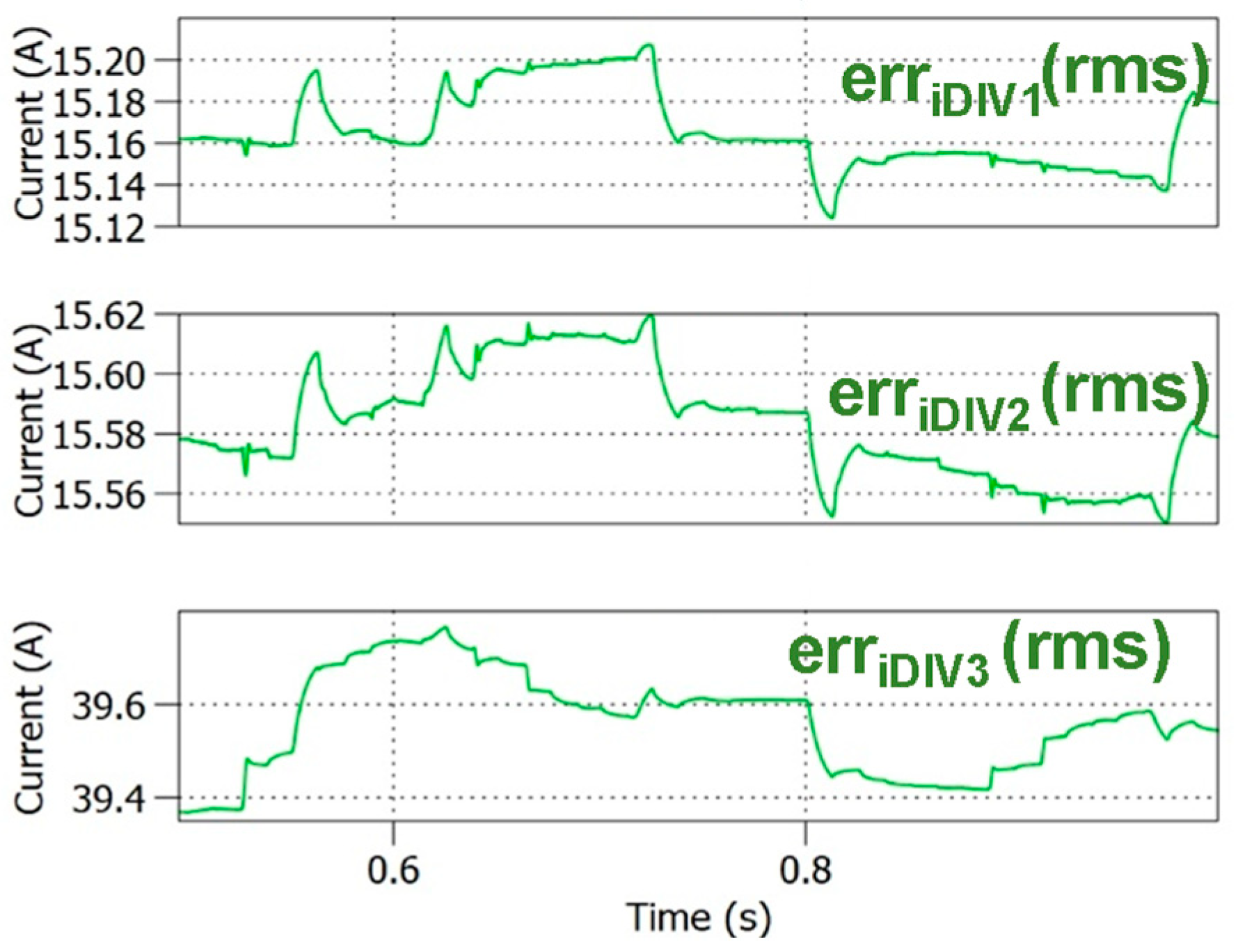

4.2. SCR-Based Cycloconverter Electrical Simulation Results

4.3. Comparison of Electrical Simulation Results for IGBT-Based and SCR-Based Power Supplies

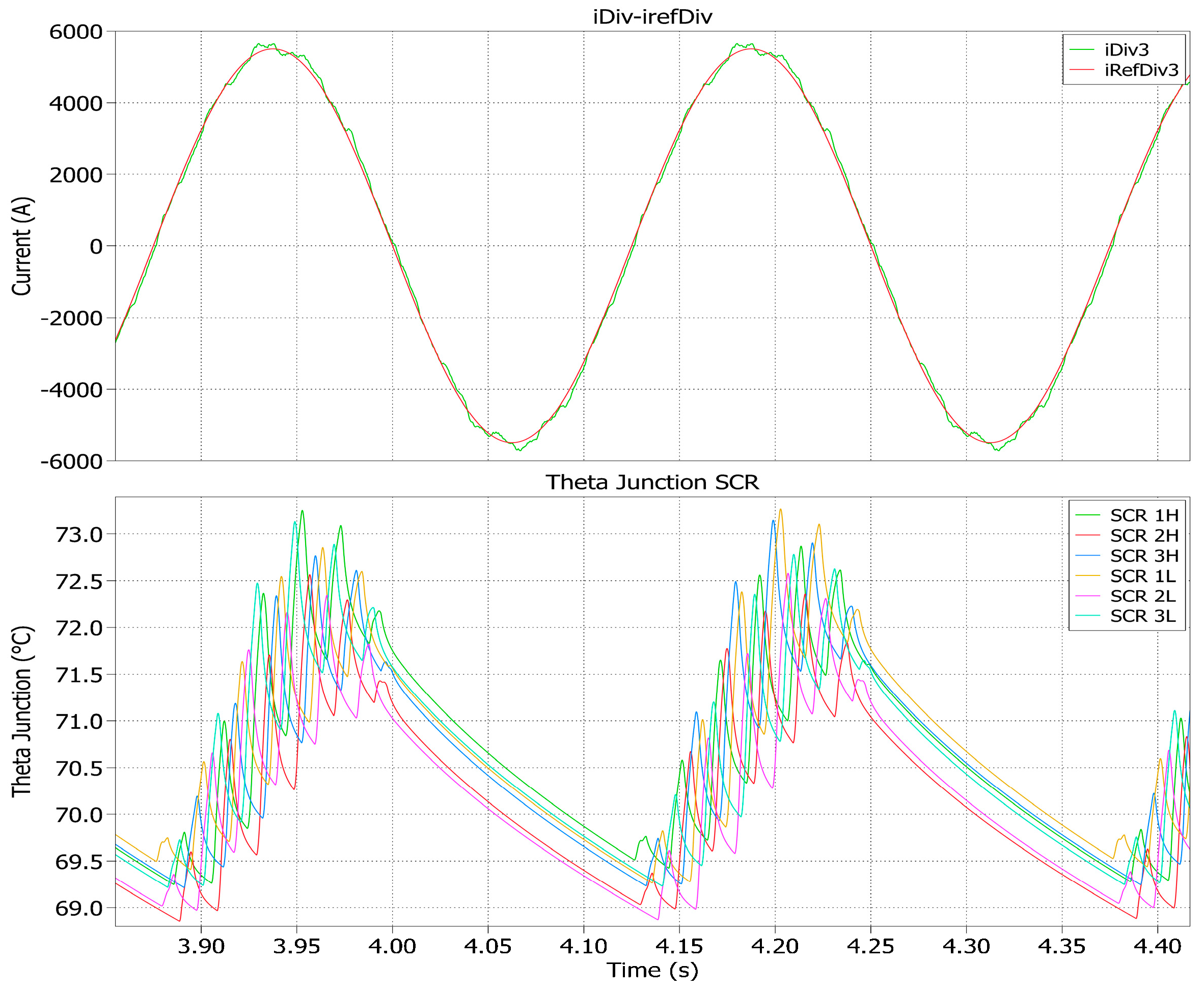

5. Switches/Converters Thermal Analysis

5.1. IGBT-Based Inverter Electro-Thermal Simulation Results

5.2. SCR-Based Cycloconverter Electro-Thermal Simulation Results

6. Discussion

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- EUROfusion. European Research Roadmap to the Realisation of Fusion Energy. 2018. Available online: http://www.euro-fusion.org/eurofusion/roadmap/ (accessed on 30 August 2025).

- ITER Website. Available online: http://www.iter.org (accessed on 30 August 2025).

- Fusion Industry Association. Available online: https://www.fusionindustryassociation.org/ (accessed on 30 August 2025).

- Federici, G.; Bachmann, C.; Barucca, L.; Baylard, C.; Biel, W.; Boccaccini, L.V.; Bustreo, C.; Ciattaglia, S.; Cismondi, F.; Corato, V.; et al. Overview of the DEMO staged design approach in Europe. Nucl. Fusion 2019, 59, 066013. [Google Scholar] [CrossRef]

- Siccinio, M.; Biel, W.; Cavedon, M.; Fable, E.; Federici, G.; Janky, F.; Lux, H.; Maviglia, F.; Morris, J.; Palermo, F.; et al. DEMO physics challenges beyond ITER. Fusion Eng. Des. 2020, 156, 1116033. [Google Scholar] [CrossRef]

- Wesson, J. Tokamaks, 3rd ed.; Clarendon Press: Oxford, UK, 2003. [Google Scholar]

- Lampasi, A.; Pipolo, S.; Albanese, R.; Ambrosino, R.; Bifaretti, S.; Bojoi, R.; Bonaiuto, V.; Castaldo, A.; Caldora, M.; Cocchi, A.; et al. Overview of the Divertor Tokamak Test (DTT) coil power supplies. Fusion Eng. Des. 2023, 188, 113442. [Google Scholar] [CrossRef]

- Martone, R.; Albanese, R.; Crisanti, F.; Martin, P.; Pizzuto, A. DTT Divertor Tokamak Test facility—Interim Design Report, ENEA, 2019. Available online: https://iris.unibas.it/bitstream/11563/136383/2/DTT_IDR_2019_WEB1.pdf (accessed on 15 July 2025).

- Romanelli, F. Divertor Tokamak Test facility Project: Status of Design and Implementation. Nucl. Fusion 2024, 64, 112015. [Google Scholar] [CrossRef]

- Kotschenreuther, M.; Valanju, P.M.; Mahajan, S.M.; Wiley, J.C. On heat loading, novel divertors, and fusion reactors. Phys. Plasmas 2007, 14, 072502. [Google Scholar] [CrossRef]

- Ambrosino, R. DTT—Divertor Tokamak Test facility: A testbed for DEMO. Fusion Eng. Des. 2021, 167, 1123300. [Google Scholar] [CrossRef]

- Innocente, P.; Ambrosino, R.; Brezinsek, S.; Calabrò, G.; Castaldo, A.; Crisanti, F.; Dose, G.; Neu, R.; Roccella, S. Design of a multi-configurations divertor for the DTT facility. Nucl. Mater. Energy 2022, 33, 101276. [Google Scholar] [CrossRef]

- Acampora, E.; Ambrosino, R.; Castaldo, A.; Iervolino, R. Magnetic control of DTT alternative plasma configurations. Fusion Eng. Des. 2023, 192, 113617. [Google Scholar] [CrossRef]

- Griva, G.; Musumeci, S.; Stella, F.; Bojoi, R.; Lampasi, A.; Zito, P.; Bifaretti, S. HIL Investigation of a Single-Phase Inverter for a Tokamak Non-Axisymmetric In-Vessel Coil Power Supply. IEEE Trans. Ind. Appl. 2024, 60, 4076–4086. [Google Scholar] [CrossRef]

- Griva, G.; Musumeci, S.; Stella, F.; Bojoi, R.; Lampasi, A.; Bifaretti, S. C-HIL Implementation of Cascaded Multilevel Inverter for Vertical Stabilization and Radial Control Power Supplies of Divertor Tokamak Test. In Proceedings of the 2024 International Conference on Smart Energy Systems and Technologies (SEST), Torino, Italy, 10–12 September 2024; pp. 1–6. [Google Scholar]

- Lampasi, A.; Testa, R.; Gudala, B.; Terlizzi, C.; Pipolo, S.; Tenconi, S. Optimization of DC Energy Storage in Tokamak Poloidal Coils. Appl. Sci. 2024, 14, 8975. [Google Scholar] [CrossRef]

- Acampora, E.; Albanese, R.; Ambrosino, R.; Castaldo, A.; Innocente, P.; Loschiavo, V.P. Conceptual design of in-vessel divertor coils in DTT. Fusion Eng. Des. 2023, 193, 113651. [Google Scholar] [CrossRef]

- Ambrosino, R.; Ariola, M.; Bachmann, C.; Castaldo, A.; Maviglia, F.; Mattei, M.; Tartaglione, G. Sweeping control performance on DEMO device. Fusion Eng. Des. 2021, 197, 114029. [Google Scholar] [CrossRef]

- Teschke, M.; ASDEX Upgrade Team. Development of an active overvoltage protection for the new ASDEX upgrade divertor coils. Fusion Eng. Des. 2021, 171, 112541. [Google Scholar] [CrossRef]

- Syah, M.N.; Firmansyah, E.; Utomo, D.R. Interleaved Bidirectional DC-DC Converter Operation Strategies and Problem Challenges: An Overview. In Proceedings of the IEEE International Conference in Power Engineering Application (ICPEA), Shah Alam, Malaysia, 7–8 March 2022; pp. 1–6. [Google Scholar] [CrossRef]

- Galkin, I.A.; Saltanovs, R.; Bubovich, A.; Blinov, A.; Peftitsis, D. Considerations on Combining Unfolding Inverters with Partial Power Regulators in Battery–Grid Interface Converters. Energies 2023, 17, 893. [Google Scholar] [CrossRef]

- Do, T.A.; Nguyen, Q.D.; Vu, P.; Ngo, M.D.; Ahn, S. Comparative Analysis of PWM Techniques for Interleaved Full Bridge Converter in an AC Battery Application. Energies 2023, 17, 375. [Google Scholar] [CrossRef]

- Datasheet URL IGBT Module FF1800R23IE7. Available online: https://www.infineon.com/assets/row/public/documents/non-assigned/49/infineon-ff1800r23ie7-datasheet-en.pdf (accessed on 15 July 2025).

- Wu, B.; Pontt, J.; Rodríguez, J.; Bernet, S.; Kouro, S. Current-Source Converter and Cycloconverter Topologies for Industrial Medium-Voltage Drives. IEEE Trans. Ind. Electron. 2008, 55, 2786–2797. [Google Scholar] [CrossRef]

- Tahmid, M.R.; Malek, M.A.; Islam, M.R.; Khan, M.A.G. Advanced thyristor-based cycloconverter for efficient three-phase conversion with low THD. E-Prime—Adv. Electr. Eng. Electron. Energy 2025, 11, 100918. [Google Scholar] [CrossRef]

- Barría, V.G.; Olivares, J.P. Design of a 12-pulse cycloconverter with fault-tolerance capability. In Proceedings of the 2011 14th European Conference on Power Electronics and Applications, Birmingham, UK, 30 August–1 September 2011; pp. 1–10. [Google Scholar]

- Datasheet URL SCR T4771N22TOF. Available online: https://www.infineon.com/assets/row/public/documents/60/49/infineon-t4771n-ds-en-de.pdf (accessed on 15 July 2025).

- Kandlikar, S.G.; Hayner, C.N. Liquid Cooled Cold Plates for Industrial High-Power Electronic Devices—Thermal Design and Manufacturing Considerations. Heat Transf. Eng. 2009, 30, 918–930. [Google Scholar] [CrossRef]

- Aranzabal, I.; Perez-Peña, F.J.; Lima, A.V.; de la Osa, A.R.; Alonso, J.M. Comparison between conventional single-phase and two-phase cooling systems for electric vehicle IGBT modules. IEEE Trans. Power Electron. 2019, 34, 11236–11248. [Google Scholar] [CrossRef]

- Kandlikar, S.G. Liquid Cooled Cold Plates for Industrial High-Power Electronic Devices: A Review. Heat Transf. Eng. 2010, 31, 156–171. [Google Scholar]

- Price, A.; Savulak, M. A review of selected thermal management solutions for avionics. IEEE Trans. Components Packag. Technol. 2003, 26, 26–39. [Google Scholar] [CrossRef]

- Akgül, M.B.; Erçel, F.S. Thermal Performance Analysis of a Liquid Cooling Plate for Power Electronics. Celal Bayar Üniversitesi Fen Bilimleri Dergisi 2021, 20, 72–81. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| Output voltage (peak max (DiV3) | 1.7 kV |

| Peak output current | 5.5 kA |

| IGBT rated voltage VCES | 2300 V |

| IGBT rated current | 1800 A |

| Repetitive peak forward Current (tp = 1 ms) | 3600 A |

| Collector–emitter Saturation voltage VCEsat @125 °C, Typ. | 2.15 V |

| Diode forward voltage VF @125 °C, Typ. | 3 V |

| Diode peak reverse recovery Current IRM @125 °C, | 1450 A |

| Part number and package: | FF1800R23IE7 by Infineon PrimePACK™3+ B-series module |

| Number of switching legs for the interleaved approach of one DC/AC unit | 4 |

| Parallel switches for the unfolder low-side and high-side of one DC/AC unit | 3 |

| Parameter | IGBT Inverters | SCR Cycloconverters |

|---|---|---|

| Current control error (RMS, for DIV3) | 39.6 A | 135 A |

| Thermal margin (percentage of maximum junction temperature vs. limit) | 130 °C/150 °C 86.7% | 73 °C/125 °C 58.4% |

| Estimated number of main switching devices | 14 IGBTs + 14 diodes | 24 SCRs |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Griva, G.; Musumeci, S.; Bojoi, R.; Stella, F.; Lampasi, A. Design Assessment of Power Supply Systems for Divertor Coils in the Divertor Tokamak Test. Appl. Sci. 2025, 15, 10441. https://doi.org/10.3390/app151910441

Griva G, Musumeci S, Bojoi R, Stella F, Lampasi A. Design Assessment of Power Supply Systems for Divertor Coils in the Divertor Tokamak Test. Applied Sciences. 2025; 15(19):10441. https://doi.org/10.3390/app151910441

Chicago/Turabian StyleGriva, Giovanni, Salvatore Musumeci, Radu Bojoi, Fausto Stella, and Alessandro Lampasi. 2025. "Design Assessment of Power Supply Systems for Divertor Coils in the Divertor Tokamak Test" Applied Sciences 15, no. 19: 10441. https://doi.org/10.3390/app151910441

APA StyleGriva, G., Musumeci, S., Bojoi, R., Stella, F., & Lampasi, A. (2025). Design Assessment of Power Supply Systems for Divertor Coils in the Divertor Tokamak Test. Applied Sciences, 15(19), 10441. https://doi.org/10.3390/app151910441