Exploitation of an Industrial Low-Bandwidth Communication Line for Modulation-Level Synchronization of Voltage Source Converters

Abstract

1. Introduction

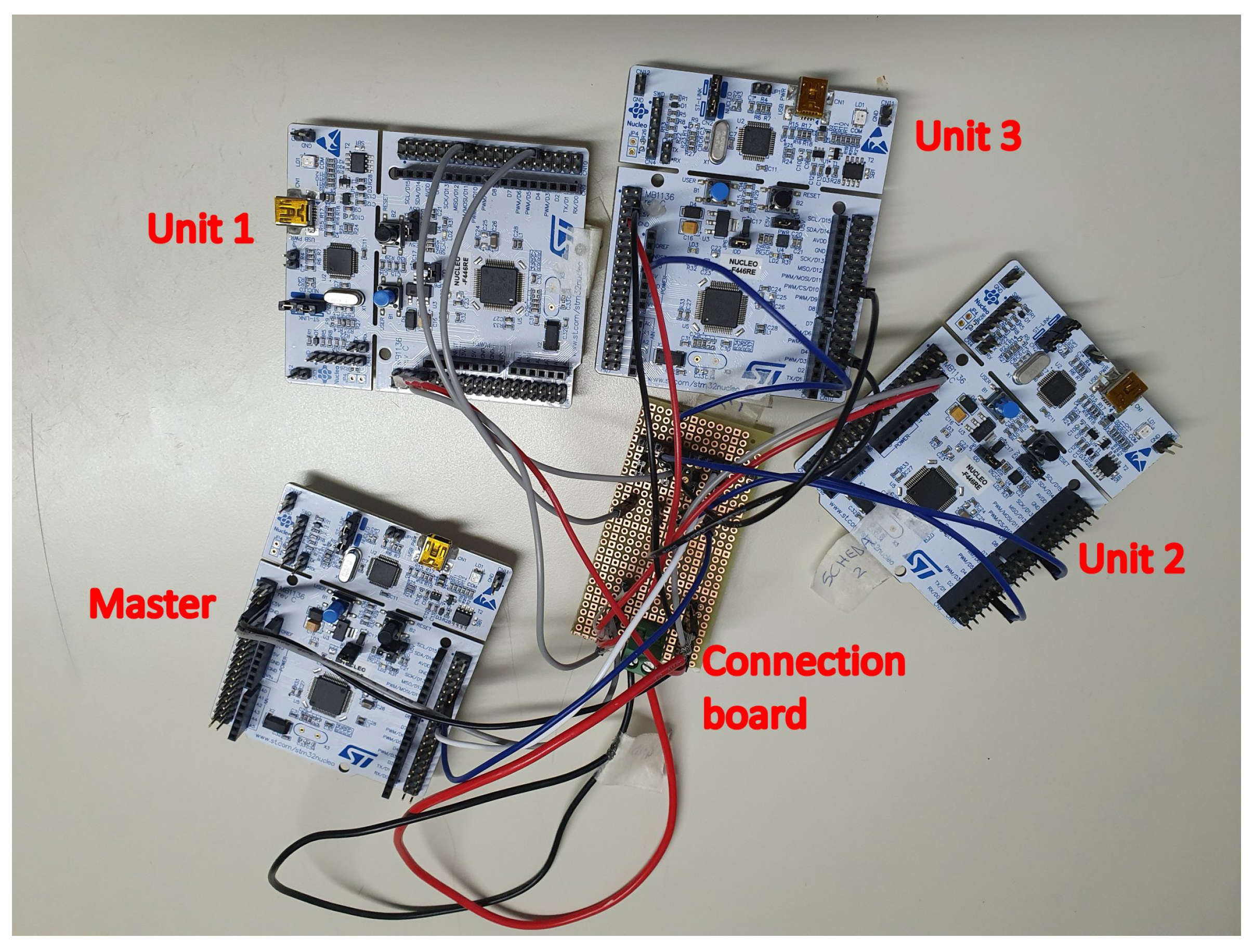

2. Materials and Methods

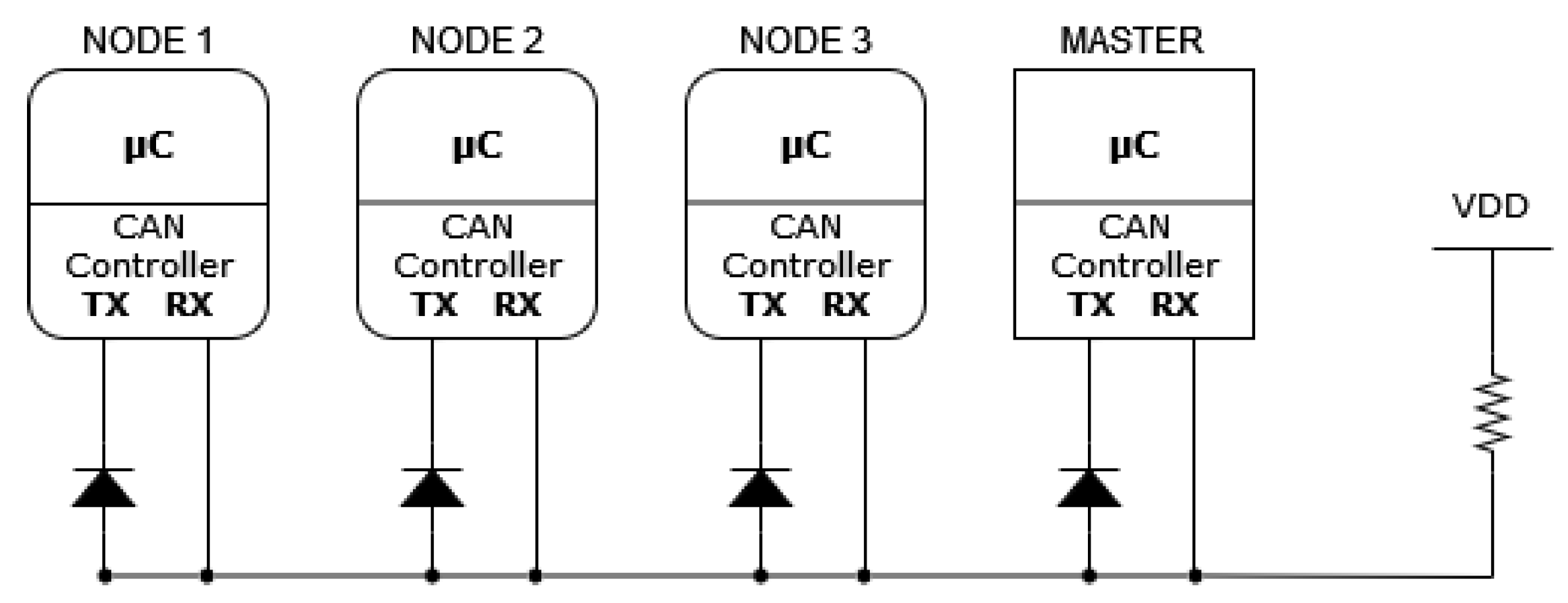

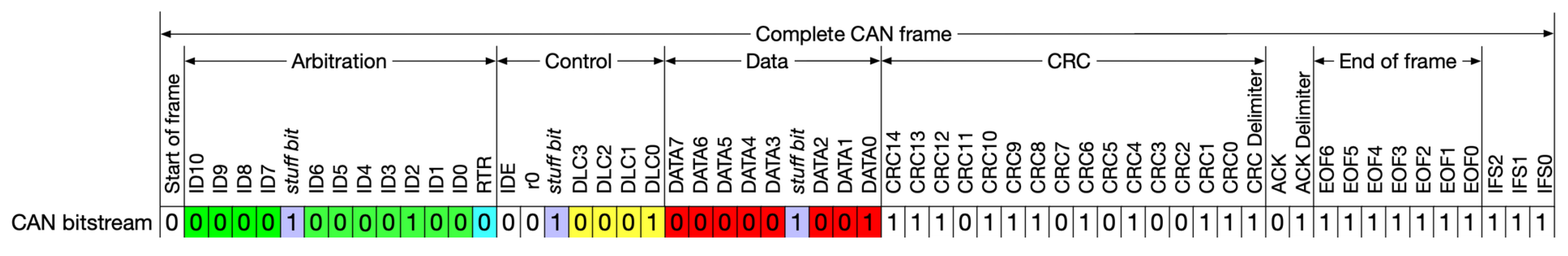

2.1. CAN Peripheral Synchronization Method

- Synchronization segment: where an edge is expected to be.

- Propagation segment: used to compensate line and drivers delay.

- Phase segments 1 and 2: dynamic length segments used to perform synchronization.

2.2. Oscillators Tolerance

2.3. CAN Peripheral Interrupt Synchronization

- Transmission and reception of incoming messages;

- Construction of bit time (Time Quanta, Sync and Phase segments);

- Interrupt management registers;

- Diagnostic information.

- Validation;

- Peripheral FIFO register signaling;

- Interrupt management (ends with first instruction of ISR);

- PWM starting sequence.

2.4. GPIO Interrupt Synchronization

3. Results

3.1. Frequency Drift

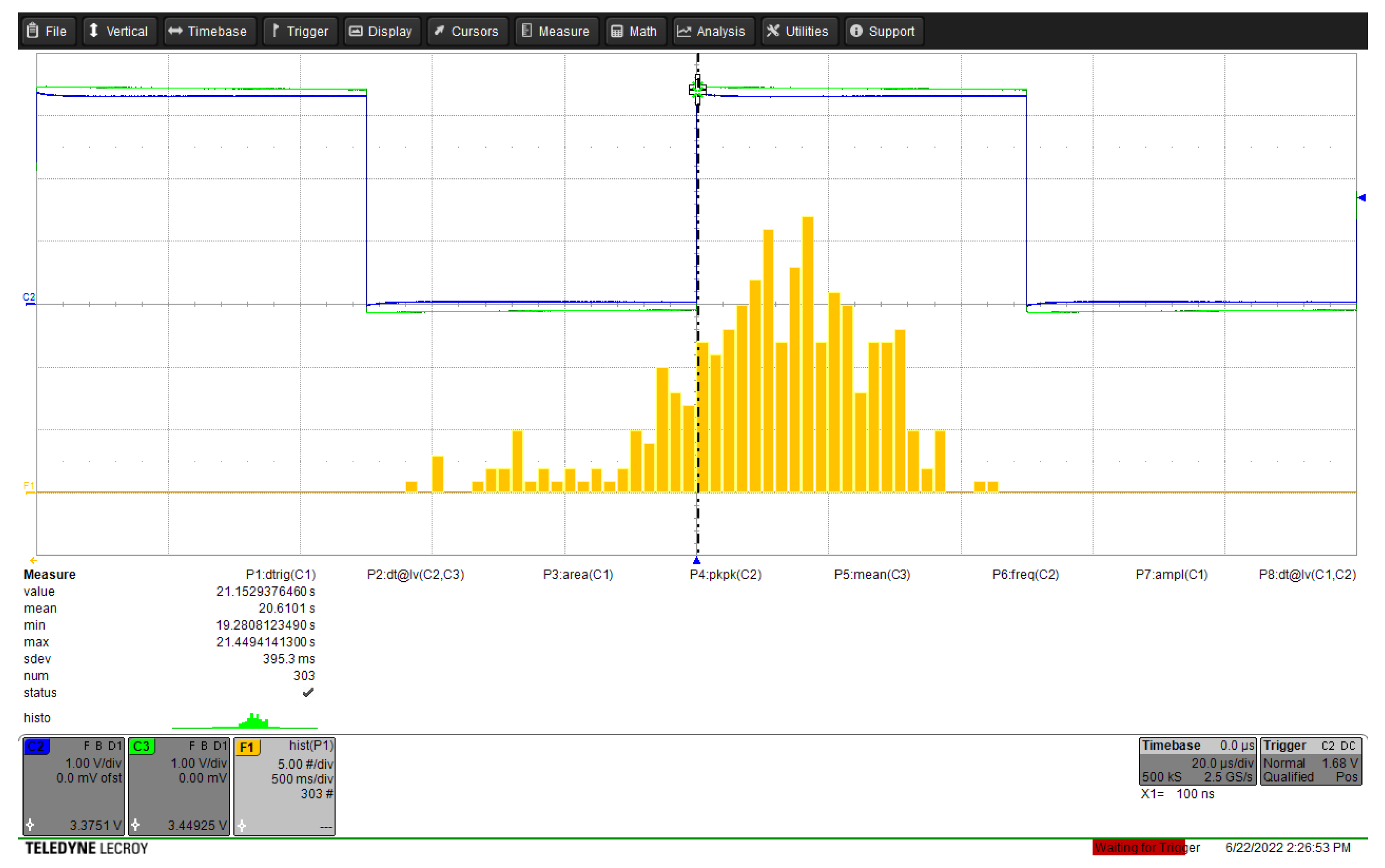

3.2. CAN Peripheral Interrupt Synchronization

3.3. GPIO Interrupt Synchronization

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zhang, J.; Li, Y.; Wang, H.; Cai, X.; Igarashi, S.; Wang, Z. Thermal smooth control based on orthogonal circulating current for multi-MW parallel wind power converter. In Proceedings of the 2014 International Power Electronics and Application Conference and Exposition, Shanghai, China, 5–8 November 2014; IEEE: Shanghai, China, 2014; pp. 146–151. [Google Scholar] [CrossRef]

- Li, W.; Zhang, X.; Zhuang, Y.; Zhang, G.; Wang, G.; Xu, D. A Five-Level Space Vector Modulation Scheme for Parallel Operated Three-Level Inverters With Reduced Line Current Distortion. IEEE Trans. Power Electron. 2020, 35, 11235–11249. [Google Scholar] [CrossRef]

- Tan, L.; Zhu, N.; Wu, B. An Integrated Inductor for Eliminating Circulating Current of Parallel Three-Level DC–DC Converter-Based EV Fast Charger. IEEE Trans. Ind. Electron. 2016, 63, 1362–1371. [Google Scholar] [CrossRef]

- Rodriguez-Amenedo, J.L.; Arnaltes-Gomez, S.; Aragues-Penalba, M.; Gomis-Bellmunt, O. Control of the Parallel Operation of VSC-HVDC Links Connected to an Offshore Wind Farm. IEEE Trans. Power Deliv. 2019, 34, 32–41. [Google Scholar] [CrossRef]

- Kim, S.A.; Han, S.W.; Byun, S.I.; Cho, Y.H. Improved parallel operation mode control of parallel connected 12-pulse thyristor dual converter for urban railway power substations. In Proceedings of the 2016 IEEE 17th Workshop on Control and Modeling for Power Electronics (COMPEL), Trondheim, Norway, 27–30 June 2016; IEEE: Trondheim, Norway, 2016; pp. 1–6. [Google Scholar] [CrossRef]

- Arnaudov, D.D.; Vuchev, S.A. Investigation of Resonant Converters Parallel Operation to a Common Load. In Proceedings of the 2018 IEEE XXVII International Scientific Conference Electronics-ET, Sozopol, Bulgaria, 13–15 September 2018; IEEE: Sozopol, Bulgaria, 2018; pp. 1–4. [Google Scholar] [CrossRef]

- Chen, T.P. Zero-Sequence Circulating Current Reduction Method for Parallel HEPWM Inverters Between AC Bus and DC Bus. IEEE Trans. Ind. Electron. 2012, 59, 290–300. [Google Scholar] [CrossRef]

- Xueguang, Z.; Wenjie, Z.; Jiaming, C.; Dianguo, X. Deadbeat Control Strategy of Circulating Currents in Parallel Connection System of Three-Phase PWM Converter. IEEE Trans. Energy Convers. 2014, 29, 406–417. [Google Scholar] [CrossRef]

- Yu, H.; Tao, Y.; Li, G.J.; Yin, S.; Zhuang, J.; Sun, C. Control Strategy for Parallel Operation of Converters Based on Adaptive Virtual Inductance. In Proceedings of the 2021 International Conference on Wireless Communications and Smart Grid (ICWCSG), Hangzhou, China, 13–15 August 2021; IEEE: Hangzhou, China, 2021; pp. 444–448. [Google Scholar] [CrossRef]

- Li, D.; Huang, X.; Nie, C.; Niu, J.; Chen, R.; Lin, M.; Ji, S.; Wang, F.; Tolbert, L.M.; Giewont, W. Paralleling Operation of 10 kV SiC MOSFET-Based Modular Multi-Level Converters (MMCs) for Scalable Asynchronous Microgrid Power Conditioning System. In Proceedings of the 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), Phoenix, AZ, USA, 14–17 June 2021; IEEE: Phoenix, AZ, USA, 2021; pp. 1444–1450. [Google Scholar] [CrossRef]

- Choo, K.L. Parallel connection of DC/AC switched mode power converter in utility distribution system. In Proceedings of the 2008 IEEE 2nd International Power and Energy Conference, Johor Bahru, Malaysia, 1–3 December 2008; IEEE: Johor Bahru, Malaysia, 2008; pp. 1369–1372. [Google Scholar] [CrossRef]

- Gan, J.; Yin, Q.; Chen, T.; Zhao, L.; Deng, C.; Liu, Z. Reasearch on the circulating current suppression for parallel T-type three-level PCS based on on-line synchronization and average current. In Proceedings of the 2019 IEEE 3rd Advanced Information Management, Communicates, Electronic and Automation Control Conference (IMCEC), Chongqing, China, 11–13 October 2019; IEEE: Chongqing, China, 2019; pp. 773–776. [Google Scholar] [CrossRef]

- Gohil, G.; Bede, L.; Teodorescu, R.; Kerekes, T.; Blaabjerg, F. Evaluation of circulating current suppression methods for parallel interleaved inverters. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; IEEE: Milwaukee, WI, USA, 2016; pp. 1–8. [Google Scholar] [CrossRef]

- Asiminoaei, L.; Aeloiza, E.; Kim, J.; Enjeti, P.; Blaabjerg, F.; Moran, L.; Sul, S. Parallel Interleaved Inverters for Reactive Power and Harmonic Compensation. In Proceedings of the 37th IEEE Power Electronics Specialists Conference, Jeju, Republic of Korea, 18–22 June 2006; IEEE: Jeju, Republic of Korea, 2006; pp. 1–7. [Google Scholar] [CrossRef]

- Rannestad, B.; Munk-Nielsen, S.; Gadgaard, K. Discontinuous interleaving of parallel inverters for efficiency improvement. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; IEEE: Warsaw, Poland, 2017; pp. P.1–P.10. [Google Scholar] [CrossRef]

- Gohil, G.; Bede, L.; Teodorescu, R.; Kerekes, T.; Blaabjerg, F. An Integrated Inductor for Parallel Interleaved Three-Phase Voltage Source Converters. IEEE Trans. Power Electron. 2016, 31, 3400–3414. [Google Scholar] [CrossRef]

- Trintis, I.; Gohil, G.; Wurzer, M.; Franzen, M.; Pallesgaard, S.L.; Munk-Nielsen, S.; Carne Kjaer, P. Line reactor for parallel-interleaved high power inverters. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; IEEE: Warsaw, Poland, 2017; pp. P.1–P.10. [Google Scholar] [CrossRef]

- Gohil, G.; Bede, L.; Teodorescu, R.; Kerekes, T.; Blaabjerg, F. Magnetic Integration for Parallel Interleaved VSCs Connected in a Whiffletree Configuration. IEEE Trans. Power Electron. 2016, 31, 7797–7808. [Google Scholar] [CrossRef]

- Zhang, D.; Wang, F.; Burgos, R.; Boroyevich, D. Total Flux Minimization Control for Integrated Inter-Phase Inductors in Paralleled, Interleaved Three-Phase Two-Level Voltage-Source Converters With Discontinuous Space-Vector Modulation. IEEE Trans. Power Electron. 2012, 27, 1679–1688. [Google Scholar] [CrossRef]

- Soldati, A.; Undre, V.; Concari, C.; Alsayid, B.A.; Dradi, M.H. Parallel Operation of Voltage Source Converters without Filter Inductors: Control of the Circulating Current. In Proceedings of the 2020 2nd IEEE International Conference on Industrial Electronics for Sustainable Energy Systems (IESES), Cagliari, Italy, 1–3 September 2020; IEEE: Cagliari, Italy, 2020; pp. 125–130. [Google Scholar] [CrossRef]

- Rumble, J. CRC Handbook of Chemistry and Physics: A Ready-Reference Book of Chemical and Physical Data, 102nd ed.; CRC Press: Boca Raton, FL, USA, 2021. [Google Scholar]

- Reatti, A.; Corti, F.; Tesi, A.; Torlai, A.; Kazimierczuk, M.K. Effect of Parasitic Components on Dynamic Performance of Power Stages of DC-DC PWM Buck and Boost Converters in CCM. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; IEEE: Sapporo, Japan, 2019; pp. 1–5. [Google Scholar] [CrossRef]

- ISO 11898; CAN Specification Version 2.0. Bosch: Gailingen, Germany, 1991; pp. 1–72.

| Units under Test | N (Number of Tests) | Average [s] | Std. Dev. [ms] | Minimum [s] | Maximum [s] |

|---|---|---|---|---|---|

| 303 | |||||

| 338 | |||||

| 314 |

| Units under Test | Oscillator Mismatch [ppm] |

|---|---|

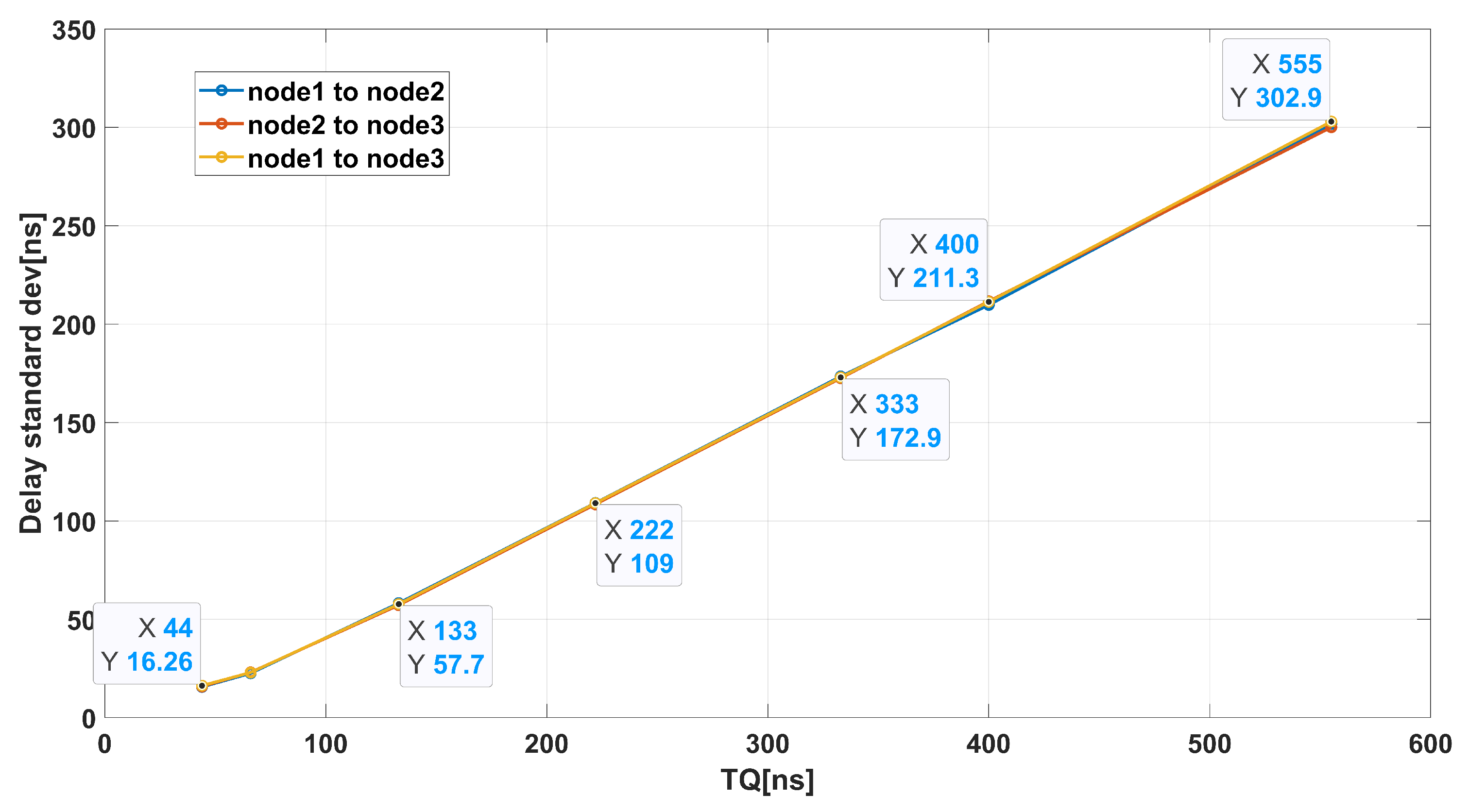

| Delay Sigma | ns | ns |

|---|---|---|

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lodi Rizzini, G.; Bassani, M.; Concari, C.; Soldati, A. Exploitation of an Industrial Low-Bandwidth Communication Line for Modulation-Level Synchronization of Voltage Source Converters. Appl. Sci. 2023, 13, 230. https://doi.org/10.3390/app13010230

Lodi Rizzini G, Bassani M, Concari C, Soldati A. Exploitation of an Industrial Low-Bandwidth Communication Line for Modulation-Level Synchronization of Voltage Source Converters. Applied Sciences. 2023; 13(1):230. https://doi.org/10.3390/app13010230

Chicago/Turabian StyleLodi Rizzini, Gabriele, Marco Bassani, Carlo Concari, and Alessandro Soldati. 2023. "Exploitation of an Industrial Low-Bandwidth Communication Line for Modulation-Level Synchronization of Voltage Source Converters" Applied Sciences 13, no. 1: 230. https://doi.org/10.3390/app13010230

APA StyleLodi Rizzini, G., Bassani, M., Concari, C., & Soldati, A. (2023). Exploitation of an Industrial Low-Bandwidth Communication Line for Modulation-Level Synchronization of Voltage Source Converters. Applied Sciences, 13(1), 230. https://doi.org/10.3390/app13010230