Design and Implementation of Synthetic Aperture Radar (SAR) Field-Programmable Gate Array (FPGA)-Based Processor

Abstract

:Featured Application

Abstract

1. Introduction

2. Implementation of FPGA-Based On-Board SAR Processor

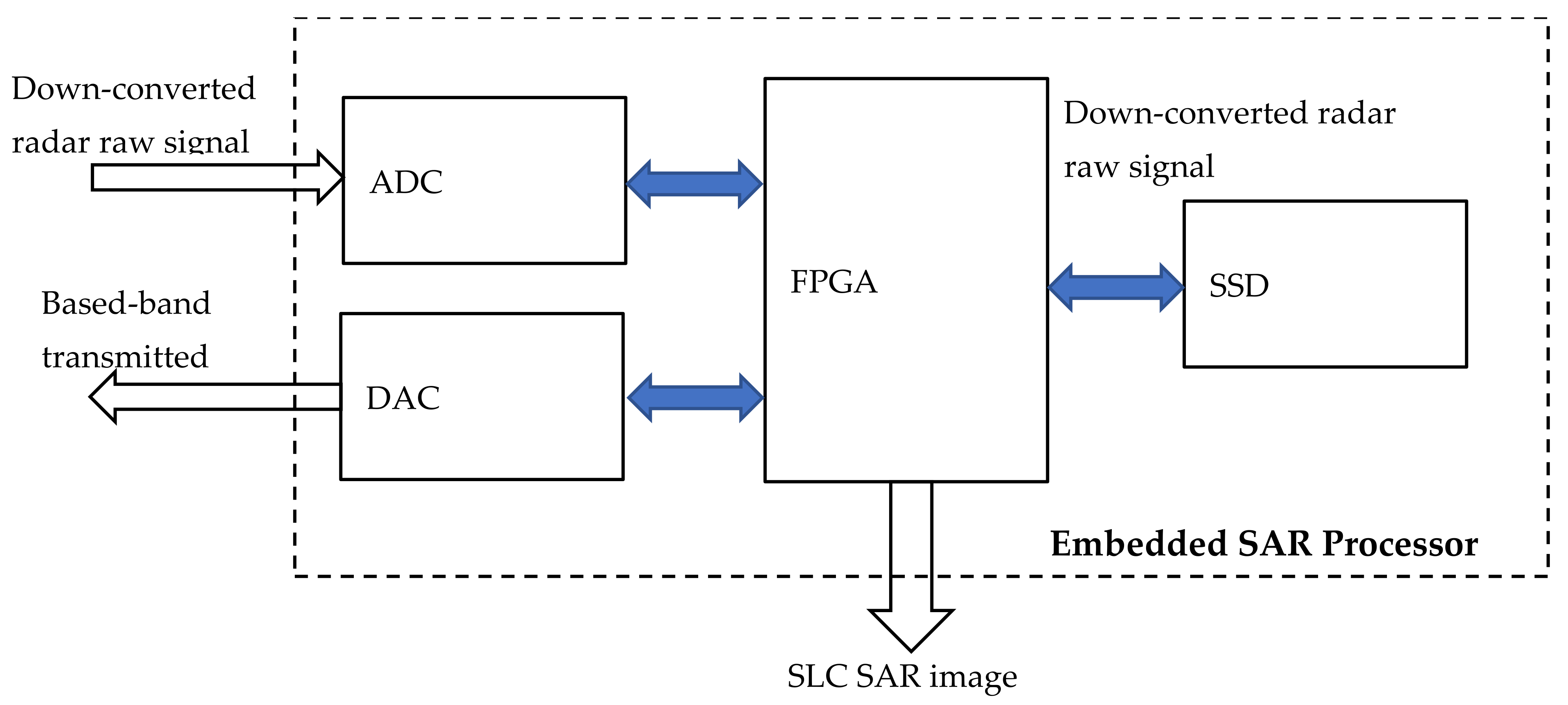

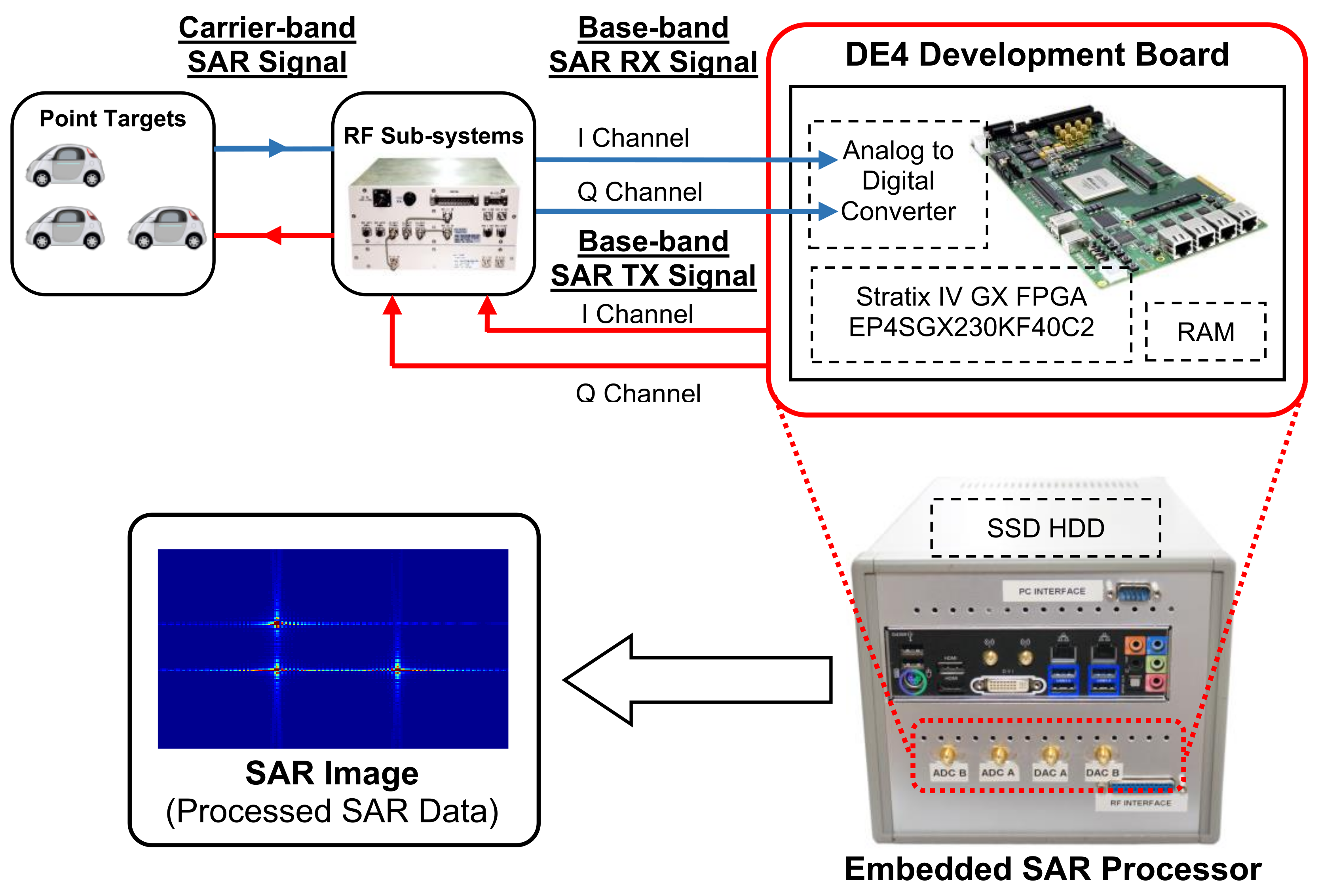

2.1. SAR Processor Architecture

- (i)

- Analogue-to-Digital Converter (ADC) and Digital-to-Analogue Converter (DAC)This module acts as the analogue interface of the system. The ADC digitizes the incoming analogue signal (radar return echo), and the DAC produces the baseband analogue radar signal, with the frequency typically modulated by a continuous wave pulse signal.

- (ii)

- FPGA-based Embedded SAR ProcessorActs as ADC and DAC control and data buffer. This portion of the system interfaces and controls data flow with the DAC and ADC chips. All signalling, including operating modes, are controlled by this block.The main task of the FPGA module is to execute the SAR image-formation algorithm process and output the SAR images. In this module, FFT/IFFT, complex multiplication and other operations are performed on the raw data and produce the correct SAR images.

- (iii)

- Data StorageThe solid-state device (SSD), which it is made of non-volatile memory chips, is used as data storage. The SSD is used to store the received SAR raw data, as well as the processed SAR images.

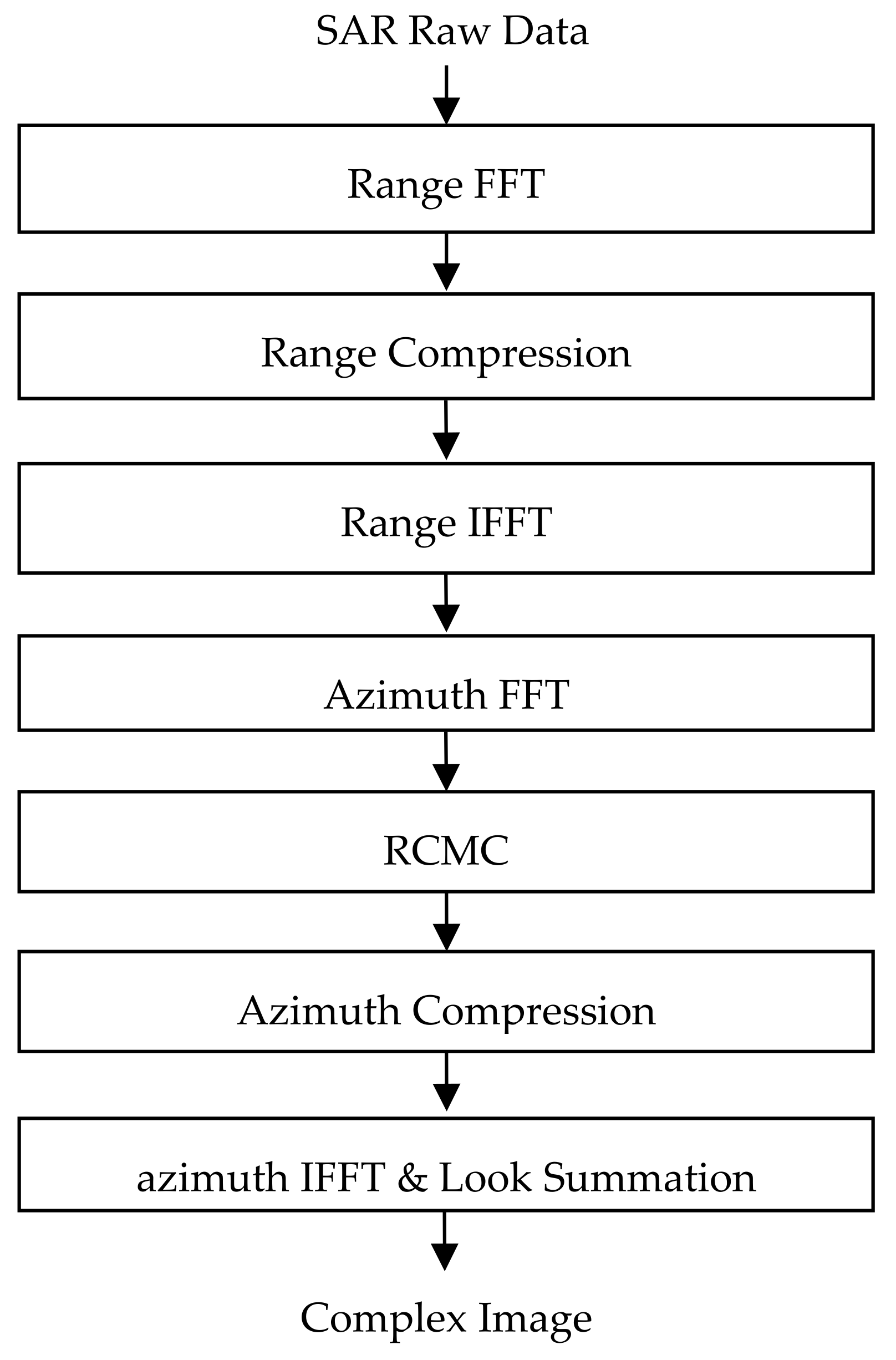

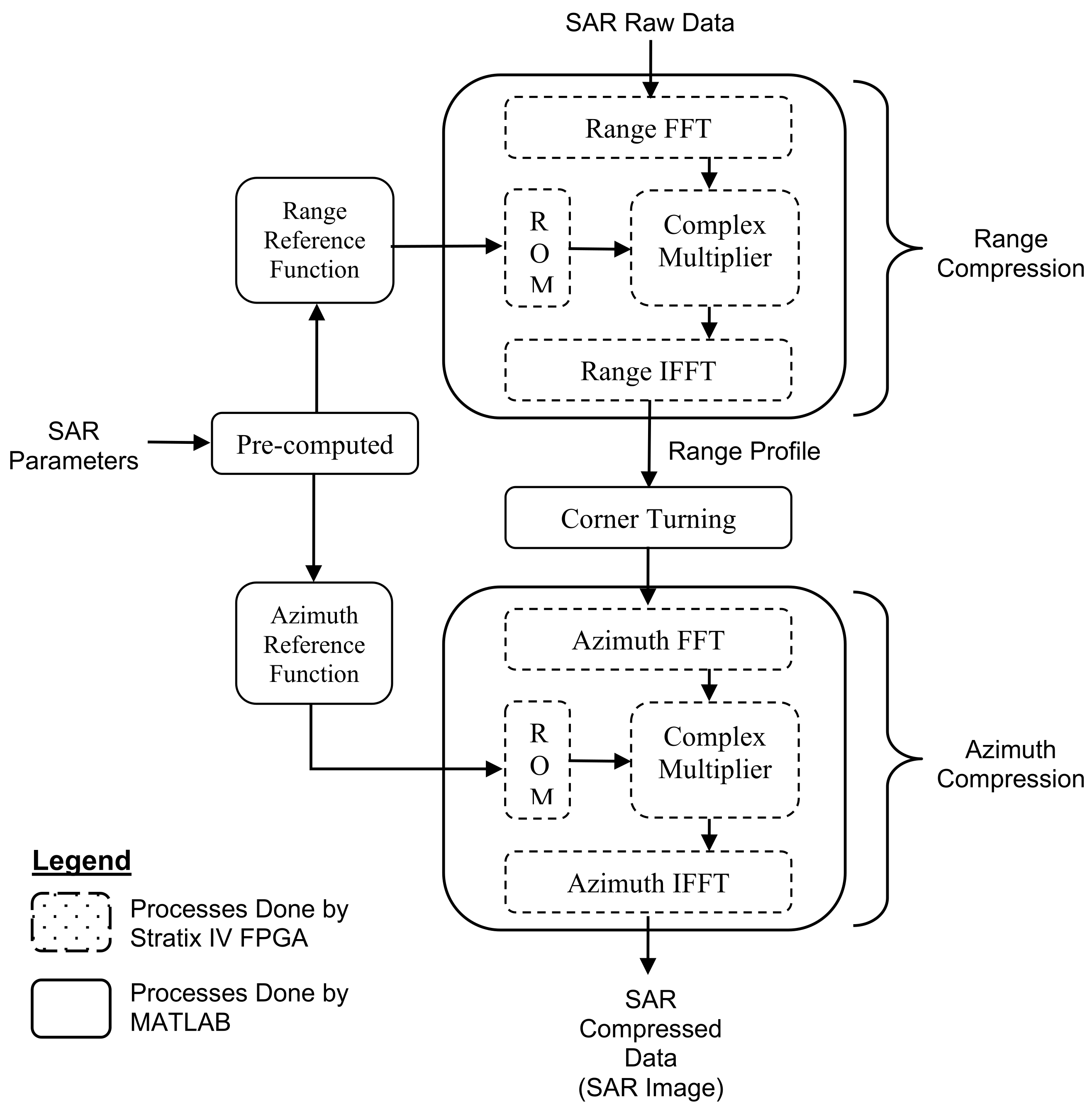

2.2. SAR Image-Formation Algorithm

2.3. SAR Processor Implementation

3. Performance Evaluation of the Proposed SAR Processor

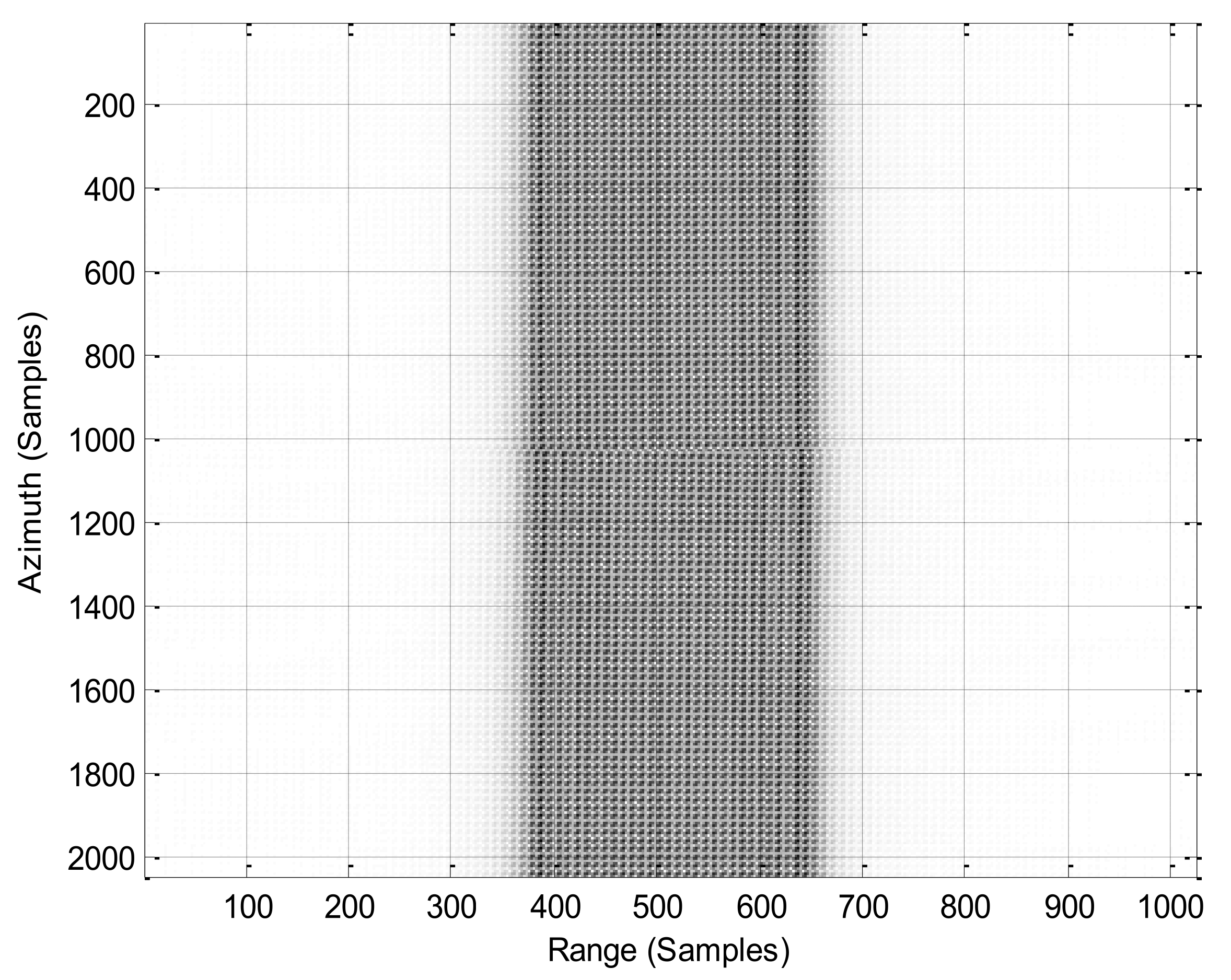

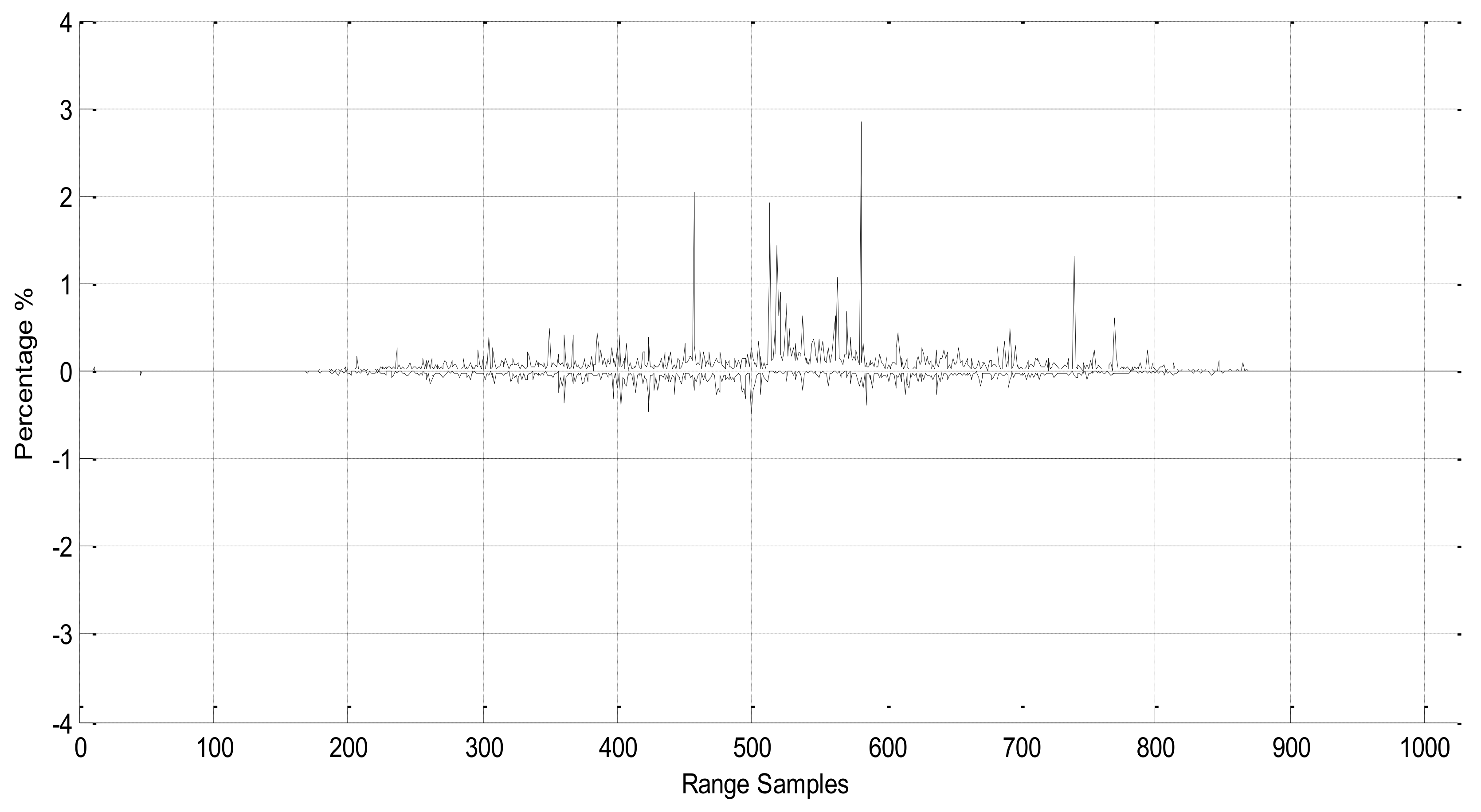

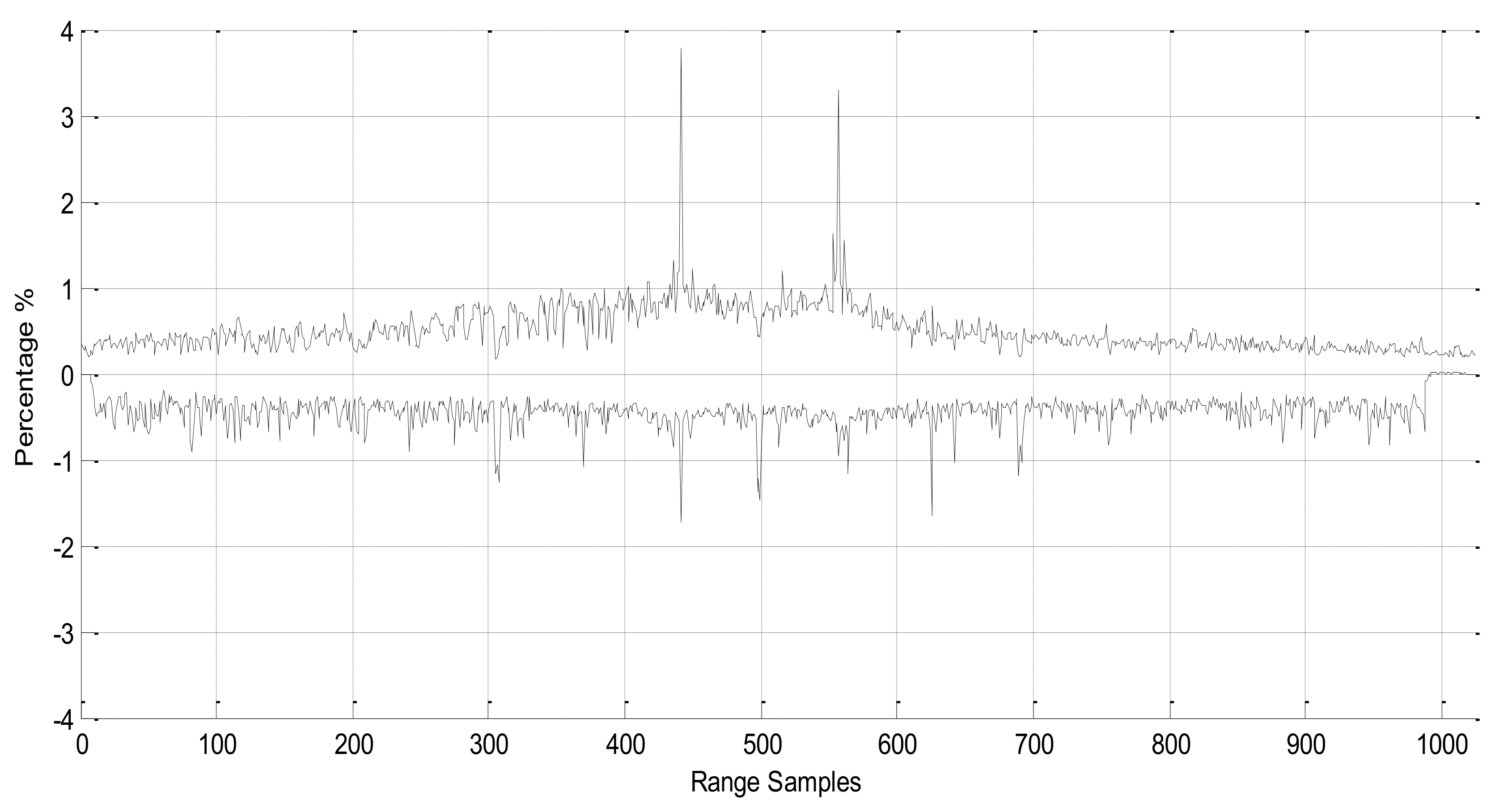

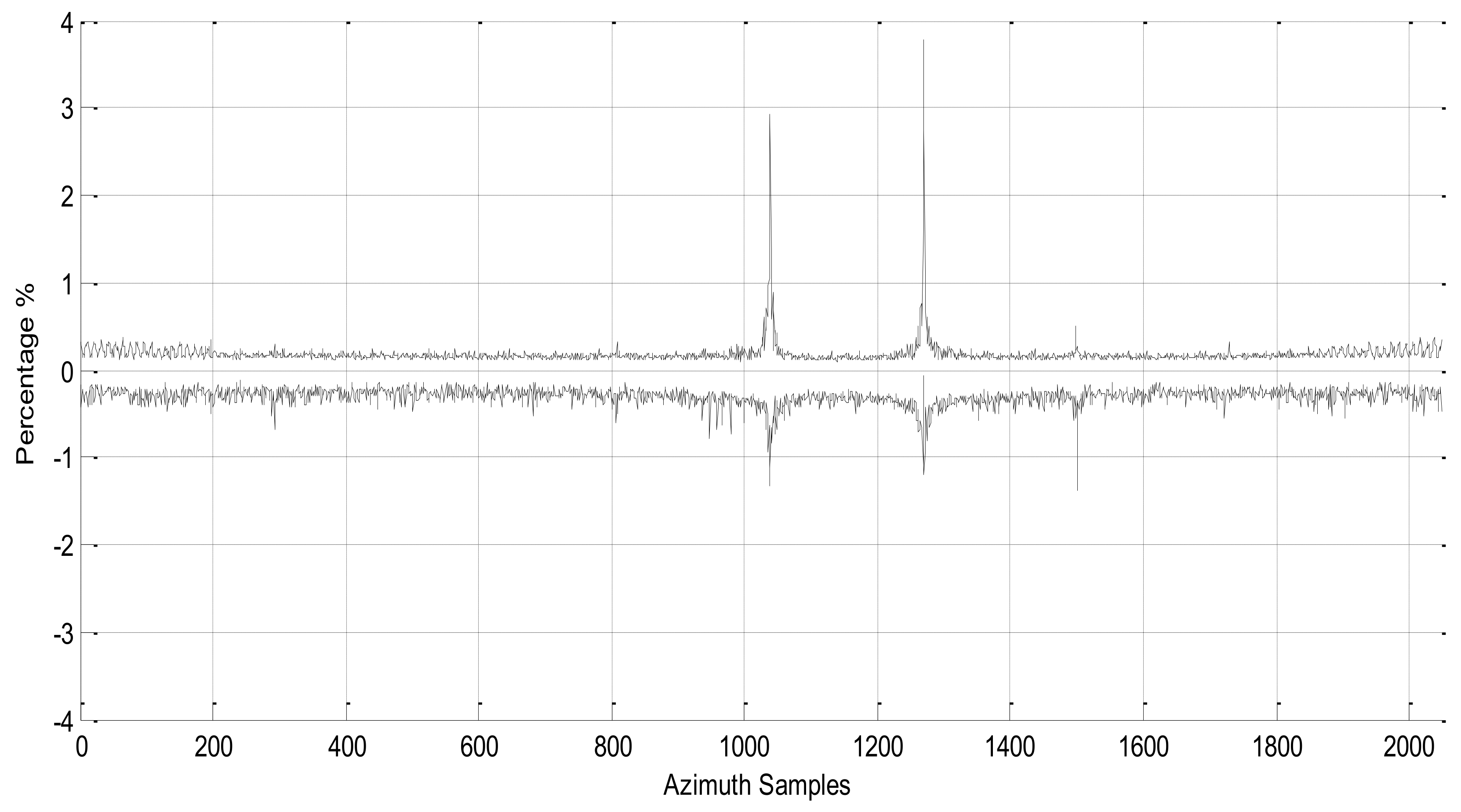

3.1. Precision Comparison of the Proposed SAR Processor and MATLAB-Based SAR Processor

3.2. Timing Performance Analysis

3.3. Hardware Resource Utilisation

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Conflicts of Interest

References

- Stimson, G.W. Introduction to Airborne Radar; SciTech Pub: Tamil Nadu, India, 1998. [Google Scholar]

- Chan, Y.K.; Koo, V.C. An introduction to synthetic aperture radar (SAR). Prog. Electromagn. Res. B 2008, 2, 27–60. [Google Scholar] [CrossRef] [Green Version]

- Wiley, C.A. Synthetic Aperture Radars. IEEE Trans. Aerosp. Electron. Syst. 1984, 21, 440–443. [Google Scholar] [CrossRef]

- Gart, J.H. Electronics and Aerospace Industry in Cold War Arizona, 1945–1968: Motorola, Hughes Aircraft, Goodyear Aircraft; Arizona State University: Tempe, AZ, USA, 2006. [Google Scholar]

- Cutrona, L.; Leith, E.; Palermo, C.; Porcello, L. Optical data processing and filtering systems. IRE Trans. Inf. Theory 1960, 6, 386–400. [Google Scholar] [CrossRef]

- Wu, C. A Digital System to Produce Imagery from SAR Data. In Proceedings of the AIAA Conference: System Design Driven by Sensors, Pasadena, CA, USA, 18–20 October 1976. [Google Scholar]

- Kramer, H.J. Observation of the Earth and its Environment: Survey of Missions and Sensors; Springer Science & Business Media: Berlin/Heidelberg, Germany, 1992. [Google Scholar]

- Prati, C.; Rampa, V. Real-time Parallel Processor for On-board Airborne Synthetic Aperture Radar (SAR). IEEE Int. Symp. Circuits Syst. 1990, 4, 2905–2908. [Google Scholar]

- Meisl, P.G.; Ito, M.R.; Cumming, I.G. Parallel Processors for Synthetic Aperture Radar Imaging. In Proceedings of the IEEE Proceedings of International Conference on Parallel Processing, Ithaca, NY, USA, 12–16 August 1996; Volume 2, pp. 124–131.

- Zhu, L.; Hong, W.; Wang, J.; Yuan, Y. DSP hardware implementation of BAVQ encoding for SAR raw data. In Proceedings of the IEEE Radar Conference, Long Beach, CA, USA, 25 April 2002; pp. 48–52. [Google Scholar]

- Nolte, N.; Simon-Klar, C.; Langemeter, S.; Kirscht, M.; Pirsch, P. Next generation on-board SAR processor for compact airborne systems. In Proceedings of the IEEE Proceedings of International Geoscience and Remote Sensing Symposium, IGARSS’04, Anchorage, AK, USA, 20–24 September 2004; Volume 2, pp. 1514–1517.

- Wang, D.; Ali, M. Synthetic Aperture Radar on low power multi-core Digital Signal Processor. In Proceedings of the IEEE Conference on High Performance Extreme Computing (HPEC), Waltham, MA USA, 10–12 September 2012; pp. 1–6. [Google Scholar]

- Long, T.; Zeng, T.; Hu, C.; Dong, X.; Chen, L.; Liu, Q.; Wang, Y. High resolution radar real-time signal and information processing. China Commun. 2019, 16, 105–133. [Google Scholar]

- Lee, Y.-C.; Chan, Y.K.; Koo, V. Design and Implementation of FPGA-Based FFT Co-Processor Using Verilog Hardware Description Language. Prog. Electromagn. Res. B 2021, 92, 47–70. [Google Scholar] [CrossRef]

- Chan, Y.K.; Lee, Y.C.; Koo, V.C. Synthetic Aperture Radar (SAR) Signal Simulation Using Range Doppler Algorithm (RDA). Def. S T Tech. Bull. 2020, 13, 295–315. [Google Scholar]

- Le, C.; Chan, S.; Cheng, F.; Fang, W.; Fischman, M.; Hensley, S.; Johnson, R.; Jourdan, M.; Marina, M.; Parham, B.; et al. Onboard FPGA-based SAR Processing for Future Spaceborne Systems. In Proceedings of the IEEE in Radar Conference, Philadelphia, PA, USA, 29 April 2004; pp. 15–20. [Google Scholar]

- Leśnik, C.; Kawalec, A.; Serafin, P. A real time SAR processor implementation with FPGA. WIT Trans. Model. Simul. 2011, 51, 435–444. [Google Scholar]

- Lou, Y.; Clark, D.; Marks, P.; Muellerschoen, R.J.; Wang, C.C. Onboard Radar Processor Development for Rapid Response to Natural Hazards. IEEE J. Sel. Top. Appl. Earth Obs. Remote Sens. 2016, 9, 2770–2776. [Google Scholar] [CrossRef]

- Yang, C.; Li, B.; Chen, L.; Wei, C.; Xie, Y.; Chen, H.; Yu, W. A Spaceborne Synthetic Aperture Radar Partial Fixed-Point Imaging System Using a Field-Programmable Gate Array—Application-Specific Integrated Circuit Hybrid Heterogeneous Parallel Acceleration Technique. Sensors 2017, 17, 1493. [Google Scholar] [CrossRef]

- Liu, R.; Zhu, D.; Wang, D.; Du, W. FPGA Implementation of SAR Imaging Processing System. In Proceedings of the 2019 6th Asia-Pacific Conference on Synthetic Aperture Radar (APSAR), Xiamen, China, 26–29 November 2019; pp. 1–5. [Google Scholar]

- Kuon, I.; Rose, J. Measuring the Gap Between FPGAs and ASICs. IEEE Trans. Comput.-Aided Des. Integr. Circuits Systems. 2008, 26, 203–215. [Google Scholar] [CrossRef] [Green Version]

- Wu, C.; Liu, K.Y.; Jin, M. Modeling and a Correlation Algorithm for Spaceborne SAR Signals. IEEE Trans. Aerosp. Electron. Syst. 1982, 18, 563–575. [Google Scholar]

- Jin, M.Y.; Wu, C. A SAR Correlation Algorithm Which Accommodates Large Range Migration. IEEE Trans. Geosci. Remote Sens. 1984, 22, 592–597. [Google Scholar] [CrossRef]

- Cumming, I.G.; Wong, F.H. Digital Processing of Synthetic Aperture Radar Data. Artech House 2005, 1, 108–110. [Google Scholar]

- Cafforio, C.; Prati, C.; Rocca, F. SAR focusing using seismic migration techniques. IEEE Trans. Aerosp. Electron. Syst. 1991, 27, 194–207. [Google Scholar] [CrossRef]

- Li, A.; Lofeld, O. Two-Dimensional SAR Processing in the Frequency Domain. In Proceedings of the IGARSS’91, Espoo, Finland, 3–6 June 1991; pp. 1065–1068. [Google Scholar]

- Scheuer, T.E.; Wong, F.H. Comparison of SAR Processor Based on a Wave Equation Formulation. In Proceedings of the IGARSS’91, Espoo, Finland, 3–6 June 1991; Volume 2, pp. 635–639. [Google Scholar]

- Bamler, R. A comparison of Range-Dopper and Wavenumber Domain SAR Focusing Algorithms. IEEE Trans. Geosci. Remote Sens. 1992, 30, 706–713. [Google Scholar] [CrossRef]

- Prati, C.; Rocca, E. Focusing SAR Data with time-varying Doppler Centroid. IEEE Trans. Geosci. Remote Sens. 1992, 30, 550–558. [Google Scholar] [CrossRef]

- Raney, R.K. An Exact Wide Field Digital Imaging Algorithm. Int. Remote Sens. 1992, 13, 991–998. [Google Scholar] [CrossRef]

- Moreira, A.; Huang, Y. Airborne SAR processing of highly squinted SAR data using a chirp scaling approach with integrated motion compensation. IEEE Trans. Geosci. Remote Sens. 1994, 32, 1029–1040. [Google Scholar] [CrossRef]

- Raney, R.K.; Runge, H.; Bamler, R.; Cumming, I.G.; Wong, F.H. Precision SAR Processing Using Chirp Scaling. IEEE Trans. Geosci. Remote Sens. 1994, 32, 786–799. [Google Scholar] [CrossRef]

- Davidson, G.W.; Cumming, I.G.; Ito, M.R. A Chirp Scaling Approach for Processing Squint Mode SAR Data. IEEE Trans. Aerosp. Electron. Syst. 1996, 32, 121–133. [Google Scholar] [CrossRef]

- Moreira, A.; Mitermayer, J.; Scheiber, R. Extended Chirp Scaling Algorithm for Air and Spacebome SAR Data Processing in Stripmap And Scansar Imaging Modes. IEEE Trans. Geosci. Remote Sens. 1996, 34, 1123–1136. [Google Scholar] [CrossRef]

- Zhang, F.; Li, G.; Li, W.; Hu, W.; Hu, Y. Accelerating Spaceborne SAR Imaging Using Multiple CPU/GPU Deep Collaborative Computing. Sensors 2016, 16, 494. [Google Scholar] [CrossRef] [Green Version]

- Gu, C.F.; Chang, W.; Li, X.; Liu, Z. Multi-Core DSP Based Parallel Architecture for FMCW SAR Real-Time Imaging. Radioengineering 2015, 24, 1084–1090. [Google Scholar] [CrossRef]

- Bierens, B.J. Vollmuller On-board Payload Data Processor (OPDP) and its application in advanced multi-mode, multi-spectral and interferometric satellite SAR instruments. In Proceedings of the 9th European Conference on Synthetic Aperture Radar, Nuremberg, Germany, 23–26 April 2012. [Google Scholar]

- Desai, N.M.; Kumar, B.S.; Sharma, R.K.; Kunal, A.; Gameti, R.B.; Gujraty, V.R. Near Real Time SAR Processors for ISRO’s Multi-Mode RISAT-I and DMSAR. In Proceedings of the 7th European Conference on Synthetic Aperture Radar, Friedrichshafen, Germany, 2–5 June 2008. [Google Scholar]

- Franceschetti, G.; Tesauro, M.; Strollo, A.G.M.; Napoli, E.; Cimino, C.; Spirito, P.; Mazzeo, A.; Mazzocca, N. A VLSI architecture for real time processing of one-bit coded SAR signals. In Proceedings of the URSI International Symposium on Signals, Systems, and Electronics, Pisa, Italy, 29 September–2 October 1998. [Google Scholar]

| Name of Parameters | Symbols | Value (Units) |

|---|---|---|

| Slant-range centre | R(ηc) | 30 km |

| Transmitted pulse duration | Τ | 2.5 μs |

| Chirp-signal bandwidth | B | 50 MHz |

| Range-chirp signal sweep rate | β | 20 MHz/μs |

| Range resolution | δR | 3-m |

| Range-sampling frequency | fs | 100 MHz |

| Carrier-signal frequency | f0 | 5.3 GHz |

| Azimuth-sampling frequency (PRF) | fa | 350 Hz |

| Radar-platform velocity | Vr | 150 ms−1 |

| Real antenna-aperture length | La | 1 m |

| Modules | Range Compression (2048 Azimuth Lines) | Azimuth Compression (4096 Range Lines) | Total Time (ms) to form a SAR Image | ||||

|---|---|---|---|---|---|---|---|

| 4096 FFT | Complex Multiplier | 4096 IFFT | 2048 FFT | Complex Multiplier | 2048 IFFT | ||

| Operation Time (ms) | 345.27 | 24.66 | 345.27 | 320.6 | 24.66 | 320.6 | 1381.06 |

| Area of Hardware Resources | Resources Reduction | |

|---|---|---|

| Altera IP 2048-FFT/IFFT vs. Proposed 2048-FFT/IFFT | Altera IP 4096-FFT/IFFT vs. Proposed 4096-FFT/IFFT | |

| Combinational ALUTs | 68.16% | 55.46% |

| Total dedicated logic registers | 79.84% | 80.08% |

| Total pins | 20.00% | 20.00% |

| Total block-memory bits | 44.78% | 43.44% |

| M9K block memory | 38.46% | 36.84% |

| DSP block 18-bit elements | 33.33% | 66.67% |

| Area of Hardware Resources | Range Compression | Azimuth Compression | Total Hardware Utilisation | ||||||

|---|---|---|---|---|---|---|---|---|---|

| 4096 FFT | Complex Multiplier | ROM | 4096 IFFT | 2048 FFT | Complex Multiplier | ROM | 2048 IFFT | ||

| Combinational ALUTs | 1602 | 83 | 574 | 1602 | 1088 | 83 | 574 | 1088 | 6694 |

| Total dedicated logic registers | 1085 | 88 | 32 | 1085 | 1135 | 88 | 32 | 1135 | 4680 |

| Total oins | 68 | 74 | 45 | 68 | 68 | 74 | 45 | 68 | 510 |

| Total block-memory bits | 352,256 | 98 | 55 | 352,256 | 172,032 | 98 | 55 | 172,032 | 1,048,882 |

| M9K block memory | 41 | 0 | 0 | 41 | 24 | 0 | 0 | 24 | 130 |

| DSP block 18-bit elements | 8 | 2 | 0 | 8 | 8 | 2 | 0 | 8 | 36 |

| Year | Schemes | Data Granularity | Working Frequency | Power Consumption | Processing Time |

|---|---|---|---|---|---|

| 2020 | PFGA (proposed) | 4096 × 2048 | 340 MHz | 0.905 W [14] | 1.38 s |

| 2019 | FPGA [20] | 4096 × 2048 | 200 MHz | - | 2.1 s |

| 2018 | SoC [13] | 16,384 × 16,384 | 200 MHz | <8 W | <8 s |

| 2017 | FPGA + ASIC [17] | 16,384 × 16,384 | 100 MHz | 21 W | 12.1 s |

| 2016 | FPGA + Microprocess [16] | 6472 × 3328 | - | 68 W | 8 s |

| 2016 | CPU + GPU [35] | 32,768 × 32,768 | - | >330 W | 2.8 s |

| 2015 | Multi-DSP [36] | 4096 × 4096 | 100 MHz | - | 2.178 s |

| 2012 | CPU + ASIC [37] | 1024 × 1024 | 100 MHz | 10 W | - |

| 2008 | Multi-DSP [38] | 4096 × 4096 | 100 MHz | 35 W | 13 s |

| 1998 | ASIC [39] | 1020 × 200 | 10 MHz | 2 W | - |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chan, Y.K.; Lee, Y.C.; Koo, V.C. Design and Implementation of Synthetic Aperture Radar (SAR) Field-Programmable Gate Array (FPGA)-Based Processor. Appl. Sci. 2022, 12, 1808. https://doi.org/10.3390/app12041808

Chan YK, Lee YC, Koo VC. Design and Implementation of Synthetic Aperture Radar (SAR) Field-Programmable Gate Array (FPGA)-Based Processor. Applied Sciences. 2022; 12(4):1808. https://doi.org/10.3390/app12041808

Chicago/Turabian StyleChan, Yee Kit, Yung Chong Lee, and Voon Chet Koo. 2022. "Design and Implementation of Synthetic Aperture Radar (SAR) Field-Programmable Gate Array (FPGA)-Based Processor" Applied Sciences 12, no. 4: 1808. https://doi.org/10.3390/app12041808

APA StyleChan, Y. K., Lee, Y. C., & Koo, V. C. (2022). Design and Implementation of Synthetic Aperture Radar (SAR) Field-Programmable Gate Array (FPGA)-Based Processor. Applied Sciences, 12(4), 1808. https://doi.org/10.3390/app12041808