Radio Frequency Reflectometry of Single-Electron Box Arrays for Nanoscale Voltage Sensing Applications

Abstract

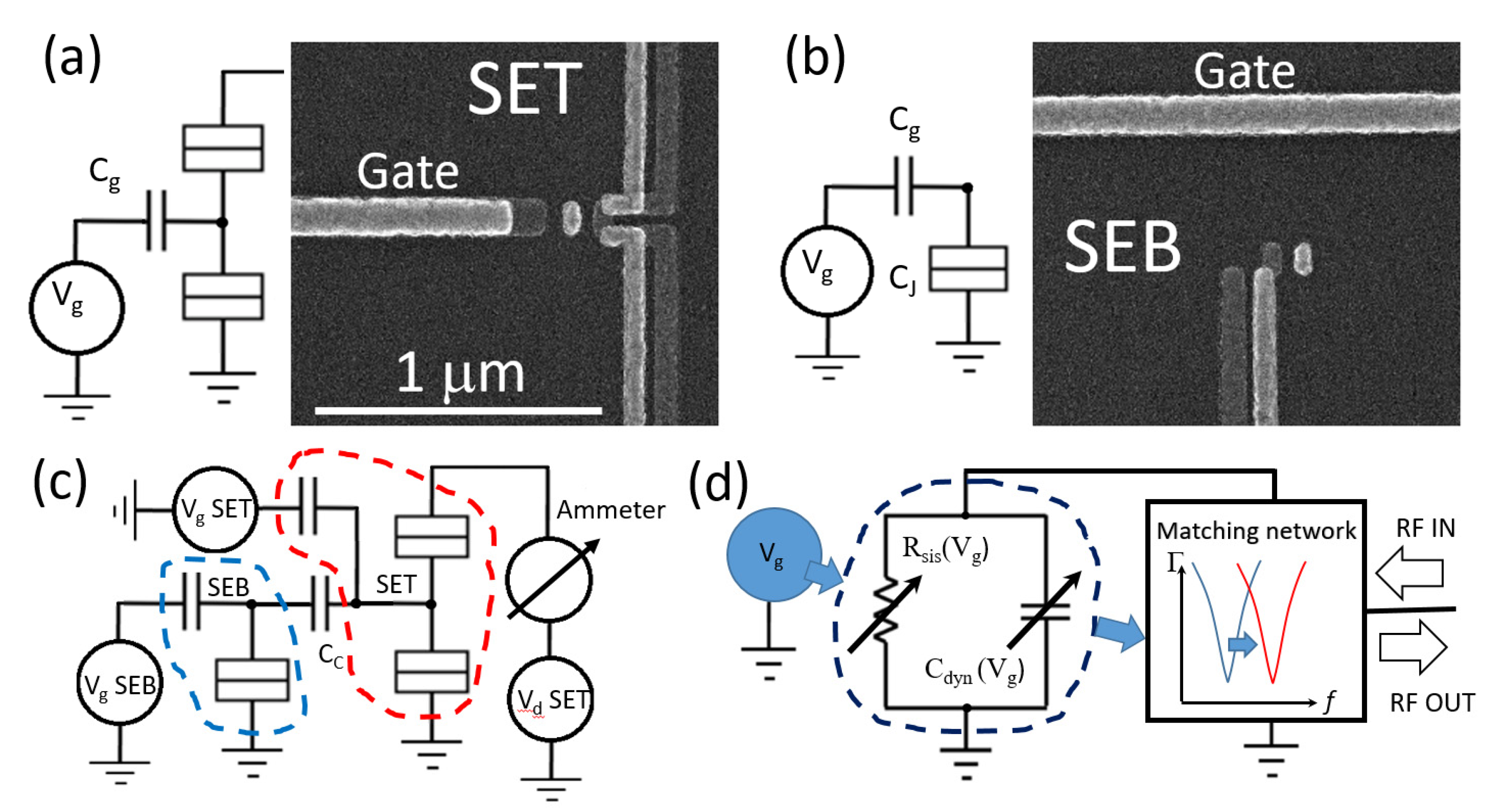

1. Introduction

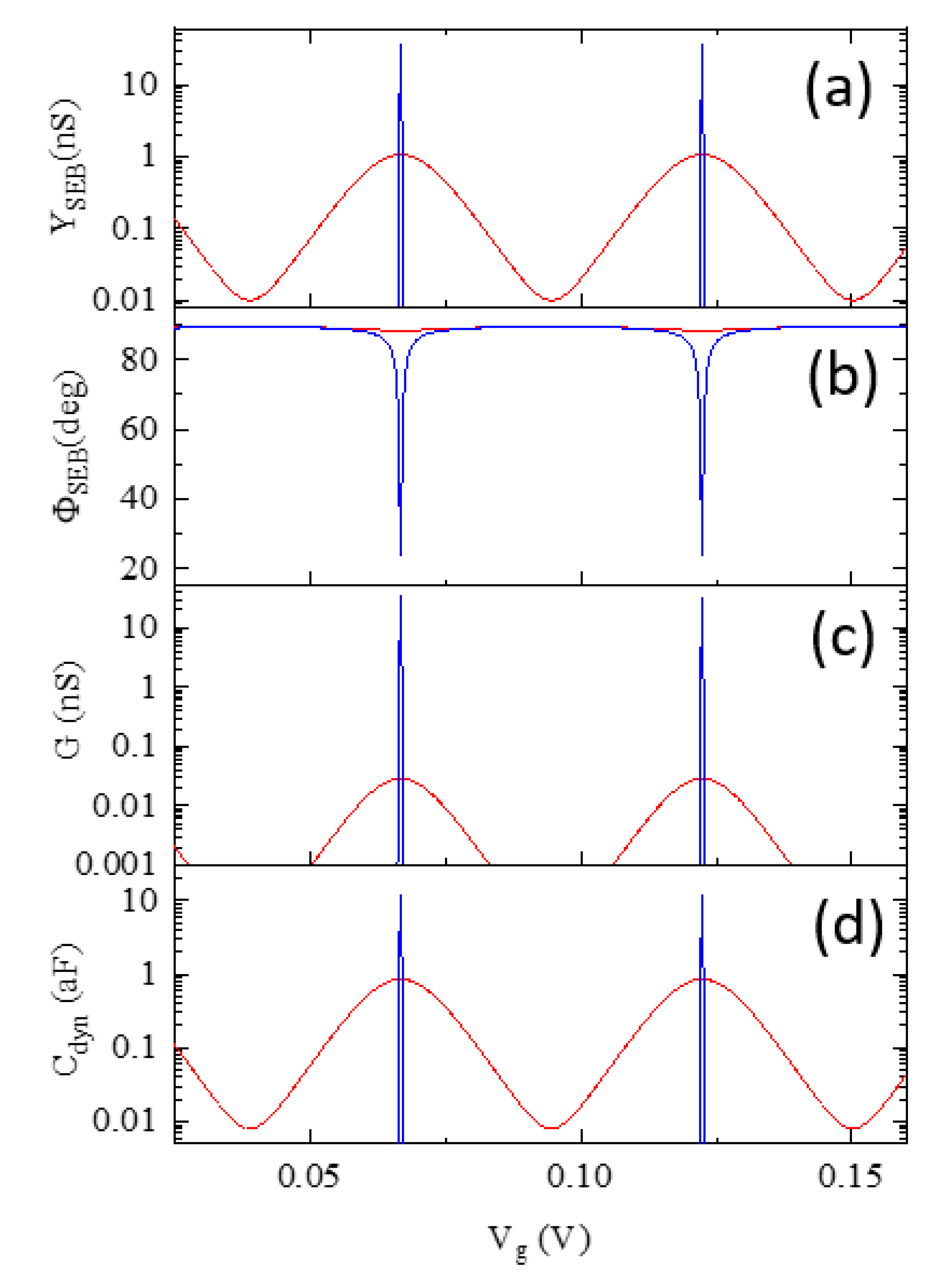

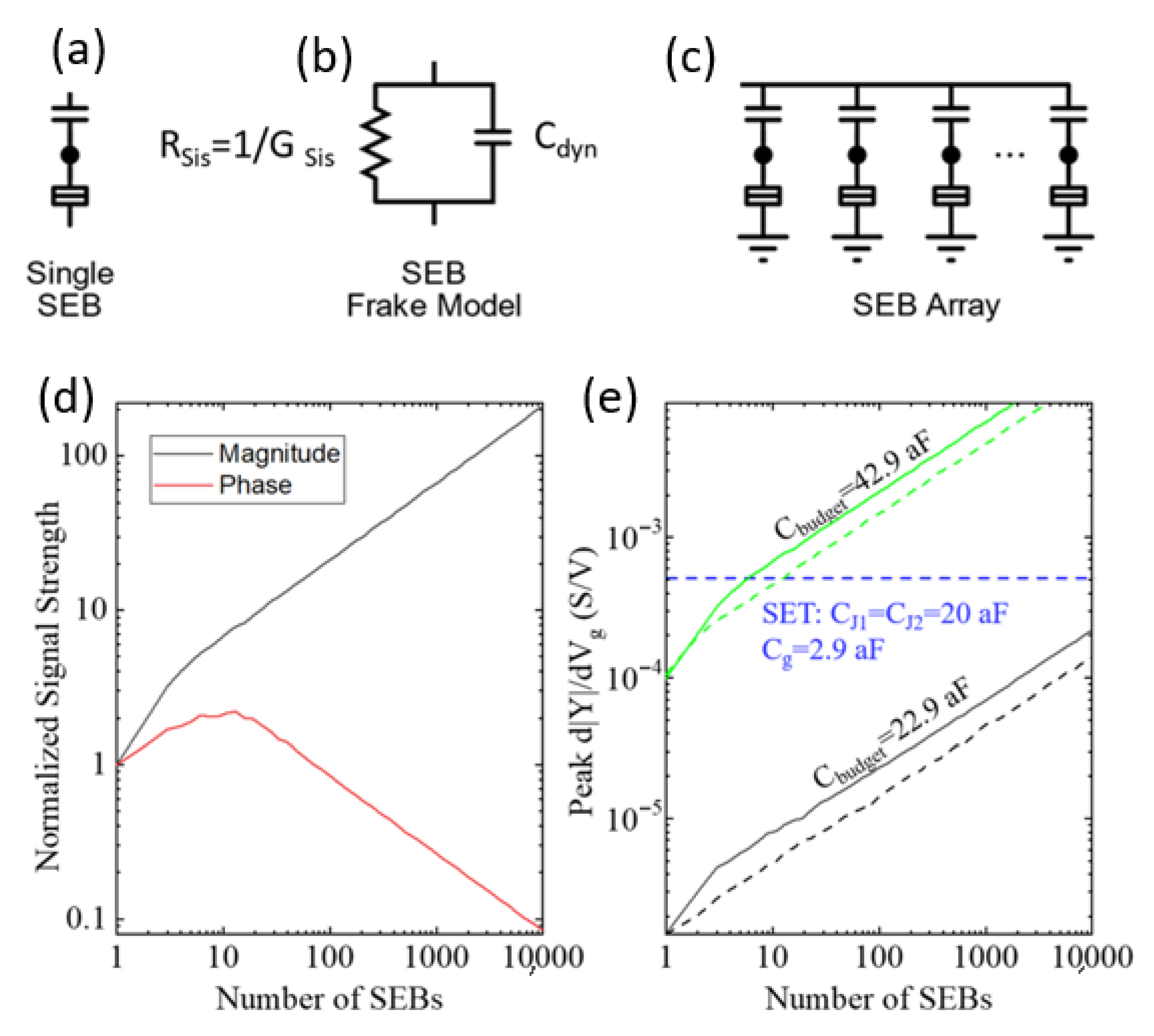

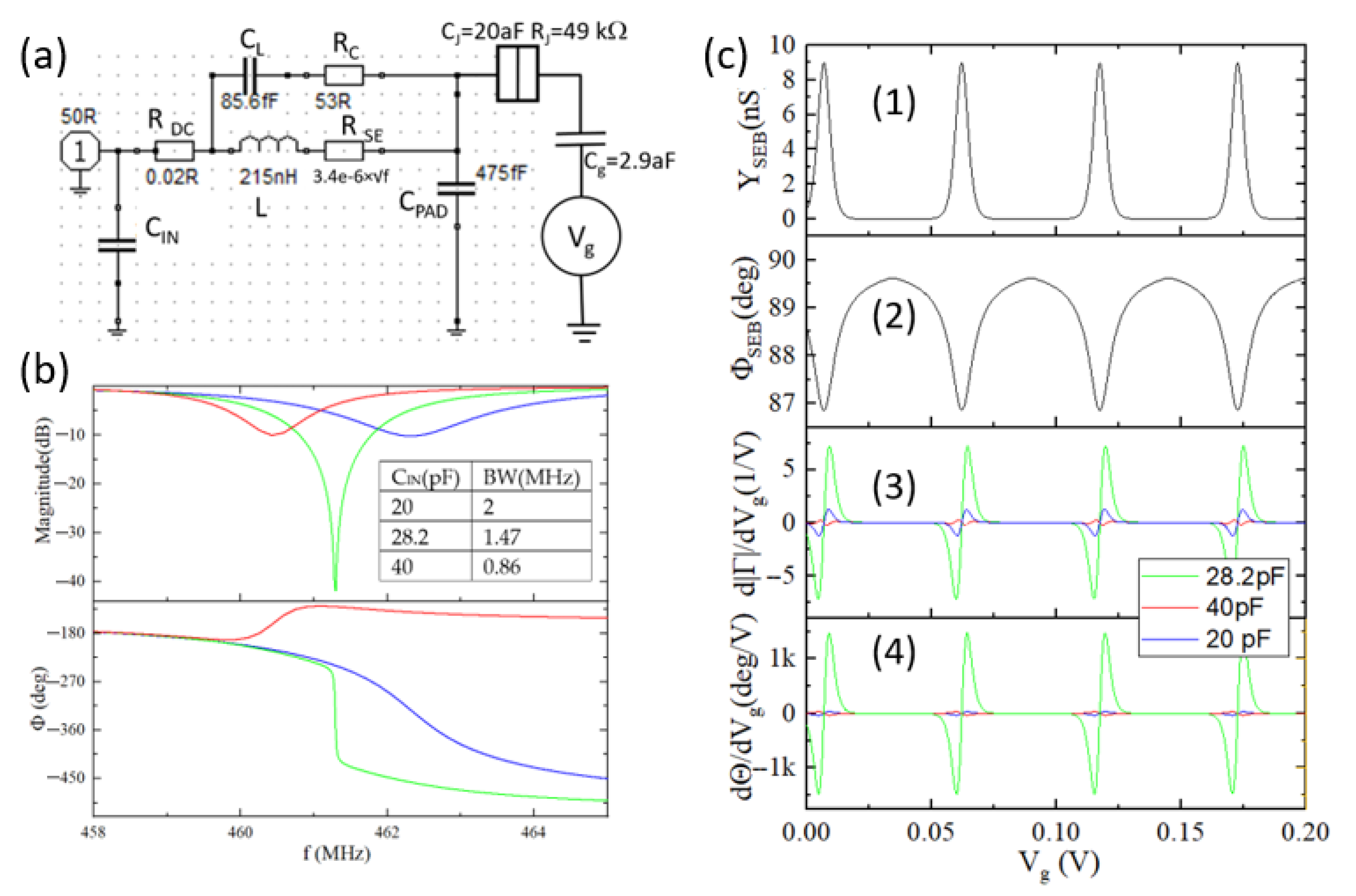

2. Analysis and Simulations of SEB Arrays for Probing Using RF Reflectometry

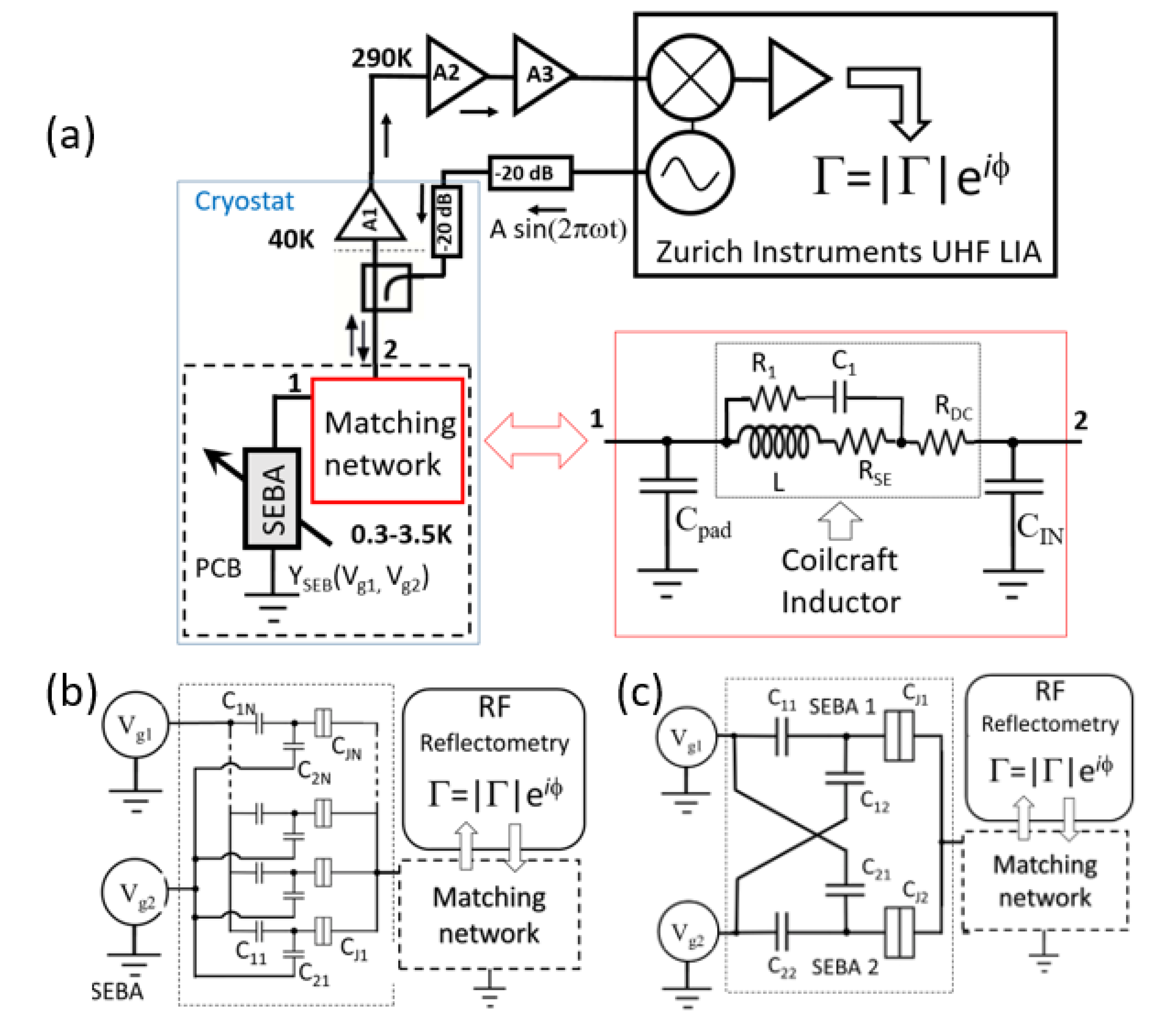

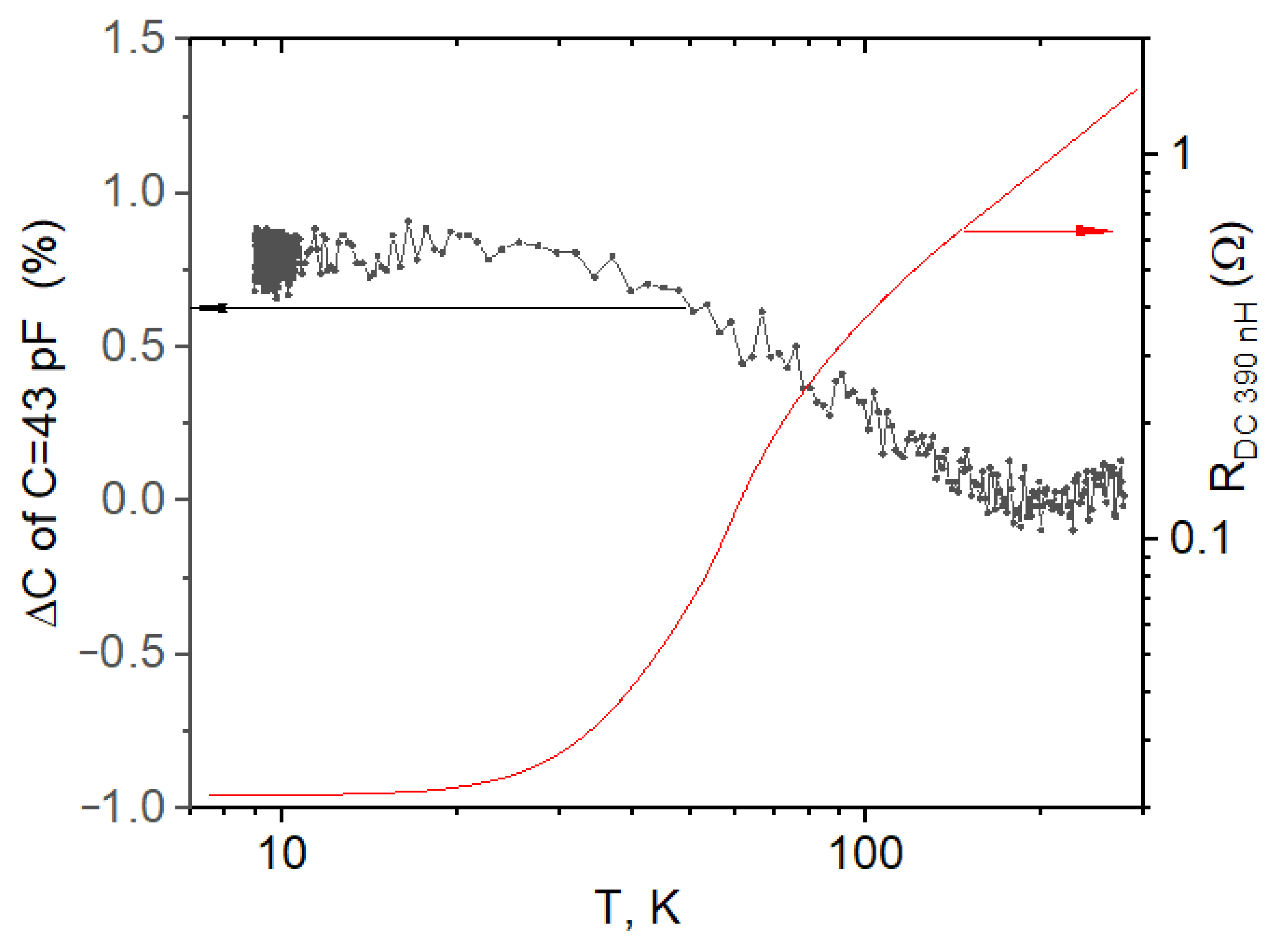

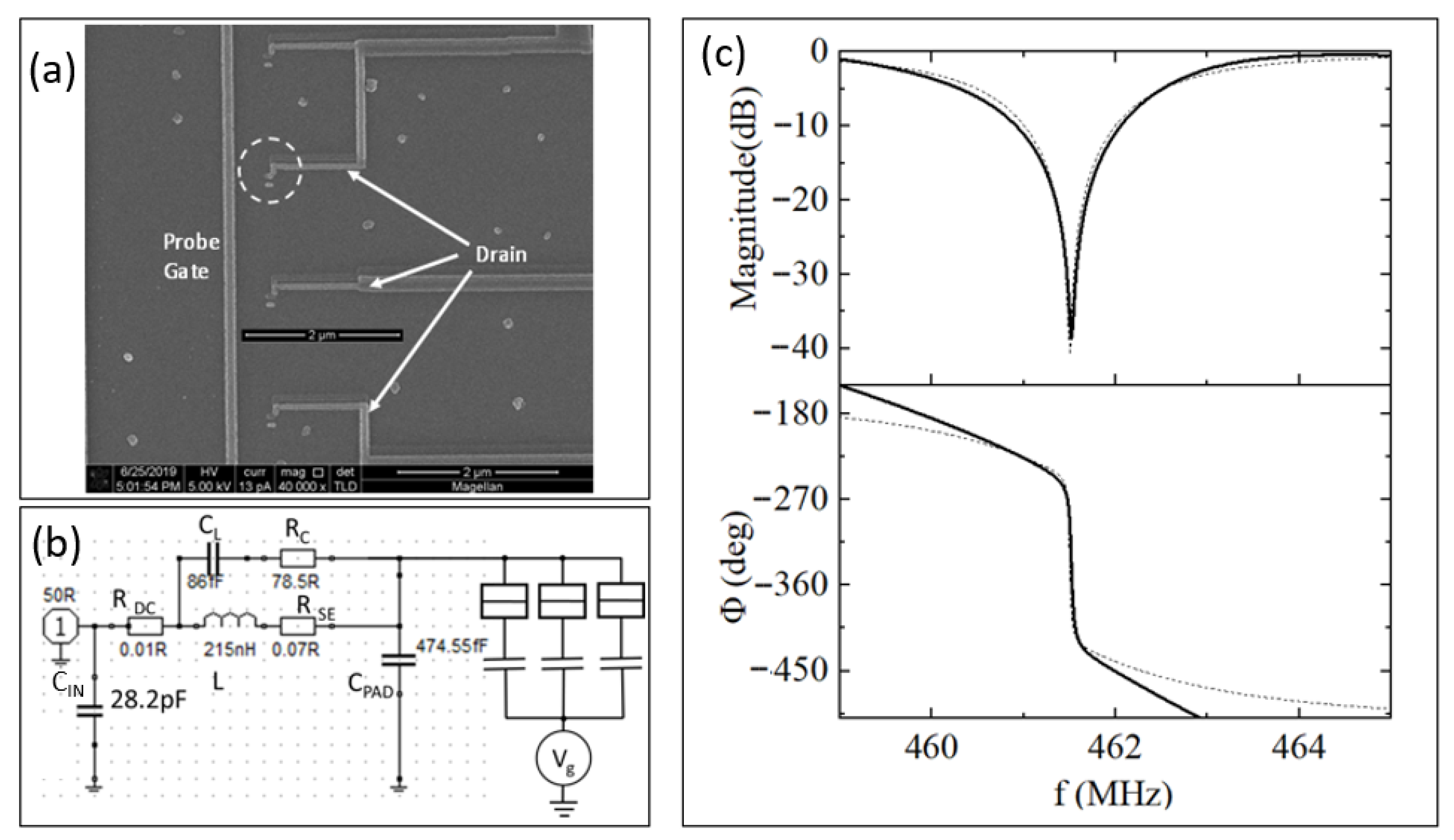

3. Experimental Setup: Reflectometer and Matching Network Considerations

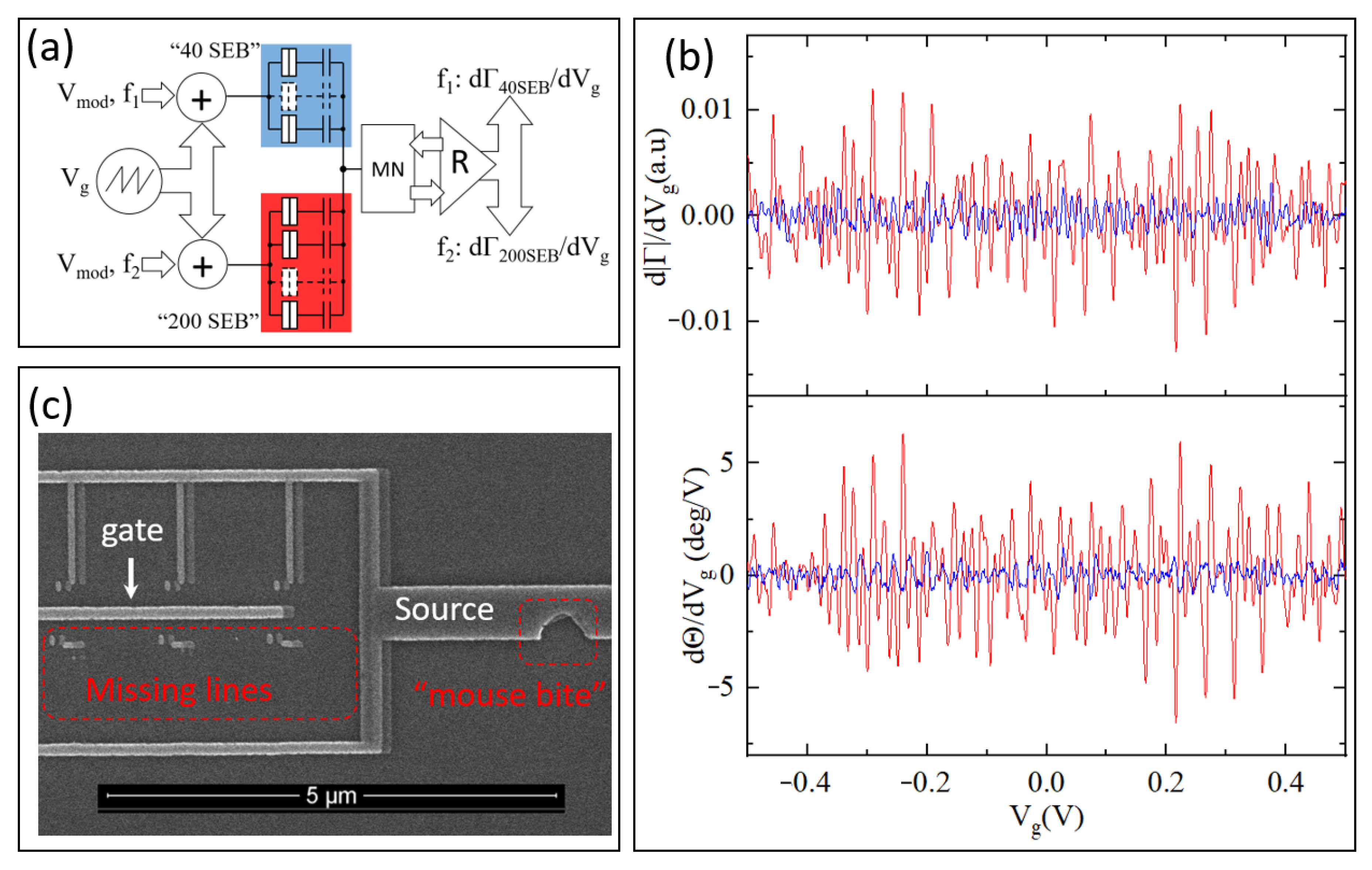

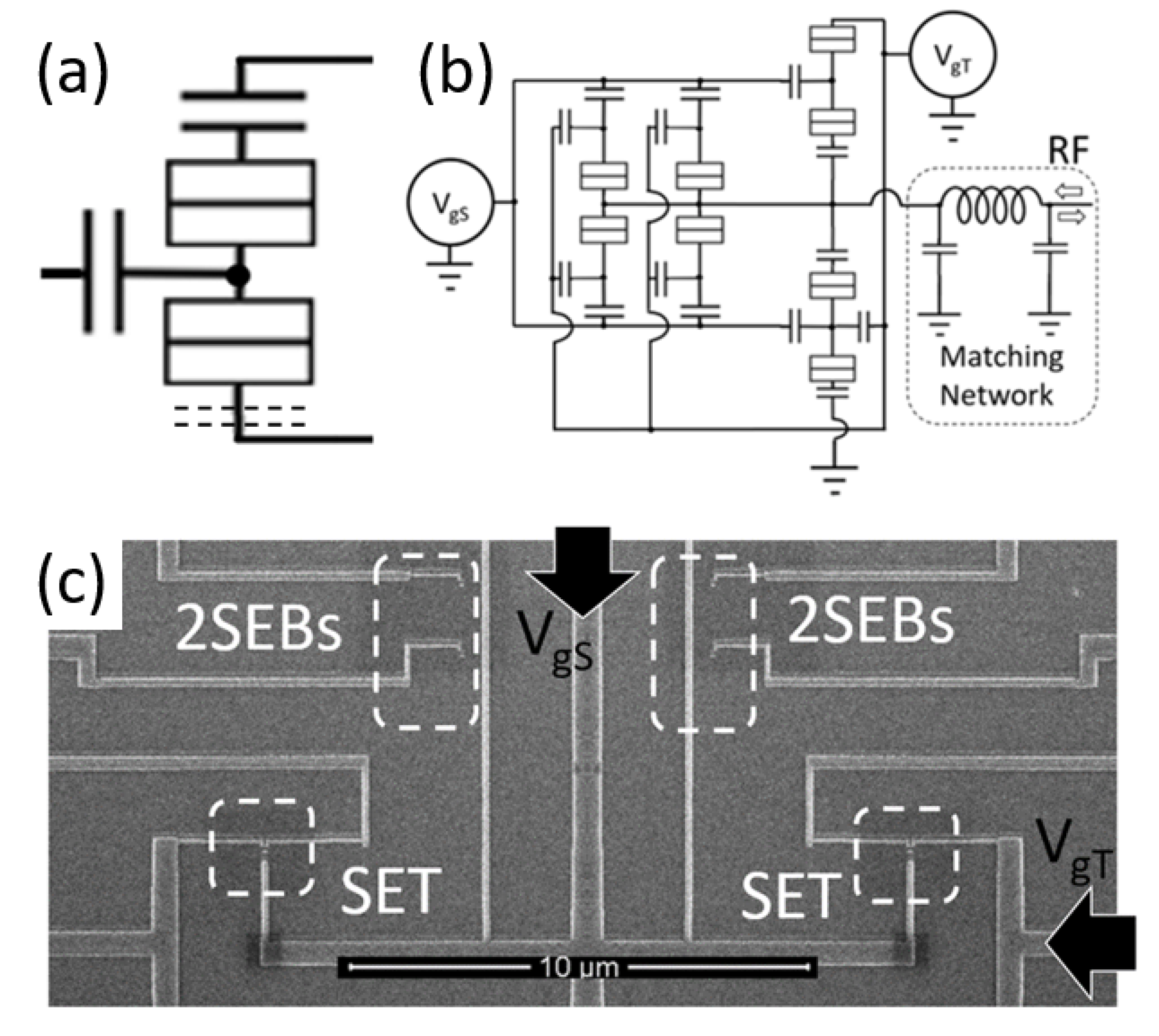

3.1. Hardware Configuration

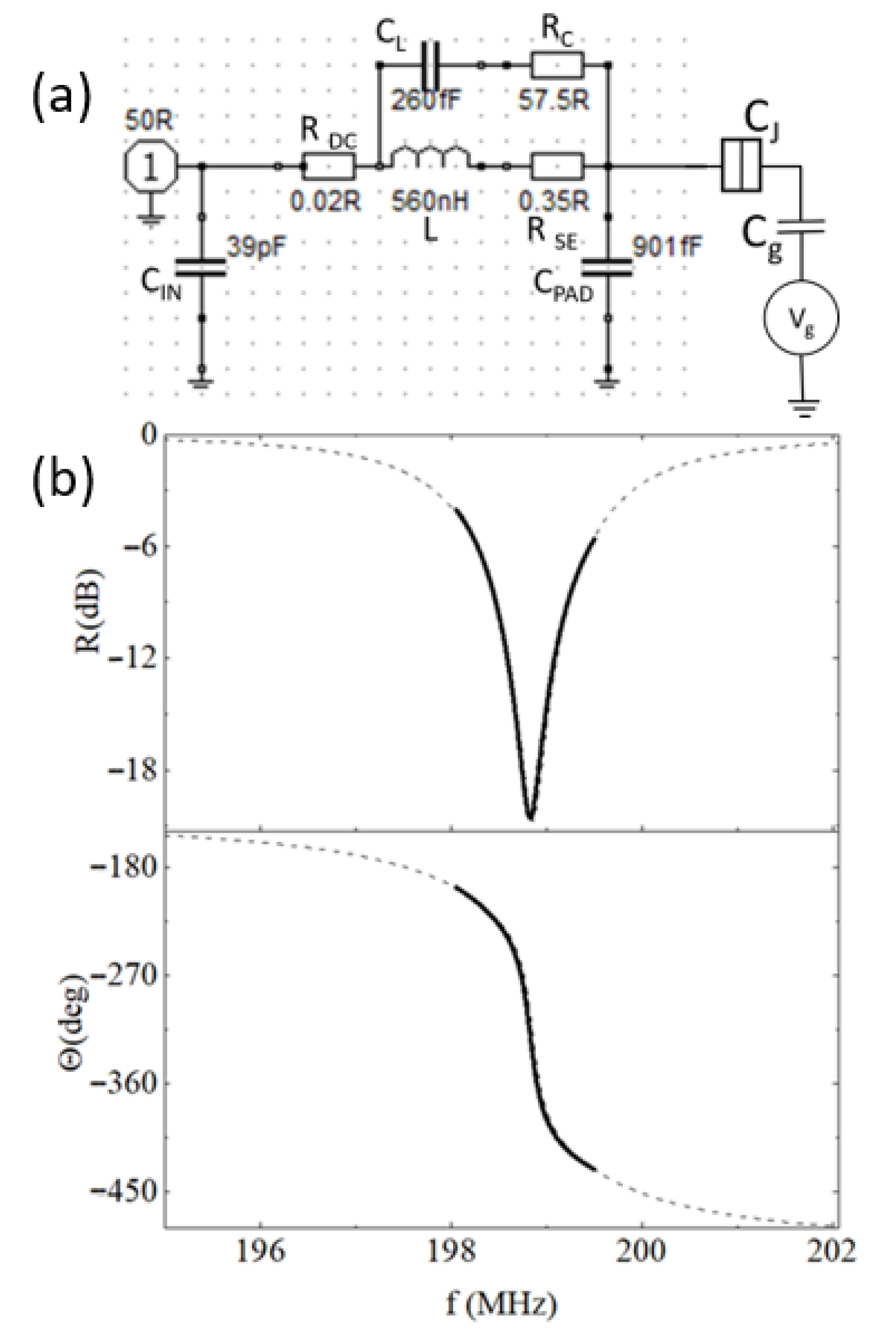

3.2. Matching Network Design

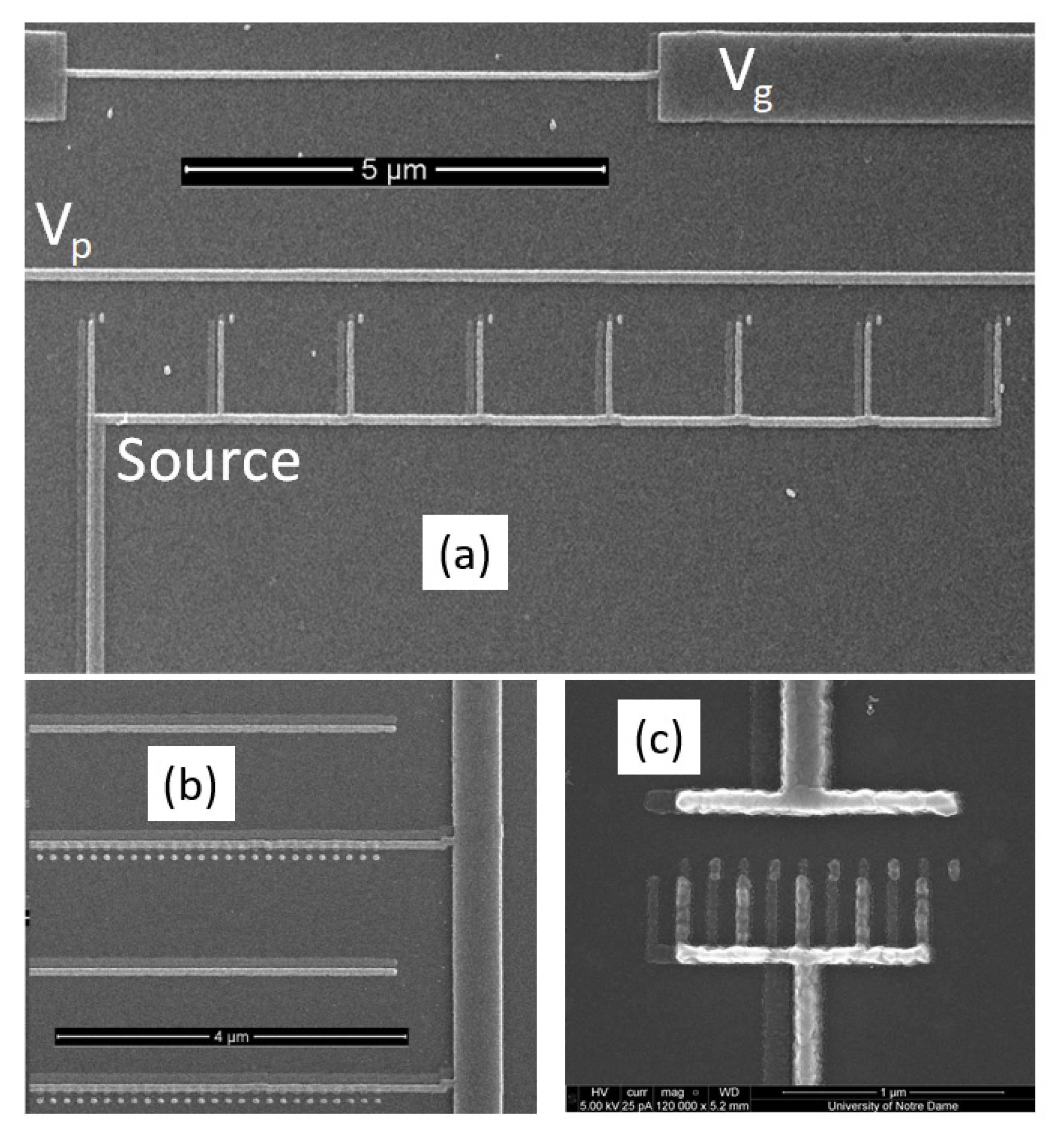

4. Fabrication

5. Experimental Results and Discussion

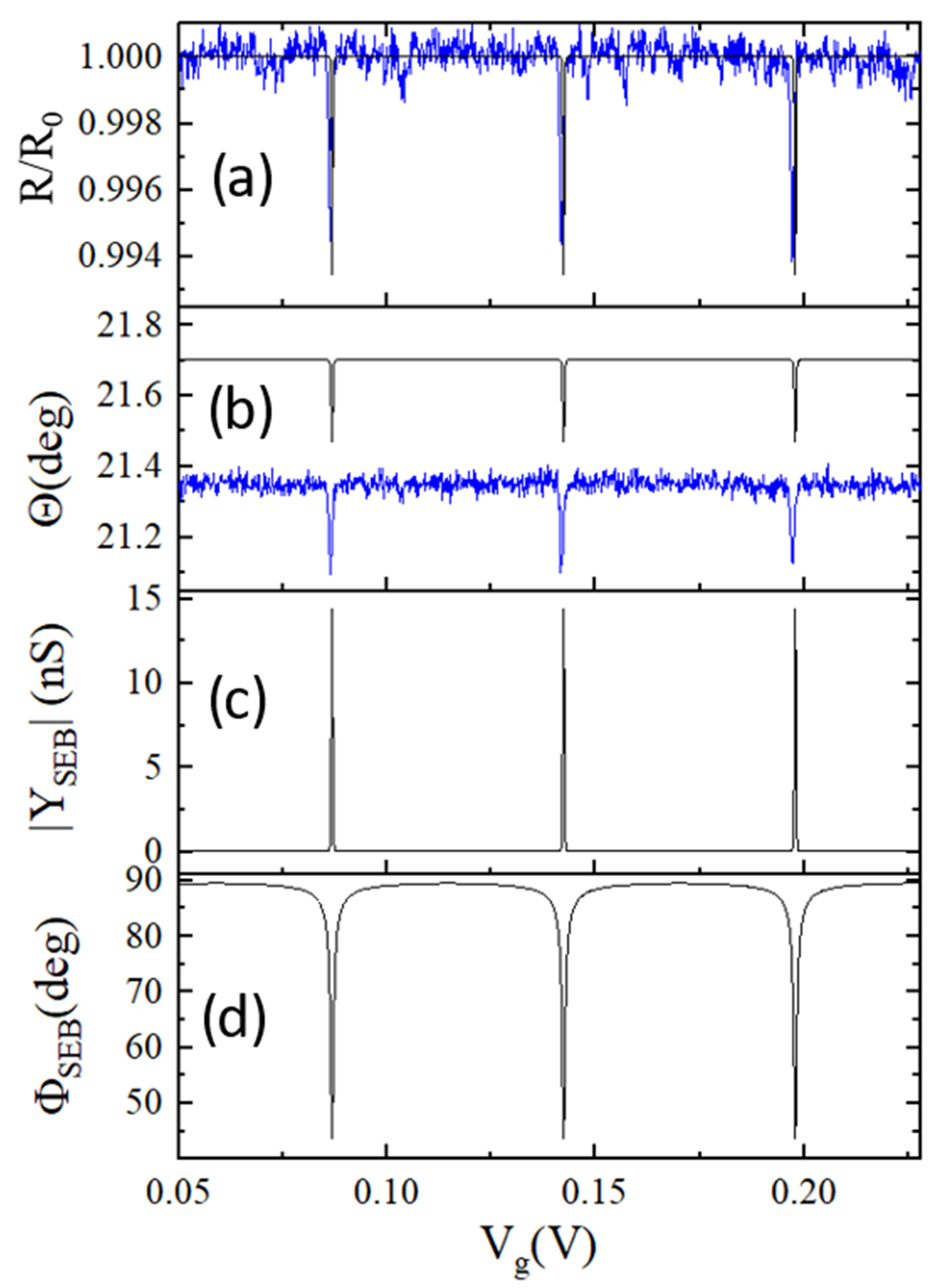

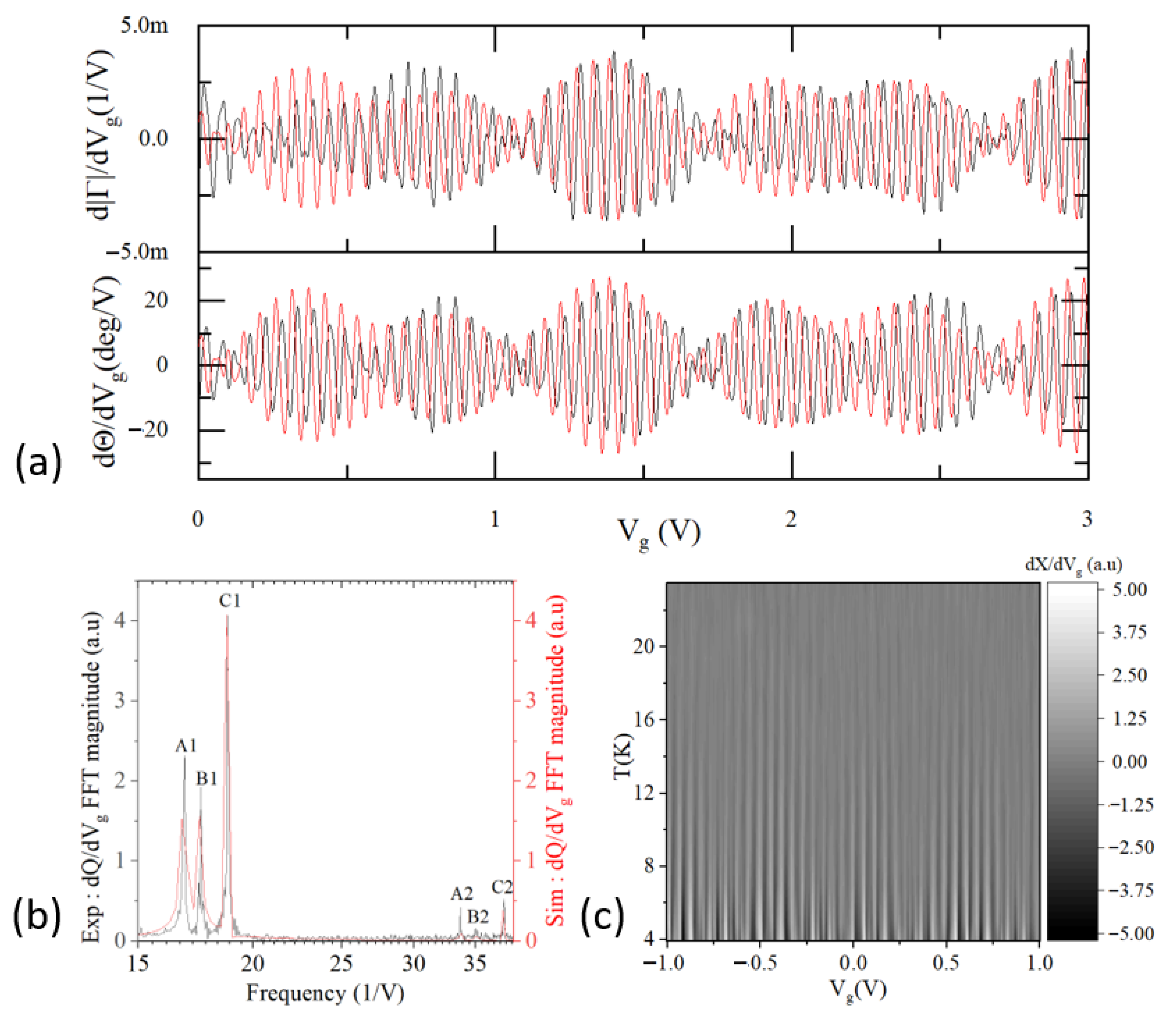

5.1. Characterization of Individual SEBs

5.2. Characterization of SEB Arrays

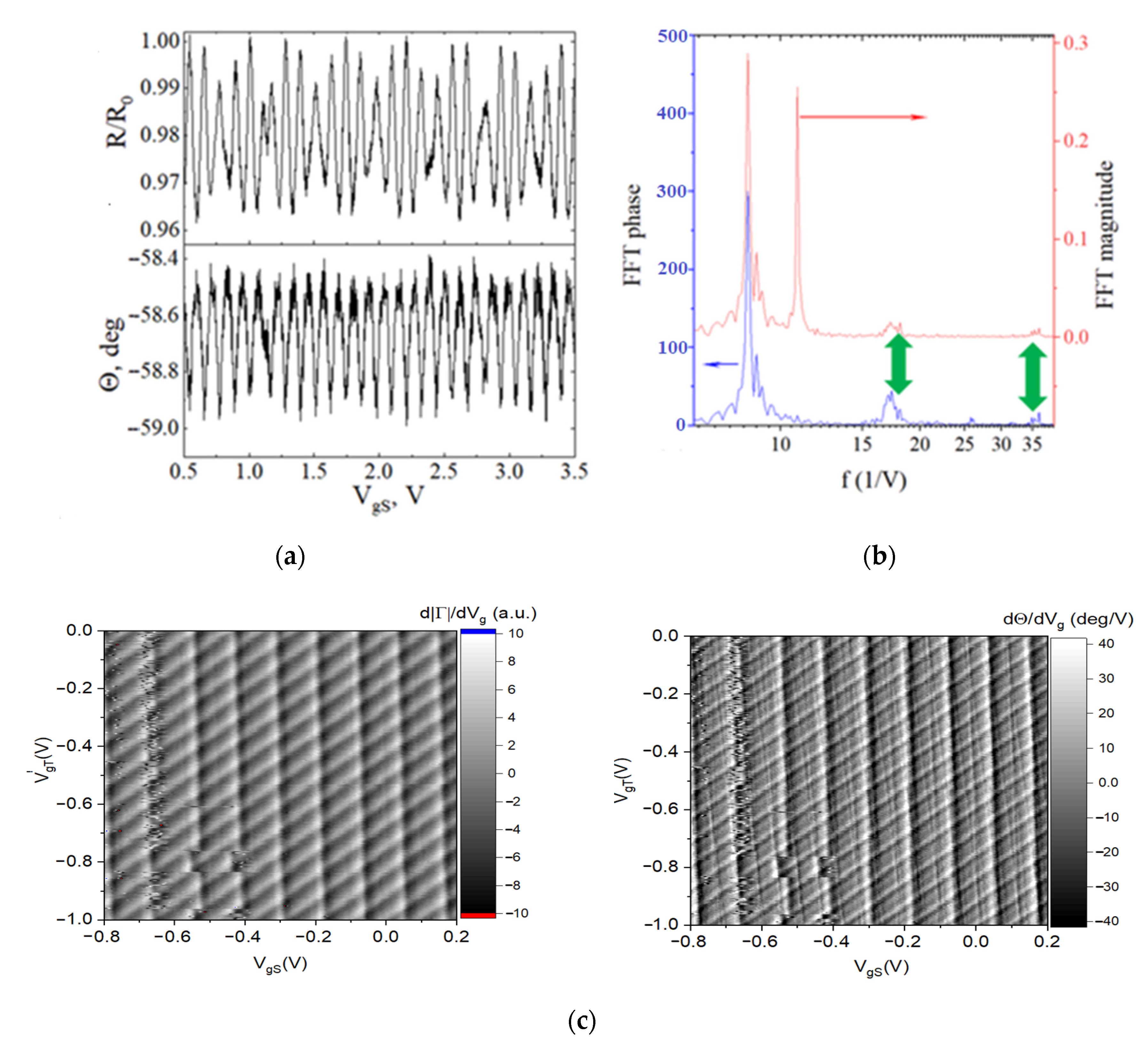

5.2.1. Characterization of a Small (N = 3) SEBA

5.2.2. Comparative Characterization of Larger (“N = 40” vs. “N = 200”) SEBAs

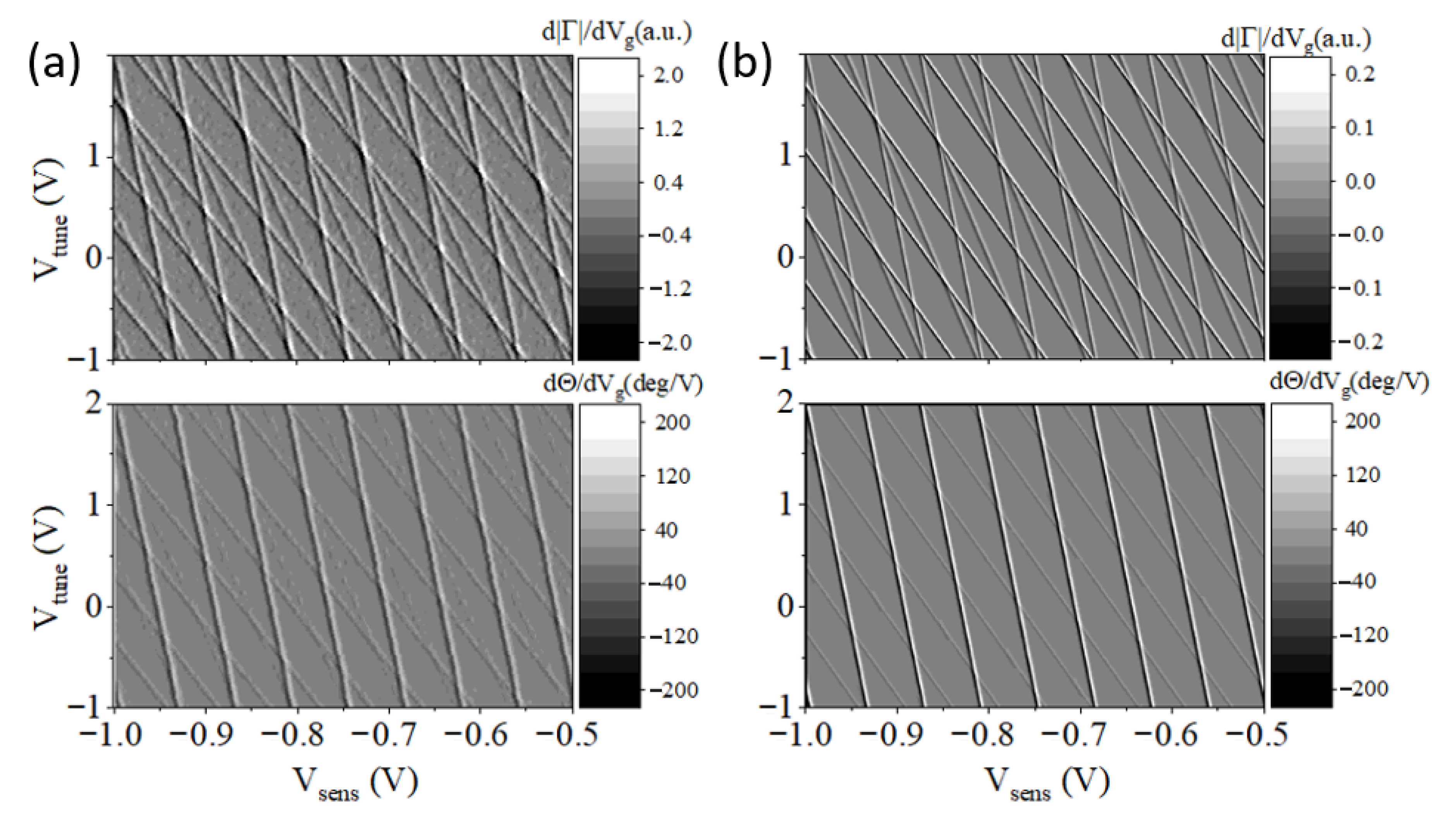

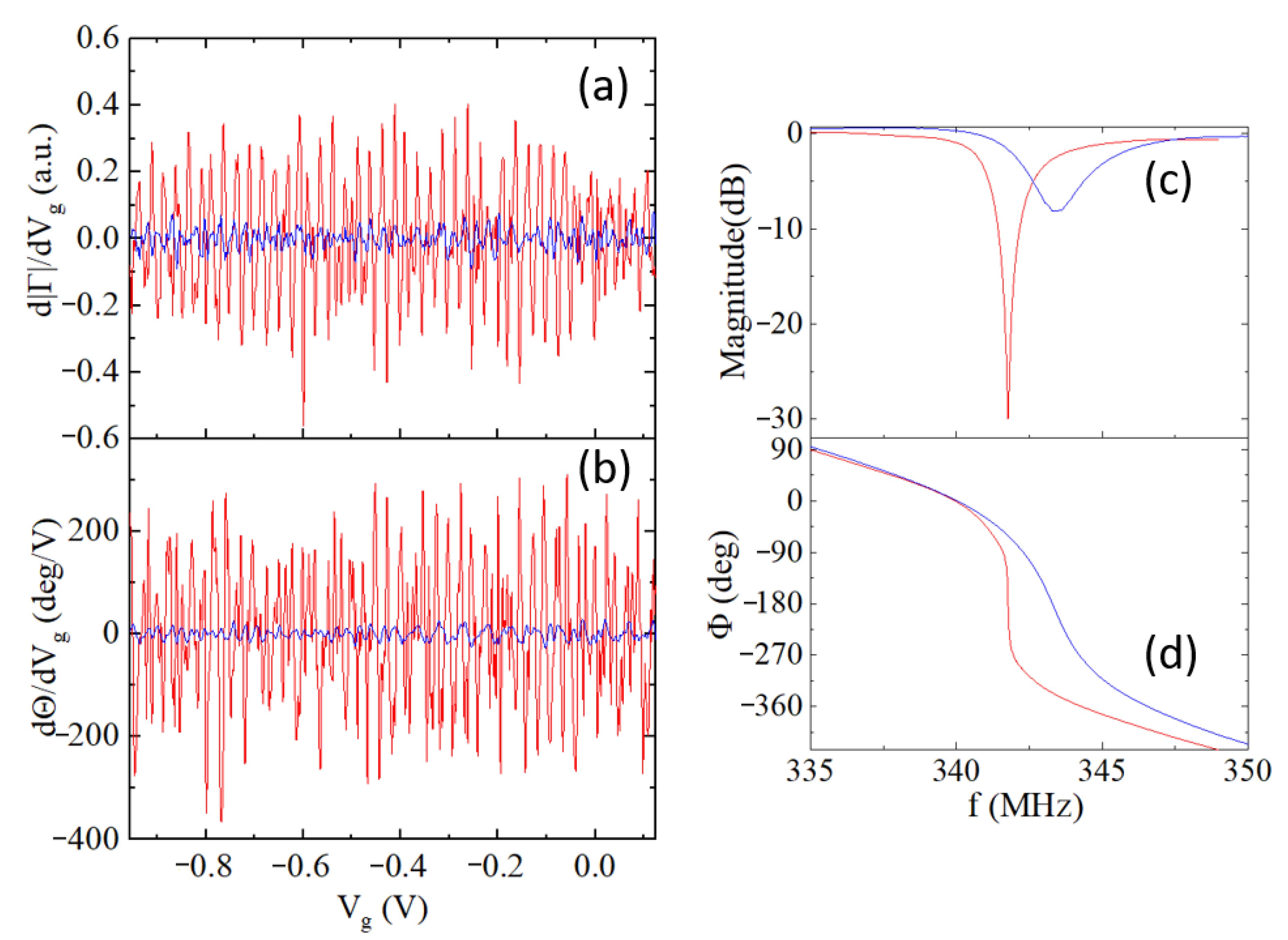

5.2.3. Experimental Characterization of SEB Arrays with Different Matching Networks

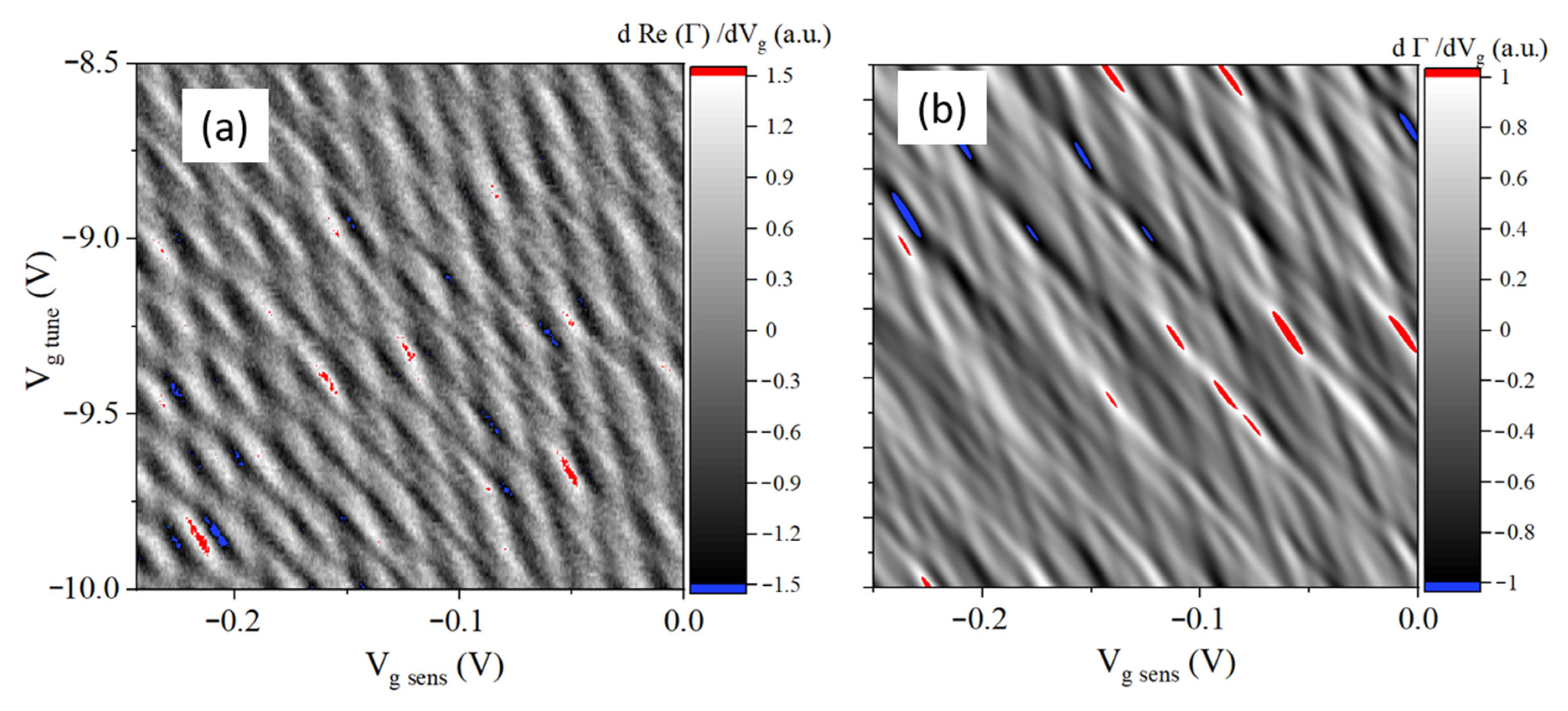

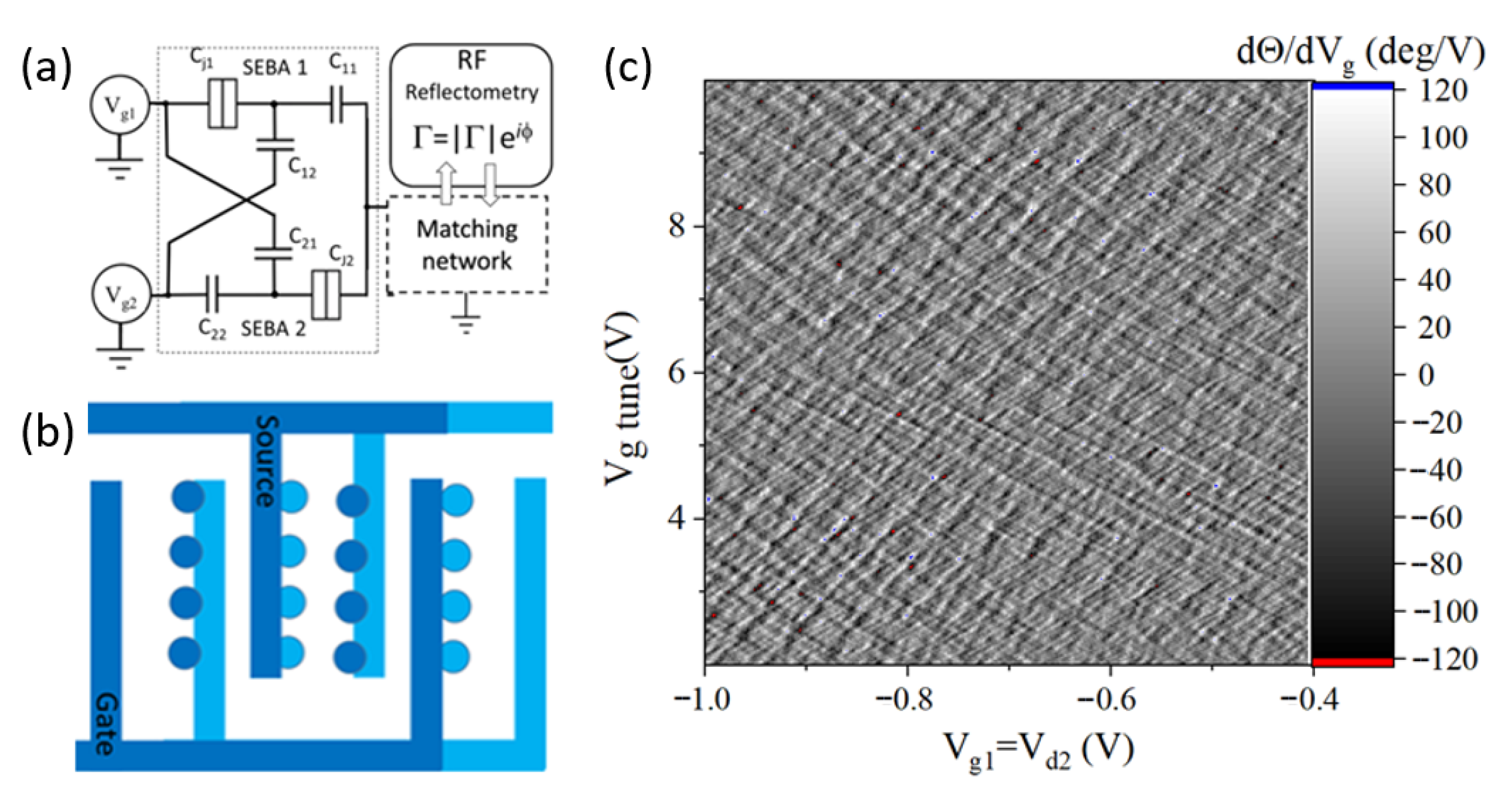

5.2.4. Characterization of Cross-Coupled SEB Arrays

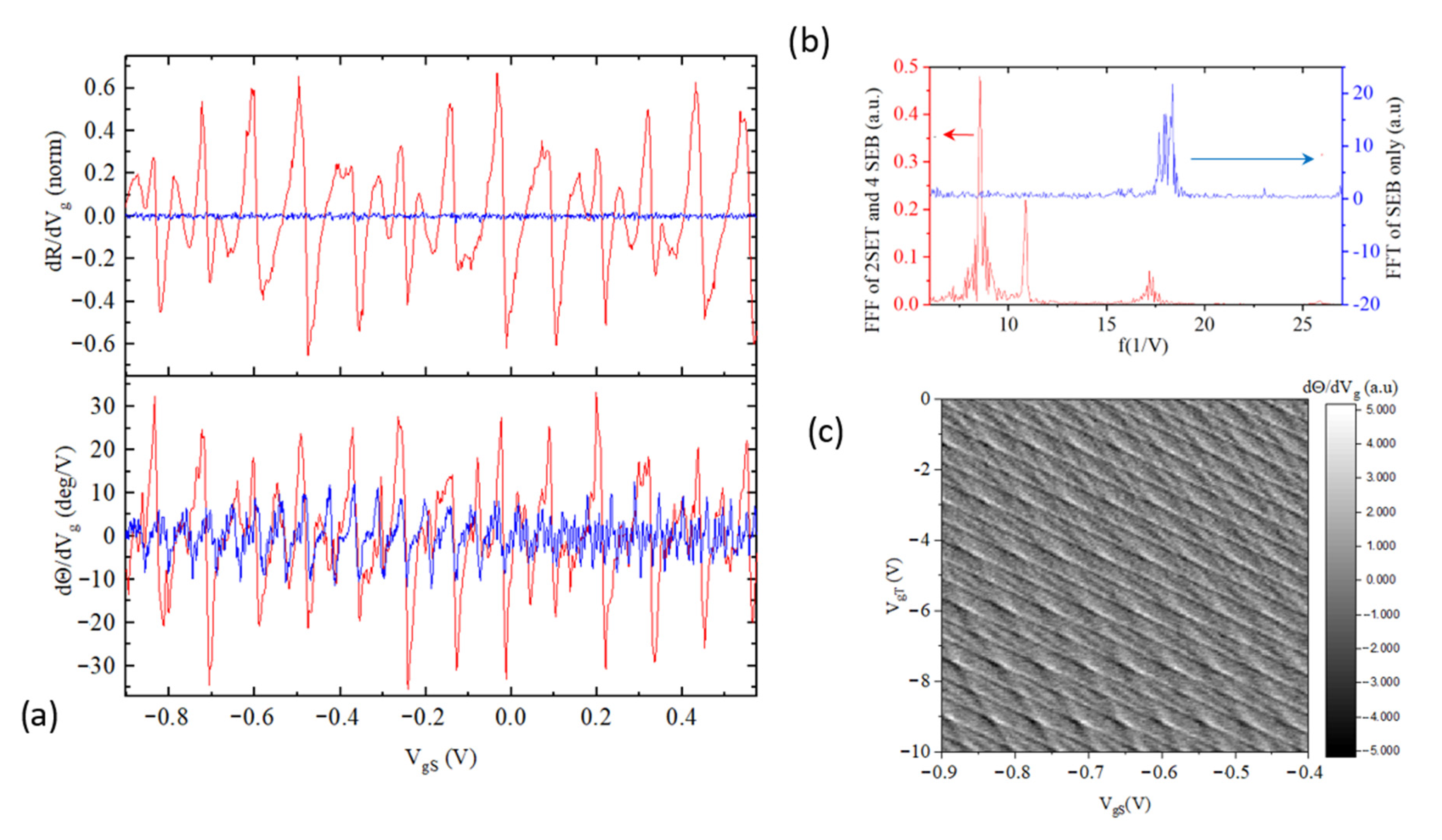

5.3. Comparison of Performance between SEB Array and DC-Decoupled SET

6. Conclusions

Supplementary Materials

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Likharev, K.K. Single-electron devices and their applications. Proc. IEEE 1999, 87, 606–632. [Google Scholar] [CrossRef]

- Brenning, H.; Kafanov, S.; Duty, T.; Kubatkin, S.; Delsing, P. An ultrasensitive radio-frequency single-electron transistor working up to 4.2 K. J. Appl. Phys. 2006, 100, 114321. [Google Scholar] [CrossRef]

- Su, L.; Xinxing, L.; Hua, Q.; Xiaofeng, G. A sensitive charge scanning probe based on silicon single electron transistor. J. Semicond. 2016, 37, 044008. [Google Scholar] [CrossRef]

- Suter, K.; Akiyama, T.; De Rooij, N.F.; Huefner, M.; Ihn, T.; Staufer, U. Integration of a Fabrication Process for an Aluminum Single-Electron Transistor and a Scanning Force Probe for Tuning-Fork-Based Probe Microscopy. J. Microelectromechanical Syst. 2010, 19, 1088–1097. [Google Scholar] [CrossRef]

- Yoo, M.J.; Fulton, T.A.; Hess, H.F.; Willett, R.L.; Dunkleberger, L.N.; Chichester, R.J.; West, K.W. Scanning single-electron transistor microscopy: Imaging individual charges. Science 1997, 276, 579–582. [Google Scholar] [CrossRef] [PubMed]

- Brenning, H.T.; Kubatkin, S.E.; Erts, D.; Kafanov, S.G.; Bauch, T.; Delsing, P. A single electron transistor on an atomic force microscope probe. Nano Lett. 2006, 6, 937–941. [Google Scholar] [CrossRef]

- Aassime, A.; Johansson, G.; Wendin, G.; Schoelkopf, R.J.; Delsing, P. Radio-frequency single-electron transistor as readout device for qubits: Charge sensitivity and backaction. Phys. Rev. Lett. 2001, 86, 3376–3379. [Google Scholar] [CrossRef]

- Bladh, K.; Gunnarsson, D.; Johansson, G.; Käck, A.; Wendin, G.; Aassime, A.; Delsing, P. Reading out charge qubits with a radio-frequency single-electron-transistor. In Condensation and Coherence in Condensed Matter. Proceedings of the Nobel Jubilee Symposium, Goteborg, Sweden, 4–7 December 2001; The Royal Swedish Academy of Sciences: Stockholm, Sweden, 2002. [Google Scholar]

- Crippa, A.; Maurand, R.; Bourdet, L.; Kotekar-Patil, D.; Amisse, A.; Jehl, X.; Barraud, S. Electrical Spin Driving by $g$-Matrix Modulation in Spin-Orbit Qubits. Phys. Rev. Lett. 2018, 120, 137702. [Google Scholar] [CrossRef]

- Gonzalez-Zalba, M.F.; Barraud, S.; Ferguson, A.J.; Betz, A.C. Probing the limits of gate-based charge sensing. Nat. Commun. 2015, 6, 1–8. [Google Scholar] [CrossRef]

- Hollenberg LC, L.; Wellard, C.J.; Pakes, C.I.; Fowler, A.G. Single-spin readout for buried dopant semiconductor qubits. Phys. Rev. B 2004, 69, 233301. [Google Scholar] [CrossRef]

- Kotekar-Patil, D.; Corna, A.; Maurand, R.; Crippa, A.; Orlov, A.; Barraud, S.; Sanquer, M. Pauli spin blockade in CMOS double quantum dot devices. Phys. Status Solidi B 2017, 254, 1600581. [Google Scholar] [CrossRef]

- Morello, A.; Escott, C.C.; Huebl, H.; Van Beveren, L.W.; Hollenberg LC, L.; Jamieson, D.N.; Clark, R.G. Architecture for high-sensitivity single-shot readout and control of the electron spin of individual donors in silicon. Phys. Rev. B 2009, 80, 081307. [Google Scholar] [CrossRef]

- Petersson, K.D.; Smith, C.G.; Anderson, D.; Atkinson, P.; Jones GA, C.; Ritchie, D.A. Charge and spin state readout of a double quantum dot coupled to a resonator. Nano Lett. 2010, 10, 2789–2793. [Google Scholar] [CrossRef] [PubMed]

- Niemeyer, J. Eine einfache Methode zur Herstellung kleinster Josephson-Elemente. Ptb Mitt. 1974, 84, 251–253. [Google Scholar]

- Dolan, G.J. Offset works for lift-off photoprocessing. Appl. Phys. Lett. 1977, 31, 337–339. [Google Scholar] [CrossRef]

- Lafarge, P.; Pothier, H.; Williams, E.R.; Esteve, D.; Urbina, C.; Devoret, M.H. Direct observation of macroscopic charge quantization. Z. Phys. B 1991, 85, 327–332. [Google Scholar] [CrossRef]

- Schoelkopf, R.J.; Wahlgren, P.; Kozhevnikov, A.A.; Delsing, P.; Prober, D.E. The radio-frequency single-electron transistor (RF-SET): A fast and ultrasensitive electrometer. Science 1998, 280, 1238–1242. [Google Scholar] [CrossRef]

- Zimmerli, G.; Kautz, R.L.; Martinis, J.M. Voltage gain in the single-electron transistor. Appl. Phys. Lett. 1992, 61, 2616–2618. [Google Scholar] [CrossRef]

- Kafanov, S.; Delsing, P. Measurement of the shot noise in a single-electron transistor. Phys. Rev. B 2009, 80, 155320. [Google Scholar] [CrossRef]

- Gustavsson, S.; Gunnarsson, D.; Delsing, P. Cryogenic amplifier for intermediate source impedance with gigahertz bandwidth. Appl. Phys. Lett. 2006, 88, 153505. [Google Scholar] [CrossRef]

- Persson, F.; Wilson, C.M.; Sandberg, M.; Johansson, G.; Delsing, P. Excess Dissipation in a Single-Electron Box: The Sisyphus Resistance. Nano Lett. 2010, 10, 953–957. [Google Scholar] [CrossRef] [PubMed]

- Luryi, S. Quantum capacitance devices. Appl. Phys. Lett. 1988, 52, 501–503. [Google Scholar] [CrossRef]

- Mizuta, R.; Otxoa, R.M.; Betz, A.C.; Gonzalez-Zalba, M.F. Quantum and tunneling capacitance in charge and spin qubits. Phys. Rev. B 2017, 95, 045414. [Google Scholar] [CrossRef]

- Zimmerman, N.M.; Keller, M.W. Dynamic input capacitance of single-electron transistors and the effect on charge-sensitive electrometers. J. Appl. Phys. 2000, 87, 8570–8574. [Google Scholar] [CrossRef]

- Frake, J.C.; Kano, S.; Ciccarelli, C.; Griffiths, J.; Sakamoto, M.; Teranishi, T.; Buitelaar, M.R. Radio-frequency capacitance spectroscopy of metallic nanoparticles. Sci. Rep. 2015, 5, 10858. [Google Scholar] [CrossRef] [PubMed]

- Beenakker, C.W.J. Theory of Coulomb-blockade oscillations in the conductance of a quantum dot. Phys. Rev. B 1991, 44, 1646–1656. [Google Scholar] [CrossRef] [PubMed]

- Filmer, M. Development of High Speed Nanoscale Sensors Based on Single-Electron Devices. Ph.D. Thesis, Univeristy of Notre Dame, Notre Dame, IN, USA, 2020. [Google Scholar]

- Chisum, J.D.; Popovic, Z. Performance limitations and measurement analysis of a near-field microwave microscope for nondestructive and subsurface detection. IEEE Trans. Microw. Theory Tech. 2012, 60, 2605–2615. [Google Scholar] [CrossRef]

- Bray, J.R.; Roy, L. Measuring the unloaded, loaded, and external quality factors of one- and two-port resonators using scattering-parameter magnitudes at fractional power levels. IEEE Proc. Microw. Antennas Propag. 2004, 151, 345–350. [Google Scholar] [CrossRef]

- Ares, N.; Schupp, F.J.; Mavalankar, A.; Rogers, G.; Griffiths, J.; Jones, G.A.C.; Briggs, G.A.D. Sensitive Radio-Frequency Measurements of a Quantum Dot by Tuning to Perfect Impedance Matching. Phys. Rev. Appl. 2016, 5, 034011. [Google Scholar] [CrossRef]

- Zirkle, T.A. A parallel single-electron box array scanning probe. In Electrical Engineering; University of Notre Dame: Notre Dame, IN, USA, 2019; p. 189. [Google Scholar]

- Filmer, M.J.; Zirkle, T.A.; Chisum, J.; Orlov, A.O.; Snider, G.L. Using single-electron box arrays for voltage sensing applications. Appl. Phys. Lett. 2020, 116, 213103. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zirkle, T.A.; Filmer, M.J.; Chisum, J.; Orlov, A.O.; Dupont-Ferrier, E.; Rivard, J.; Huebner, M.; Sanquer, M.; Jehl, X.; Snider, G.L. Radio Frequency Reflectometry of Single-Electron Box Arrays for Nanoscale Voltage Sensing Applications. Appl. Sci. 2020, 10, 8797. https://doi.org/10.3390/app10248797

Zirkle TA, Filmer MJ, Chisum J, Orlov AO, Dupont-Ferrier E, Rivard J, Huebner M, Sanquer M, Jehl X, Snider GL. Radio Frequency Reflectometry of Single-Electron Box Arrays for Nanoscale Voltage Sensing Applications. Applied Sciences. 2020; 10(24):8797. https://doi.org/10.3390/app10248797

Chicago/Turabian StyleZirkle, Thomas A., Matthew J. Filmer, Jonathan Chisum, Alexei O. Orlov, Eva Dupont-Ferrier, Joffrey Rivard, Matthew Huebner, Marc Sanquer, Xavier Jehl, and Gregory L. Snider. 2020. "Radio Frequency Reflectometry of Single-Electron Box Arrays for Nanoscale Voltage Sensing Applications" Applied Sciences 10, no. 24: 8797. https://doi.org/10.3390/app10248797

APA StyleZirkle, T. A., Filmer, M. J., Chisum, J., Orlov, A. O., Dupont-Ferrier, E., Rivard, J., Huebner, M., Sanquer, M., Jehl, X., & Snider, G. L. (2020). Radio Frequency Reflectometry of Single-Electron Box Arrays for Nanoscale Voltage Sensing Applications. Applied Sciences, 10(24), 8797. https://doi.org/10.3390/app10248797