Review on Short-circuit Current Analysis and Suppression Techniques for MMC-HVDC Transmission Systems

Abstract

1. Introduction

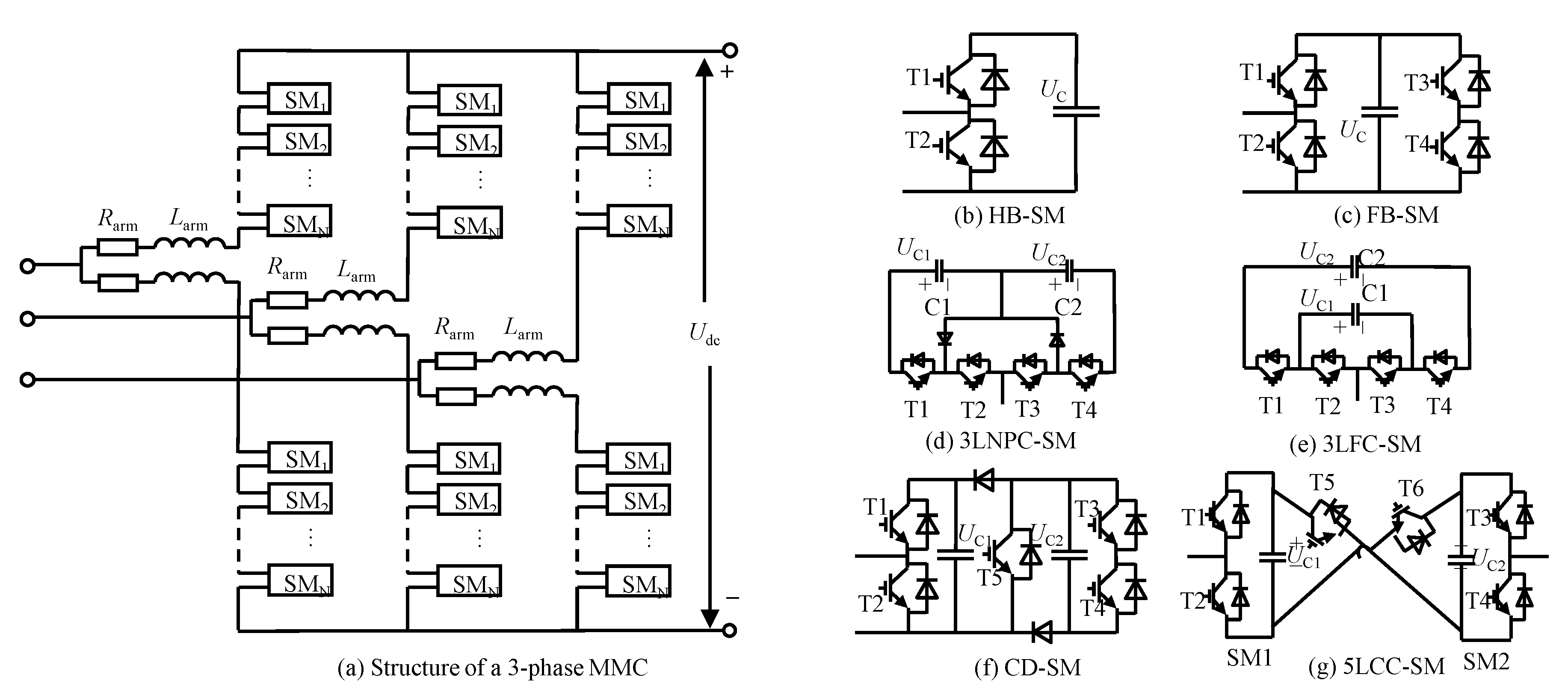

2. A Brief Introduction of MMC

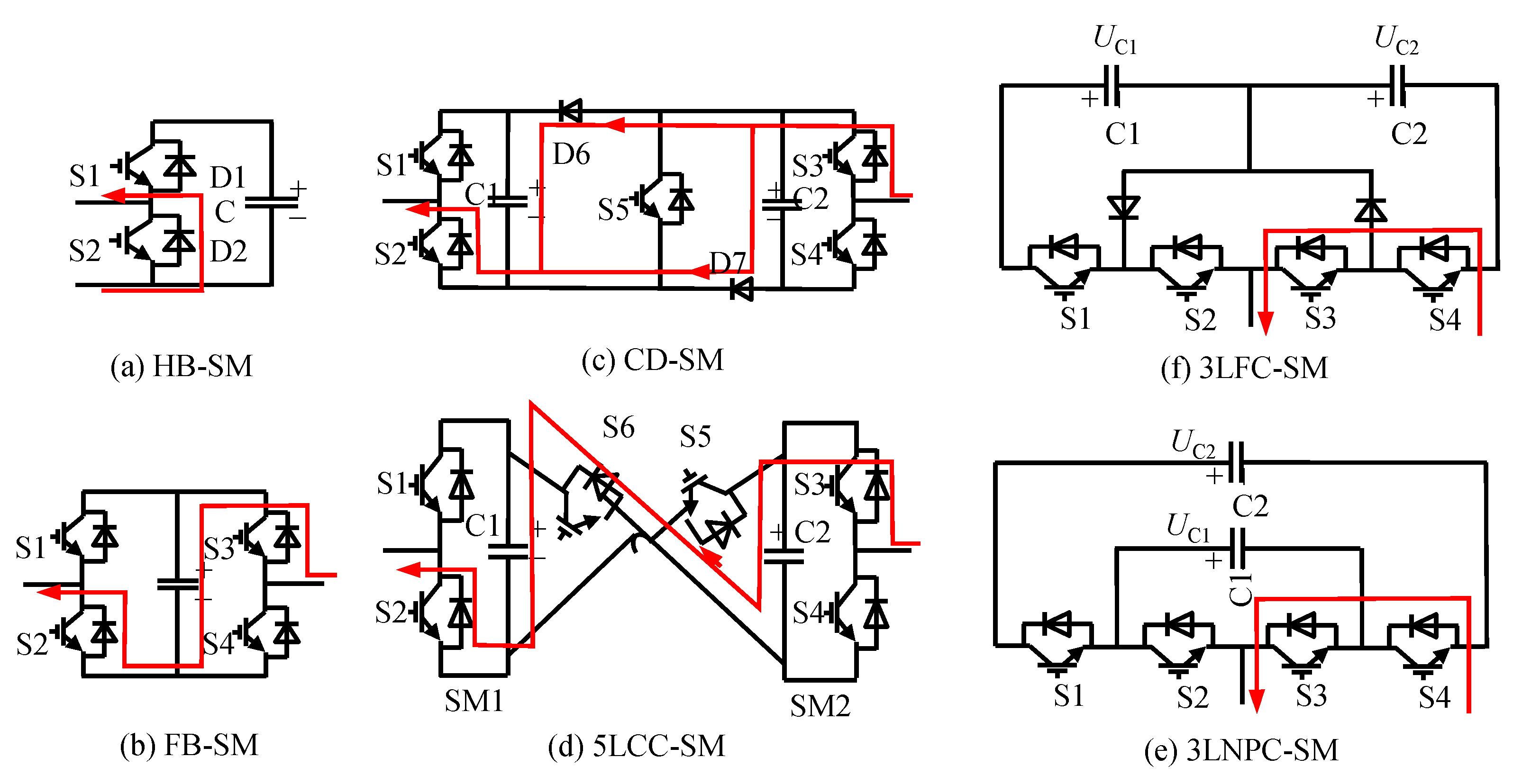

- HB circuit: the HB-SM is inserted or bypassed by turning on or , respectively. When the SM is switched-on or in inserted state, its output voltage equals to its capacitor voltage . Otherwise, when the SM is switched-off or in bypassed state, the output voltage is 0 [18].

- FB circuit: the operation state of FB-SM is determined by the switching states of the four switches to . When in switched-on/inserted state, the output voltage equals to the capacitor voltage . Otherwise, it is 0. The costs of an MMC based on the FB-SMs are higher than that of an MMC based on the HB-SMs due to the increased number of switches in each SM [16].

- CD circuit: a CD-SM consists of two HB-SMs, two additional diodes, and one extra integrated gate bipolar transistor (IGBT) with its anti-parallel diode. During normal operation, the switch is always in conduction state and the dynamics of CD-SM are equivalent to two series connected HB-SMs [16].

- 3LCC circuit: there are two different types of 3LCC-SM, three level neutral-point-clamped (NPC), and three-level flying capacitor (FC). For a three-level FC-SM, its power losses are similar with a HB-SM. The power losses of NPC-SM are higher than the HB-SM and lower than the FB-SM [3]. The 3LCC-SM based MMC is not very attractive from the perspective of manufacturing and control [17].

- 5LCC circuit: there are two HB-SMs connected back-to-back by two extra IGBTs with their anti-parallel diodes in a 5LCC-SM. Its power losses are the same as the CD-SM [17].

3. MMC-Based MTDC Power Grid Modelling Overview

3.1. MMC Main Circuit

- DSM: in a DSM, a detailed switch is applied to present the operational times of the switching devices and the on/off-state resistances/voltages in the SMs [20]. The detailed representation requires a small simulation time step to accurately track the switching voltage edges that are essential for the preservation of various frequency components in the AC and DC waveforms. Because a large number of electrical nodes is created in DSM, it leads to huge simulation time cost. With the increasing number of SMs in MMCs, the DSM is facing a significant challenge in computation [7]. DSM is not suitable for the dynamic analysis, control design, and fault analysis for large scale DC power systems, and simplifications shall be made.

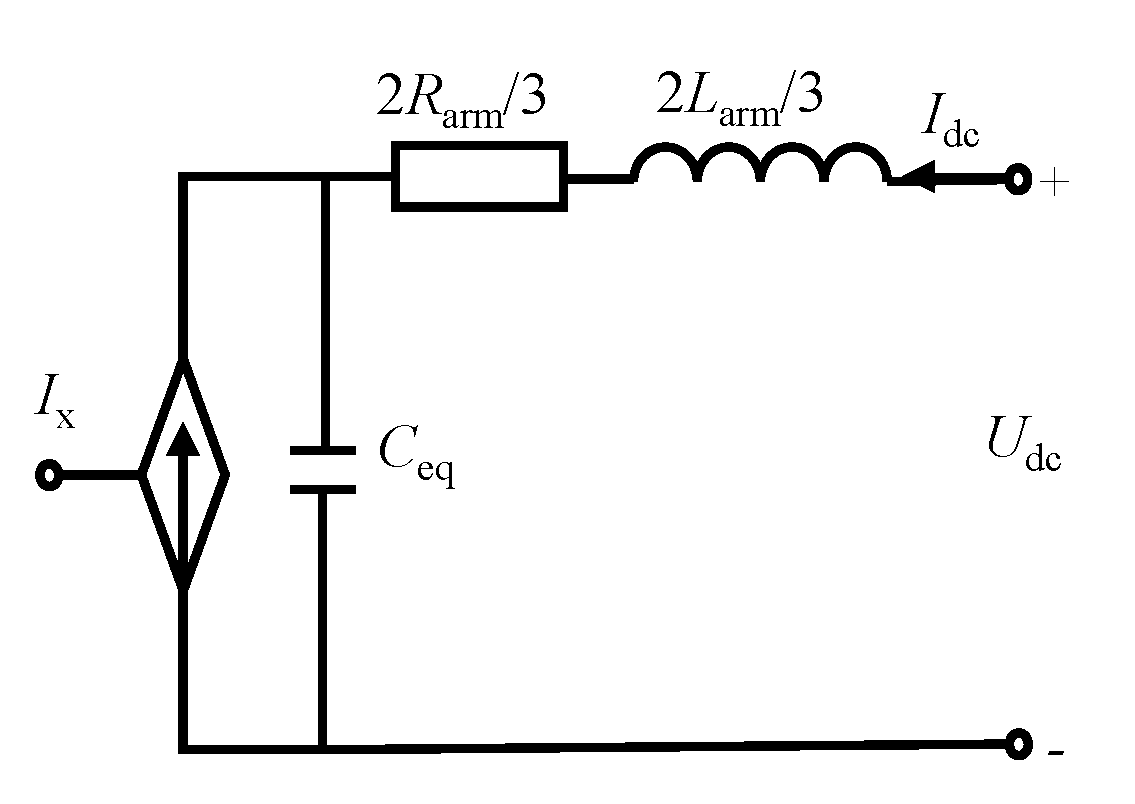

- AVM: the AVMs of MMC has been proposed to approximate system dynamics, where the switching details are not explicitly modeled and the dynamics of MMC is equivalent through using controlled voltage and current sources [18]. The relationship of the arm currents ( for upper bridge arm and for lower bridge arm) and the capacitor voltages ( for the upper bridge arm and for lower bridge arm) can be expressed aswhere C is the capacitance of each submodule capacitor; and, and are the average switching functions of the upper and lower arms.The upper and lower bridge arm voltages and areIgnoring the differences between the circuit parameters of MMC six bridge arms and high order circulating current components, the arm current contains a DC component that equals ; a fundamental frequency AC component equaling to ; and, even-order circulating current components with an amplitude of . The upper and lower arm currents are presented asThe real switching function of the bridge arm is a stepped waveform that indicates when SMs are inserted or out of work [21]. However, with the increasing number of SMs, the average switching function and can be represented by continuous waveforms:where M is the modulation index and is the phase angle of the fundamental frequency component of the switching function. and are the amplitude and phase of a control signal generated by the circulating current suppression controllers (CCSCs).In the AVM, although the individual capacitor voltages are not calculated, the large-scale dynamic behavior can be accurately modeled [22]. Instead, a single DC voltage is calculated, so that the AVM can use larger simulation time steps and it requires less computational resources [23]. It provides faster simulation speed and is more efficient than models that consider the detailed MMC converter topology. It has been proposed for studying the dynamics behavior of both single MMC [24,25] and DC power grids [26,27,28,29].

- SAVM: the SAVM assumes that all of the internal variables in the MMC are perfectly controlled, all submodule capacitor voltages are perfectly balanced, and second harmonic circulating currents in each phase are suppressed [22,26]. It is a simplified model that is based on the AVM by ignoring the internal circulating current dynamic process. Therefore, the average switching function can be simplified toIt is suitable for the study of large-scale MMC-based MTDC power grids and system-level controller design, as discussed in [30].

- DEM: based on the equivalent branch model of a bridge arm, a DEM of MMC is proposed in [31,32]. In the DEM, the dynamics of each SM capacitor is represented by an equivalent controlled voltage source in series with resistance [31]. The values of and arewhere C is the capacitance of each SM’s capacitor, is the time-step for simulation, and is the SM capacitor current. The DEM has three major assumptions: an off-state switch is equivalent to an open circuit; and on-state that is equivalent to ; is equal to the corresponding bridge arm current when the SM is inserted. is equal to 0, when the SM is passed by [32].As a result of the aforementioned assumptions, each MMC arm can be modeled as a series connection of arm inductor , equivalent voltage source , and equivalent resistance . Figure 3 shows the equivalent circuit of each submodule of the MMC in DEM.The equivalent bridge voltage can be given bywhere i is the index of SM; N is the number of SM in each bridge arm; and, satisfiesMeanwhile,where is the number of SMs in on-state.The DEM provides a detailed representation of SMs switching events and individual capacitor ripples. It is feasible for arbitrary number of submodules. The DEM can be applied in order to design the balancing control of the capacitor voltages in the bridge arm. It can also represent the blocked mode, which is essential for accurately describing the MMC behaviors during startup and fault conditions [31,33].

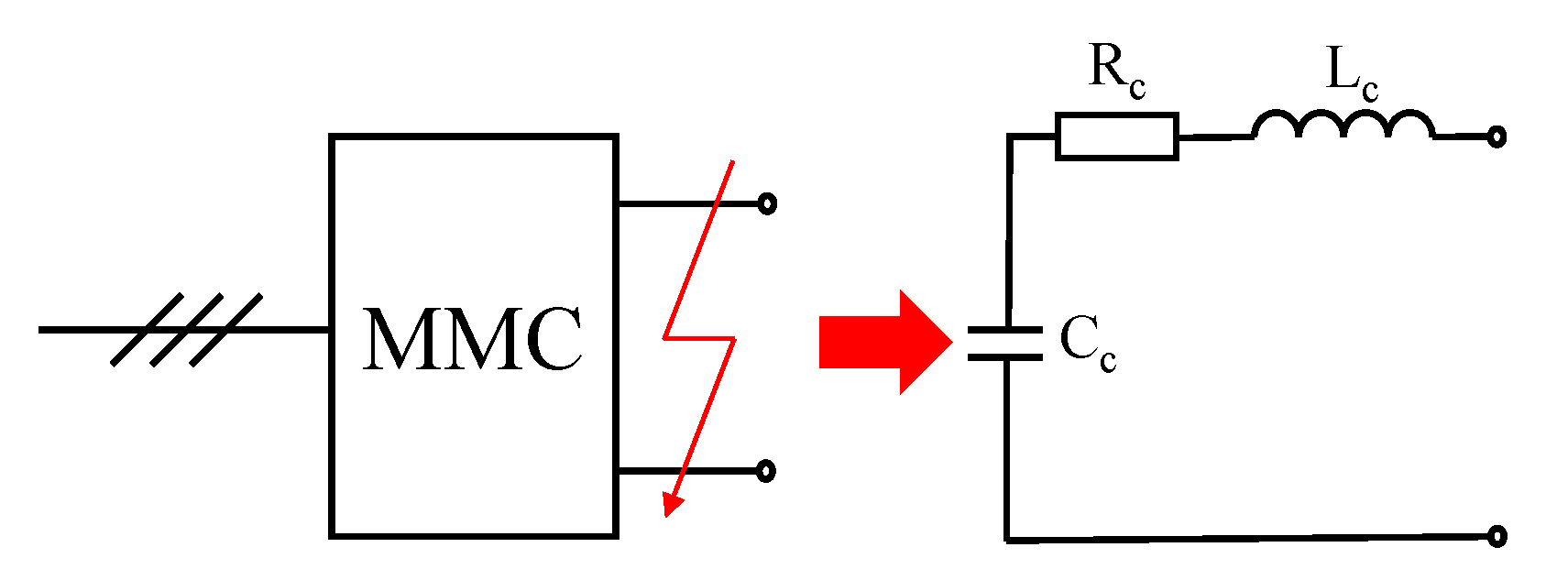

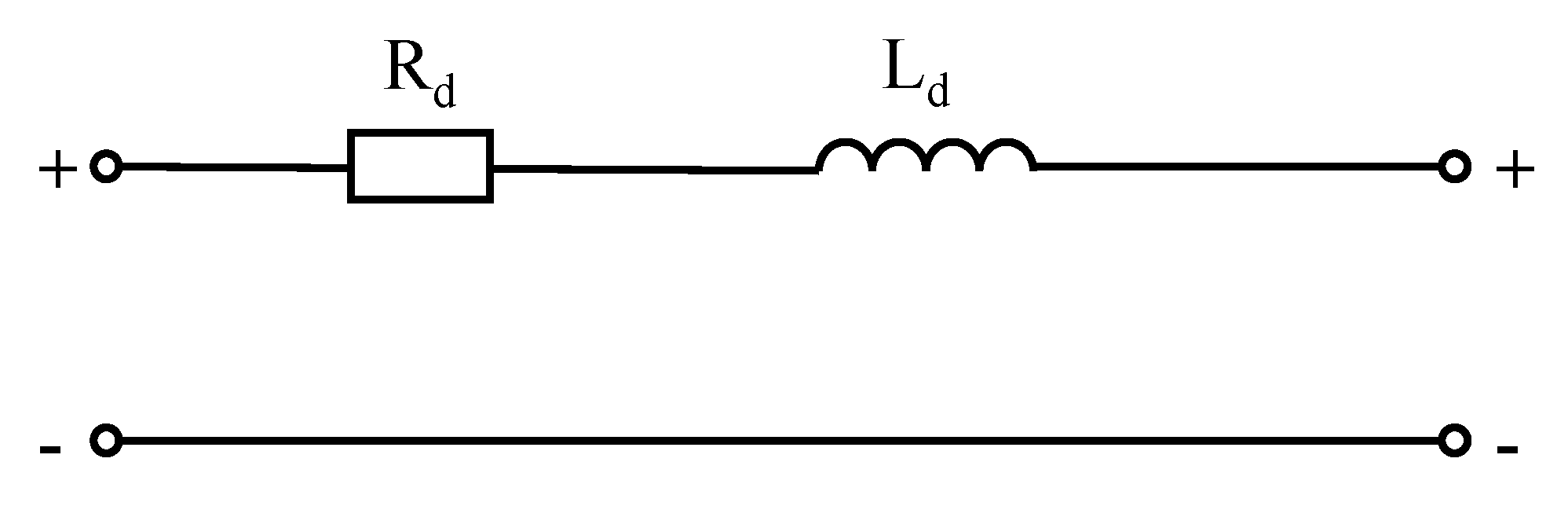

- EDM: because the capacitor discharge currents of SMs are the dominant components of the DC short-circuit current in DC power girds, MMCs are equivalent to a series RLC circuit in a EDM [13,34,35,36]. Figure 4 shows the structure of EDM.The equivalent circuit parameters can be obtained from the detailed average model parameters, as follows.where and are the resistance and inductance of the bridge arms, respectively, is the sum of the on-state resistances of all SMs. The model that is given by (10) ignores the dynamics of MMC control systems, such as the power and voltage control [13,34], and it is suitable for DC short circuit current calculation [13,34,35,36].

3.2. MMC Control Systems

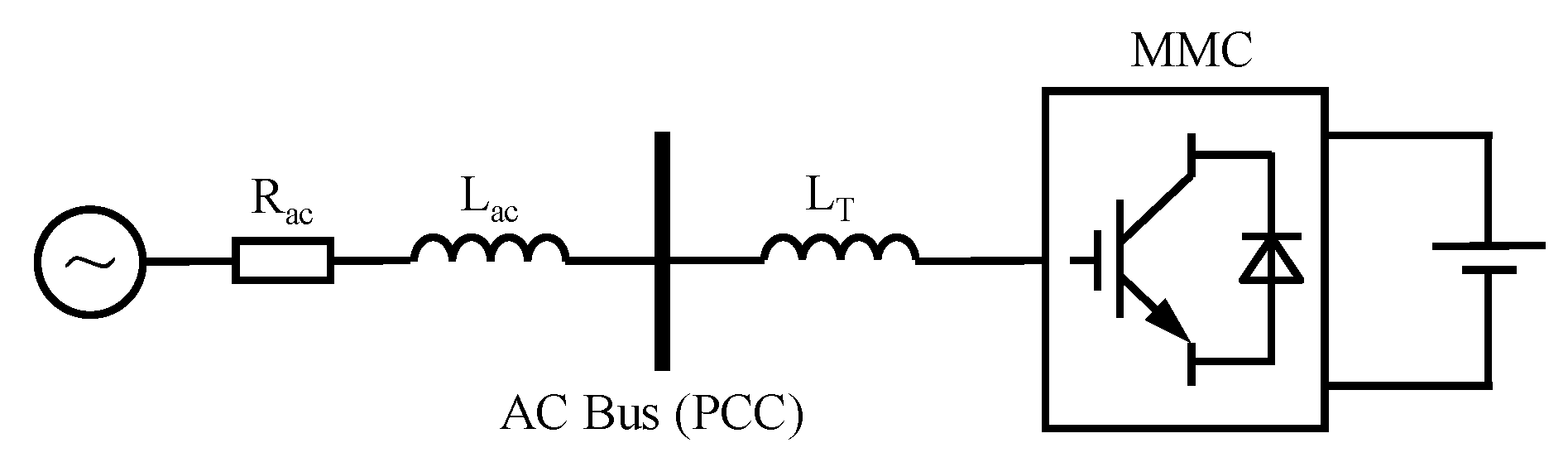

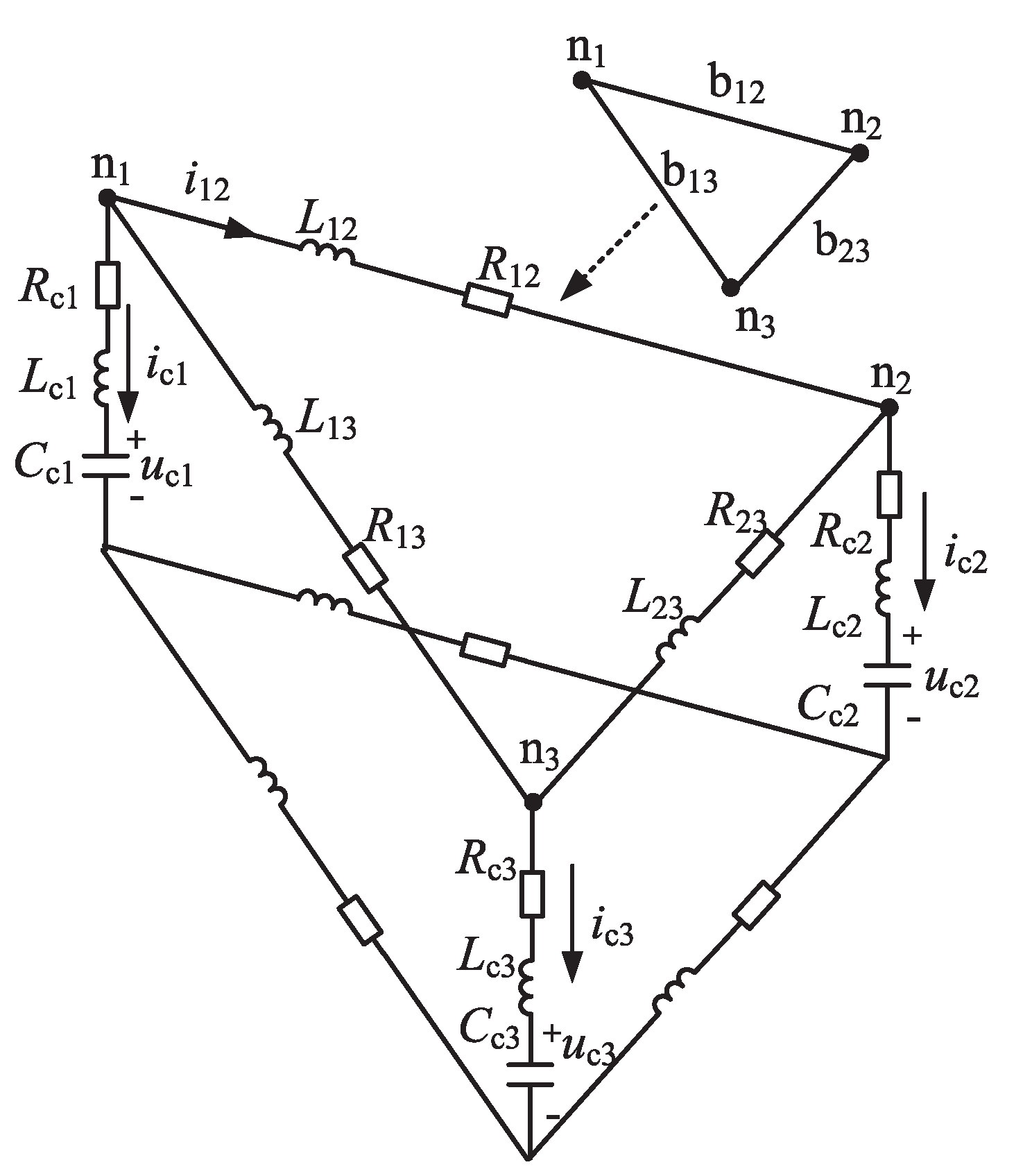

3.3. AC System

3.4. DC System

4. Analysis and Suppression Method of Short Circuit Current in MMC-Based MTDC Power Gird

4.1. Short Circuit Current Calculation Method

4.1.1. Pole-to-Pole Short Circuit Current Calculation Method

4.1.2. Short-Circuit Current Calculation Considering MMC Control

4.2. DC Short Circuit Current Suppression Method in MMC-Based MTDC Power Grid

- Using the MMC topology with DC fault ride through capability such as FB-SMs, CD-SMs, and 5LCC-SMs, etc.

- Installing current limiting device and cooperating with DC circuit breakers to isolate the DC fault line.

- Design MMC control strategies in order to suppress the short circuit current.

4.2.1. MMC Topologies with DC Fault Ride Through Capability

- CD circuit: in the CD based MMC-HVDC system, although the SMs can block the DC fault current [2], they can only generate a reverse voltage per bridge arm, which is, half of the reverse voltage produced by the FB-SMs per arm, as shown in Figure 10c. Thus, it takes more time for the CD-MMC to suppress the fault current to zero [16].

4.2.2. Fault Current Limiting Devices

- Solid FCLs: solid FCLs are the most popular topologies due to its advantages of minimum power loss under normal condition, quick response, fast recovery capacity, good reliability, and low cost [52]. A resistive based solid-state FCL is proposed in [53]. The resistive based solid-state FCL consists of a current-limiting resistor module R and a control module in parallel, as shown in Figure 12.The resistive based solid-state FCL has two operational states. In the normal operating state, reverse parallel gate turns off thyristors (GTOS) in a conducting state, which ensures that the current-limiting resistor R is bypassed and the operational current can flow through the GTOs. Under DC fault conditions, and are turned off according to the operation signal issued by the fault detection system, and R is rapidly put into use, which increases the system damping and inhibits the fault current’s rising.

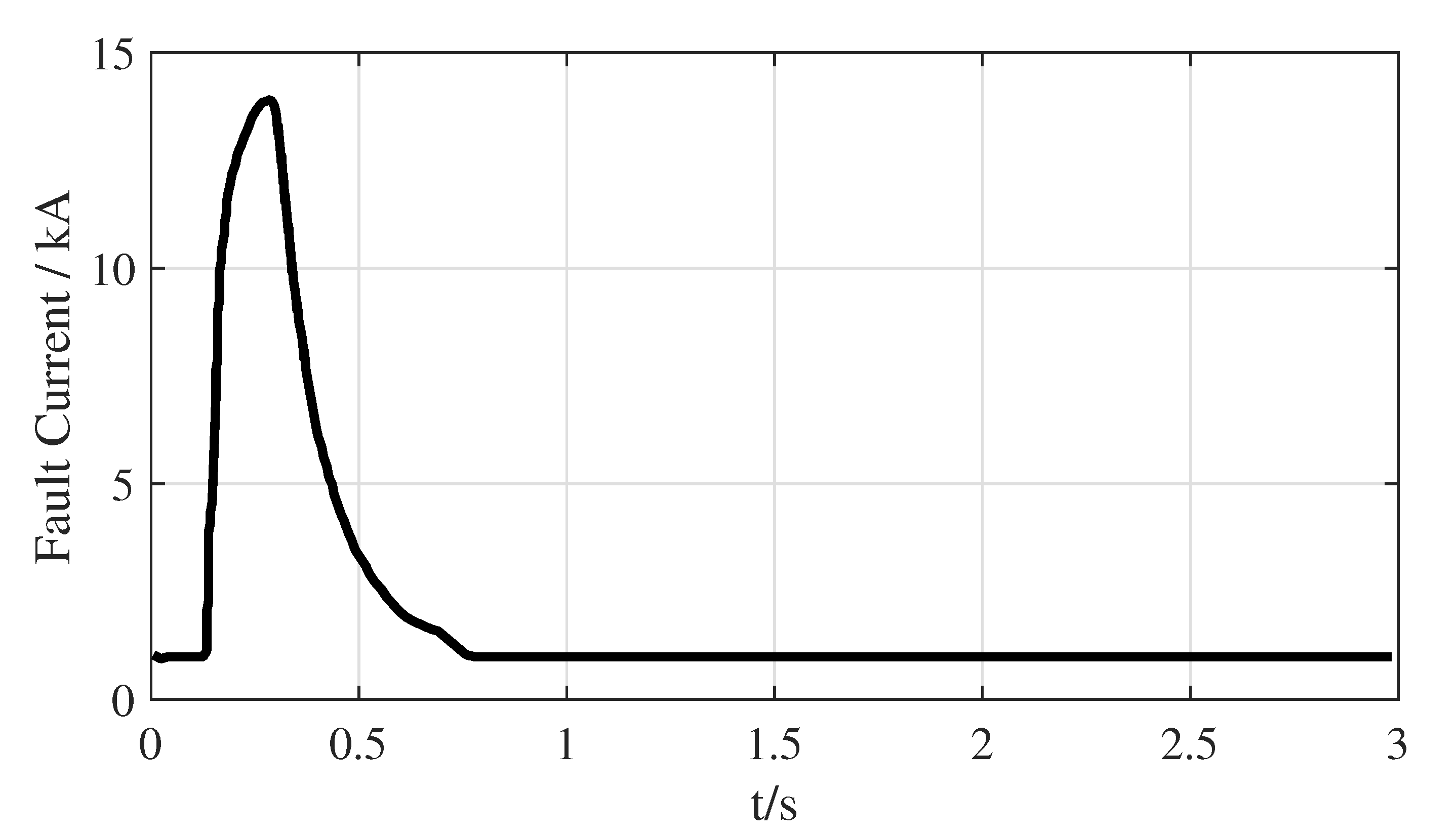

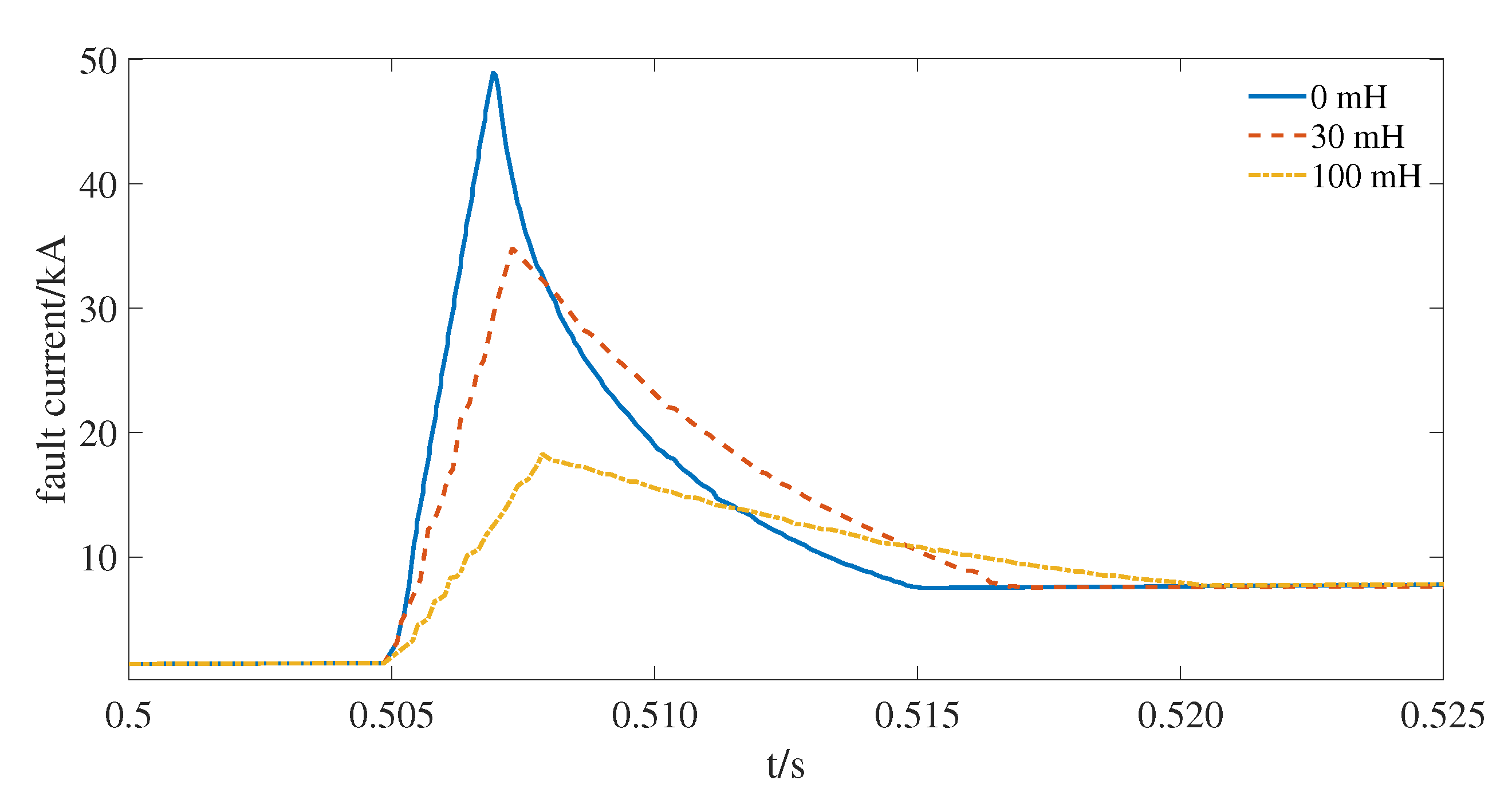

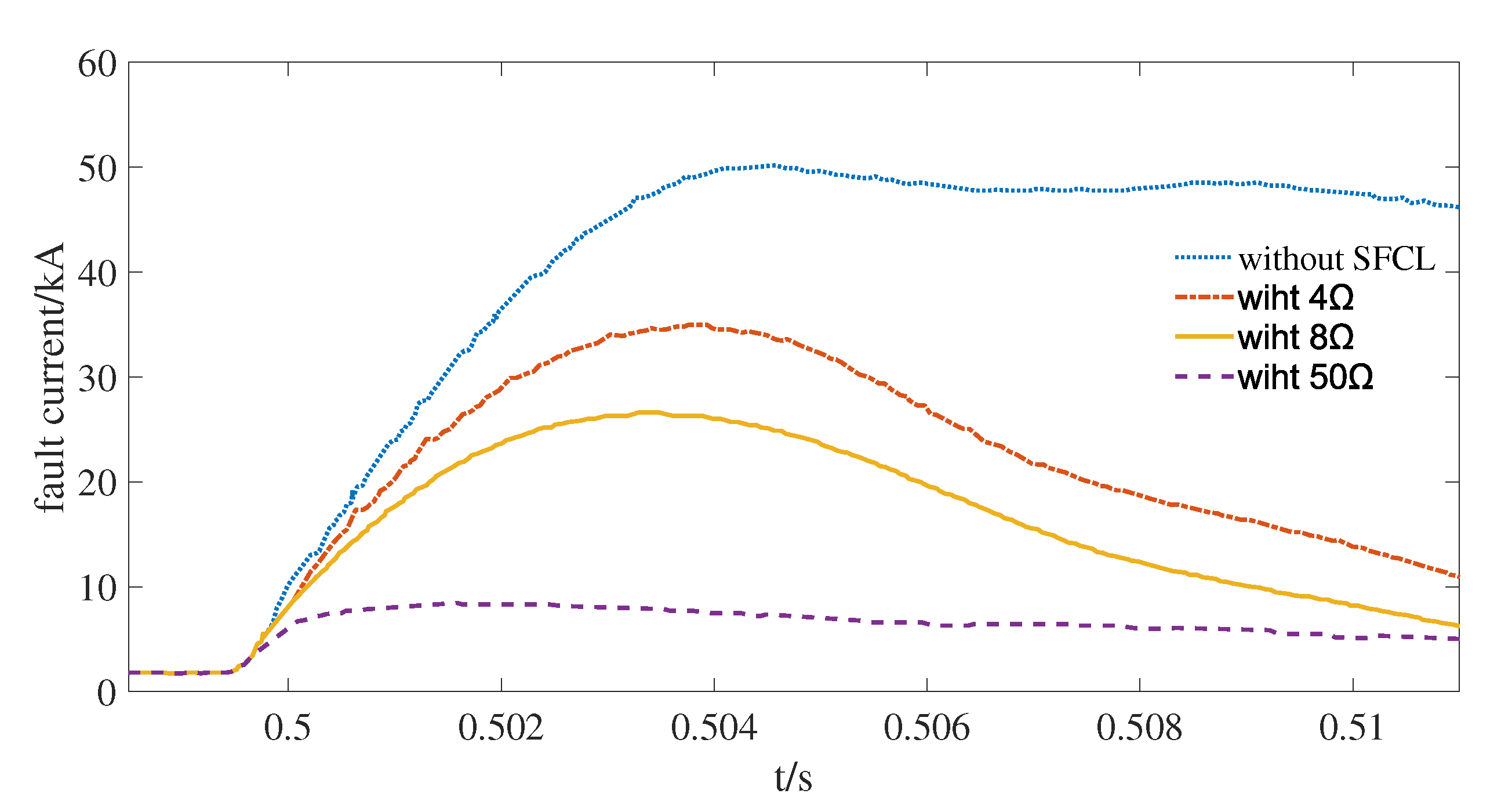

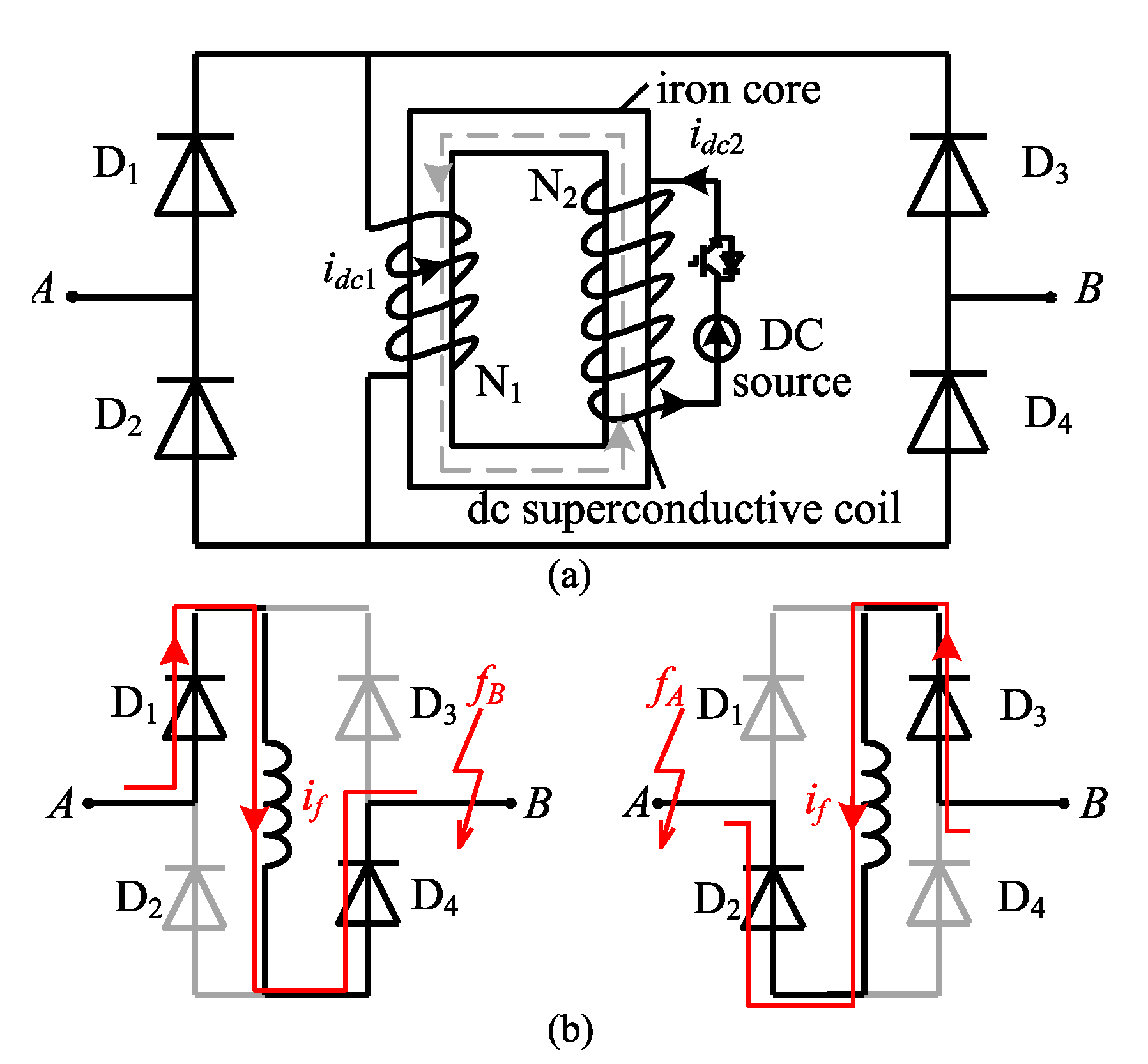

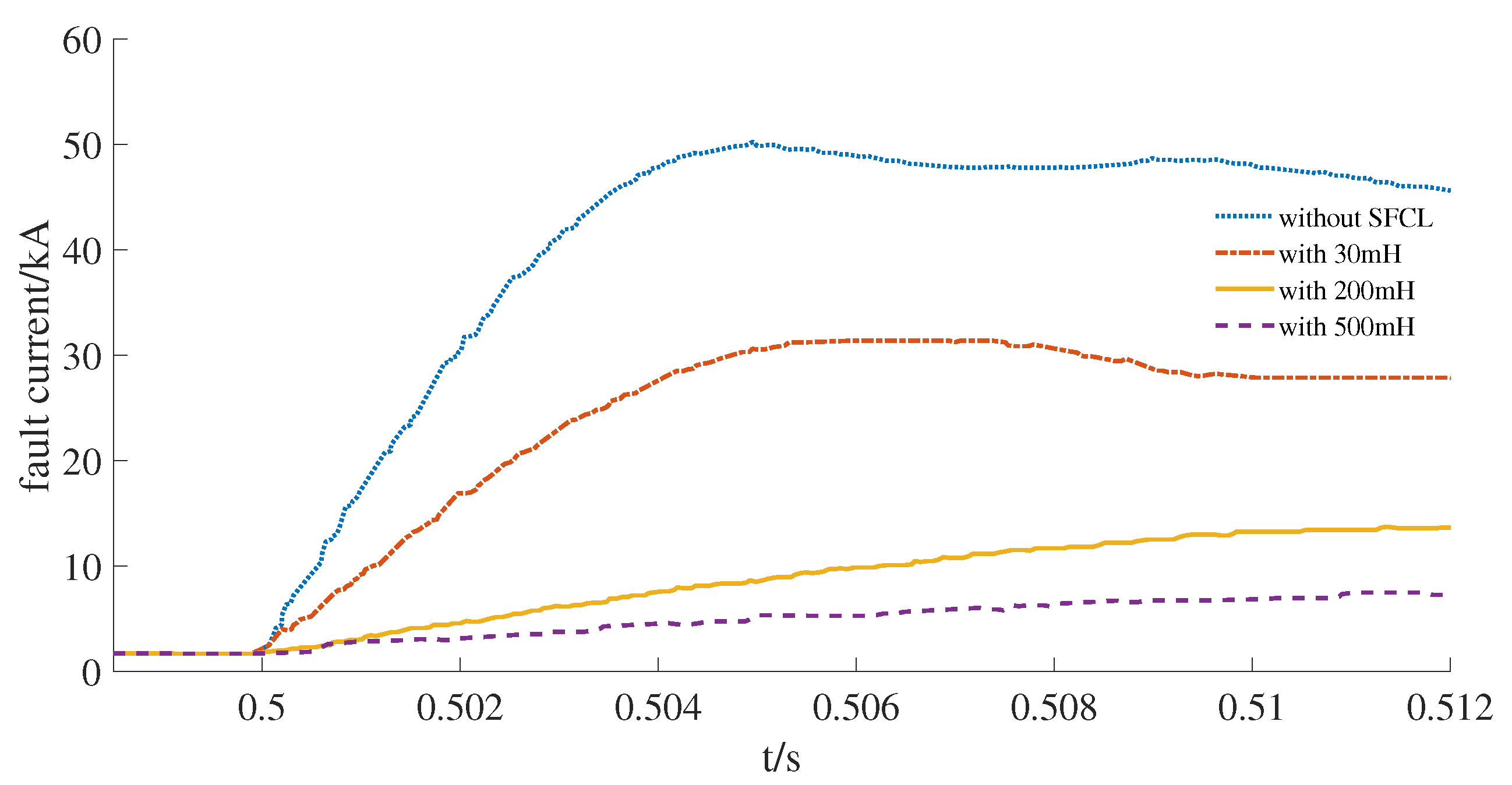

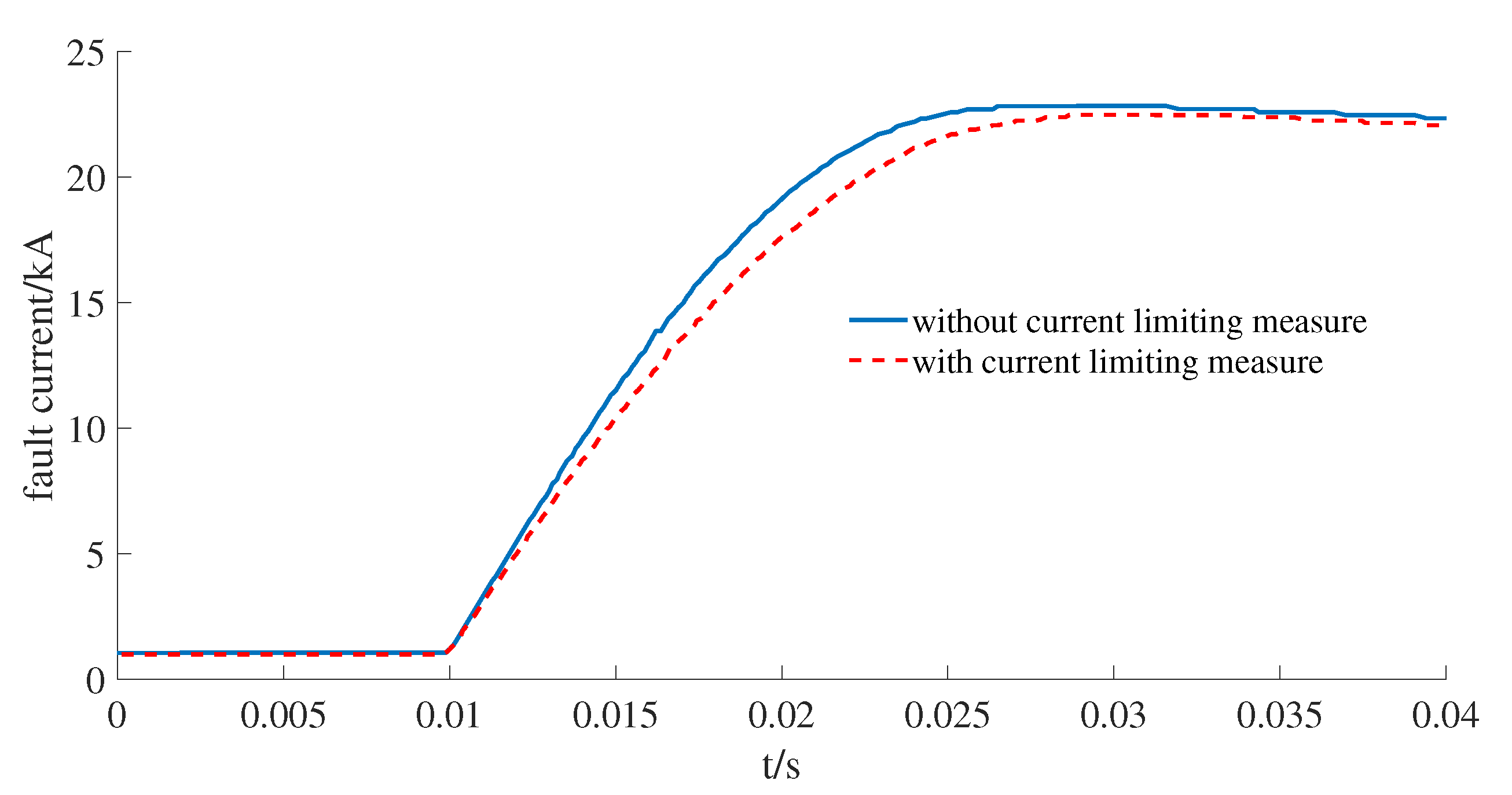

- SFCL: the SFCL operates under a superconducting state in normal operation state, which offers no resistance to the load current. Meanwhile, it can achieve high resistance under fault conditions [50,54,55,56]. Figure 13 shows the short circuit current with resistive FCLs in a four-terminal MMC-based power grid, whose structure and parameters can be found in [50]. It can be found that, although the amplitude of the DC short circuit current can be effectively decreased, the resistive SFCL cannot limit the rising rate. To remedy this defect, reference [50] proposes an improved structure for inductive SFCL, as shown in Figure 14.The inductive SFCL consists of several diodes and a saturated iron core SFCL. The saturated iron core SFCL is placed between the bridges composed with four diodes (). The proposed SFCL is connected in series in DC transmission lines via connectors A and B. Under normal conditions, the DC operational current can flow through the diodes groups and , or and . Wherever the short circuit fault occurs, the bi-directional SFCL allows for the fault current flow through. The copper made primary coils of the iron core SFCL are connected with the DC system. The secondary coils are made of superconductive materials and powered by a DC source. The external feature of the proposed inductive SFCL is equivalent to a small inductance and it has little impact on the system normal operational dynamics.The improved inductive SFCLs are applied to the four-terminal power grid that is shown in [50]. Under DC short circuit fault conditions, the inductance of the SFCL increases rapidly in order to restrain the rising rate of the short circuit current as shown in Figure 15. However, the permeability and the coil turns limit the size of the proposed inductive SFCL [50]. Moreover, superconductive FCL needs a high technological level and huge capital cost [47], which makes it unable to be widely applied in MMC-based MTDC power grids.

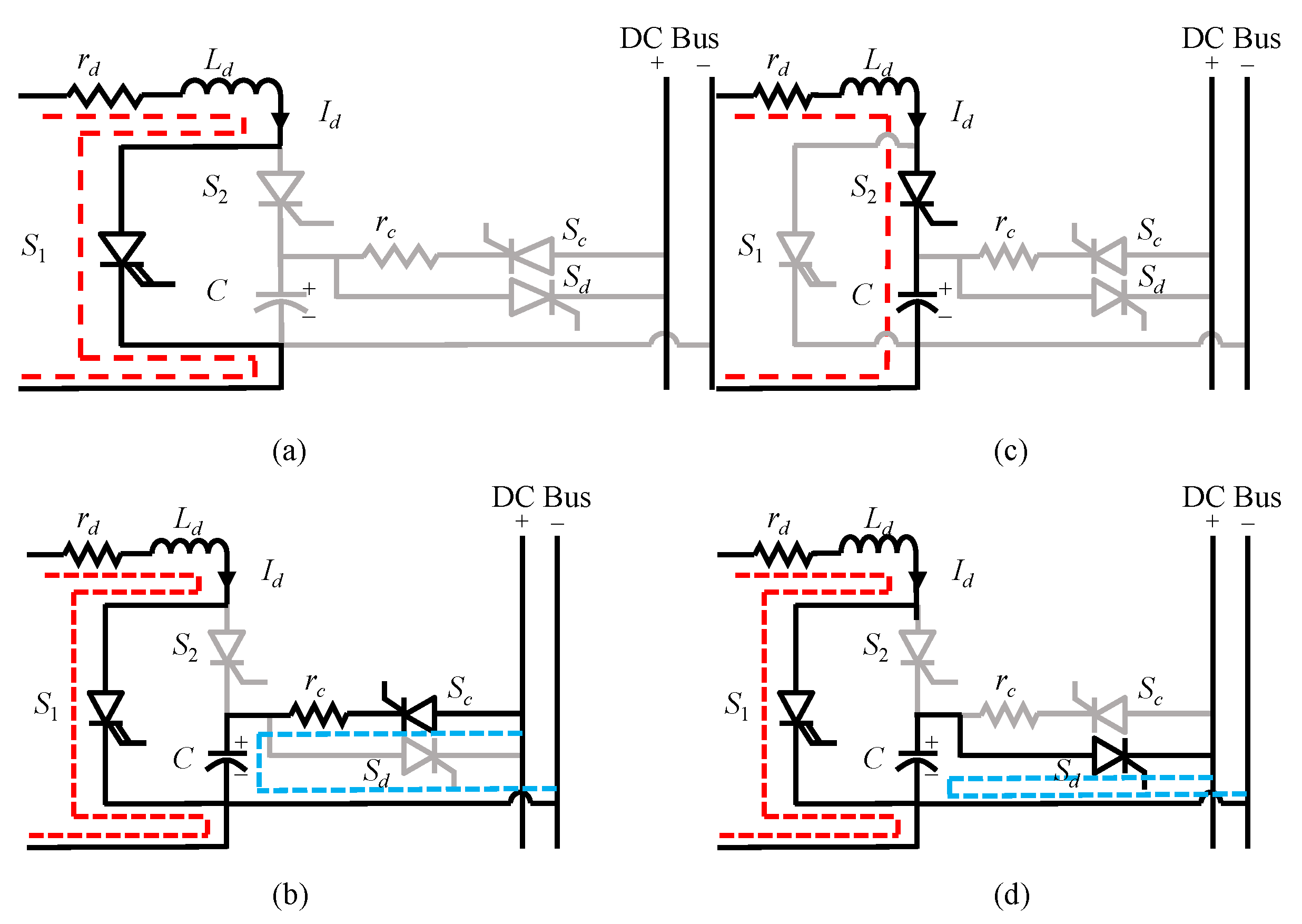

- NSFCL: a kind of structure of NSFCL, called capacitor-based FCL (CBFCL), is proposed in [57] and the power circuit structure of the CBFCL is shown Figure 16.The CBFCL consists of three main sections:

- -

- isolation transformer and rectifier;

- -

- a bypass switch; and,

- -

- capacitor bank section with DC bus and corresponding switches.

Switch is applied to flow the normal operation current, while is applied to flow the fault current. Energy is transfered between the capacitor bank section and the DC bus through and . The operation modes that are under normal conditions are shown in Figure 16a,b and operation modes under fault conditions are shown in Figure 16c,d. Under normal conditions, is turened off and the capacitor bank section is charged while taking into account resistor in series with capacitor bank after a time constant. Because the capacitor bank section receives electrical energy from the DC bus, which leads to a voltage rise. is conducted after the voltage of capacitor bank section reached a determined level. The proposed CBFCL circuit has little impact on the normal operation of the MMC-HVDC system. When a DC short circuit fault occurs, is conducted. By turning on in short circuit current limitation, it makes the capacitor bank section and inductor participate insert in current path.

4.2.3. MMC Fault Current Suppression Control Strategy

5. Conclusions and Future Trend Exploration

Author Contributions

Funding

Conflicts of Interest

References

- Shah, R.; Sánchez, J.C.; Preece, R.; Barnes, M. Stability and control of mixed AC–DC systems with VSC-HVDC: A review. IET Gener. Transm. Distrib. 2018, 12, 2207–2219. [Google Scholar] [CrossRef]

- Liu, G.; Xu, F.; Xu, Z.; Zhang, Z.; Tang, G. Assembly HVDC Breaker for HVDC Grids With Modular Multilevel Converters. IEEE Trans. Power Electron. 2017, 32, 931–941. [Google Scholar] [CrossRef]

- Debnath, S.; Qin, J.; Bahrani, B.; Saeedifard, M.; Barbosa, P. Operation, Control, and Applications of the Modular Multilevel Converter: A Review. IEEE Trans. Power Electron. 2015, 30, 37–53. [Google Scholar] [CrossRef]

- Qin, B.; Li, H.; Zhang, X.; Ding, T.; Ma, K.; Mei, S. Quantitative short-term voltage stability analysis of power systems integrated with DFIG-based wind farms. IET Gener. Transm. Distrib. 2020. [Google Scholar] [CrossRef]

- Ali, S.; Badar, J.; Akhter, F.; Bukhari, S.S.H.; Ro, J.-S. Real-Time Controller Design Test Bench for High-Voltage Direct Current Modular Multilevel Converters. Appl. Sci. 2020, 10, 6004. [Google Scholar] [CrossRef]

- An, T.; Tang, G.F.; Wang, W.N. Research and application on multiterminal and DC grids based on VSC-HVDC technology in China. High Volt. 2017, 2, 1–10. [Google Scholar] [CrossRef]

- Zhang, L.; Zou, Y.; Yu, J.; Qin, J.; Vittal, V.; Karady, G.G.; Shi, D.; Wang, Z. Modeling, control, and protection of modular multilevel converter-based multi-terminal HVDC systems: A review. CSEE J. Power Energy Syst. 2017, 3, 340–352. [Google Scholar] [CrossRef]

- Qin, B.; Li, H.; Zhou, X.; Li, J.; Liu, W. Low-Voltage Ride-Through Techniques in DFIG-BasedWind Turbines: A Review. Appl. Sci. 2020, 10, 2154. [Google Scholar] [CrossRef]

- Qin, B.; Ma, J.; Li, W.; Ding, T.; Sun, H.; Zomaya, A.Y. Decomposition-Based Stability Analysis for Isolated Power Systems With Reduced Conservativeness. IEEE Trans. Autom. Sci. Eng. 2020, 17, 1623–1632. [Google Scholar] [CrossRef]

- Wang, W.; Barnes, M. Power Flow Algorithms for Multi-Terminal VSC-HVDC With Droop Control. IEEE Trans. Power Syst. 2014, 29, 1721–1730. [Google Scholar] [CrossRef]

- Prieto-Araujo, E.; Bianchi, F.D.; Junyent-Ferre, A.; Gomis-Bellmunt, O. Methodology for Droop Control Dynamic Analysis of Multi-terminal VSC-HVDC Grids for Offshore Wind Farms. IEEE Trans. Power Deliv. 2011, 26, 2476–2485. [Google Scholar] [CrossRef]

- Thams, F.; Eriksson, R.; Molinas, M. Interaction of Droop Control Structures and Its Inherent Effect on the Power Transfer Limits in Multi-terminal VSC-HVDC. IEEE Trans. Power Deliv. 2017, 32, 182–192. [Google Scholar] [CrossRef]

- Li, C.; Zhao, C.; Xu, J.; Ji, Y.; Zhang, F.; An, T. A Pole-to-Pole Short-Circuit Fault Current Calculation Method for DC Grids. IEEE Trans. Power Syst. 2017, 32, 4943–4953. [Google Scholar] [CrossRef]

- Eriksson, R.; Beerten, J.; Ghandhari, M.; Belmans, R. Optimizing DC Voltage Droop Settings for AC/DC System Interactions. IEEE Trans. Power Deliv. 2014, 29, 362–369. [Google Scholar] [CrossRef]

- Franck, C.M. HVDC Circuit Breakers: A Review Identifying Future Research Needs. IEEE Trans. Power Deliv. 2011, 26, 998–1007. [Google Scholar] [CrossRef]

- Marquardt, R. Modular multilevel converter: An universal concept for HVDC-networks and extended DC-bus-applications. In Proceedings of the 2010 International Power Electronics Conference-ECCE ASIA, Sapporo, Japan, 21–24 June 2010; pp. 502–507. [Google Scholar]

- Qin, J.; Saeedifard, M.; Rockhill, A.; Zhou, R. Hybrid Design of Modular Multilevel Converters for HVDC Systems Based on Various Submodule Circuits. IEEE Trans. Power Deliv. 2015, 30, 385–394. [Google Scholar] [CrossRef]

- Li, T.; Gole, A.M.; Zhao, C. Harmonic Instability in MMC-HVDC Converters Resulting from Internal Dynamics. IEEE Trans. Power Deliv. 2016, 31, 1738–1747. [Google Scholar] [CrossRef]

- Meng, X.; Han, J.; Pfannschmidt, J.; Wang, L.; Li, W.; Zhang, F.; Belanger, J. Combining Detailed Equivalent Model With Switching-Function-Based Average Value Model for Fast and Accurate Simulation of MMCs. IEEE Trans. Energy Convers. 2020, 35, 484–496. [Google Scholar] [CrossRef]

- Guo, D.; Rahman, M.H.; Ased, G.P.; Xu, L.; Emheme, A.; Burt, G.M.; Audichya, Y. Detailed quantitative comparison of half-bridge modular multilevel converter modelling methods. J. Eng. 2019, 2019, 1292–1298. [Google Scholar] [CrossRef]

- Song, Q.; Liu, W.; Li, X.; Rao, H.; Xu, S.; Li, L. A Steady-State Analysis Method for a Modular Multilevel Converter. IEEE Trans. Power Electron. 2013, 28, 3702–3713. [Google Scholar] [CrossRef]

- Xu, J.; Gole, A.M.; Zhao, C. The Use of Averaged-Value Model of Modular Multilevel Converter in DC Grid. IEEE Trans. Power Deliv. 2015, 30, 519–528. [Google Scholar] [CrossRef]

- Saad, H.; Dennetière, S.; Mahseredjian, J.; Delarue, P.; Guillaud, X.; Peralta, J.; Nguefeu, S. Modular Multilevel Converter Models for Electromagnetic Transients. IEEE Trans. Power Deliv. 2014, 29, 1481–1489. [Google Scholar] [CrossRef]

- Guo, C.; Yang, J.; Zhao, C. Investigation of Small-Signal Dynamics of Modular Multilevel Converter Under Unbalanced Grid Conditions. IEEE Trans. Ind. Electron. 2019, 66, 2269–2279. [Google Scholar] [CrossRef]

- Guo, C.; Liu, W.; Zhao, J.; Zhao, C. Impact of control system on small-signal stability of hybrid multi-infeed HVDC system. IET Gener. Transm. Distrib. 2018, 12, 4233–4239. [Google Scholar] [CrossRef]

- Peralta, J.; Saad, H.; Dennetiere, S.; Mahseredjian, J.; Nguefeu, S. Detailed and Averaged Models for a 401-Level MMC–HVDC System. IEEE Trans. Power Deliv. 2012, 27, 1501–1508. [Google Scholar] [CrossRef]

- Saad, H.; Peralta, J.; Dennetière, S.; Mahseredjian, J. Dynamic Averaged and Simplified Models for MMC-Based HVDC Transmission Systems. IEEE Trans. Power Deliv. 2013, 2013 28, 1723–1730. [Google Scholar] [CrossRef]

- Liu, S.; Xu, Z.; Hua, W.; Tang, G.; Xue, Y. Electromechanical Transient Modeling of Modular Multilevel Converter Based Multi-Terminal HVDC Systems. IEEE Trans. Power Syst. 2014, 29, 72–83. [Google Scholar] [CrossRef]

- Boyu, Q.; Wansong, L.; Ruowei, Z.; Tao, D.; Jialing, L. Small-signal stability analysis and optimal control parameters design of MMC-based MTDC transmission systems. IET Gener. Transm. Distrib. 2020. [Google Scholar] [CrossRef]

- Yu, S.; Zhang, S.; Wei, Y.; Zhu, Y.; Sun, Y. Efficient and accurate hybrid model of modular multilevel converters for large MTDC systems. IET Gener. Transm. Distrib. 2018, 12, 1565–1572. [Google Scholar] [CrossRef]

- Gnanarathna, U.N.; Gole, A.M.; Jayasinghe, R.P. Efficient Modeling of Modular Multilevel HVDC Converters (MMC) on Electromagnetic Transient Simulation Programs. IEEE Trans. Power Deliv. 2011, 26, 316–324. [Google Scholar] [CrossRef]

- Ajaei, F.B.; Iravani, R. Enhanced Equivalent Model of the Modular Multilevel Converter. IEEE Trans. Power Deliv. 2015, 30, 666–673. [Google Scholar] [CrossRef]

- Wang, S.; Alsokhiry, F.S.; Adam, G.P. Impact of Submodule Faults on the Performance of Modular Multilevel Converters. Energies 2020, 13, 4089. [Google Scholar] [CrossRef]

- Bucher, M.K.; Franck, C.M. Contribution of Fault Current Sources in Multiterminal HVDC Cable Networks. IEEE Trans. Power Deliv. 2013, 28, 1796–1803. [Google Scholar] [CrossRef]

- Xu, J.; Zhu, S.; Li, C.; Zhao, C. The Enhanced DC Fault Current Calculation Method of MMC-HVDC Grid with FCLs. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 1758–1767. [Google Scholar] [CrossRef]

- Ye, H.; Gao, S.; Li, G.; Liu, Y. Efficient Estimation and Characteristic Analysis of Short-Circuit Currents for MMC-MTDC Grids. IEEE Trans. Ind. Electron. 2020. [Google Scholar] [CrossRef]

- Wang, Y.; Zhao, C.; Guo, C.; Rehman, A.U. Dynamics and small signal stability analysis of PMSG-based wind farm with an MMC-HVDC system. CSEE J. Power Energy Syst. 2020, 6, 226–235. [Google Scholar]

- Ji, K.; Tang, G.; Yang, J.; Li, Y.; Liu, D. Harmonic Stability Analysis of MMC-Based DC System Using DC Impedance Model. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 1152–1163. [Google Scholar] [CrossRef]

- Daryabak, M.; Filizadeh, S.; Jatskevich, J.; Davoudi, A.; Cano, J.; Mehrizi-Sani, A. Modeling of LCC-HVDC Systems Using Dynamic Phasors. IEEE Trans. Power Deliv. 2014, 29, 1989–1998. [Google Scholar] [CrossRef]

- Gao, S.; Ye, H.; Liu, Y. Accurate and Efficient Estimation of Short-Circuit Current for MTDC Grids Considering MMC Control. IEEE Trans. Power Deliv. 2020, 35, 1541–1552. [Google Scholar] [CrossRef]

- Langwasser, M.; Carne, G.D.; Liserre, M.; Biskoping, M. Improved Fault Current Calculation Method for Pole-to-Pole Faults in MMC Multi-Terminal HVDC Grids Considering Control Dynamics. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018. [Google Scholar]

- Guo, Y.; Li, H.; Liang, Y.; Wang, G. A Method to Calculate Short-Circuit Faults in High-Voltage DC Grids. IEEE Trans. Power Deliv. 2020. [Google Scholar] [CrossRef]

- Xu, J.; Zhao, X.; Jing, H.; Liang, J.; Zhao, C. DC Fault Current Clearance at the Source Side of HVDC Grid Using Hybrid MMC. IEEE Trans. Power Deliv. 2020, 35, 140–149. [Google Scholar] [CrossRef]

- Vidal-Albalate, R.; Forner, J. Modeling and Enhanced Control of Hybrid Full Bridge–Half Bridge MMCs for HVDC Grid Studies. Energies 2020, 13, 180. [Google Scholar] [CrossRef]

- Tang, G.; Xu, Z.; Zhou, Y. Impacts of Three MMC-HVDC Configurations on AC System Stability Under DC Line Faults. IEEE Trans. Power Syst. 2014, 29, 3030–3040. [Google Scholar] [CrossRef]

- Solas, E.; Abad, G.; Barrena, J.A.; Aurtenetxea, S.; Cárcar, A.; Zając, L. Modular Multilevel Converter With Different Submodule Concepts—Part I: Capacitor Voltage Balancing Method. IEEE Trans. Ind. Electron. 2013, 60, 4525–4535. [Google Scholar] [CrossRef]

- Huang, Q.; Zou, G.; Sun, W.; Xu, C. Fault current limiter for the MMC-based multi-terminal DC grids. IET Gener. Transm. Distrib. 2020, 14, 3269–3277. [Google Scholar] [CrossRef]

- Rao, H. Architecture of Nan’ao multi-terminal VSC-HVDC system and its multi-functional control. CSEE J. Power Energy Syst. 2015, 1, 9–18. [Google Scholar] [CrossRef]

- Liu, K.; Huai, Q.; Qin, L.; Zhu, S.; Liao, X.; Li, Y.; Ding, H. Enhanced Fault Current-Limiting Circuit Design for a DC Fault in a Modular Multilevel Converter-Based High-Voltage Direct Current System. Appl. Sci. 2019, 9, 1661. [Google Scholar] [CrossRef]

- Wang, C.; Li, B.; He, J.; Xin, Y. Design and Application of the SFCL in the Modular Multilevel Converter Based DC System. IEEE Trans. Appl. Supercond. 2017, 27, 1–4. [Google Scholar] [CrossRef]

- Wang, S.; Li, C.; Adeuyi, O.D.; Li, G.; Ugalde-Loo, C.E.; Liang, J. Coordination of MMCs With Hybrid DC Circuit Breakers for HVDC Grid Protection. IEEE Trans. Power Deliv. 2019, 2019 34, 11–22. [Google Scholar] [CrossRef]

- Ghanbari, T.; Farjah, E.; Zandnia, A. Development of a high-performance bridge-type fault current limiter. IET Gener. Transm. Distrib. 2014, 8, 486–494. [Google Scholar] [CrossRef]

- Sujuan, X.; Yufeng, Q.; Tianshu, B. Resistive DC fault current limiter. J. Eng. 2017, 2017, 1682–1685. [Google Scholar] [CrossRef]

- Jiang, Z.; Wang, Y.; Dai, S.; Ma, T.; Yuan, X.; Liu, M.; Chen, H.; Wang, M.; Peng, C. Application and Design of Resistive SFCL in pm160 kV MMC-HVdc System. IEEE Trans. Appl. Supercond. 2019, 29, 1–5. [Google Scholar]

- Li, B.; He, J. Studies on the Application of R-SFCL in the VSC-Based DC Distribution System. IEEE Trans. Appl. Supercond. 2016, 26, 1–5. [Google Scholar] [CrossRef]

- Khan, U.A.; Lee, J.; Amir, F.; Lee, B. A Novel Model of HVDC Hybrid-Type Superconducting Circuit Breaker and Its Performance Analysis for Limiting and Breaking DC Fault Currents. IEEE Trans. Appl. Supercond. 2015, 25, 1–9. [Google Scholar] [CrossRef]

- Nourmohamadi, H.; Nazari-Heris, M.; Sabahi, M.; Abapour, M. A Novel Structure for Bridge-Type Fault Current Limiter: Capacitor-Based Nonsuperconducting FCL. IEEE Trans. Power Electron. 2018, 33, 3044–3051. [Google Scholar] [CrossRef]

- Xin, Y.; Yang, Y.; Wang, W.; Wang, T.; Xu, G.; Dong, Q. Current Suppresvsion Method for DC Side Short Circuit Fault of MMC. In Proceedings of the 4th IEEE Workshop on the Electronic Grid (eGRID), Xiamen, China, 11–14 November 2019; pp. 1–8. [Google Scholar]

- Qin, B.; Sun, H.; Ma, J.; Li, W.; Ding, T.; Wang, Z.; Zomaya, A.Y. Robust H∞ Control of Doubly Fed Wind Generator Via State-Dependent Riccati Equation Technique. IEEE Trans. Power Syst. 2019, 34, 2390–2400. [Google Scholar] [CrossRef]

- Cui, S.; Sul, S. A Comprehensive DC Short-Circuit Fault Ride through Strategy of Hybrid Modular Multilevel Converters (MMCs) for Overhead Line Transmission. IEEE Trans. Power Electron. 2016, 31, 7780–7796. [Google Scholar] [CrossRef]

| Commissioning Year | Name | Location | Terminals | Capacity, | DC Voltage, |

|---|---|---|---|---|---|

| 2020 | Zhangbei | China | 4 | 3000 | |

| 2019 | BorWin3 | Germany | 2 | 900 | |

| 2016 | Chongqing-Hubei | China | 2 | 2500 | |

| 2016 | Luxi | China | 2 | 1000 | |

| 2015 | Helwin2 | German | 2 | 690 | |

| 2015 | Xiamen | China | 2 | 1000 | |

| 2014 | Zhoushan | China | 5 | 1000 | |

| 2013 | Nan’ao | China | 3 | 200 | |

| 2011 | Nanhui | China | 2 | 18 | |

| 2010 | Trans Bay Cable | America | 2 | 400 |

| SM Topologies | Output Voltage Level | DC Short Circuit Fault Ride through Capability | Power Losses |

|---|---|---|---|

| HB-SM | No | Low | |

| FB-SM | Yes | High | |

| CD-SM | Yes | Moderate | |

| Three-level FC | No | Low | |

| Three-level NPC | No | Moderate | |

| 5LCC-SM | Yes | Moderate |

| Model | Single | Control | Circuit | System | Control | SM | DC |

|---|---|---|---|---|---|---|---|

| SM | System | Current | Level | Strategy | Level | Fault | |

| Dynamics | Dynamics | Dynamics | Analysis | Design | Analysis | Analysis | |

| DSM | √ | √ | √ | × | × | √ | √ |

| AVM | × | √ | √ | √ | √ | × | √ |

| SAVM | × | √ | × | √ | √ | × | √ |

| DEM | √ | √ | √ | × | √ | √ | × |

| EDM | × | × | × | × | × | × | √ |

| Method | SM Change | Add Devices | Increase Impedance | Iron Core | Superconducting Materials | Extra Cost | Impact on Normal Condition |

|---|---|---|---|---|---|---|---|

| FB-SM | √ | × | × | × | × | B | S |

| DB-SM | √ | × | × | × | × | B | S |

| 5LCC-SM | √ | × | × | × | × | B | S |

| DC inductor | × | √ | √ | √ | × | S | B |

| Solid FCL | × | √ | √ | × | × | M | S |

| SFCL | × | √ | √ | √ | √ | B | S |

| CBFCL | × | √ | √ | × | × | B | S |

| Hvbird MMC | √ | × | × | × | × | B | S |

| MMC control | × | × | × | × | × | × | S |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Qin, B.; Liu, W.; Zhang, R.; Liu, J.; Li, H. Review on Short-circuit Current Analysis and Suppression Techniques for MMC-HVDC Transmission Systems. Appl. Sci. 2020, 10, 6769. https://doi.org/10.3390/app10196769

Qin B, Liu W, Zhang R, Liu J, Li H. Review on Short-circuit Current Analysis and Suppression Techniques for MMC-HVDC Transmission Systems. Applied Sciences. 2020; 10(19):6769. https://doi.org/10.3390/app10196769

Chicago/Turabian StyleQin, Boyu, Wansong Liu, Ruowei Zhang, Jialing Liu, and Hengyi Li. 2020. "Review on Short-circuit Current Analysis and Suppression Techniques for MMC-HVDC Transmission Systems" Applied Sciences 10, no. 19: 6769. https://doi.org/10.3390/app10196769

APA StyleQin, B., Liu, W., Zhang, R., Liu, J., & Li, H. (2020). Review on Short-circuit Current Analysis and Suppression Techniques for MMC-HVDC Transmission Systems. Applied Sciences, 10(19), 6769. https://doi.org/10.3390/app10196769