Analysis of Work-Function Variation Effects in a Tunnel Field-Effect Transistor Depending on the Device Structure

Abstract

Featured Application

Abstract

1. Introduction

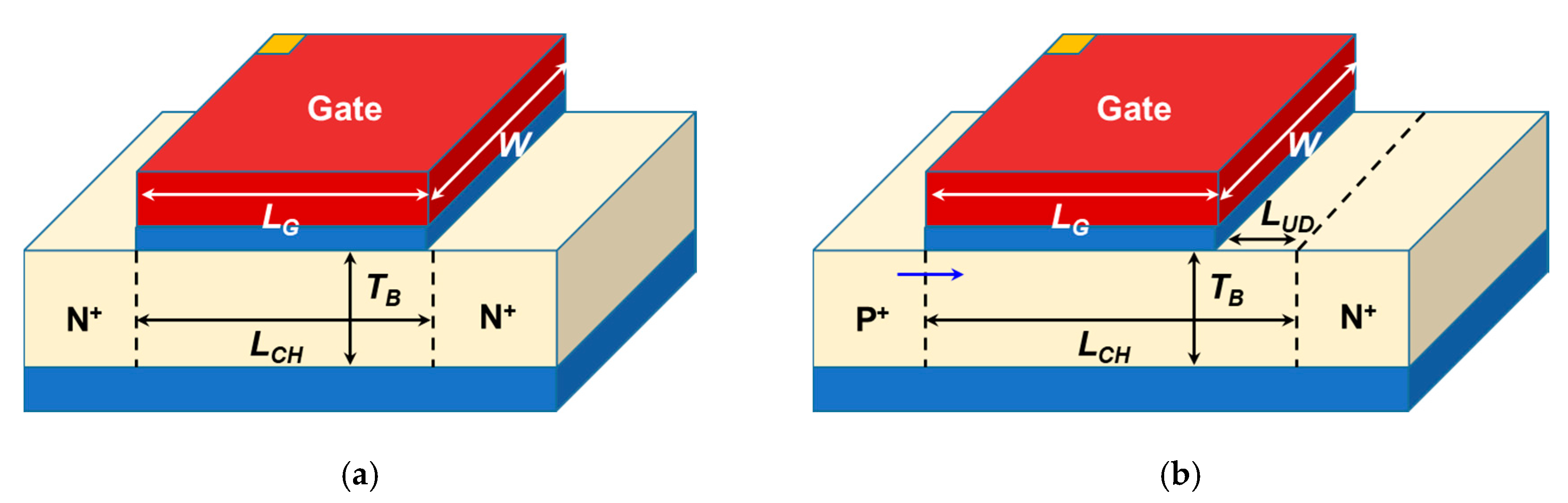

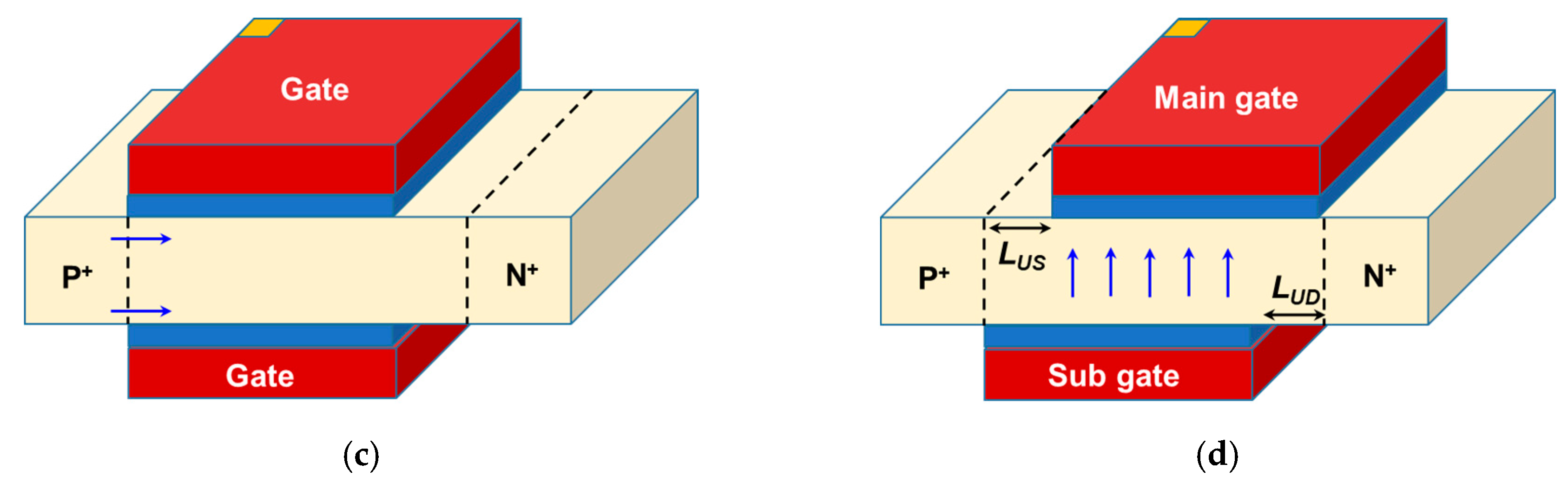

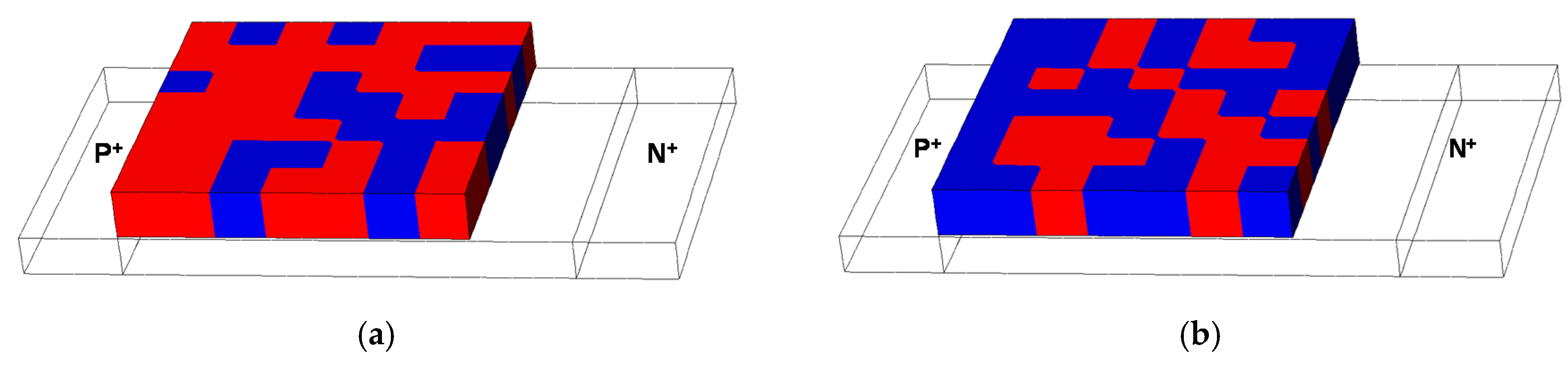

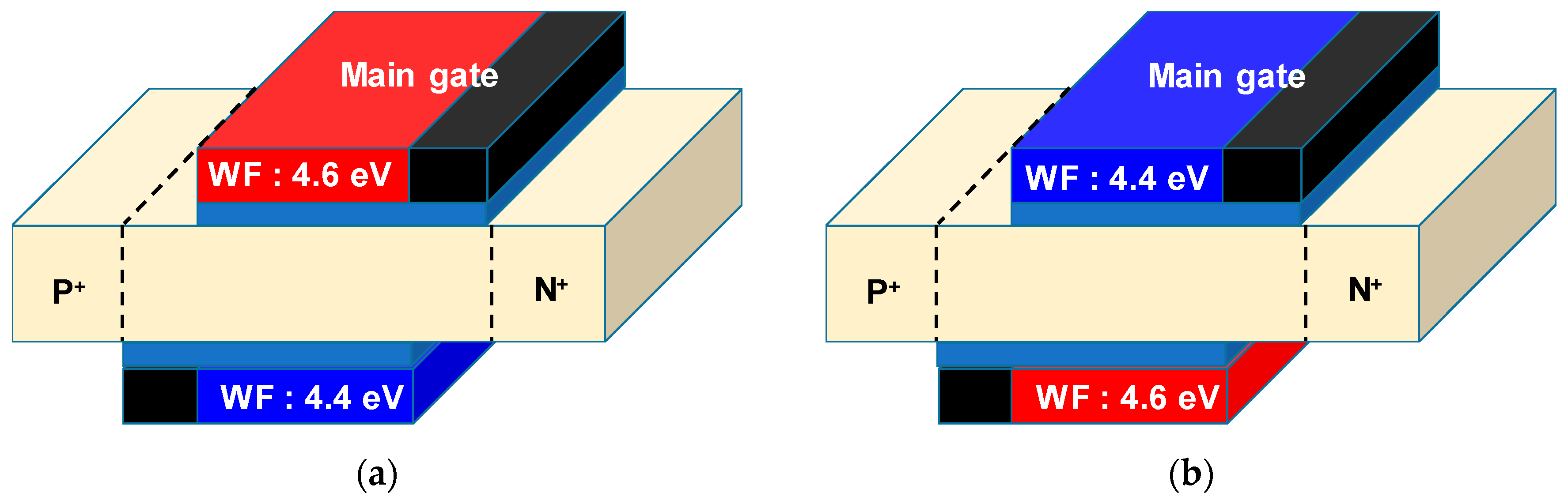

2. Device Structure and Simulation Method

3. Results and Discussions

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Lundstrom, M. Device physics at the scaling limit: What matters?[MOSFETs]. In Proceedings of the International Electron Device Meeting (IEDM), Washington, DC, USA, 8–10 December 2003. [Google Scholar] [CrossRef]

- Frank, D.J.; Dennard, R.H.; Nowak, E.; Solomon, P.M.; Taur, Y.; Wong, H.S.P. Device scaling limits of Si MOSFETs and their application dependencies. Proc. IEEE 2001, 89, 259–287. [Google Scholar] [CrossRef]

- Cheung, K.P. On the 60 mV/dec @ 300 K limit for MOSFET subthreshold swing. In Proceedings of the International Symposium on VLSI Technology, System and Application, Hsin Chu, Taiwan, 26–28 April 2010. [Google Scholar] [CrossRef]

- Li, K.-S.; Chen, P.-G.; Lai, T.-Y.; Lin, C.-H.; Cheng, C.-C.; Chen, C.-C.; Wei, Y.-J.; Hou, Y.-F.; Liao, M.-H.; Lee, M.-H. Sub-60mV-swing negative-capacitance FinFET without hysteresis. In Proceedings of the International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015. [Google Scholar] [CrossRef]

- Lin, C.-I.; Khan, A.I.; Salahuddin, S.; Hu, C. Effects of the variation of ferroelectric properties on negative capacitance FET characteristics. IEEE Trans. Electron Devices 2016, 63, 2197–2199. [Google Scholar] [CrossRef]

- McGuire, F.A.; Cheng, Z.; Price, K.; Franklin, A.D. Sub-60 mV/decade switching in 2D negative capacitance field-effect transistors with integrated ferroelectric polymer. Appl. Phys. Lett. 2016, 109, 93101. [Google Scholar] [CrossRef]

- Huang, Q.; Huang, R.; Pan, Y.; Tan, S.; Wang, Y. Resistive-Gate Field-Effect Transistor: A Novel Steep-Slope Device Based on a Metal—Insulator—Metal—Oxide Gate Stack. IEEE Electron Device Lett. 2014, 35, 877–879. [Google Scholar] [CrossRef]

- Kam, H.; Lee, D.T.; Howe, R.T.; King, T.-J. A new nano-electro-mechanical field effect transistor (NEMFET) design for low-power electronics. In Proceedings of the International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–7 December 2005. [Google Scholar] [CrossRef]

- Abelé, N.; Fritschi, R.; Boucart, K.; Casset, F.; Ancey, P.; Ionescu, A.M. Suspended-gate MOSFET: Bringing new MEMS functionality into solid-state MOS transistor. In Proceedings of the International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–7 December 2005. [Google Scholar] [CrossRef]

- Padilla, A.; Yeung, C.W.; Shin, C.; Hu, C.; Liu, T.-J.K. Feedback FET: A novel transistor exhibiting steep switching behavior at low bias voltages. In Proceedings of the International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008. [Google Scholar] [CrossRef]

- Hwang, S.; Kim, H.; Kwon, D.W.; Lee, J.-H.; Park, B.-G. Si1-xGex Positive Feedback Field-effect Transistor with Steep Subthreshold Swing for Low-voltage Operation. J. Semicond. Technol. Sci. 2017, 17, 216–222. [Google Scholar] [CrossRef]

- Choi, W.Y.; Song, J.Y.; Lee, J.D.; Park, Y.J.; Park, B.-G. 100-nm n-/p-channel I-MOS using a novel self-aligned structure. IEEE Electron Device Lett. 2005, 26, 261–263. [Google Scholar] [CrossRef]

- Ramaswamy, S.; Kumar, M.J. Junction-less impact ionization MOS: Proposal and investigation. IEEE Trans. Electron Devices 2014, 61, 4295–4298. [Google Scholar] [CrossRef]

- Huang, X.; Fang, R.; Yang, C.; Fu, K.; Fu, H.; Chen, H.; Yang, T.-H.; Zhou, J.; Montes, J.; Kozicki, M. Steep-slope field-effect transistors with AlGaN/GaN HEMT and oxide-based threshold switching device. Nanotechnology 2019, 30, 215201. [Google Scholar] [CrossRef]

- Ionescu, A.M.; Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 2011, 479, 329–337. [Google Scholar] [CrossRef]

- Choi, W.Y.; Park, B.-G.; Lee, J.D.; Liu, T.-J.K. Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 2007, 28, 743–745. [Google Scholar] [CrossRef]

- Kim, S.W.; Kim, J.H.; Liu, T.-J.K.; Choi, W.Y.; Park, B.-G. Demonstration of L-shaped tunnel field-effect transistors. IEEE Trans. Electron Devices 2016, 63, 1774–1778. [Google Scholar] [CrossRef]

- Lee, R.; Kwon, D.W.; Kim, S.; Kim, D.H.; Park, B.-G. Investigation of feasibility of tunneling field effect transistor (TFET) as highly sensitive and multi-sensing biosensors. J. Semicond. Technol. Sci. 2017, 17, 141–146. [Google Scholar] [CrossRef]

- Mayer, F.; Le Royer, C.; Damlencourt, J.F.; Romanjek, K.; Andrieu, F.; Tabone, F.C.; Previtali, B.; Deleonibus, S. Impact of SOI, Si1−xGexOI and GeOI substrates on CMOS compatible Tunnel FET performance. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008. [Google Scholar] [CrossRef]

- Gandhi, R.; Chen, Z.; Singh, N.; Banerjee, K.; Lee, S. CMOS-compatible vertical-silicon-nanowire gate-all-around ptype tunneling FETs with ≤50-mV/decade subthreshold swing. IEEE Electron Device Lett. 2011, 32, 1504–1506. [Google Scholar] [CrossRef]

- De Michielis, L.; Lattanzio, L.; Ionescu, A.M. Understanding the superlinear onset of tunnel-FET output characteristic. IEEE Electron Device Lett. 2012, 33, 1523–1525. [Google Scholar] [CrossRef]

- Toh, E.-H.; Wang, G.H.; Samudra, G.; Yeo, Y.-C. Device physics and design of double-gate tunneling field-effect transistor by silicon film thickness optimization. Appl. Phys. Lett. 2007, 90, 263507. [Google Scholar] [CrossRef]

- Kim, S.H.; Kam, H.; Hu, C.; Liu, T.-J.K. Germanium-source tunnel field effect transistors with record high I ON/I OFF. In Proceedings of the International Conference on VLSI Technology, Kyoto, Japan, 15–18 June 2009. [Google Scholar]

- Nayfeh, O.M.; Chleirigh, C.N.; Hennessy, J.; Gomez, L.; Hoyt, J.L.; Antoniadis, D.A. Design of tunneling field-effect transistors using strained-silicon/strained-germanium type-II staggered heterojunctions. IEEE Electron Device Lett. 2008, 29, 1074–1077. [Google Scholar] [CrossRef]

- Han, G.; Guo, P.; Yang, Y.; Zhan, C.; Zhou, Q.; Yeo, Y.-C. Silicon-based tunneling field-effect transistor with elevated germanium source formed on (110) silicon substrate. Appl. Phys. Lett. 2011, 98, 153502. [Google Scholar] [CrossRef]

- Kim, M.; Wakabayashi, Y.; Nakane, R.; Yokoyama, M.; Takenaka, M.; Takagi, S. High Ion/Ioff Ge-source ultrathin body strained-SOI tunnel FETs. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2014. [Google Scholar] [CrossRef]

- Takagi, S.; Kim, M.; Noguchi, M.; Ji, S.-M.; Nishi, K.; Takenaka, M. III-V and Ge/strained SOI tunnel FET technologies for low power LSIs. In Proceedings of the International Conference on VLSI Technology, Kyoto, Japan, 16–19 June 2015. [Google Scholar] [CrossRef]

- Krishnamohan, T.; Kim, D.; Raghunathan, S.; Saraswat, K. Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and <60mV/dec subthreshold slope. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008. [Google Scholar] [CrossRef]

- Kim, G.; Lee, J.; Kim, J.H.; Kim, S. High on-current Ge-channel heterojunction tunnel field-effect transistor using direct band-to-band tunneling. Micromachines 2019, 10, 77. [Google Scholar] [CrossRef]

- Kim, J.H.; Kim, H.W.; Kim, G.; Kim, S.; Park, B.-G. Demonstration of Fin-Tunnel Field-Effect Transistor with Elevated Drain. Micromachines 2019, 10, 30. [Google Scholar] [CrossRef]

- Kim, J.H.; Kim, H.W.; Shin, S.-S.; Kim, S.; Park, B.-G. Transient Analysis of Tunnel Field-Effect Transistor with Raised Drain. J. Nanosci. Nanotechnol. 2019, 19, 6212–6216. [Google Scholar] [CrossRef]

- Boucart, K.; Ionescu, A.M. Double-gate tunnel FET with high-κ gate dielectric. IEEE Trans. Electron Devices 2007, 54, 1725–1733. [Google Scholar] [CrossRef]

- Choi, K.M.; Choi, W.Y. Work-function variation effects of tunneling field-effect transistors (TFETs). IEEE Electron Device Lett. 2013, 34, 942–944. [Google Scholar] [CrossRef]

- Lattanzio, L.; De Michielis, L.; Ionescu, A.M. The electron–hole bilayer tunnel FET. Solid State Electron. 2012, 74, 85–90. [Google Scholar] [CrossRef]

- Lattanzio, L.; Dagtekin, N.; De Michielis, L.; Ionescu, A.M. On the static and dynamic behavior of the germanium electron-hole bilayer tunnel FET. IEEE Trans. Electron Devices 2012, 59, 2932–2938. [Google Scholar] [CrossRef]

- Alper, C.; Palestri, P.; Padilla, J.L.; Ionescu, A.M. The electron-hole bilayer TFET: Dimensionality effects and optimization. IEEE Trans. Electron Devices 2016, 63, 2603–2609. [Google Scholar] [CrossRef]

- Padilla, J.L.; Alper, C.; Gamiz, F.; Ionescu, A.M. Switching behavior constraint in the heterogate electron–hole bilayer tunnel FET: The combined interplay between quantum confinement effects and asymmetric configurations. IEEE Trans. Electron Devices 2016, 63, 2570–2576. [Google Scholar] [CrossRef]

- Kim, S.; Choi, W.Y.; Park, B.-G. Vertical-structured electron-hole bilayer tunnel field-effect transistor for extremely low-power operation with high scalability. IEEE Trans. Electron Devices 2018, 65, 2010–2015. [Google Scholar] [CrossRef]

- Dadgour, H.; De, V.; Banerjee, K. Statistical modeling of metal-gate work-function variability in emerging device technologies and implications for circuit design. In Proceedings of the IEEE/ACM International Conference on Computer-Aided Design, San Jose, CA, USA, 10–13 November 2008. [Google Scholar] [CrossRef]

- Lima, L.P.B.; Moreira, M.A.; Diniz, J.A.; Doi, I. Titanium nitride as promising gate electrode for MOS technology. Phys. Status Solidi C 2012, 9, 1427–1430. [Google Scholar] [CrossRef]

- Bolotov, L.; Fukuda, K.; Tada, T.; Matsukawa, T.; Masahara, M. Spatial variation of the work function in nano-crystalline TiN films measured by dual-mode scanning tunneling microscopy. Jpn. J. Appl. Phys. 2015, 54, 04DA03. [Google Scholar] [CrossRef]

- He, J.L.; Setsuhara, Y.; Shimizu, I.; Miyake, S. Structure refinement and hardness enhancement of titanium nitride films by addition of copper. Surf. Coat. Technol. 2001, 137, 38–42. [Google Scholar] [CrossRef]

- Ohmori, K.; Matsuki, T.; Ishikawa, D.; Morooka, T.; Aminaka, T.; Sugita, Y.; Chikyow, T.; Shiraishi, K.; Nara, Y.; Yamada, K. Impact of additional factors in threshold voltage variability of metal/high-k gate stacks and its reduction by controlling crystalline structure and grain size in the metal gates. In Proceedings of the International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008. [Google Scholar] [CrossRef]

- Ruiz, A.; Seoane, N.; Claramunt, S.; García-Loureiro, A.; Porti, M.; Couso, C.; Martin-Martinez, J.; Nafria, M. Workfunction fluctuations in polycrystalline TiN observed with KPFM and their impact on MOSFETs variability. Appl. Phys. Lett. 2019, 114, 093502. [Google Scholar] [CrossRef]

- Synopsys, Inc. Sentaurus Device User Guide; Synopsys Inc.: Mountain View, CA, USA, 2015; Available online: http://www.sentaurus.dsod.pl/manuals/data/sdevice_ug.pdf (accessed on 30 April 2020).

- Kao, K.-H.; Verhulst, A.S.; Vandenberghe, W.G.; Soree, B.; Groeseneken, G.; De Meyer, K. Direct and indirect band-to-band tunneling in germanium-based TFETs. IEEE Trans. Electron Devices 2011, 59, 292–301. [Google Scholar] [CrossRef]

- Llorente, C.D.; Colinge, J.-P.; Martinie, S.; Cristoloveanu, S.; Wan, J.; Le Royer, C.; Ghibaudo, G.; Vinet, M. New prospects on high on-current and steep subthreshold slope for innovative Tunnel FET architectures. Solid State Electron. 2019, 159, 26–37. [Google Scholar] [CrossRef]

- Li, W.; Liu, H.; Wang, S.; Chen, S.; Han, T.; Yang, K. Design and investigation of dopingless dual-gate tunneling transistor based on line tunneling. AIP Adv. 2019, 9, 045109. [Google Scholar] [CrossRef]

- Lee, J.W.; Choi, W.Y. Design Guidelines for Gate-Normal Hetero-Gate-Dielectric (GHG) Tunnel Field-Effect Transistors (TFETs). IEEE Access 2020, 8, 67617–67624. [Google Scholar] [CrossRef]

- Boucart, K.; Ionescu, A.M. A new definition of threshold voltage in tunnel FETs. Solid State Electron. 2008, 52, 1318–1323. [Google Scholar] [CrossRef]

- Ortiz-Conde, A.; García-Sánchez, F.J.; Muci, J.; Sucre-González, A.; Martino, J.A.; Der Agopian, P.G.; Claeys, C. Threshold voltage extraction in Tunnel FETs. Solid State Electron. 2014, 93, 49–55. [Google Scholar] [CrossRef]

- Dadgour, H.F.; Endo, K.; De, V.K.; Banerjee, K. Grain-orientation induced work function variation in nanoscale metal-gate transistors—Part I: Modeling, analysis, and experimental validation. IEEE Trans. Electron Devices 2010, 57, 2504–2514. [Google Scholar] [CrossRef]

- Nam, H.; Shin, C. Study of high-k/metal-gate work-function variation using Rayleigh distribution. IEEE Electron Device Lett. 2013, 34, 532–534. [Google Scholar] [CrossRef]

- Nam, H.; Lee, Y.; Park, J.-D.; Shin, C. Study of Work-Function Variation in High-κ/Metal-Gate Gate-All-Around Nanowire MOSFET. IEEE Trans. Electron Devices 2016, 63, 3338–3341. [Google Scholar] [CrossRef]

- Dadgour, H.F.; Endo, K.; De, V.K.; Banerjee, K. Grain-orientation induced work function variation in nanoscale metal-gate transistors—Part II: Implications for process, device, and circuit design. IEEE Trans. Electron Devices 2010, 57, 2515–2525. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| Gate length (LG) | 70 nm |

| Channel width (W) | 70 nm |

| Equivalent oxide thickness (EOT) | 2 nm |

| Channel length (LCH) | 90 nm |

| Channel thickness (TB) | 10 nm |

| Drain underlap (LUD) | 20 nm |

| Source underlap (LUS) | 20 nm |

| MOSFET source/drain doping concentration | 1020 cm−3 |

| TFET p-type source doping concentration | 1020 cm−3 |

| TFET n-type drain doping concentration | 1018 cm−3 |

| Gate work function | 4.6 eV (60%) 4.4 eV (40%) |

| MOSFET | Planar TFET | DG TFET | EHBTFET | |

|---|---|---|---|---|

| Average Vth or Average Vturn-on | −55.0 mV | 325.1 mV | 283.0 mV | 680.4 mV |

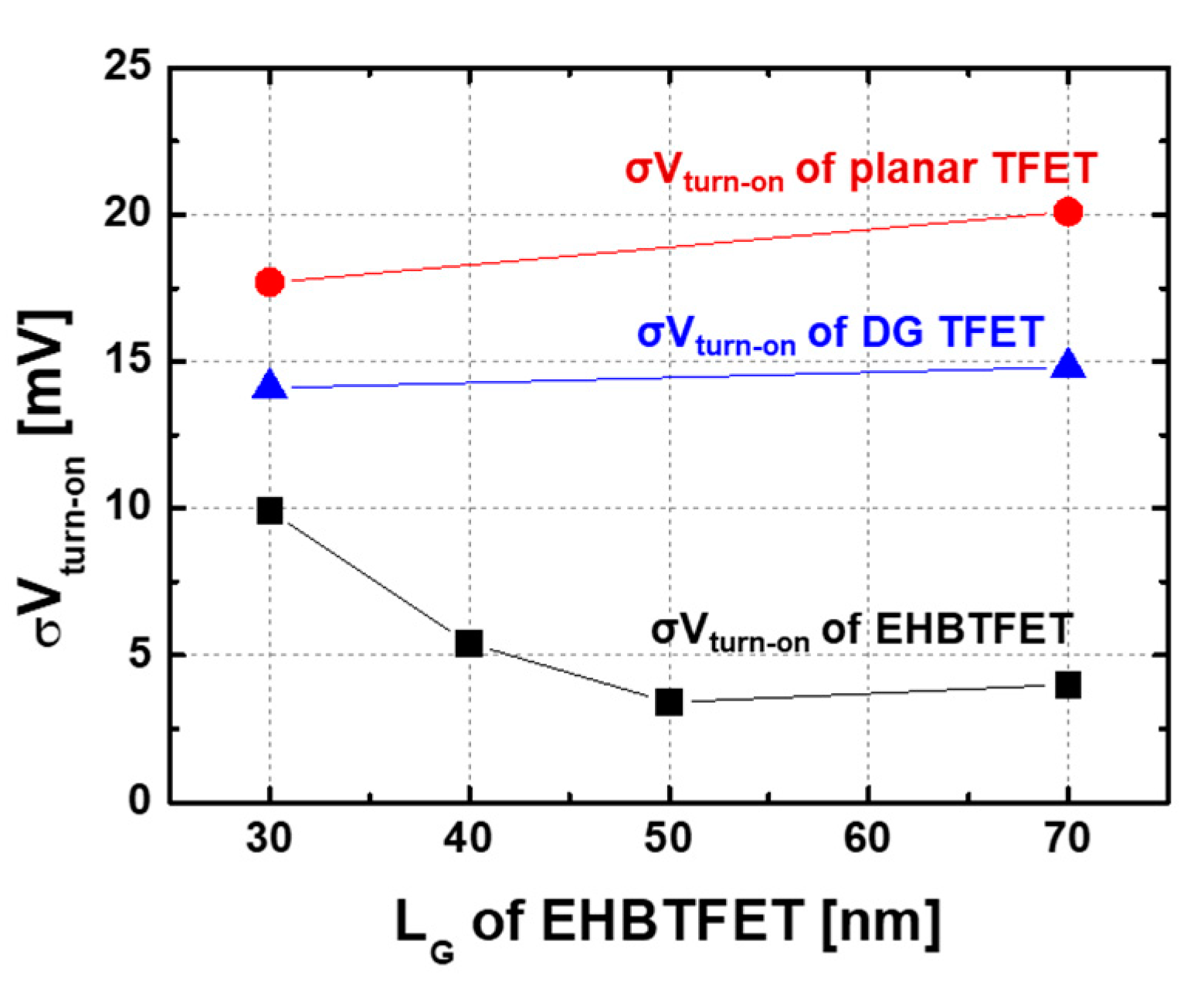

| σVth or σVturn-on | 14.0 mV | 20.1 mV | 14.8 mV | 4.0 mV |

| Average SS | 121.6 mV/decade | 64.3 mV/decade | 54.5 mV/decade | 4.6 mV/decade |

| σSS | 0.5 mV/decade | 5.6 mV/decade | 4.7 mV/decade | 1.2 mV/decade |

| Average Ion | 7.11 × 10−4 A/μm | 1.08 × 10−9 A/μm | 3.26 × 10−9 A/μm | 4.33 × 10−10 A/μm |

| σIon/Average Ion | 0.122 | 0.348 | 0.263 | 0.155 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, G.; Kim, J.H.; Kim, J.; Kim, S. Analysis of Work-Function Variation Effects in a Tunnel Field-Effect Transistor Depending on the Device Structure. Appl. Sci. 2020, 10, 5378. https://doi.org/10.3390/app10155378

Kim G, Kim JH, Kim J, Kim S. Analysis of Work-Function Variation Effects in a Tunnel Field-Effect Transistor Depending on the Device Structure. Applied Sciences. 2020; 10(15):5378. https://doi.org/10.3390/app10155378

Chicago/Turabian StyleKim, Garam, Jang Hyun Kim, Jaemin Kim, and Sangwan Kim. 2020. "Analysis of Work-Function Variation Effects in a Tunnel Field-Effect Transistor Depending on the Device Structure" Applied Sciences 10, no. 15: 5378. https://doi.org/10.3390/app10155378

APA StyleKim, G., Kim, J. H., Kim, J., & Kim, S. (2020). Analysis of Work-Function Variation Effects in a Tunnel Field-Effect Transistor Depending on the Device Structure. Applied Sciences, 10(15), 5378. https://doi.org/10.3390/app10155378