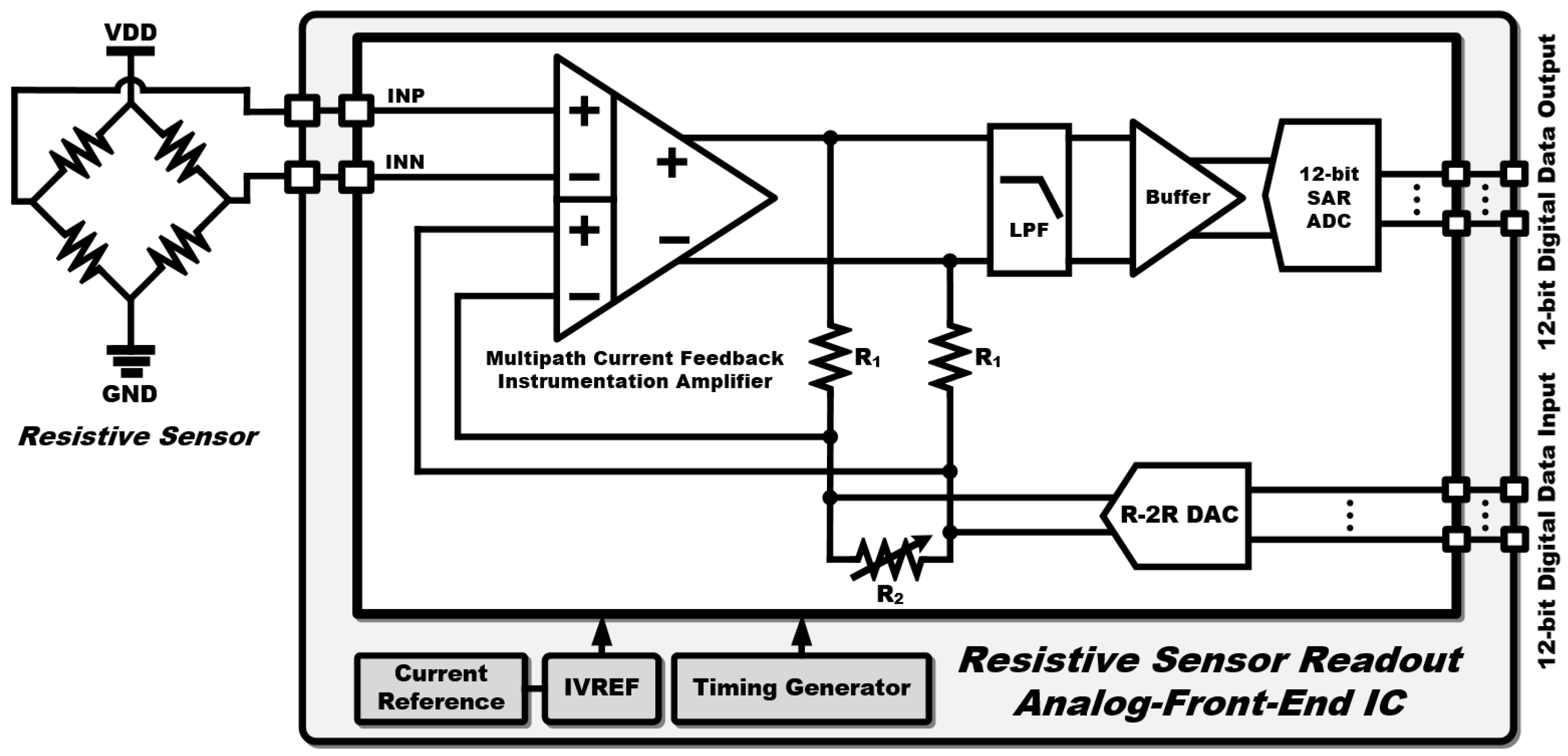

Fully Differential Chopper-Stabilized Multipath Current-Feedback Instrumentation Amplifier with R-2R DAC Offset Adjustment for Resistive Bridge Sensors

Abstract

1. Introduction

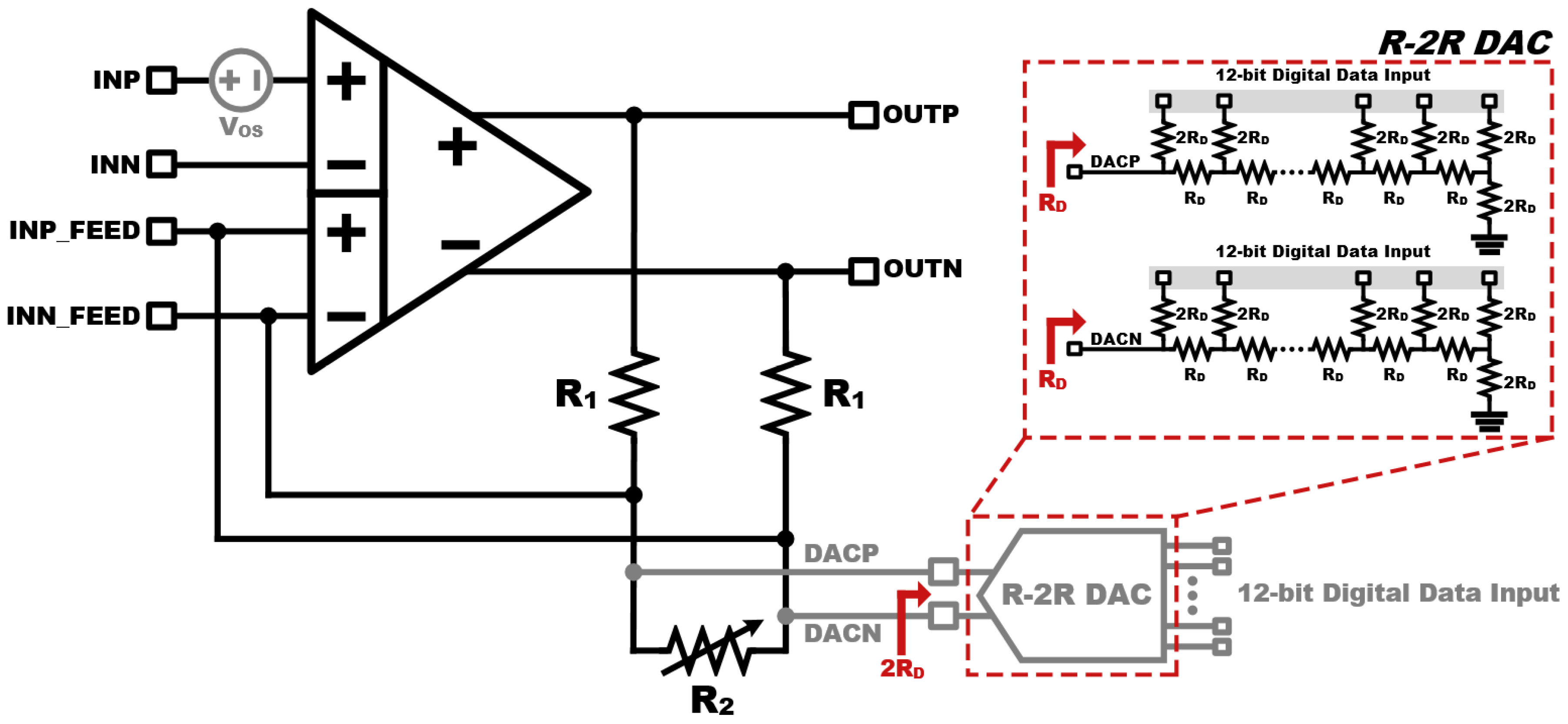

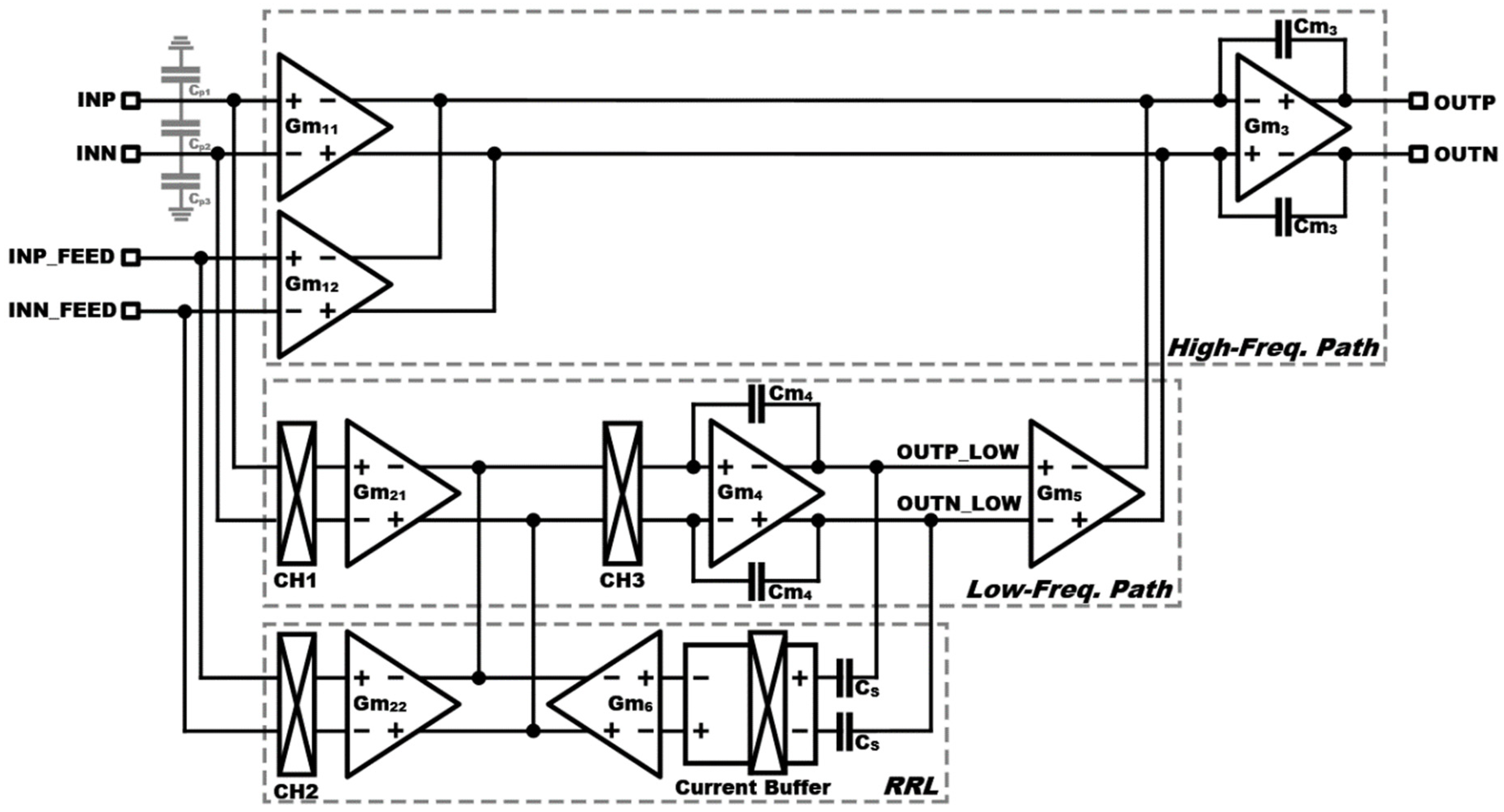

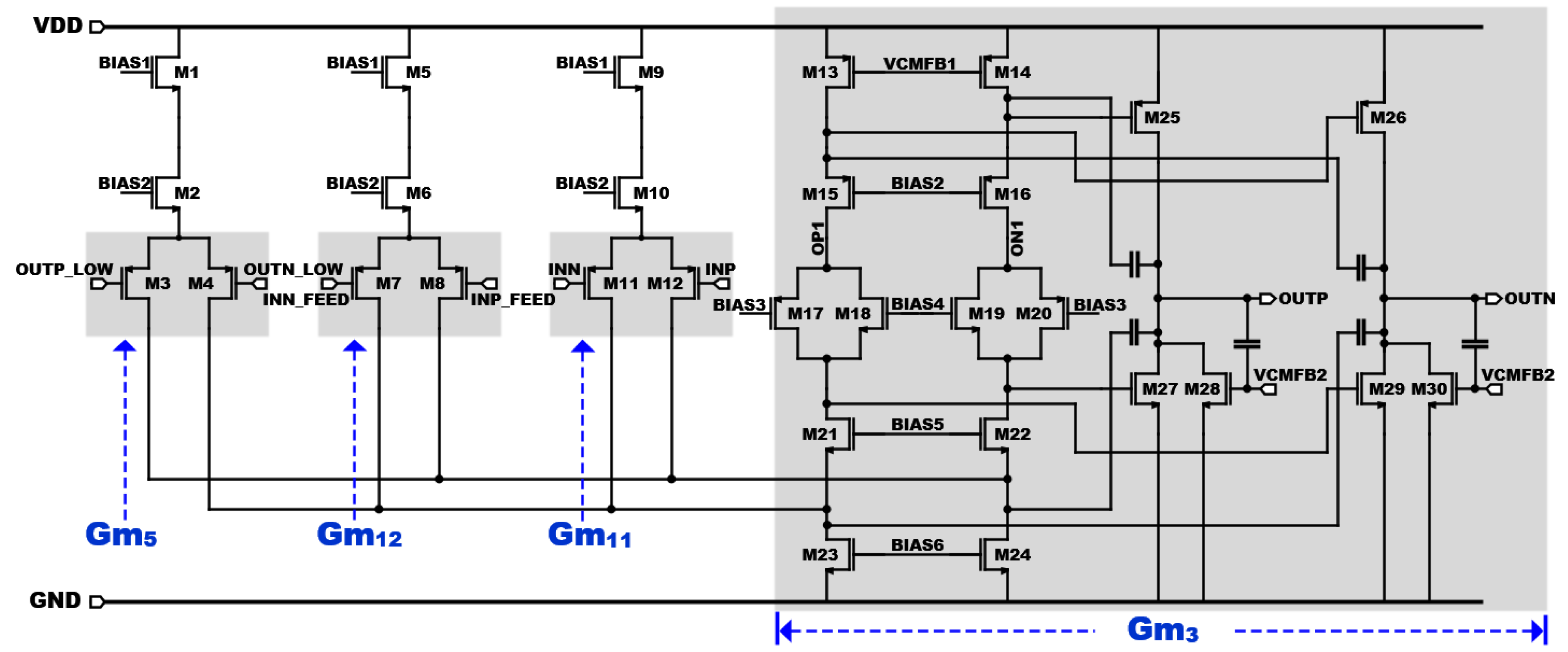

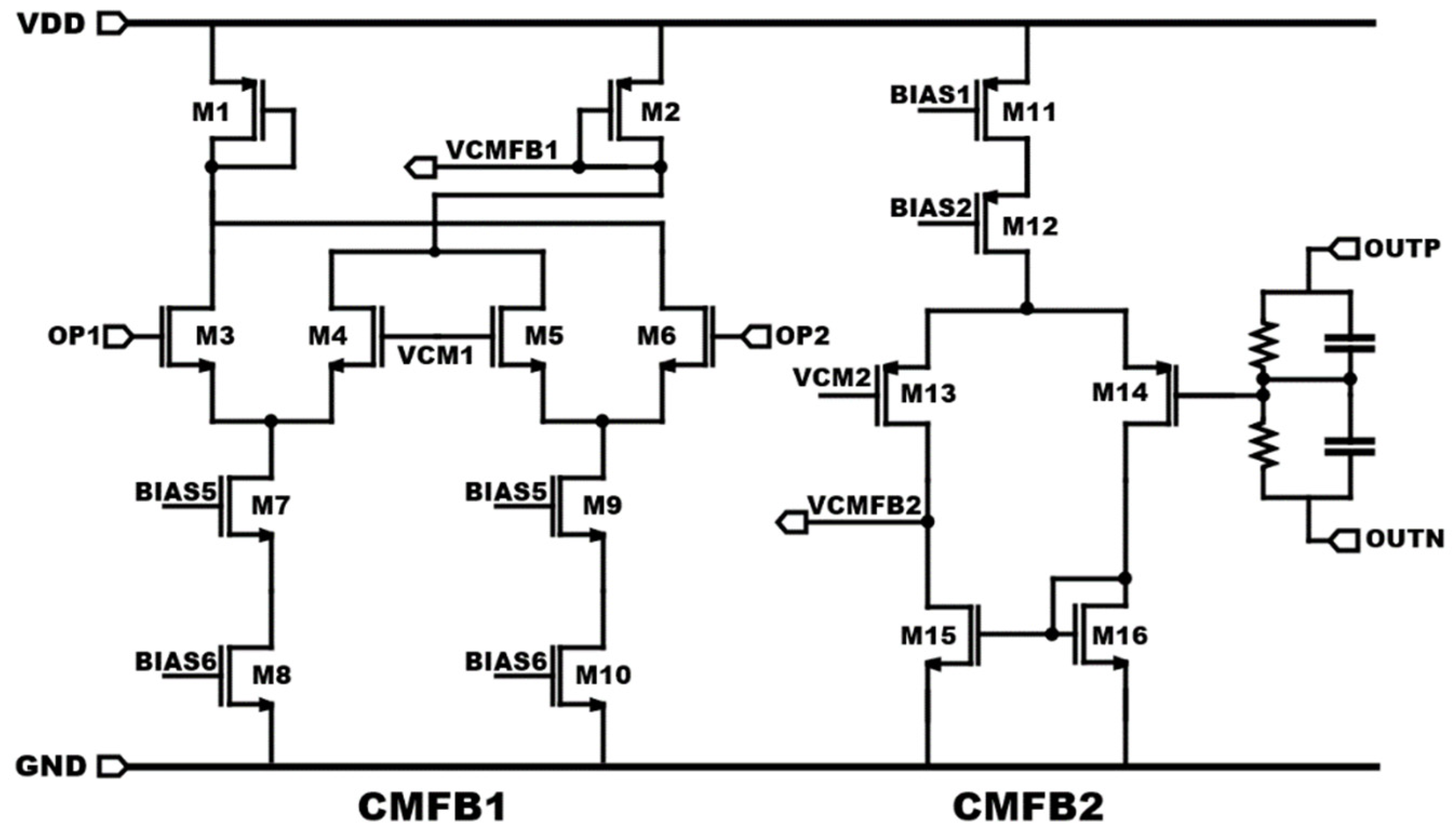

2. Circuit Implementation

2.1. Low-Frequency Path

2.2. High-Frequency Path

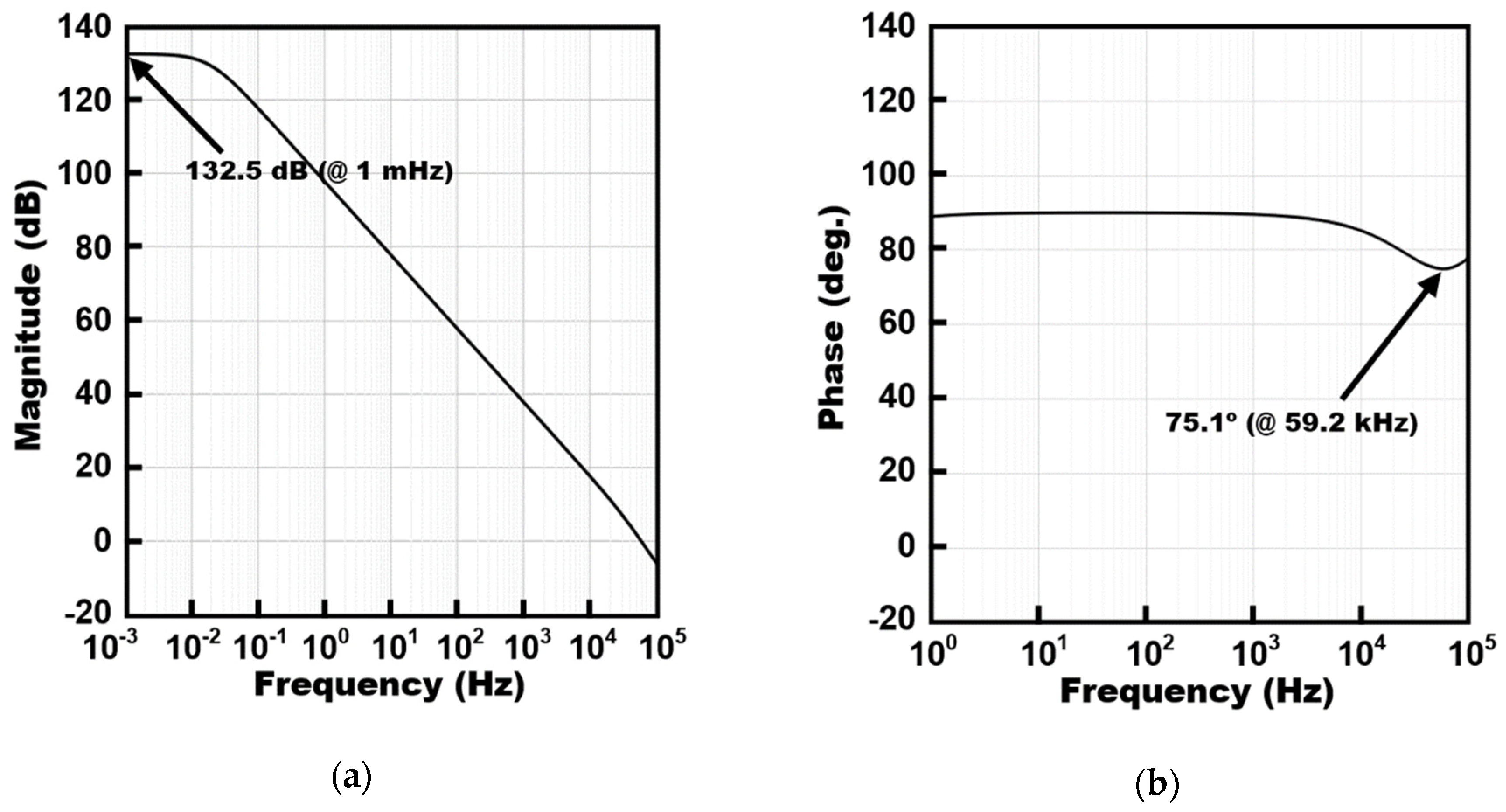

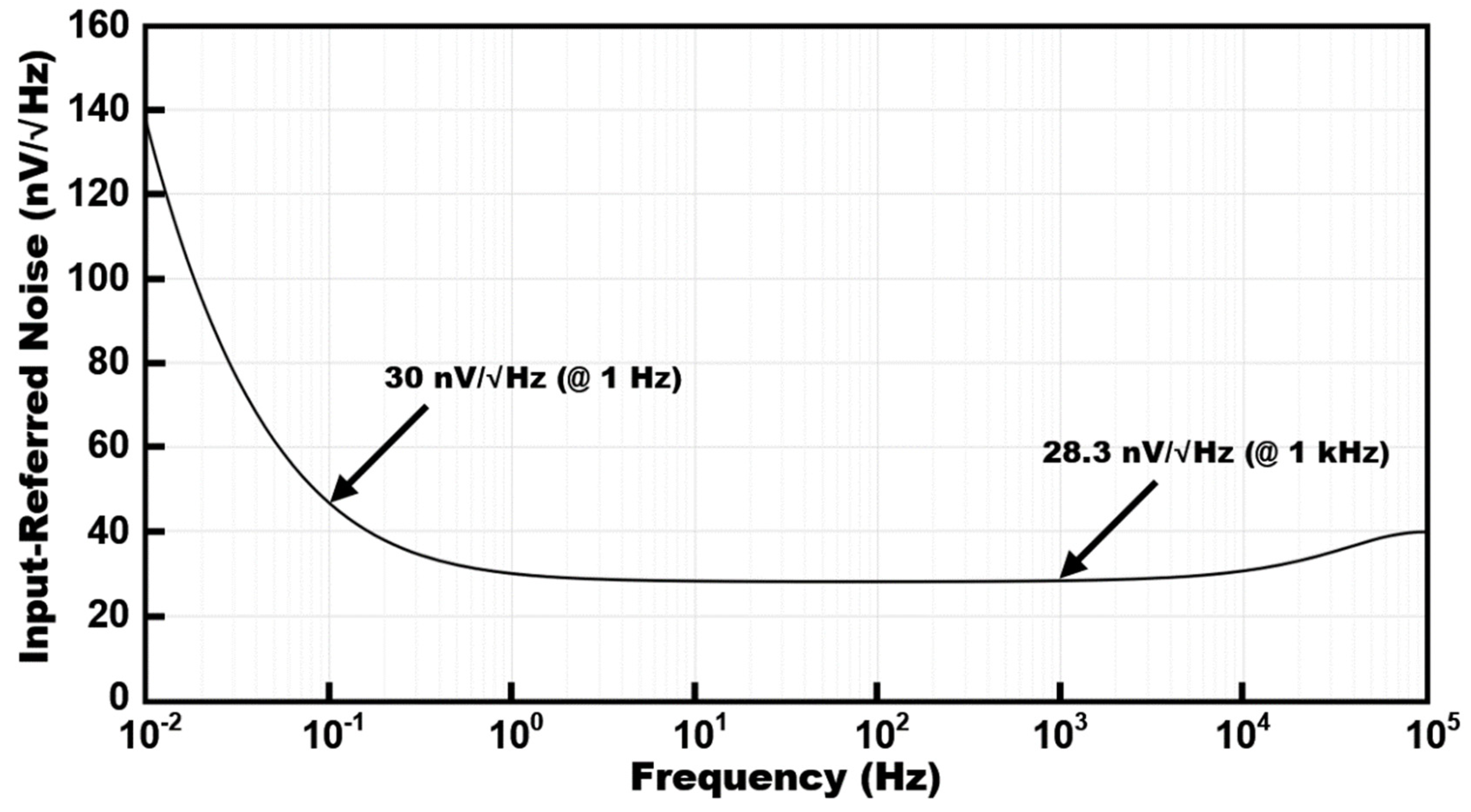

3. Simulation Results

4. Discussion and Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Vashi, S.; Ram, J.; Modi, J.; Verma, S.; Prakash, C. Internet of Things (IoT): A vision, architectural elements, and security issues. In Proceedings of the IoT in Social, Mobile, Analytics and Cloud (I-SMAC), Palladam, India, 10–11 February 2017; pp. 492–496. [Google Scholar] [CrossRef]

- Al-Fuqaha, A.; Guizani, M.; Mohammadi, M.; Aledhari, M.; Ayyash, M. Internet of Things: A Survey on Enabling Technologies, Protocols, and Applications. IEEE Commun. Surv. Tutor. 2015, 17, 2347–2376. [Google Scholar] [CrossRef]

- Hebrard, L.; Kammerer, J.B.; Braun, F. A chopper stabilized biasing circuit suitable for cascaded wheatstone-bridge-like sensors. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 1653–1665. [Google Scholar] [CrossRef]

- Barlian, A.A.; Park, W.; Mallon, J.R.; Rastegar, A.J.; Pruitt, B.L. Review: Semiconductor Piezoresistance for Microsystems. Proc. IEEE 2009, 97, 513–552. [Google Scholar] [CrossRef] [PubMed]

- Gowrishetty, U.; Walsh, K.; McNamara, S.; Roussel, T.; Aebersold, J. Single element 3-terminal pressure sensors: A new approach to pressure sensing and its comparison to the half bridge sensors. In Proceedings of the Solid-State Sensors, Actuators and Microsystems, Denver, CO, USA, 21–25 June 2009; pp. 1134–1137. [Google Scholar] [CrossRef]

- Gao, S.; Yi, Z.; Ye, Y.; Qin, M.; Huang, Q. Configuration of a Self-Heated Double Wheatstone Bridge for 2-D Wind Sensors. J. Microelectromech. Syst. 2019, 28, 125–130. [Google Scholar] [CrossRef]

- Wei, J.; Porta, M.; Tichem, M.; Staufer, U.; Sarro, P.M. Integrated Piezoresistive Force and Position Detection Sensors for Micro-Handling Applications. J. Microelectromech. Syst. 2013, 22, 1310–1326. [Google Scholar] [CrossRef]

- Fan, Q.; Huijsing, J.H.; Makinwa, K.A.A. A 21 nV/√Hz Chopper-Stabilized Multi-Path Current-Feedback Instrumentation Amplifier with 2 μV Offset. IEEE J. Solid State Circuits 2012, 47, 464–475. [Google Scholar] [CrossRef]

- Pertijs, M.A.P.; Kindt, W.J. A 140 dB-CMRR Current-Feedback Instrumentation Amplifier Employing Ping-Pong Auto-Zeroing and Chopping. IEEE J. Solid State Circuits 2010, 45, 2044–2056. [Google Scholar] [CrossRef]

- Oliaei, O. Noise analysis of correlated double sampling SC integrators with a hold capacitor. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 2003, 50, 1198–1202. [Google Scholar] [CrossRef]

- Lee, C.; Song, J. A Chopper Stabilized Current-Feedback Instrumentation Amplifier for EEG Acquisition Applications. IEEE Access 2019, 7, 11565–11569. [Google Scholar] [CrossRef]

- Enz, C.C.; Temes, G.C. Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization. Proc. IEEE 1996, 84, 1584–1614. [Google Scholar] [CrossRef]

- Wu, R.; Makinwa, K.A.A.; Huijsing, J.H. A Chopper Current-Feedback Instrumentation Amplifier With a 1 mHz 1/f Noise Corner and an AC-Coupled Ripple Reduction Loop. IEEE J. Solid State Circuits 2009, 44, 3232–3243. [Google Scholar] [CrossRef]

- Eschauzier, R.G.H.; Hogervorst, R.; Huijsing, J.H. A programmable 1.5 V CMOS class-AB operational amplifier with hybrid nested Miller compensation for 120 dB gain and 6 MHz UGF. IEEE J. Solid State Circuits 1994, 29, 1497–1504. [Google Scholar] [CrossRef]

- Wu, R.; Huijsing, J.H.; Makinwa, K.A.A. A Current-Feedback Instrumentation Amplifier with a Gain Error Reduction Loop and 0.06% Untrimmed Gain Error. IEEE J. Solid State Circuits 2011, 46, 2794–2806. [Google Scholar] [CrossRef]

- Witte, J.F.; Huijsing, J.H.; Makinwa, K.A.A. A chopper and auto-zero offset-stabilized CMOS instrumentation amplifier. In Proceedings of the VLSI Circuits, Kyoto, Japan, 16–18 June 2009; pp. 210–211. [Google Scholar]

- Butti, F.; Piotto, M.; Bruschi, P. A Chopper Instrumentation Amplifier with Input Resistance Boosting by Means of Synchronous Dynamic Element Matching. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 753–764. [Google Scholar] [CrossRef]

| This Work | [9] | [15] | [16] | [17] | |

|---|---|---|---|---|---|

| Process (µm) | 0.18 | 0.5 | 0.7 | 0.7 | 0.32 |

| Supply (V) | 3.3 | 3–5.5 | 5 | 5.5 | 3.3 |

| Current (µA) | 169 | 1700 | 290 | 325 | 170 |

| DC gain (dB) | 132.5 | 1000 | - | - | 201.2 |

| CMRR (dB) | 162 | 142 | 127 | 130 | >120 |

| PSRR+ (dB) | 112 | 138 | 130 | 114 | 115 |

| PSRR− (dB) | 110 | - | - | - | - |

| BW (kHz) | 59.2 | 800 | 800 | 640 | 40 |

| Input-referred noise (nV/√Hz) | 28.3 | 27 | 17 | 42 | 18 |

| NEF | 14.2 | 43 | 11.2 | 29.2 | 10.6 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kwon, Y.; Kim, H.; Kim, J.; Han, K.; You, D.; Heo, H.; Cho, D.-i.“.; Ko, H. Fully Differential Chopper-Stabilized Multipath Current-Feedback Instrumentation Amplifier with R-2R DAC Offset Adjustment for Resistive Bridge Sensors. Appl. Sci. 2020, 10, 63. https://doi.org/10.3390/app10010063

Kwon Y, Kim H, Kim J, Han K, You D, Heo H, Cho D-i“, Ko H. Fully Differential Chopper-Stabilized Multipath Current-Feedback Instrumentation Amplifier with R-2R DAC Offset Adjustment for Resistive Bridge Sensors. Applied Sciences. 2020; 10(1):63. https://doi.org/10.3390/app10010063

Chicago/Turabian StyleKwon, Yongsu, Hyungseup Kim, Jaesung Kim, Kwonsang Han, Donggeun You, Hyunwoo Heo, Dong-il “Dan” Cho, and Hyoungho Ko. 2020. "Fully Differential Chopper-Stabilized Multipath Current-Feedback Instrumentation Amplifier with R-2R DAC Offset Adjustment for Resistive Bridge Sensors" Applied Sciences 10, no. 1: 63. https://doi.org/10.3390/app10010063

APA StyleKwon, Y., Kim, H., Kim, J., Han, K., You, D., Heo, H., Cho, D.-i. “., & Ko, H. (2020). Fully Differential Chopper-Stabilized Multipath Current-Feedback Instrumentation Amplifier with R-2R DAC Offset Adjustment for Resistive Bridge Sensors. Applied Sciences, 10(1), 63. https://doi.org/10.3390/app10010063