Low-Noise Multimodal Reconfigurable Sensor Readout Circuit for Voltage/Current/Resistive/Capacitive Microsensors

Abstract

:1. Introduction

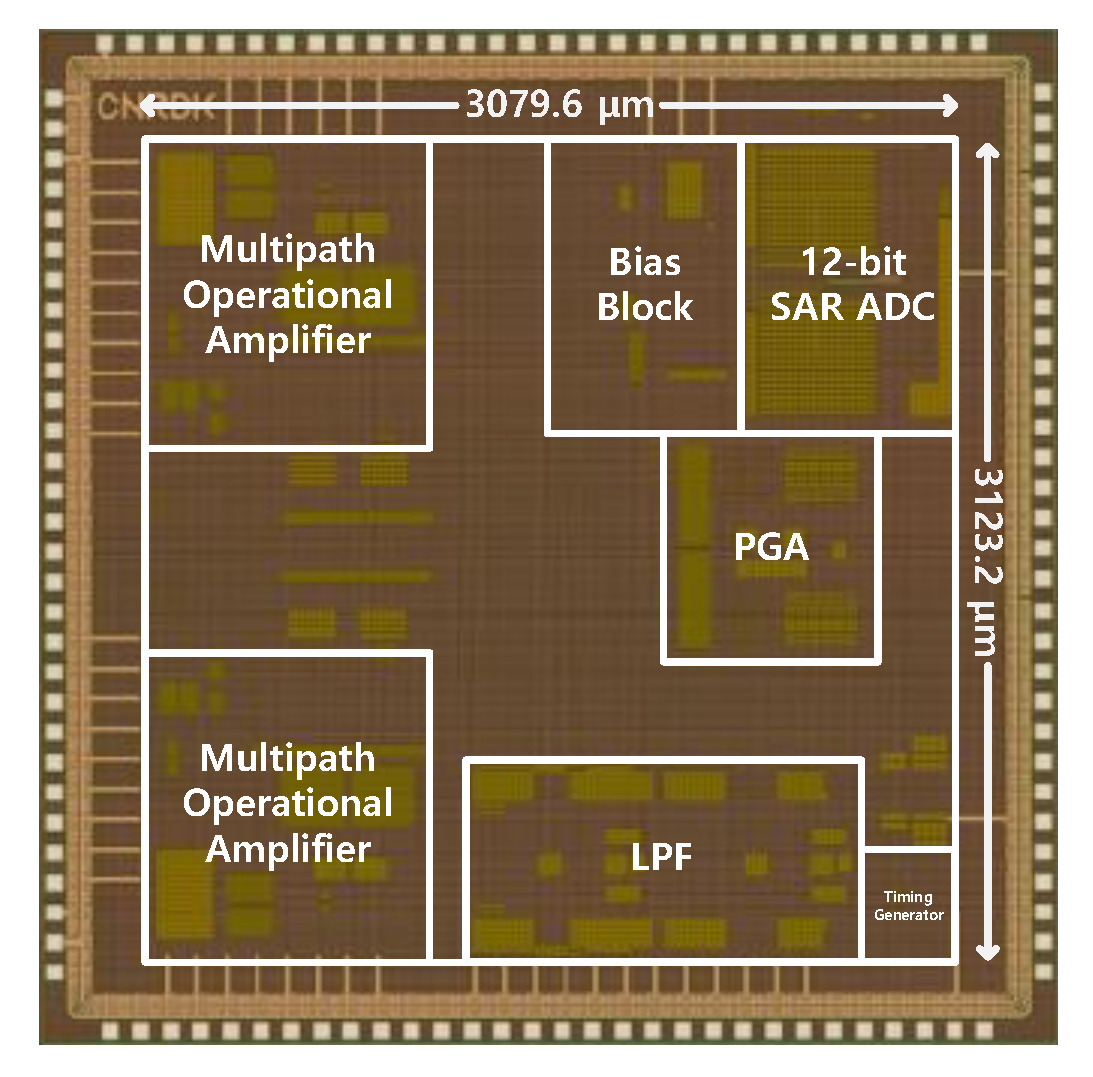

2. Proposed Multimodal Reconfigurable Sensor Readout Circuit

2.1. Top-Level Architecture

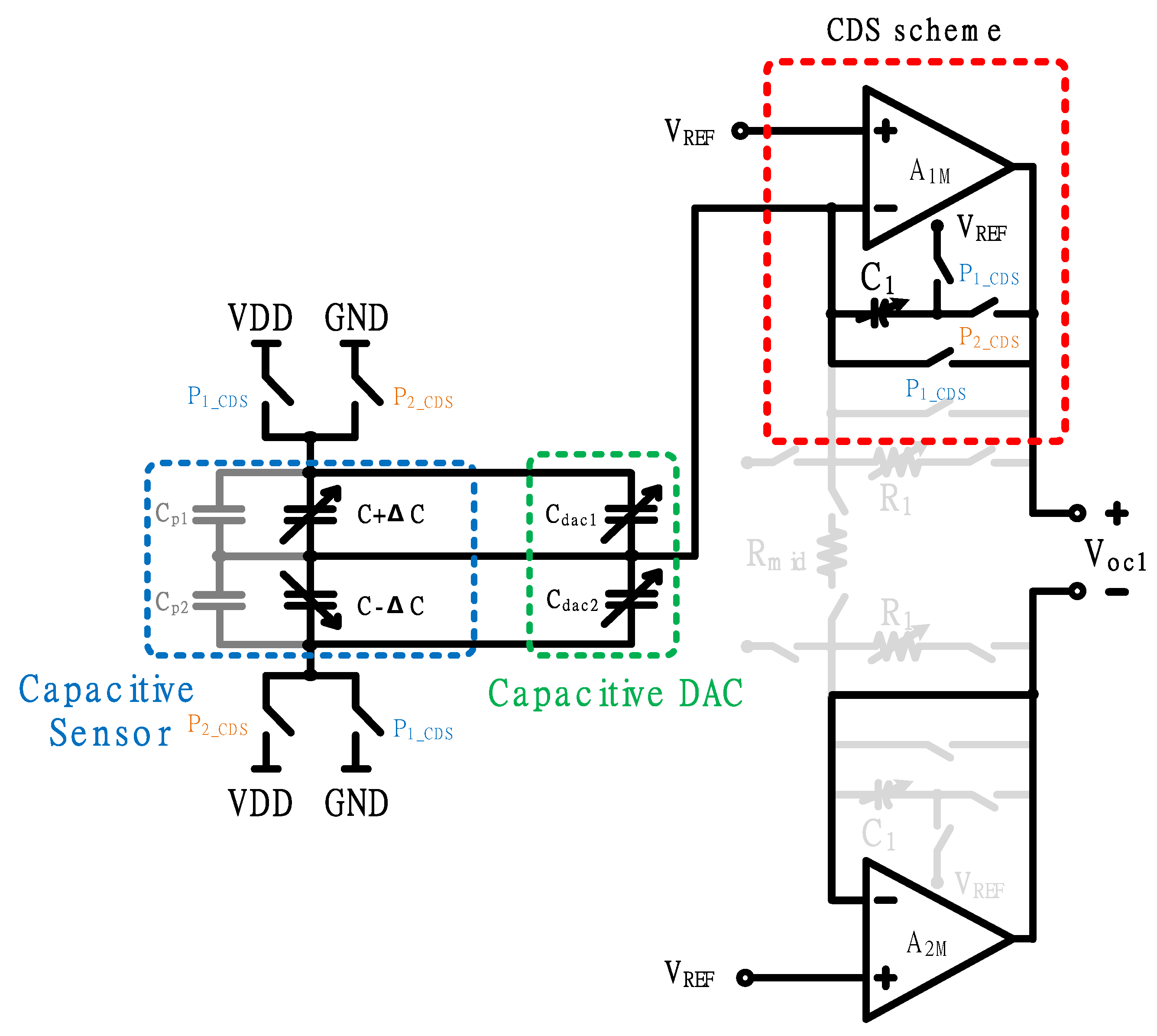

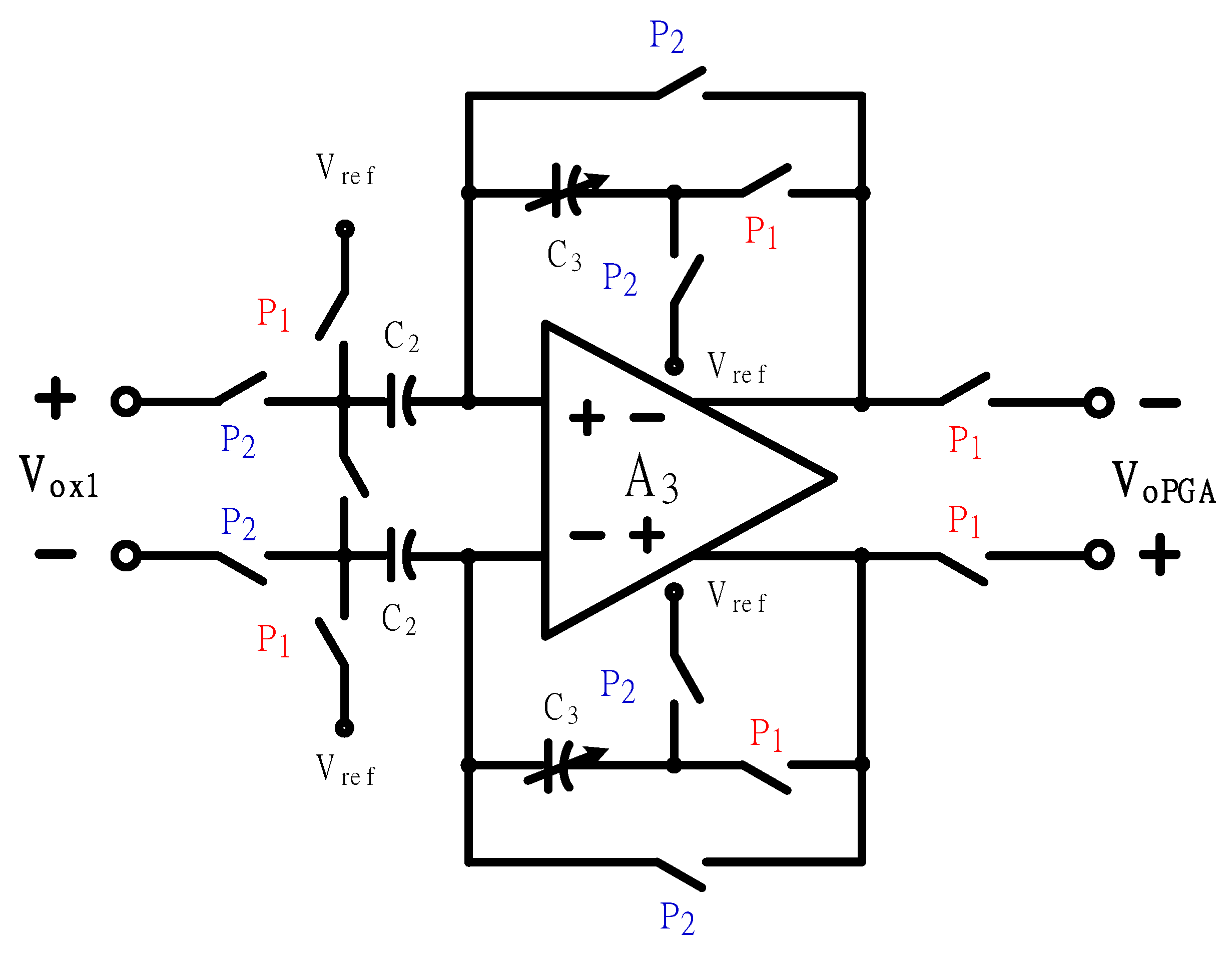

2.2. Reconfigurable Structure

2.3. Detailed Description of the Amplifiers

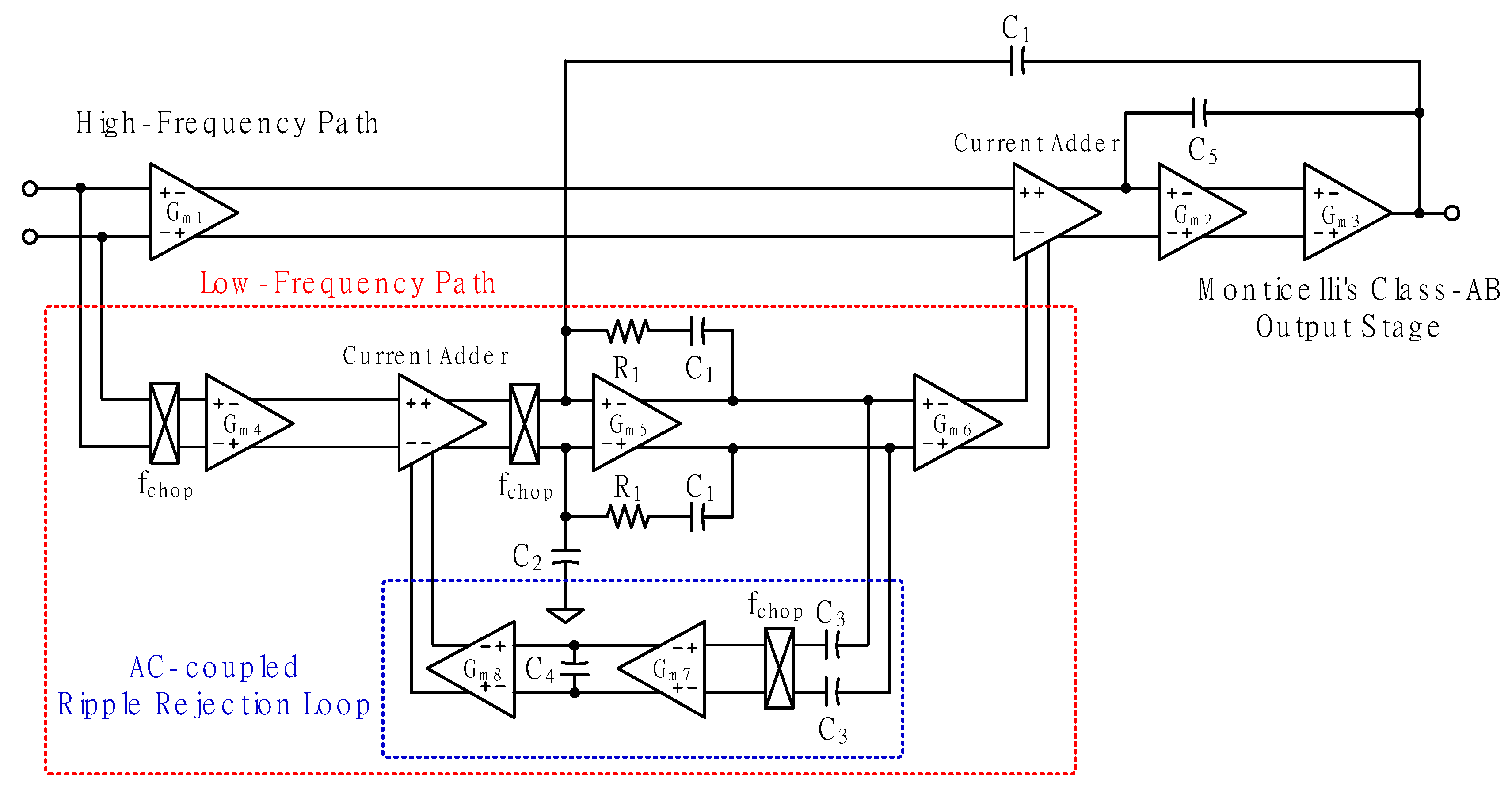

2.3.1. Chopper-Stabilized, Multi-Path Operational Amplifier with an AC-Coupled RRL

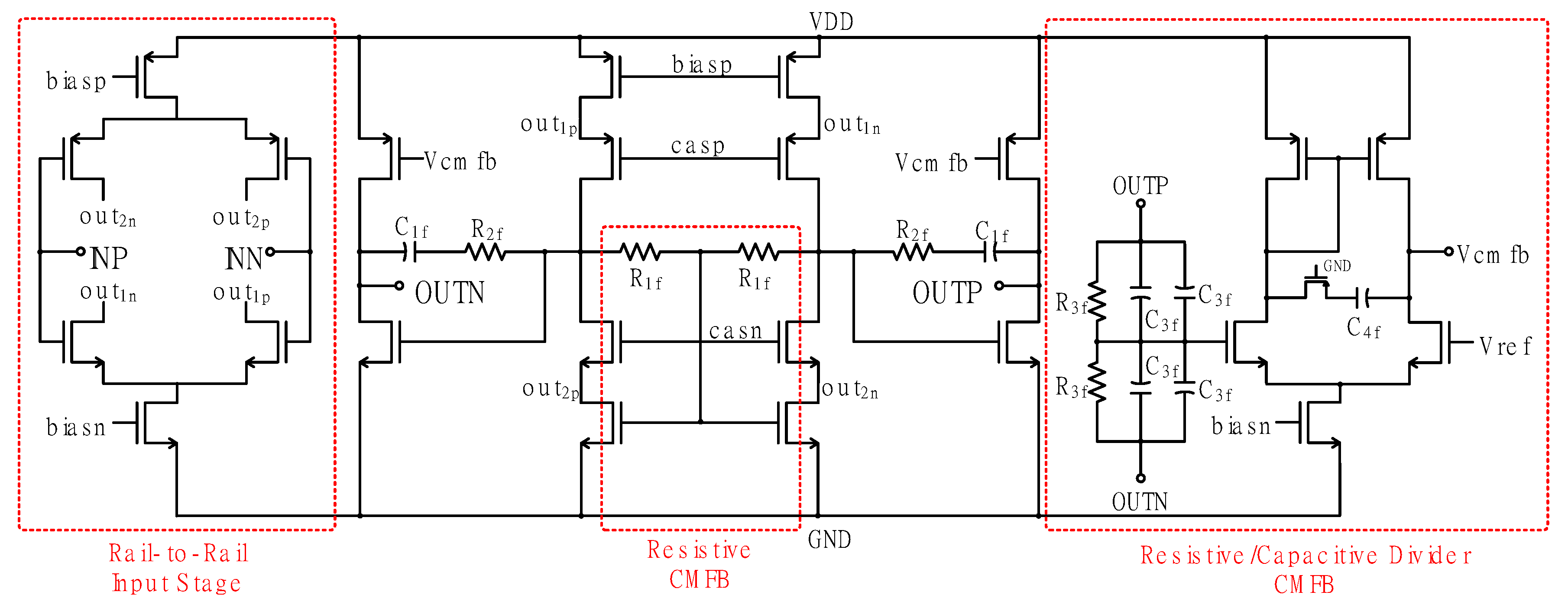

2.3.2. Fully Differential Amplifier

3. Measurement Results

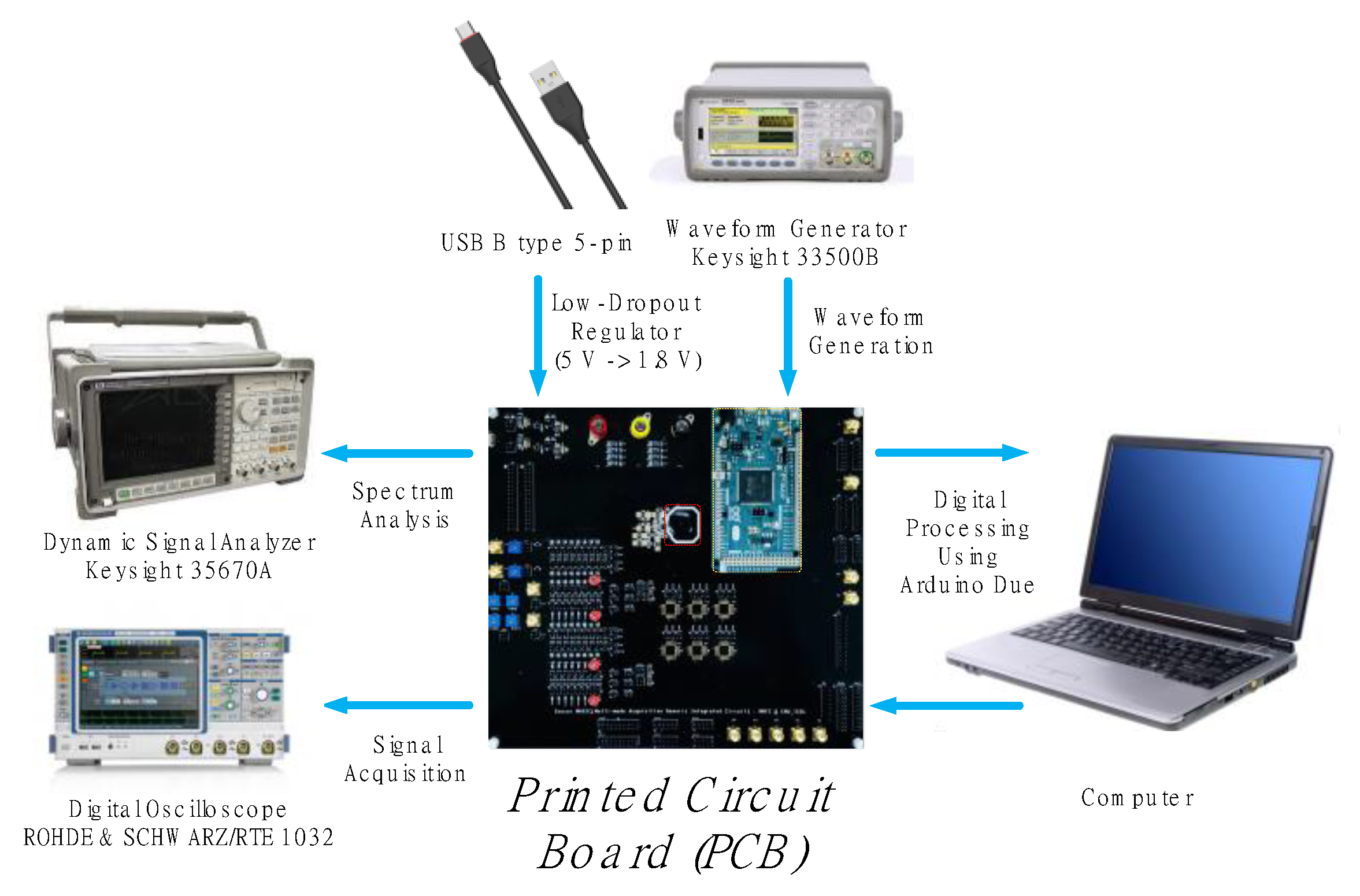

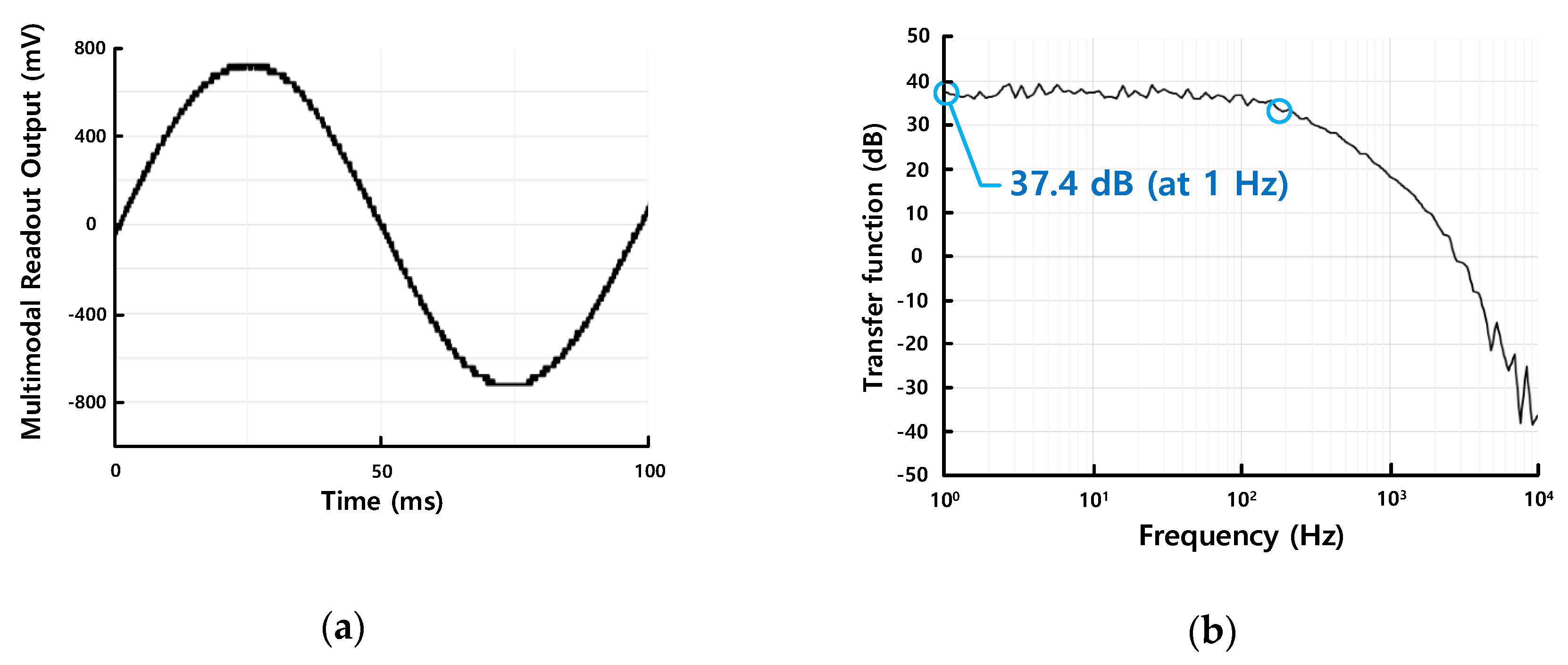

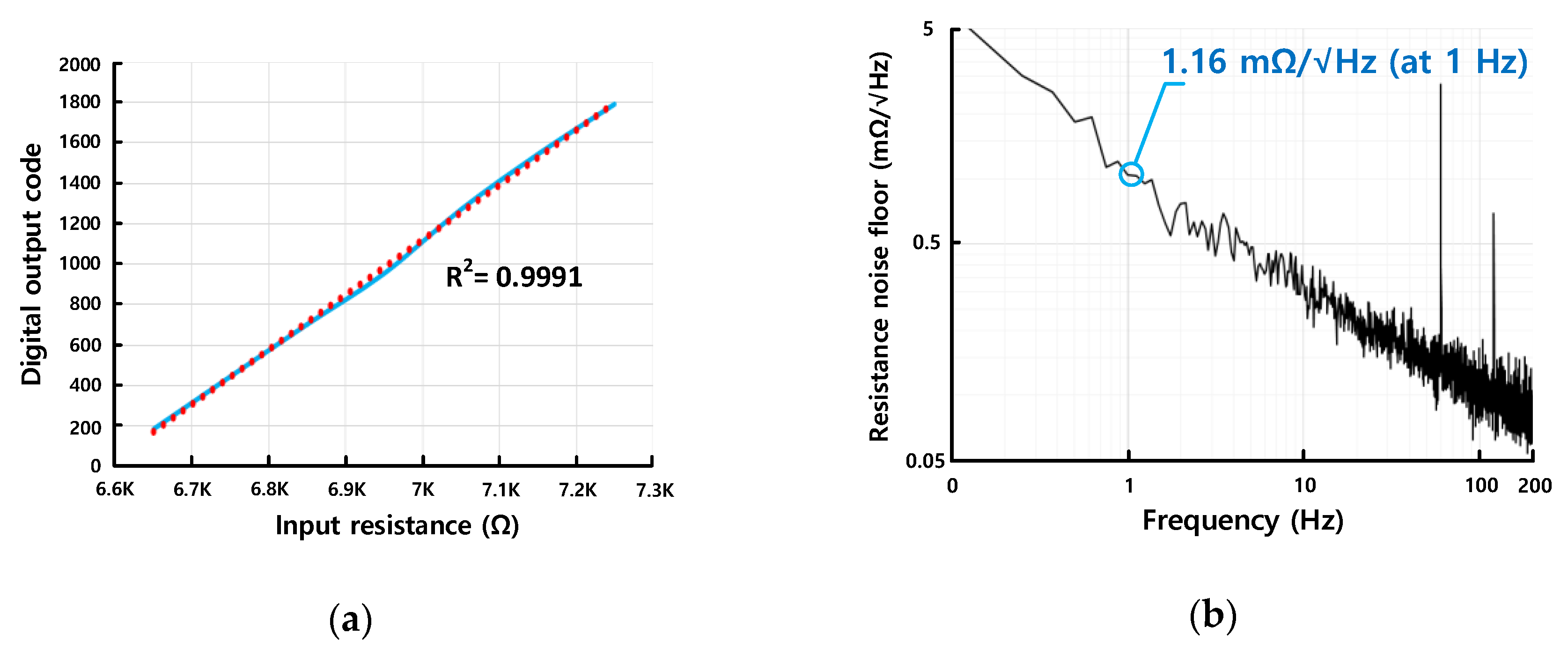

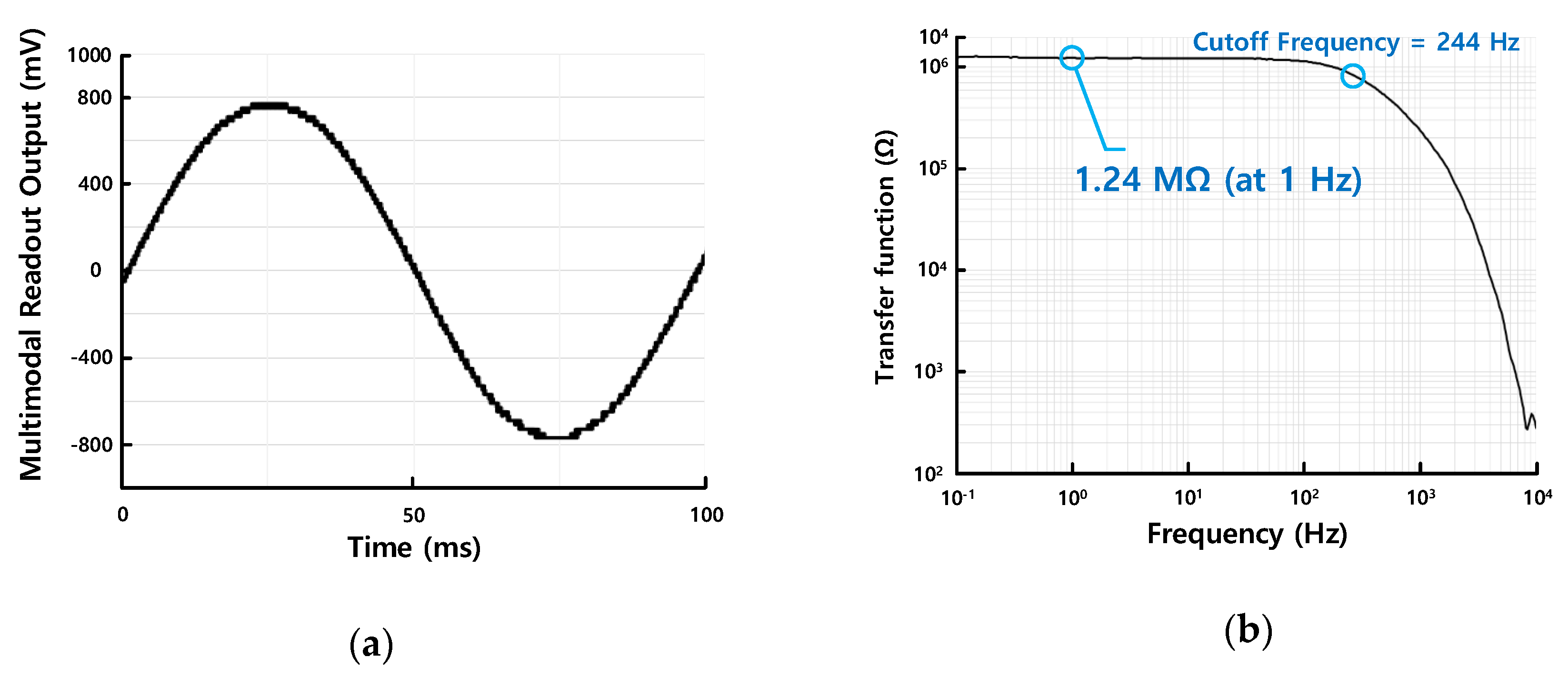

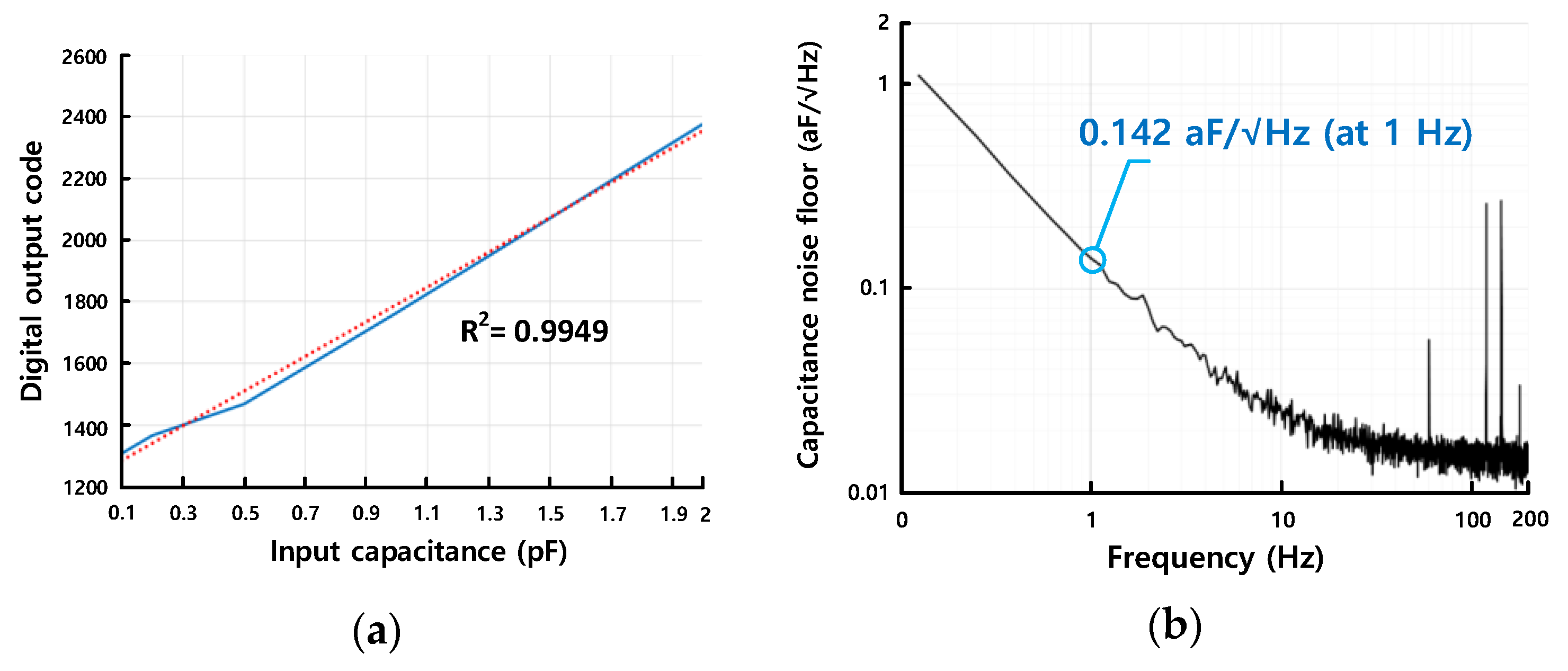

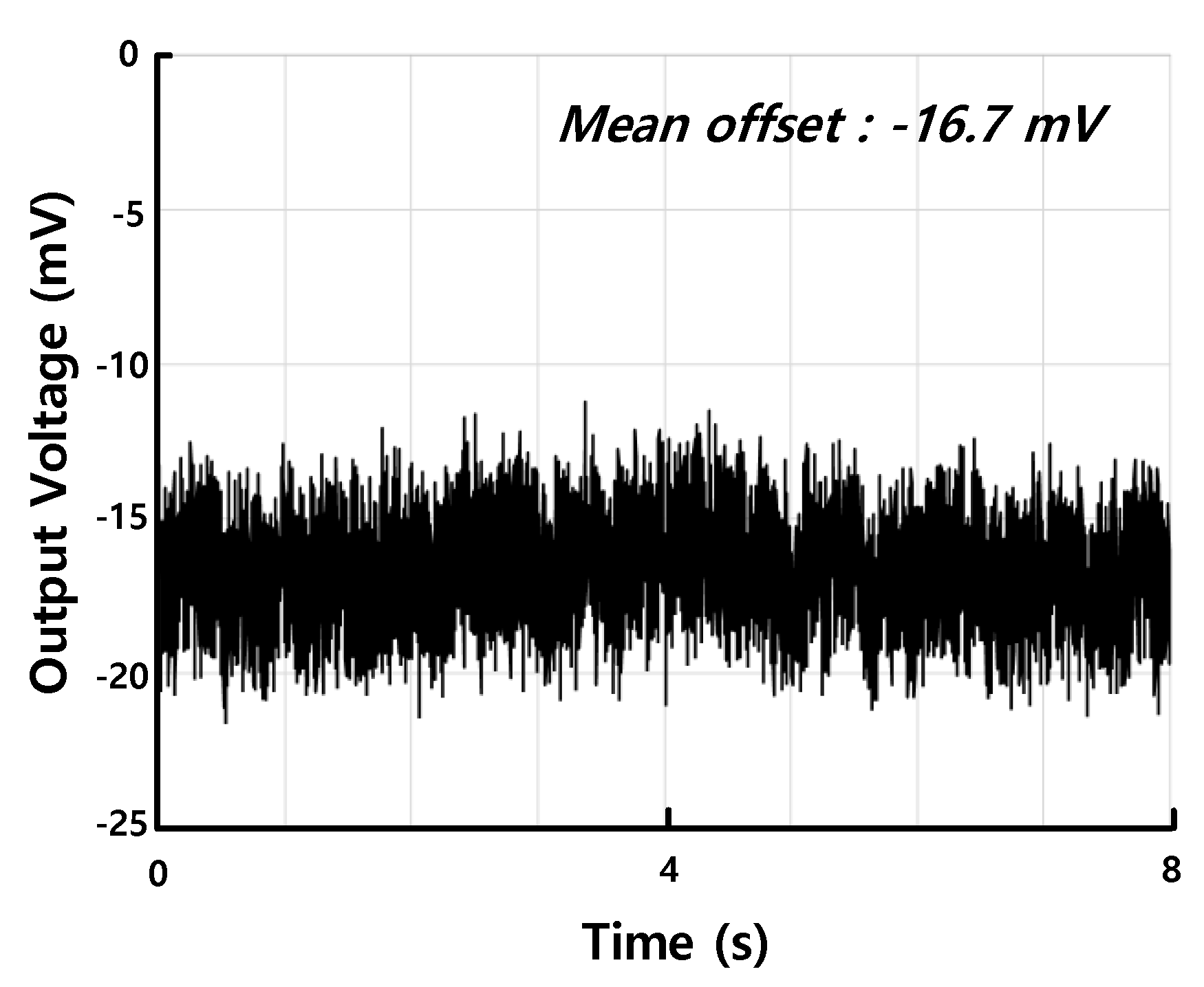

3.1. Measurement Results Using the Implemented Sensor on a Printed Circuit Board (PCB)

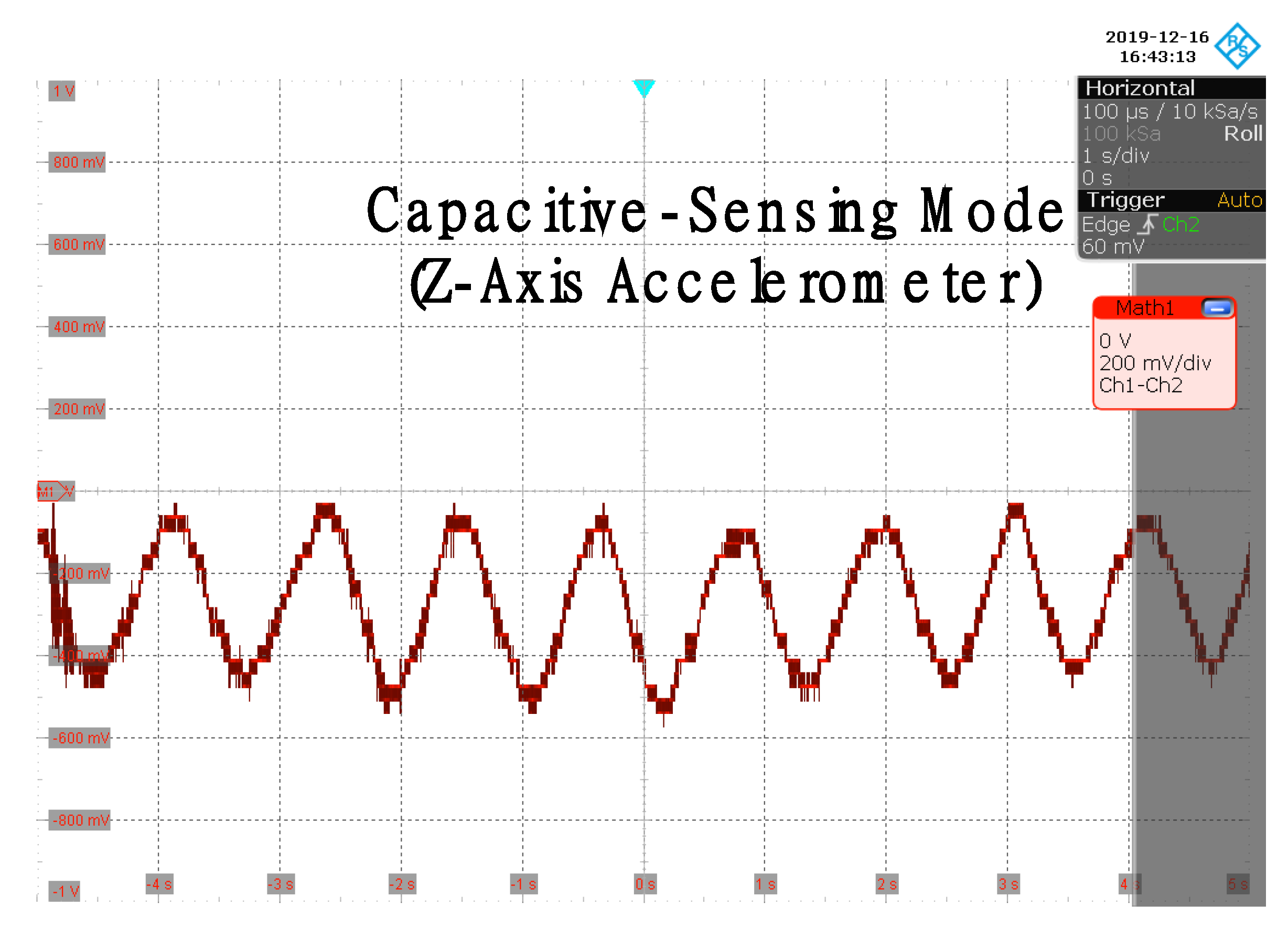

3.2. Measurement Results Using a Real Application

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Chen, S.; Xu, H.; Liu, D.; Hu, B.; Wang, H. A Vision of IoT: Applications, Challenges, and Opportunities with China Perspective. IEEE Internet Things J. 2014, 1, 349–359. [Google Scholar] [CrossRef]

- Alhoshany, A.; Omran, H.; Salama, K.N. A 45.8 fJ/Step, energy-efficient, differential SAR capacitance-to-digital converter for capacitive pressure sensing. Sens. Actuators Phys. 2016, 245, 10–18. [Google Scholar] [CrossRef]

- Gómez-Ramírez, E.; Maeda-Nunez, L.A.; Álvarez-Simón, L.C.; Flores-García, F.G. A Highly Robust Interface Circuit for Resistive Sensors. Electronics 2019, 8, 263. [Google Scholar] [CrossRef] [Green Version]

- Song, H.; Park, Y.; Kim, H.; Cho, D.D.; Ko, H. Fully integrated low-noise readout circuit with automatic offset cancellation loop for capacitive microsensors. Sensors 2015, 15, 26009–26017. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Lee, B.; Kim, H.; Kim, J.; Han, K.; Shin, S.; Kim, G.; Sul, W.S.; Lee, B.J.; Lee, S.; Ko, H. Low-noise 16-bit First-order Delta-sigma Capacitance-to-digital Converter for Capacitive Humidity Sensor. Sens. Mater. 2019, 31, 1523–1533. [Google Scholar] [CrossRef]

- Mun, Y.; Kim, H.; Ko, Y.; Park, Y.; Koo, K.; Cho, D.D.; Ko, H. Capacitive analog front-end circuit with dual-mode automatic parasitic cancellation loop. Microsyst. Technol. 2017, 23, 515–523. [Google Scholar] [CrossRef]

- Omran, H.; Arsalan, M.; Salama, K.N. An integrated energy-efficient capacitive sensor digital interface circuit. Sens. Actuators Phys. 2014, 216, 43–51. [Google Scholar] [CrossRef]

- Shah, J.; Mishra, B. IoT enabled Environmental Monitoring System for Smart Cities. In Proceedings of the 2016 Internet of Things and Applications (IOTA), Pune, India, 22–24 January 2016. [Google Scholar]

- Park, K.; Kim, S.; Eom, W.; Kim, J. A Reconfigurable Readout Integrated Circuit for Heterogeneous Display-Based Multi-Sensor Systems. Sensors 2017, 17, 759. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Helleputte, N.K.; Konijnenburg, M.K.; Kim, H.; Pettine, J.; Jee, D.; Breeschoten, A.; Morgado, A.; Torfs, T.; Groot, D.H.; Hoof, C.V.; et al. 18.3 A multi-parameter signal-acquisition SoC for connected personal health applications. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014. [Google Scholar]

- Musa, A.; Minotani, T.; Matsunaga, K.; Kondo, T.; Morimura, H. An 8-Mode Reconfigurable Sensor-Independent Readout Circuit for Trillion Sensors Era. In Proceedings of the 2015 IEEE Tenth International Conference on Intelligent Sensors, Sensor Networks and Information Processing (ISSNIP), Singapore, 7–9 April 2015. [Google Scholar]

- Huang, Y.; Tzeng, T.; Lin, T.; Huang, C.; Yen, P.; Kuo, P.; Lin, C.; Lu, S. A Self-Powered CMOS Reconfigurable Multi-Sensor SoC for Biomedical Applications. IEEE J. Solid State Circuit 2014, 49, 851–866. [Google Scholar] [CrossRef]

- Ghoreishzadeh, S.; Boero, C.; Pullini, A.; Baj-Rossi, C.; Carrara, S.; Micheli, G. Sub-mW Reconfigurable Interface IC for Electrochemical Sensing. In Proceedings of the 2014 IEEE Biomedical Circuits and Systems Conference (BioCAS) Proceedings, Lausanne, Switzerland, 22–24 October 2014. [Google Scholar]

- Jun, J.; Rhee, C.; Kim, M.; Kang, J.; Kim, S. A 21.8 b sub-100μHz 1/f corner 2.4 μV-offset programmable-gain read-out IC for bridge measurement systems. In Proceedings of the 2018 IEEE International Solid—State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 February 2018. [Google Scholar]

- Belloni, M.; Bonizzoni, E.; Fornasari, A.; Maloberti, F. A Micropower Chopper—CDS Operational Amplifier. IEEE J. Solid State Circuits 2010, 45, 2521–2529. [Google Scholar] [CrossRef]

- Lee, B.; Ko, Y.; Kim, H.; Mun, Y.; Huh, S.; Song, D.; Roh, Y.; Ko, H. Low-noise Reconfigurable 12- to 16-bit Delta-Sigma Capacitance-to-digital Converter with Chopper Stabilization Technique. Sens. Mater. 2018, 30, 1671–1679. [Google Scholar] [CrossRef]

- Ko, H.; Kim, H.; Lee, B.; Kim, J.; Cho, D.D.; Han, K. Low-noise Analog Front-end with Chopper-stabilized Multipath Current-feedback Instrumentation Amplifier for Resistive Sensors. Sens. Mater. 2019, 30, 1697–1706. [Google Scholar] [CrossRef]

- Enz, C.C.; Temes, G.C. Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization. Proc. IEEE 1996, 84, 1584–1614. [Google Scholar] [CrossRef] [Green Version]

- Mallya, S.; Nevin, J.H. Design procedures for a fully differential folded-cascode CMOS operational amplifier. IEEE J. Solid State Circuits 1989, 24, 1737–1740. [Google Scholar] [CrossRef]

- Ong, G.T.; Chan, P.K. A Power-Aware Chopper-Stabilized Instrumentation Amplifier for Resistive Wheatstone Brdige Sensors. IEEE Trans. Instrum. Meas. 2017, 63, 2253–2264. [Google Scholar] [CrossRef]

- Zhao, M.; Lu, W.; Chen, Z.; Zhang, T.; Wu, F.; Zhang, Y.; Liu, D. A Low-Noise Switched-Capacitor Interface for a Capacitive Micro-Accelerometer. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015. [Google Scholar]

| Overall Performance of the Proposed Multimodal Readout Circuit | ||||||

|---|---|---|---|---|---|---|

| Technology | 1P6M 0.18-µm CMOS Process | |||||

| Supply Voltage | 1.8 V | |||||

| Multimodal Readout Circuit | Bias Block | |||||

| Signal type | Voltage | Resistance | Current | Capacitance | Power | 483.7 µW (sim) |

| Low-Pass Filter | ||||||

| Input range | 70 mV (max) | 0.4–400 Ω | 1.65 µA (max) | ±2 pF | Bandwidth | 1 kHz (sim) |

| Total power | 2.784 mW | 2.552 mW | 2.8 mW | Power | 487.8 µW (sim) | |

| Input noise (1–200 Hz) | 5.25 µVrms | 2.9 mΩrms | 742 pArms | 0.313 aFrms | PGA | |

| Pchop | 1 MHz (chopping frequency) | Gain | 13.9–44 dB | |||

| Pcds | 125 kHz (CDS frequency) | Power | 608 µW (sim) | |||

| Multi-Path Operational Amplifier | Clock Generator | |||||

| Power | 10.09 µW (sim) | Power | 138 µW (sim) | |||

| UGBW | 4.81 MHz | |||||

| Open loop gain | 98 dB | |||||

| 12-bit SAR ADC | ||||||

| Power | 802.98 µW (sim) | |||||

| Sampling frequency | 1 MHz | |||||

| Flexible Bend Sensor | Capacitive Z-Axis Accelerometer | ||

|---|---|---|---|

| Signal Type | R | Signal Type | C |

| Flat resistance | 10 kΩ | Torque/g | 2.03 × 10−10 |

| Resistance tolerance | ±30% | Nominal capacitance | 5.409 pF |

| Bend resistance range | 60–110 kΩ | Δ C/g | 0.125 pF/g |

| Resolution | 0.5 mg | ||

| Δ degree/g | 3.65 × 10−4 μm/g | ||

| Parameter | This Work | Ref. [20] | Ref. [21] | Ref. [10] | Ref. [12] |

|---|---|---|---|---|---|

| Supply (V) | 1.8 | 2.7 | 5 | 1.2 | 1.8 |

| Technology (µm) | 0.18 | 0.18 | 0.35 | 0.18 | 0.35 |

| Power consumption (mW) | 2.552 | 0.02765 | 189.3 | 0.058 | 0.942 |

| Area (mm2) | 9.61 | N/A | 12.5 | N/A | 11.25 |

| Signal type | V/I/R/C | R | C | V/R | V/I/R/C |

| Noise cancellation | Chopping, CDS | Chopping | CDS | Chopping | Chopping |

| Input noise | 5.25 µVrms | 3.76 µVrms | N/A | 0.6 µVrms | 0.769 µVrms |

| Resistance noise floor | 2.9 mΩrms | N/A | N/A | 8.6 mΩ/√Hz | N/A |

| Input current noise | 742 pArms | N/A | N/A | N/A | N/A |

| Capacitance noise floor | 0.313 aFrms | N/A | 0.41 aFrms | N/A | N/A |

| Input range | V: 70 mVpp R: 0.4–400 Ω I: 1.65 µA C: ±2 pF | V: 17.6 mV | C: ±2.9 pF | V: 30 mVpp R: N/A | C: 10 pF |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

You, D.; Kim, H.; Kim, J.; Han, K.; Heo, H.; Kwon, Y.; Kim, G.; Sul, W.S.; Lee, J.W.; Lee, B.J.; et al. Low-Noise Multimodal Reconfigurable Sensor Readout Circuit for Voltage/Current/Resistive/Capacitive Microsensors. Appl. Sci. 2020, 10, 348. https://doi.org/10.3390/app10010348

You D, Kim H, Kim J, Han K, Heo H, Kwon Y, Kim G, Sul WS, Lee JW, Lee BJ, et al. Low-Noise Multimodal Reconfigurable Sensor Readout Circuit for Voltage/Current/Resistive/Capacitive Microsensors. Applied Sciences. 2020; 10(1):348. https://doi.org/10.3390/app10010348

Chicago/Turabian StyleYou, Donggeun, Hyungseup Kim, Jaesung Kim, Kwonsang Han, Hyunwoo Heo, Yongsu Kwon, Gyungtae Kim, Woo Suk Sul, Jong Won Lee, Boung Ju Lee, and et al. 2020. "Low-Noise Multimodal Reconfigurable Sensor Readout Circuit for Voltage/Current/Resistive/Capacitive Microsensors" Applied Sciences 10, no. 1: 348. https://doi.org/10.3390/app10010348

APA StyleYou, D., Kim, H., Kim, J., Han, K., Heo, H., Kwon, Y., Kim, G., Sul, W. S., Lee, J. W., Lee, B. J., & Ko, H. (2020). Low-Noise Multimodal Reconfigurable Sensor Readout Circuit for Voltage/Current/Resistive/Capacitive Microsensors. Applied Sciences, 10(1), 348. https://doi.org/10.3390/app10010348