Multi-Level Analysis of On-Chip Optical Wireless Links

Abstract

Featured Application

Abstract

1. Introduction

2. Background on Networks-On-Chip

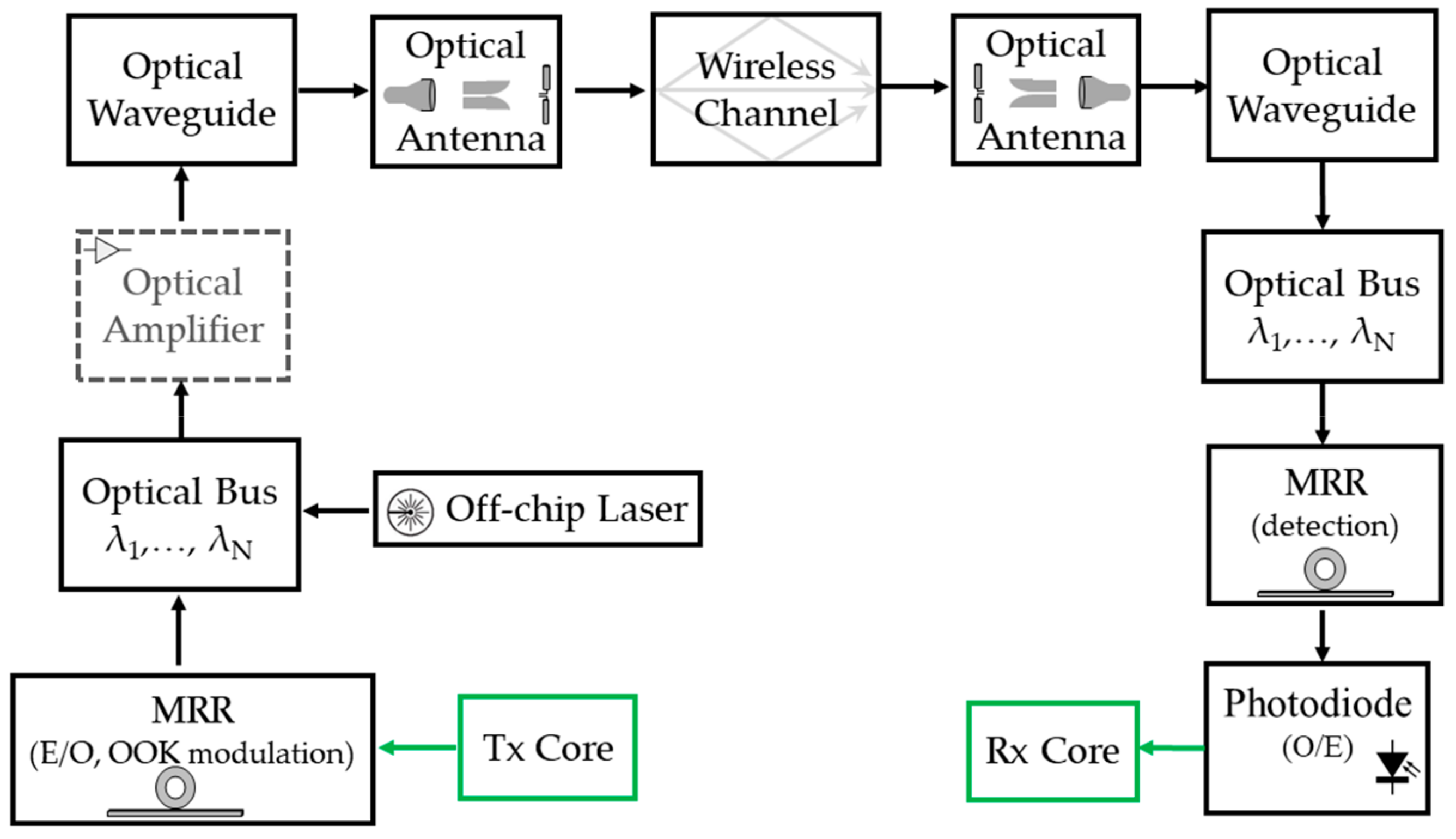

3. Physical Description of the On-Chip, Optical Wireless Link

3.1. Physical Optical Interconnects

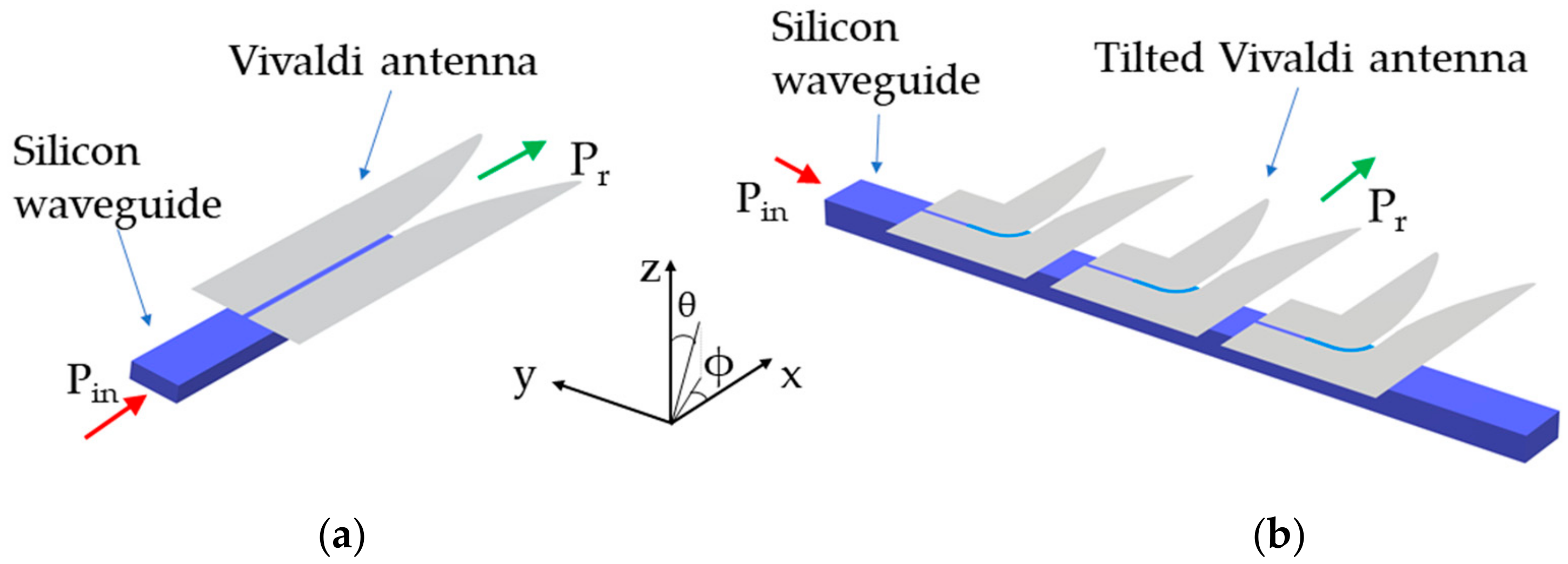

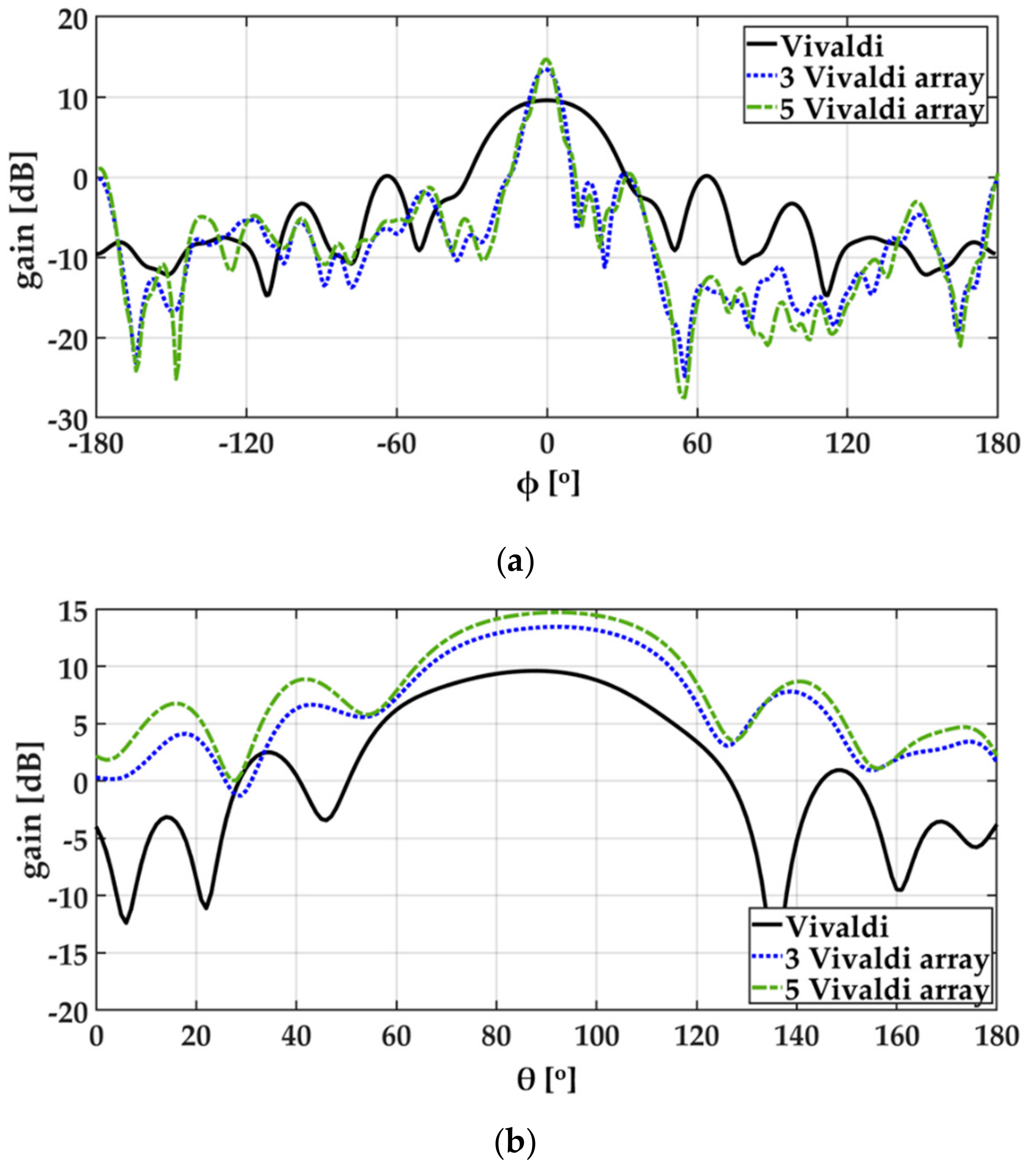

3.2. Optical Antennas

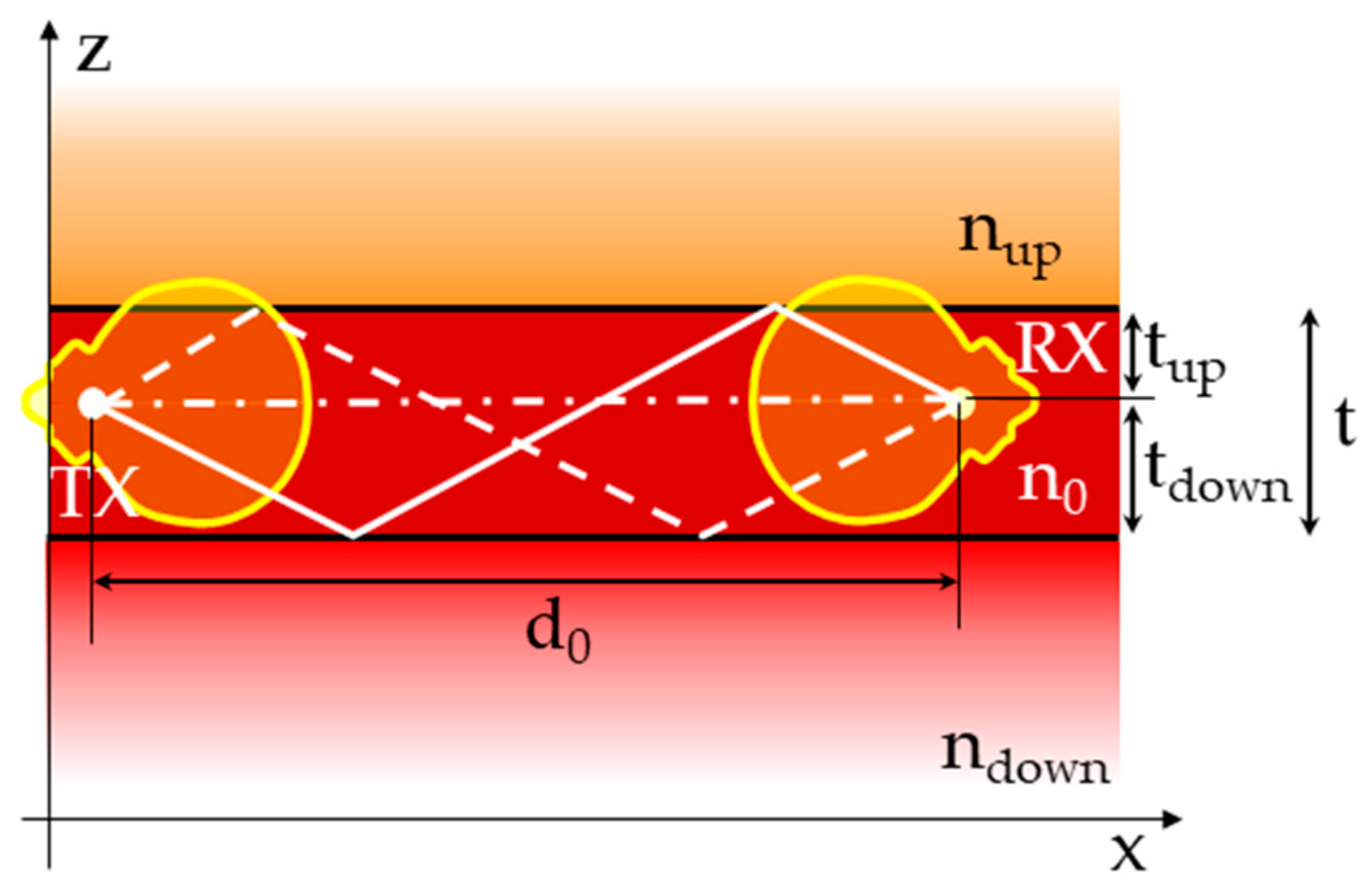

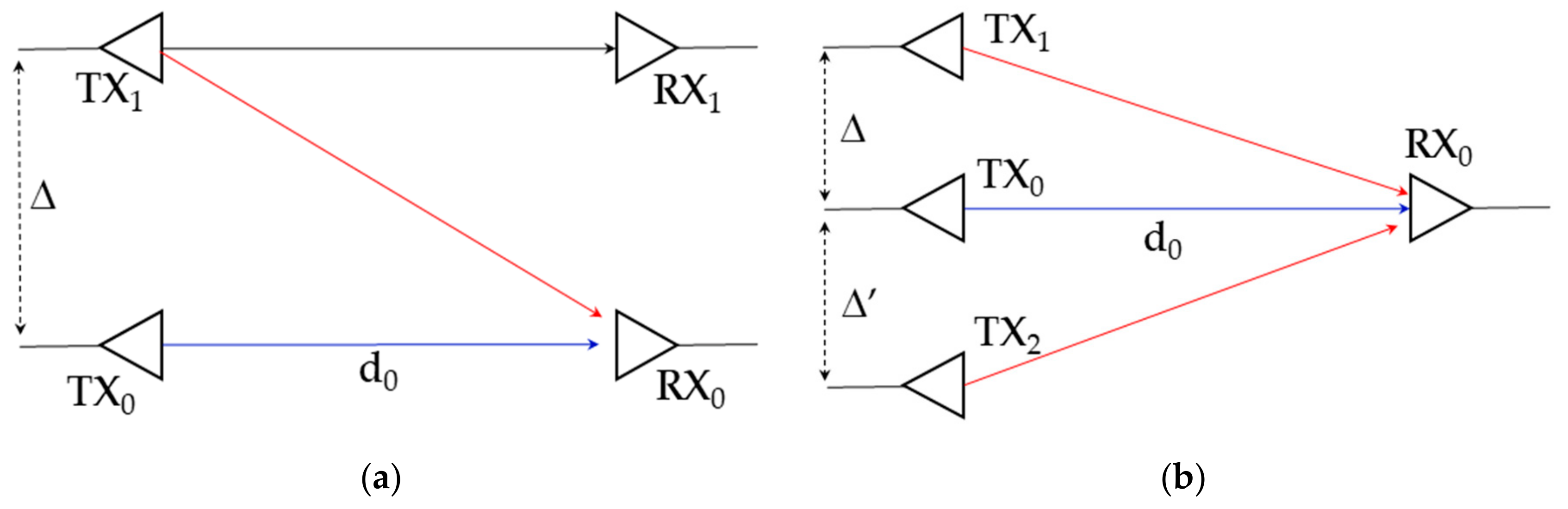

3.3. Optical Wireless Channel

4. Performance Assessment of Optical Wireless Networks-on-Chip

5. Results and Discussion

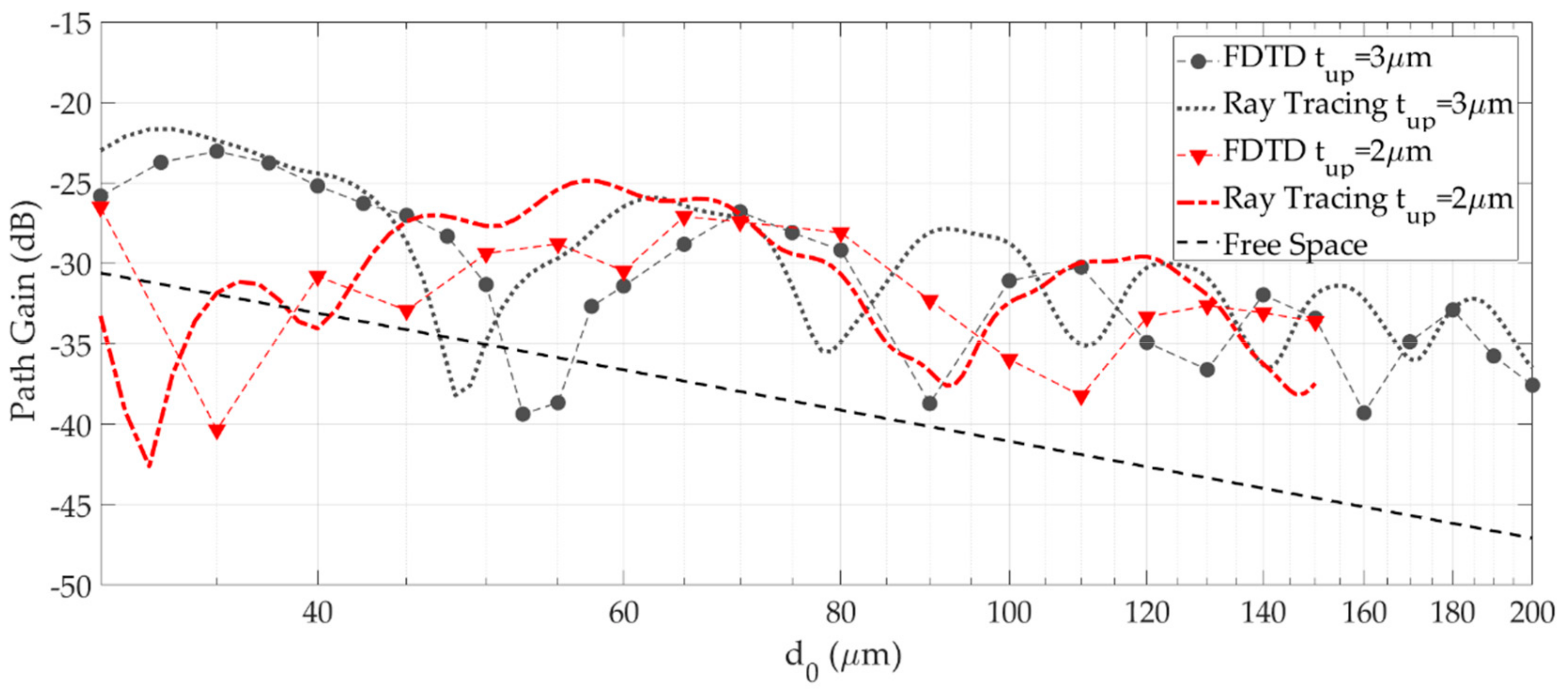

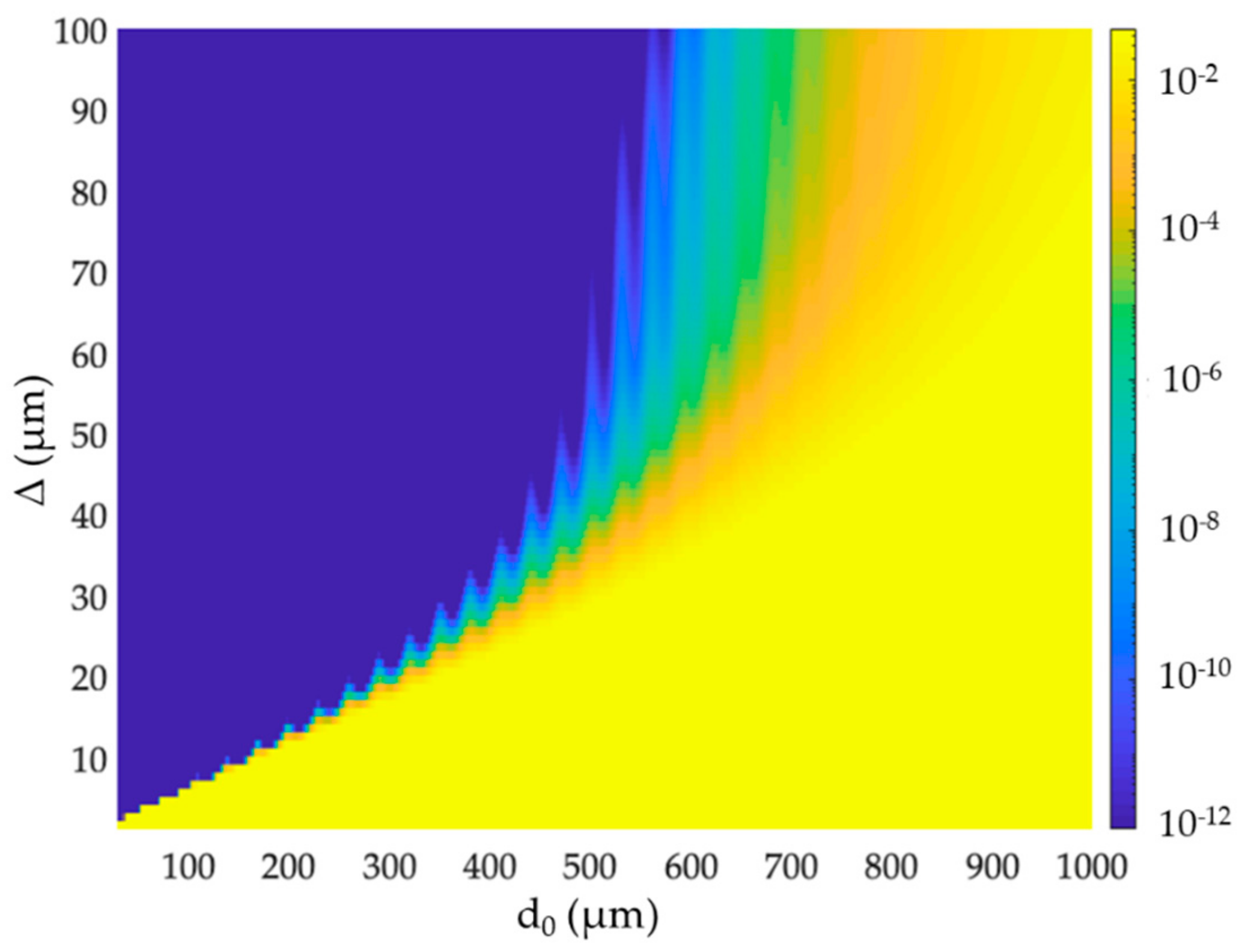

5.1. Ray Tracing Analysis of the Optical Wireless Channel

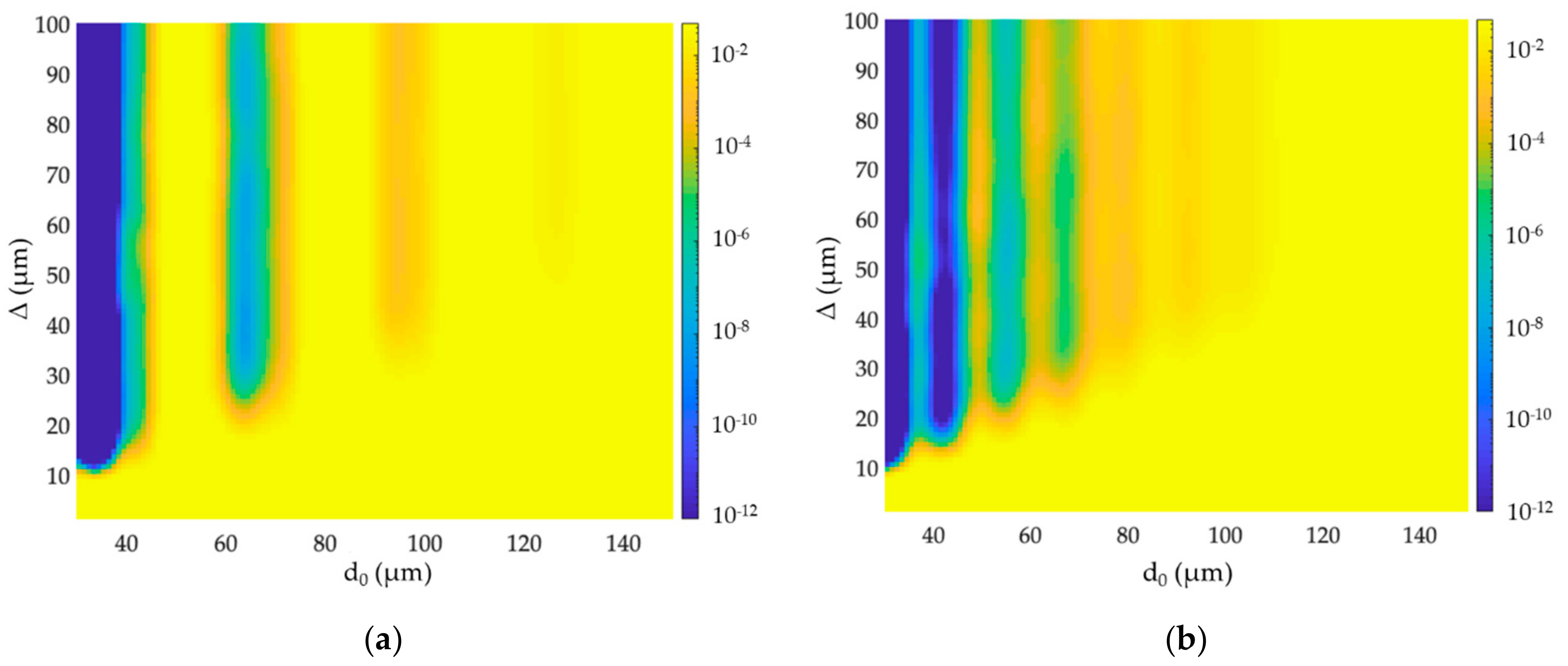

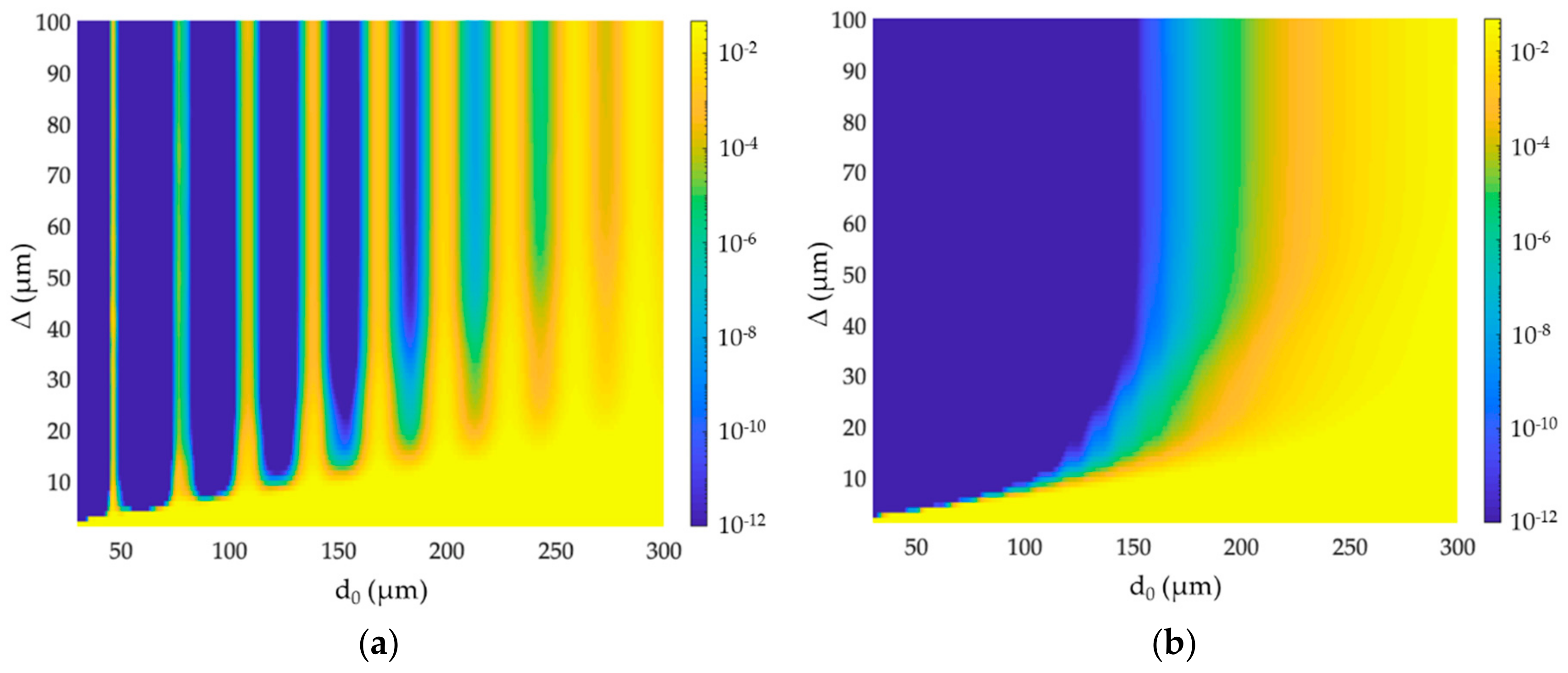

5.2. Link Level Assessment of Bit Error Probability

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Blake, G.; Dreslinski, R.G.; Mudge, T. A survey of multicore processors. IEEE Signal. Process. Mag. 2009, 26, 26–37. [Google Scholar] [CrossRef]

- Abadal, S.; Mestres, A.; Torrellas, J.; Alarcon, E.; Cabellos-Aparicio, A. Medium Access Control in Wireless Network-on-Chip: A Context Analysis. IEEE Commun. Mag. 2018, 56, 172–178. [Google Scholar] [CrossRef]

- Karkar, A.; Mak, T.; Tong, K.-F.; Yakovlev, A. A Survey of Emerging Interconnects for On-Chip Efficient Multicast and Broadcast in Many-Cores. IEEE Circuits Syst. Mag. 2016, 16, 58–72. [Google Scholar] [CrossRef]

- Deb, S.; Ganguly, A.; Pande, P.P.; Belzer, B.; Heo, D. Wireless NoC as Interconnection Backbone for Multicore Chips: Promises and Challenges. IEEE J. Emerg. Sel. Top. Circuits Syst. 2012, 2, 228–238. [Google Scholar] [CrossRef]

- Abdal, S.; Iannazzo, M.; Nemirovsky, M.; Cabellos-Aparicio, A.; Lee, H.; Alarcon, E. On the Area and Energy Scalability of Wireless Network-on-Chip: A Model-Based Benchmarked Design Space Exploration. IEEE Trans. Netw. 2015, 23, 1501–1513. [Google Scholar] [CrossRef]

- Werner, S.; Navaridas, J.; Lujan, M. A Survey on Optical Network-on-Chip Architectures. ACM Comput. Surv. J. 2018, 50, 89. [Google Scholar] [CrossRef]

- Alam, B.; Veroli, A.; Benedetti, A. Analysis on vertical directional couplers with long range surface plasmons for multilayer optical routing. J. Appl. Phys. 2016, 120. [Google Scholar] [CrossRef]

- Matolak, D.W.; Kodi, A.; Kaya, S.; Di Tomaso, D.; Laha, S.; Rayess, W. Wireless Networks-on-Chips: Architecture, Wireless Channel, and Devices. IEEE Wirel. Commun. 2012, 19, 58–65. [Google Scholar] [CrossRef]

- Bellanca, G.; Calò, G.; Kaplan, A.E.; Bassi, P.; Petruzzelli, V. Integrated Vivaldi plasmonic antenna for wireless on-chip optical communications. Opt. Express 2017, 25, 16214–16227. [Google Scholar] [CrossRef]

- Fuschini, F.; Barbiroli, M.; Zoli, M.; Bellanca, G.; Calò, G.; Bassi, P.; Petruzzelli, V. Ray tracing modeling of electromagnetic propagation for on-chip wireless optical communications. J. Low Power Electron. Appl. 2018, 8, 39. [Google Scholar] [CrossRef]

- Karanth, A.; Kaya, S.; Sikder, A.M.; Louri, A.; Laha, S.; Carbaugh, D.; Xin, H.; Wu, J.; DiTomaso, D. Sustainability in Network-on-Chips by Exploring Heterogeneity in Emerging Technologies. IEEE Trans. Sustain. Comput. 2019, 4, 293–307. [Google Scholar] [CrossRef]

- Zhang, Y.P.; Chen, Z.M.; Sui, M. Propagation Mechanisms of Radio Waves over Intra-Chip Channels with Integrated Antennas: Frequency-Domain Measurements and Time Domain Analysis. IEEE Trans. Antennas Propag. 2007, 55, 2900–2906. [Google Scholar] [CrossRef]

- Yan, L.; Hanson, G.W. Wave Propagation Mechanisms for Intra-Chip Communications. IEEE Trans. Antennas Propag. 2009, 57, 2715–2724. [Google Scholar]

- El Masri, I.; Martin, P.-M.; Mondal, H.K.; Allanic, R.; Le Gouguec, T.; Quendo, C.; Roland, C.; Diguet, J.-P. Accurate Channel Models for Realistic Design Space Exploration of Future Wireless NoCs. In Proceedings of the 12th IEEE/ACM International Symposium on Networks-on-Chip, Turin, Italy, 4–5 October 2018. [Google Scholar]

- Timoneda, X.; Cabellos-Aparicio, A.; Manessis, D.; Alarcon, E.; Abadal, S. Channel Characterization for Chip-scale Wireless Communications within Computing Packages. In Proceedings of the 12th IEEE/ACM International Symposium on Networks-on-Chip, Turin, Italy, 4–5 October 2018. [Google Scholar]

- Gade, S.H.; Rout, S.S.; Deb, S. On-Chip Wireless Channel Propagation: Impact of Antenna Directionality and Placement on Channel Performance. In Proceedings of the 12th IEEE/ACM International Symposium on Networks-on-Chip, Turin, Italy, 4–5 October 2018. [Google Scholar]

- Laha, S.; Kaya, S.; Matolak, D.W.; Rayess, W.; DiTomaso, D.; Kodi, A. A New Frontier in Ultralow Power Wireless Links: Network-on-Chip and Chip-to-Chip Interconnects. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2015, 34, 186–198. [Google Scholar] [CrossRef]

- Nafari, M.; Feng, L.; Jornet, J.M. On-chip Wireless Optical Channel Modeling for Massive Multi-core Computing Architectures. In Proceedings of the 2017 IEEE Wireless Communications and Networking Conference, San Francisco, CA, USA, 19–22 March 2017. [Google Scholar]

- Garcia-Meca, C.; Lechago, S.; Brimont, A.; Griol, A.; Mas, S.; Sanchez, L.; Bellieres, L.; Losilla, N.S.; Martì, J. On-chip wireless silicon photonics: From reconfigurable interconnects to lab-on-chip devices. Light: Sci. Appl. 2017, 6, e17053. [Google Scholar] [CrossRef]

- Miller, D.A.B. Device Requirements for Optical Interconnects to Silicon Chips. Proc. IEEE 2009, 97, 1166–1185. [Google Scholar] [CrossRef]

- Benini, L.; De Micheli, G. Networks on chips: A new SoC paradigm. Computer 2002, 35, 70–78. [Google Scholar] [CrossRef]

- Duong, L.H.K.; Wang, Z.; Nikdast, M.; Xu, J.; Yang, P.; Wang, Z.; Maeda, R.K.V.; Li, H.; Wang, X.; Le Beux, S.; et al. Coherent and Incoherent Crosstalk Noise Analyses in Interchip/Intrachip Optical Interconnection Networks. IEEE Trans. Very Large Scale Integr. Syst. 2016, 24, 2475–2487. [Google Scholar] [CrossRef]

- Ganguly, A.; Chang, K.; Deb, S.; Pande, P.P.; Belzer, B.; Teuscher, C. Scalable Hybrid Wireless Network-on-Chip Architectures for Multicore Systems. IEEE Trans. Comput. 2011, 60, 1485–1502. [Google Scholar] [CrossRef]

- Matolak, D.W.; Kaya, S.; Kodi, A. Channel Modeling for Wireless Networks-on-Chips. IEEE Commun. Mag. 2013, 51, 180–186. [Google Scholar] [CrossRef]

- Levi, A.F.J. Silicon Photonics Stumbles at the Last Meter. IEEE Spectr. 2018. Available online: https://spectrum.ieee.org/semiconductors/optoelectronics/silicon-photonics-stumbles-at-the-last-meter (accessed on 25 December 2019).

- Van Zant, P. Microchip Fabrication: A Practical Guide to Semiconductor Process.; McGraw-Hill Education: New York City, NY, USA, 2014. [Google Scholar]

- Ohashi, K.; Nishi, K.; Shimizu, T.; Nakada, M.; Fujikata, J.; Ushida, J.; Torii, S.; Nose, K.; Mizuno, M.; Yukawa, H.; et al. On-Chip Optical Interconnect. Proc. IEEE 2009, 97, 1186–1198. [Google Scholar] [CrossRef]

- Bakir, M.S.; Meindl, J.D. Integrated Interconnect Technologies for 3D Nanoelectronic Systems; Artech House: Norwood, MA, USA, 2009; pp. 183–248. [Google Scholar]

- Sun, C.; Wade, M.T.; Lee, Y.; Orcutt, J.S.; Alloatti, L.; Georgas, M.S.; Waterman, A.S.; Shainline, J.M.; Avizienis, R.R.; Lin, S.; et al. Single-chip microprocessor that communicates directly using light. Nature 2015, 528, 534–538. [Google Scholar] [CrossRef] [PubMed]

- Atabaki, A.H.; Moazeni, S.; Pavanello, F.; Gevorgyan, H.; Notaros, J.; Alloatti, L.; Wade, M.T.; Sun, C.; Kruger, S.A.; Meng, H.; et al. Integrating photonics with silicon nanoelectronics for the next generation of systems on a chip. Nature 2018, 556, 349–354. [Google Scholar] [CrossRef] [PubMed]

- Stojanović, V.M.; Ram, R.J.; Popović, M.A.; Lin, S.; Moazeni, S.; Wade, M.; Sun, C.; Alloatti, L.; Atabaki, A.; Pavanello, F.; et al. Monolithic silicon-photonic platforms in state-of-the-art CMOS SOI processes. Opt. Express 2018, 26, 13106–13121. [Google Scholar] [CrossRef]

- Van Winkle, S.; DiTomaso, D.; Kennedy, M.; Kodi, A. Energy-efficient optical Network-on-Chip architecture for heterogeneous multicores. In Proceedings of the IEEE Optical Interconnects Conference, San Diego, CA, USA, 9–11 May 2016. [Google Scholar]

- Bogaerts, W.; De Heyn, P.; Van Vaerenbergh, T.; De Vos, K.; Selvaraja, S.K.; Dumon, P.; Bienstman, P.; Van Thourhout, D.; Baets, R. Silicon microring resonators. Laser Photonics Rev. 2012, 6, 47–73. [Google Scholar] [CrossRef]

- Agrawal, P. Lightwave Technology: Telecommunication Systems; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2005. [Google Scholar]

- Mondal, H.K.; Gade, S.H.; Deb, S.; Ganguly, A. Interference-Aware Wireless Network-on-Chip Architecture Using Directional Antennas. IEEE Trans. Multi-Scale Comput. Syst. 2017, 3, 193–205. [Google Scholar] [CrossRef]

- Vantrease, D.; Schreiber, R.; Monchiero, M.; McLaren, M.; Jouppi, N.P.; Fiorentino, M.; Davis, A.; Binkert, N.; Beausoleil, R.G.; Ahn, J.H. Corona: System Implications of Emerging Nanophotonic Technology. In Proceedings of the International Symposium on Computer Architecture, Beijing, China, 21–25 June 2008. [Google Scholar]

- Calò, G.; Bellanca, G.; Alam, B.; Kaplan, A.E.; Bassi, P.; Petruzzelli, V. Array of plasmonic vivaldi antennas coupled to silicon waveguides for wireless networks through on-chip optical technology. Opt. Express 2018, 26, 30267–30277. [Google Scholar] [CrossRef]

- Calò, G.; Bellanca, G.; Kaplan, A.E.; Bassi, P.; Petruzzelli, V. Double vivaldi antenna for wireless optical networks on chip. Opt. Quantum Electron. 2018, 50, 261. [Google Scholar] [CrossRef]

- Calò, G.; Alam, B.; Bellanca, G.; Fuschini, F.; Barbiroli, M.; Tralli, V.; Bassi, P.; Stomeo, T.; Bozzetti, M.; Kaplan, A.E.; et al. Dielectric and Plasmonic Vivaldi Antennas for On-Chip Wireless Communication. In Proceedings of the 21st International Conference on Transparent Optical Networks, Angers, France, 9–13 July 2019. [Google Scholar]

- Shafiei Dehkordi, J.; Tralli, V. Interference Analysis for Optical Wireless Interconnections. In Proceedings of the 29th IEEE International Symposium on Personal, Indoor and Mobile Radio Communications, Bologna, Italy, 9–12 September 2018. [Google Scholar]

- Shafiei Dehkordi, J.; Tralli, V. Interference Analysis for Optical Wireless Communications in Network-on-Chip Scenarios. IEEE Trans. Commun. (Early Access) 2019. [Google Scholar] [CrossRef]

- Wang, J.; Lee, S. Ge-Photodetectors for Si-Based Optoelectronic Integration. Sensors 2011, 11, 696–718. [Google Scholar] [CrossRef]

- Sikder, M.A.I.; Kodi, A.; Kaya, S.; Louri, A. OWN: Optical and Wireless Network-on-Chip for Kilo-core Architectures. In Proceedings of the 23rd Annual Symposium on High-Performance Interconnects, Santa Clara, CA, USA, 26–28 August 2015. [Google Scholar]

- Burns, G. Solid State Physics; Academic Press: Cambridge, MA, USA, 1986. [Google Scholar]

| Interconnect Solution | NoC Technology | Related References |

|---|---|---|

| Physical Interconnection | Networks-on-Chip (NoC) | [1,5,20,21] |

| Optical Networks-on-Chip (ONoC) | [5,6,11,20,22] | |

| Wireless Networks | Millimeter wave and THz (WiNoC) | [4,5,8,17,23,24] |

| Optical (OWiNoC) | [9,10,18,19,24] |

| Geometrical | Electromagnetic | ||

|---|---|---|---|

| tdown | 2 μm or 3 μm | frequency | 193.5 THz (λ0 = 1.55 μm) |

| tup | 2 μm or 3 μm | ndown | 3.47 (Silicon, metal otherwise) |

| t | tdown + tup | n0 | 1.44 (Silica) |

| d | tens to hundreds of μm | nup | 1 (Air) |

| antenna | single/array of plasmonic Vivaldi antenna [9,37] | ||

| System Parameter | Value |

|---|---|

| Pin,av | 0 dBm |

| ηPD | 0.7 A/W |

| Rb | 10 Gbit/s |

| Teq | 600 K |

| RL | 1 kΩ |

| K | 1.38 × 10−23 J/k |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Fuschini, F.; Barbiroli, M.; Calò, G.; Tralli, V.; Bellanca, G.; Zoli, M.; Shafiei Dehkordi, J.; Nanni, J.; Alam, B.; Petruzzelli, V. Multi-Level Analysis of On-Chip Optical Wireless Links. Appl. Sci. 2020, 10, 196. https://doi.org/10.3390/app10010196

Fuschini F, Barbiroli M, Calò G, Tralli V, Bellanca G, Zoli M, Shafiei Dehkordi J, Nanni J, Alam B, Petruzzelli V. Multi-Level Analysis of On-Chip Optical Wireless Links. Applied Sciences. 2020; 10(1):196. https://doi.org/10.3390/app10010196

Chicago/Turabian StyleFuschini, Franco, Marina Barbiroli, Giovanna Calò, Velio Tralli, Gaetano Bellanca, Marco Zoli, Jinous Shafiei Dehkordi, Jacopo Nanni, Badrul Alam, and Vincenzo Petruzzelli. 2020. "Multi-Level Analysis of On-Chip Optical Wireless Links" Applied Sciences 10, no. 1: 196. https://doi.org/10.3390/app10010196

APA StyleFuschini, F., Barbiroli, M., Calò, G., Tralli, V., Bellanca, G., Zoli, M., Shafiei Dehkordi, J., Nanni, J., Alam, B., & Petruzzelli, V. (2020). Multi-Level Analysis of On-Chip Optical Wireless Links. Applied Sciences, 10(1), 196. https://doi.org/10.3390/app10010196