Real-Time Temperature Estimation of the Machine Drive SiC Modules Consisting of Parallel Chips per Switch for Reliability Modelling and Lifetime Prediction

Abstract

1. Introduction

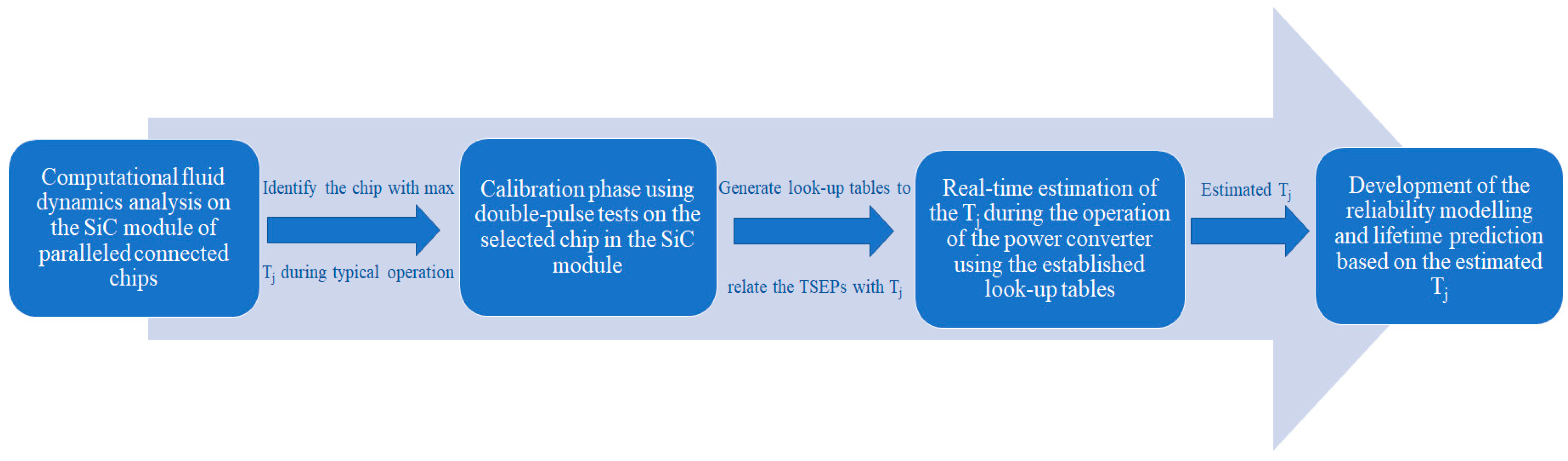

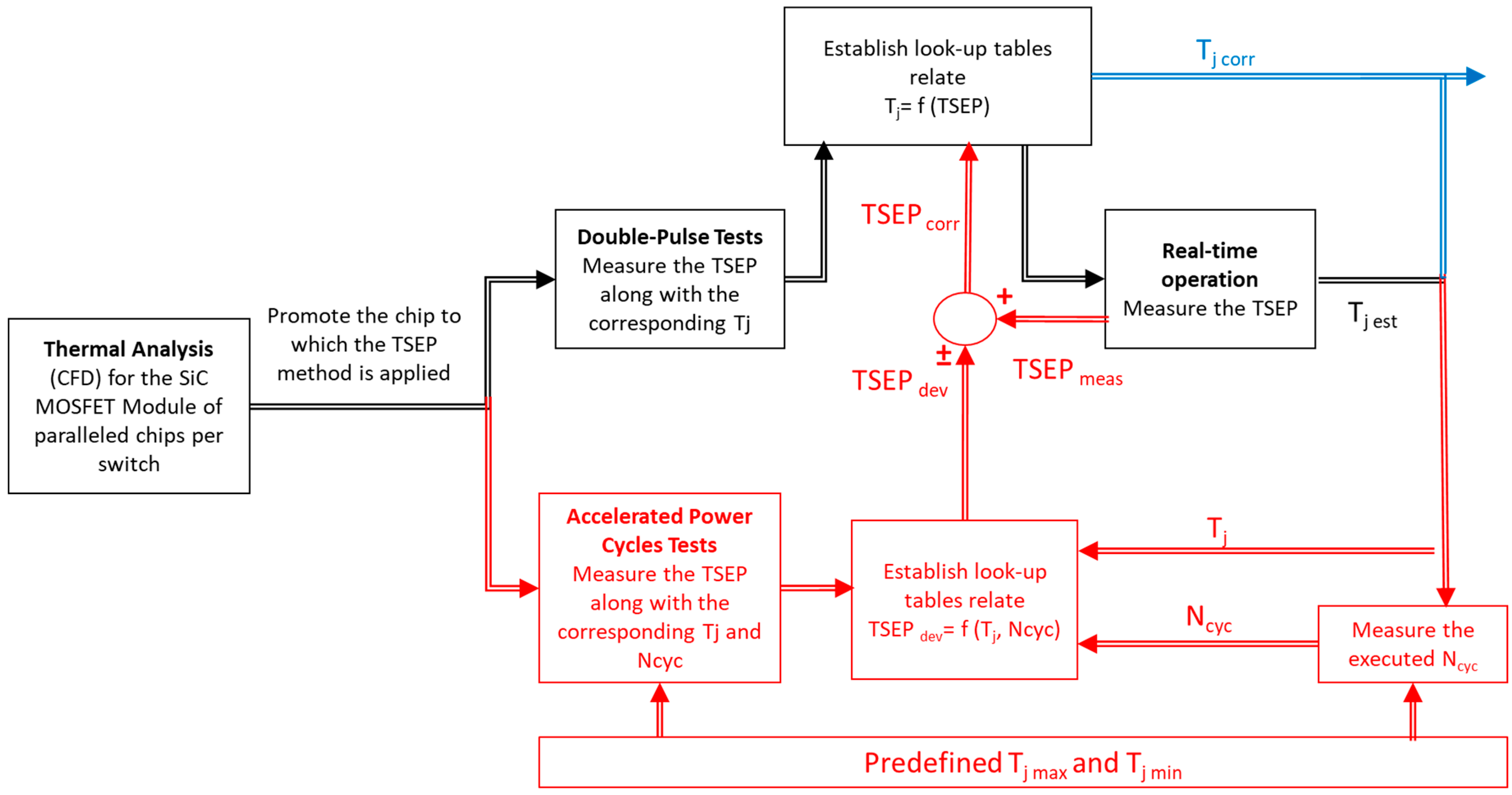

2. Proposed Methodical Procedure for the Tj Estimation

3. Thermal Analysis for the SiC MOSFET Module

- The inlet air temperature is at 40 °C with a fixed airflow rate of 4 m/s.

- SiC chips with thermal conductivity of 150 W/mK.

- Silver sintering simulated as a solid with thermal conductivity of 250 W/mK [43] and thickness of 100 µm.

- DBC copper Si3N4 layers with thermal conductivities 398 and 85 W/mK.

4. Double-Pulse Tests

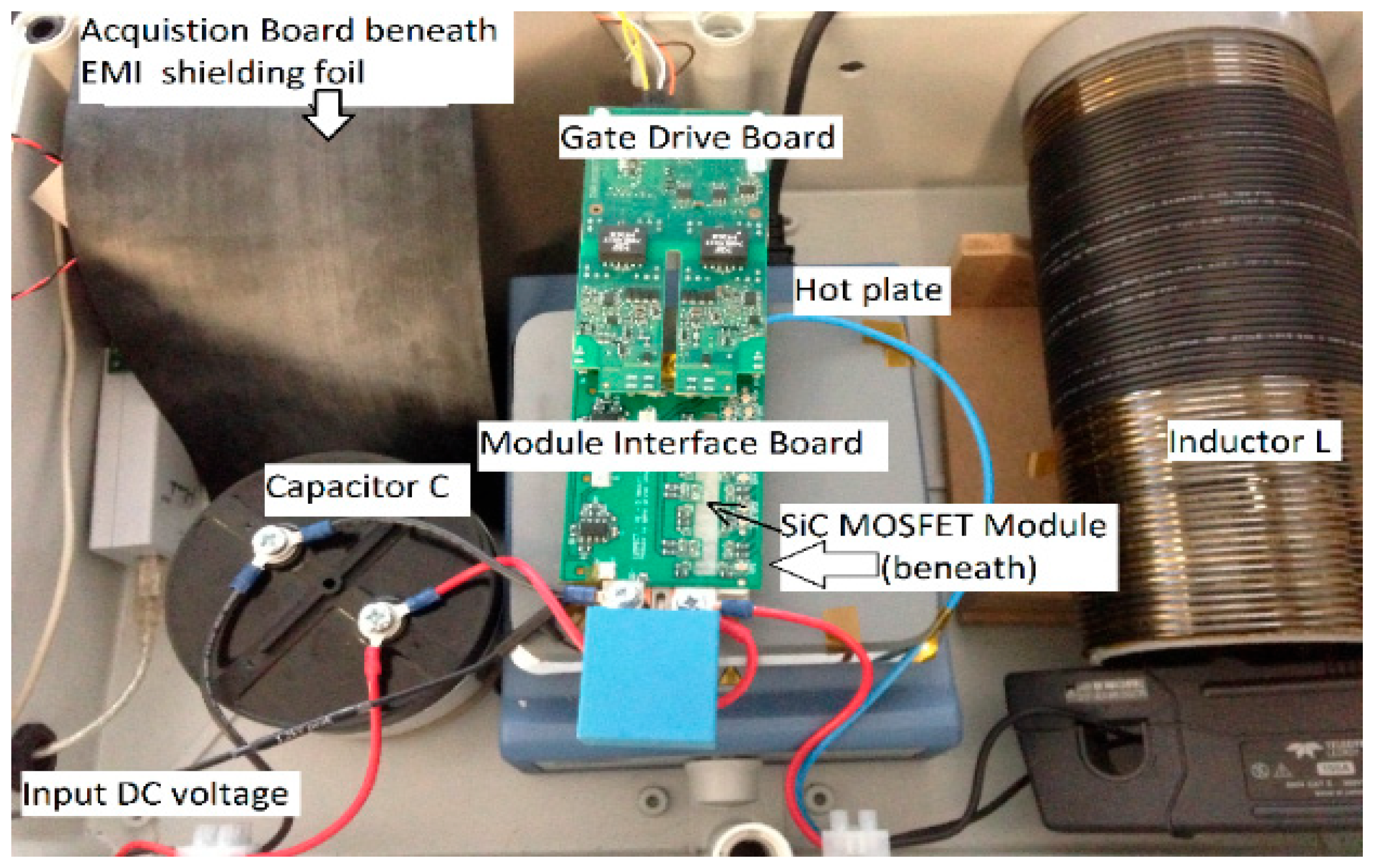

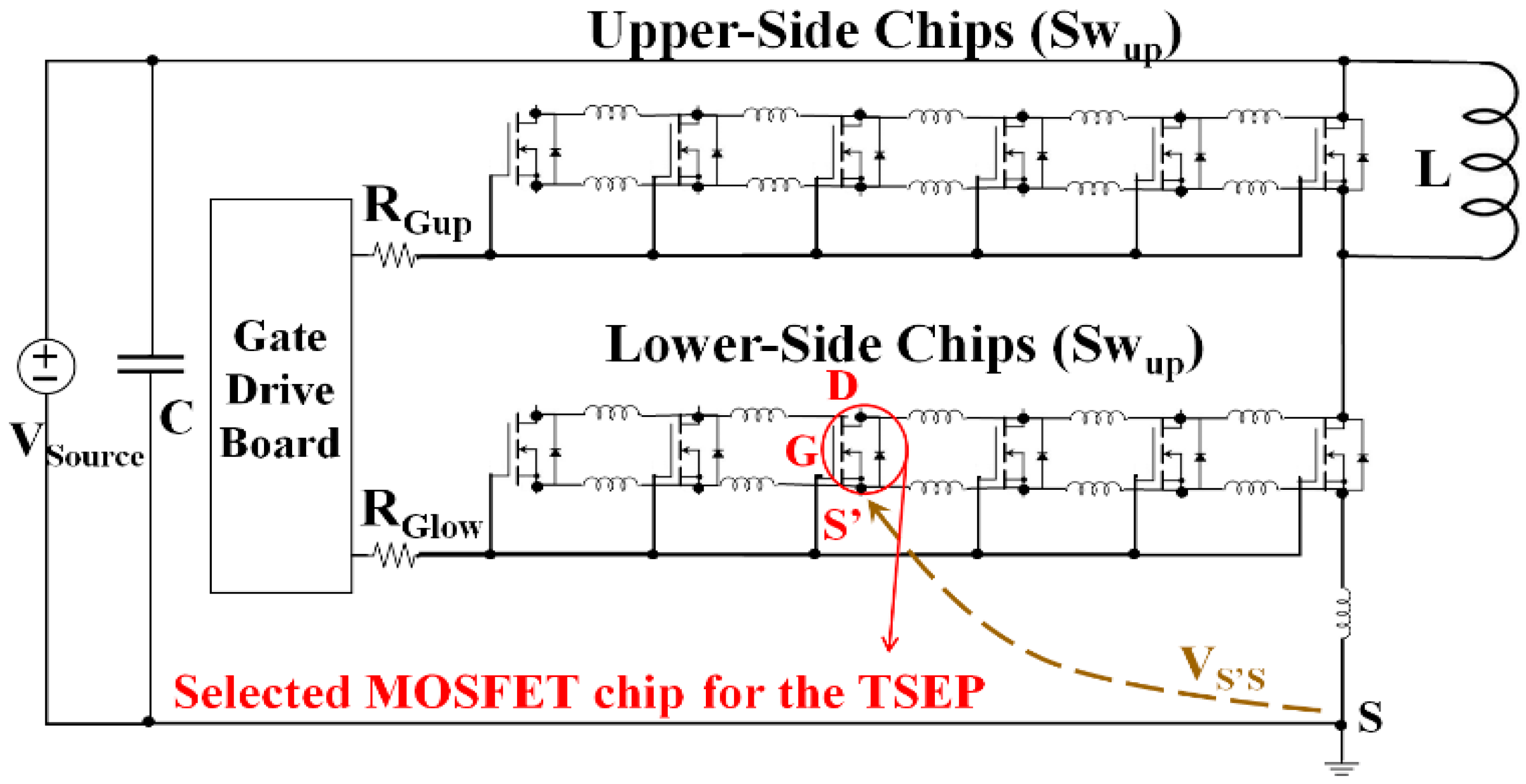

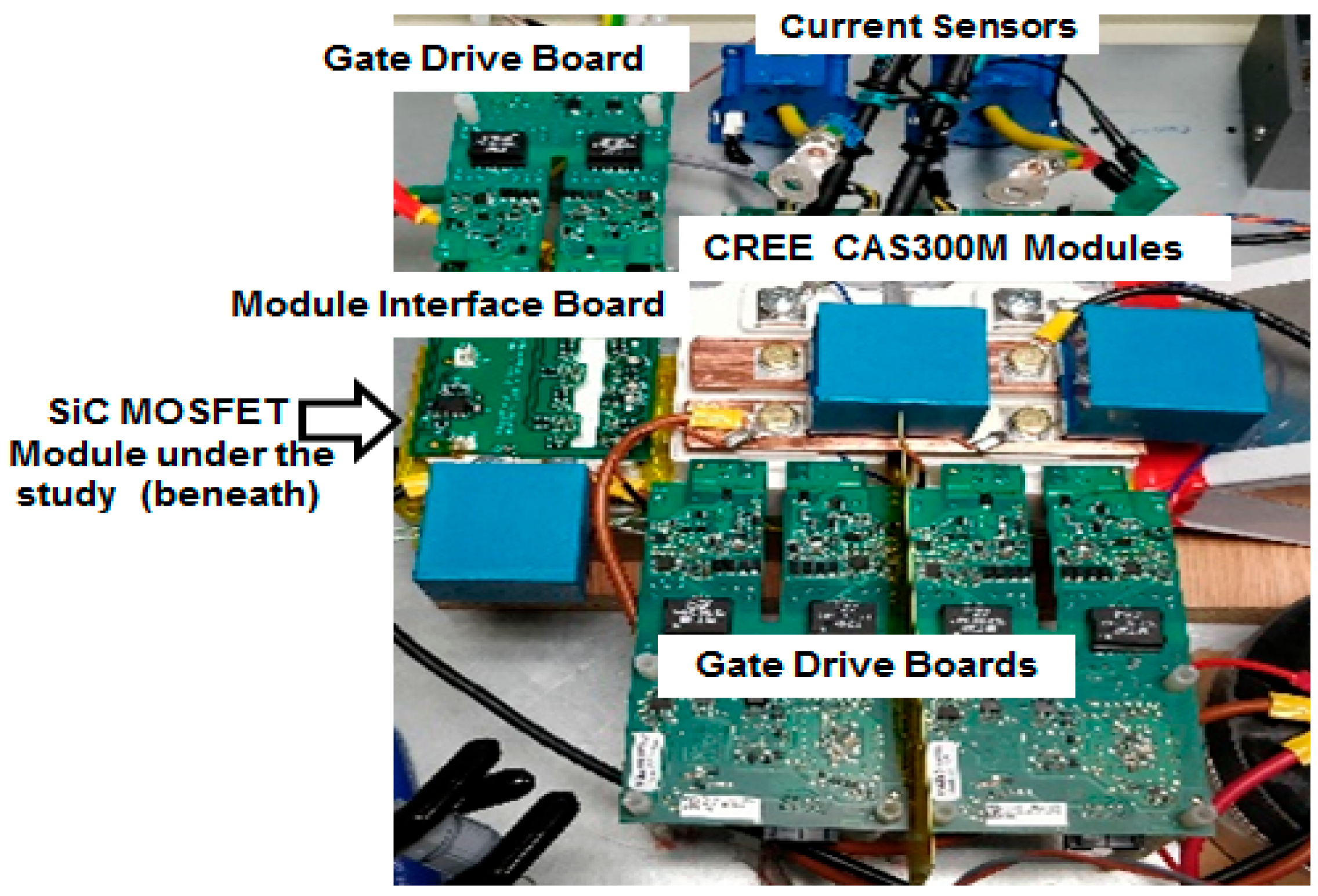

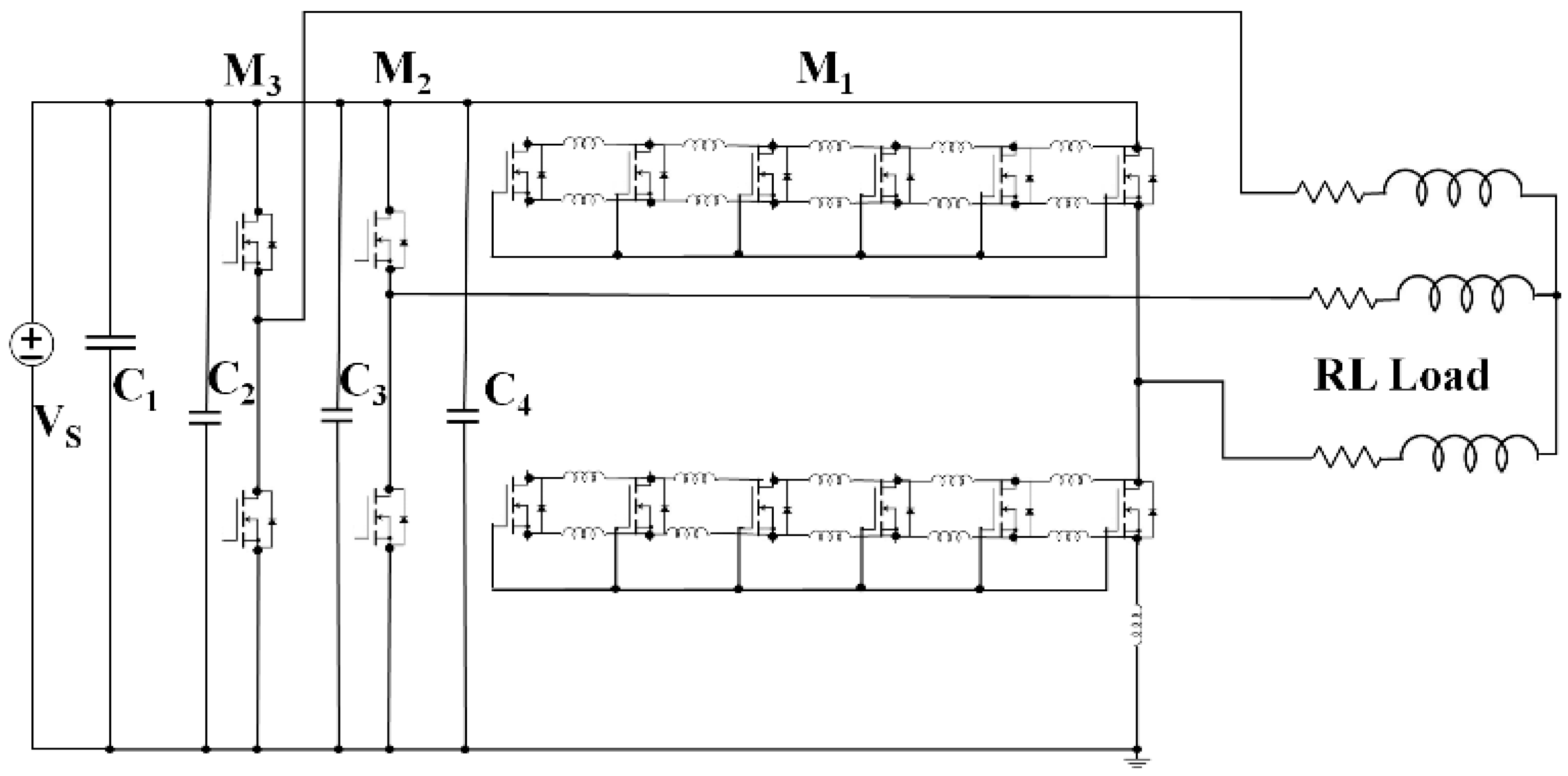

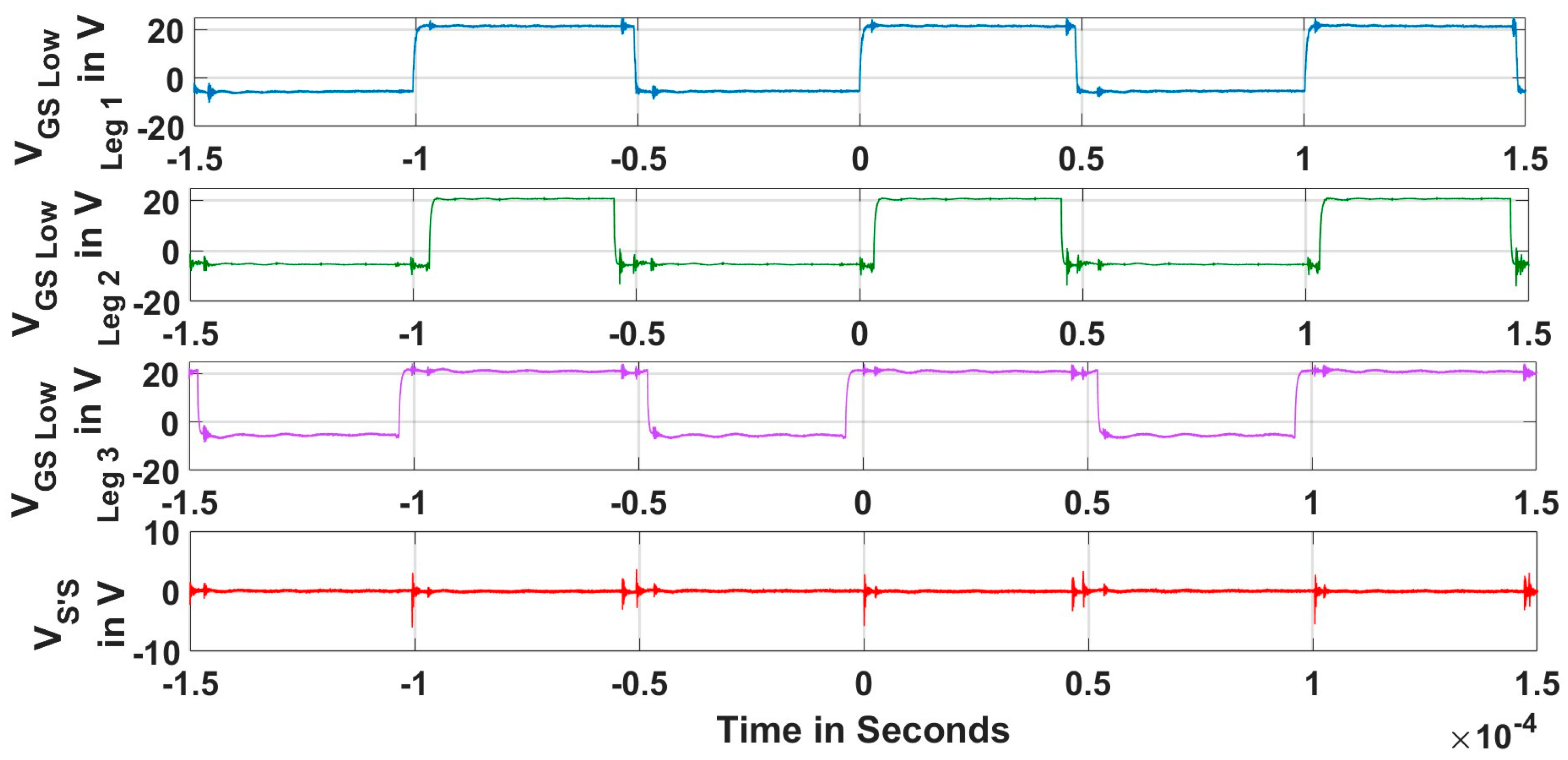

5. Real-Time Inverter Operation

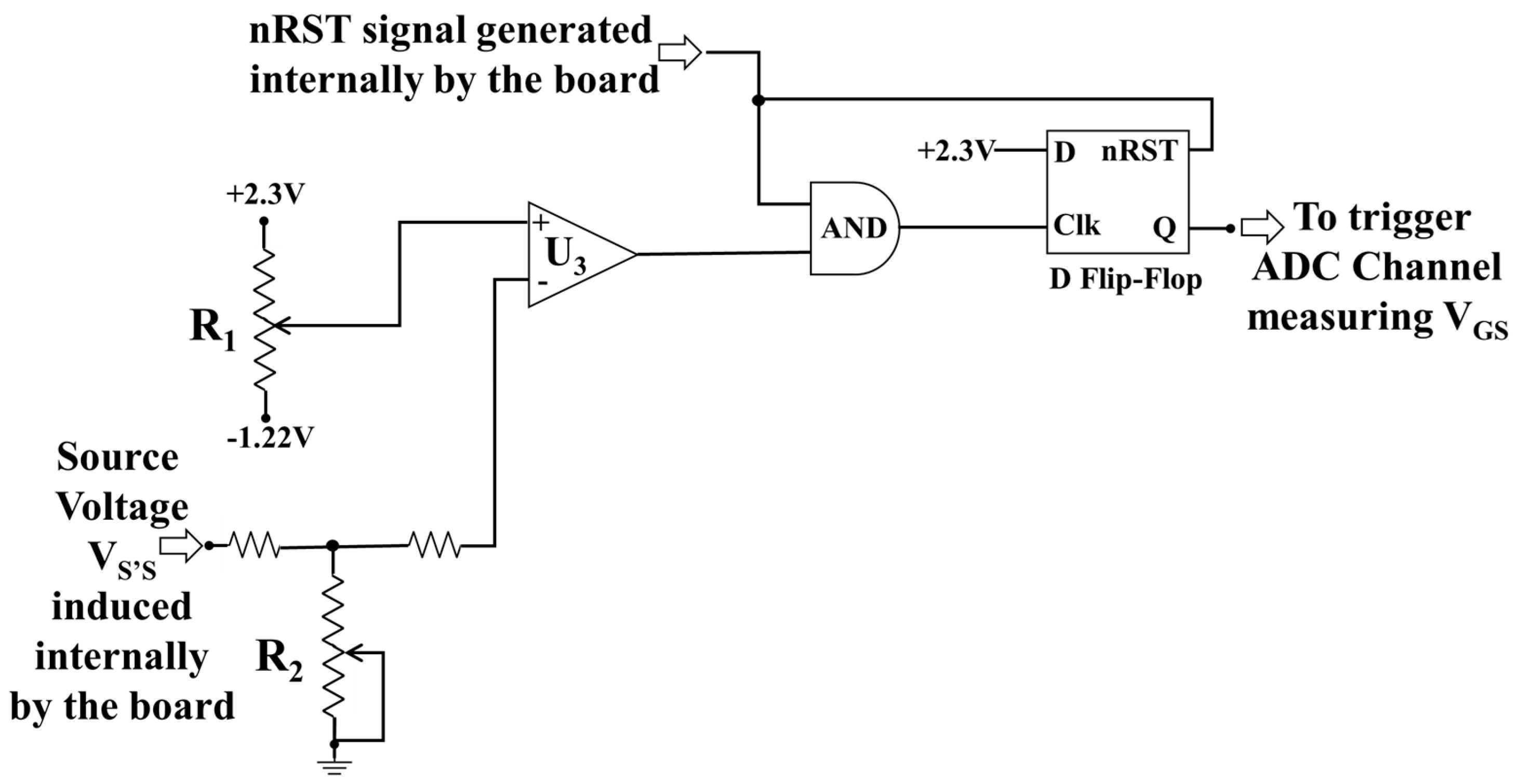

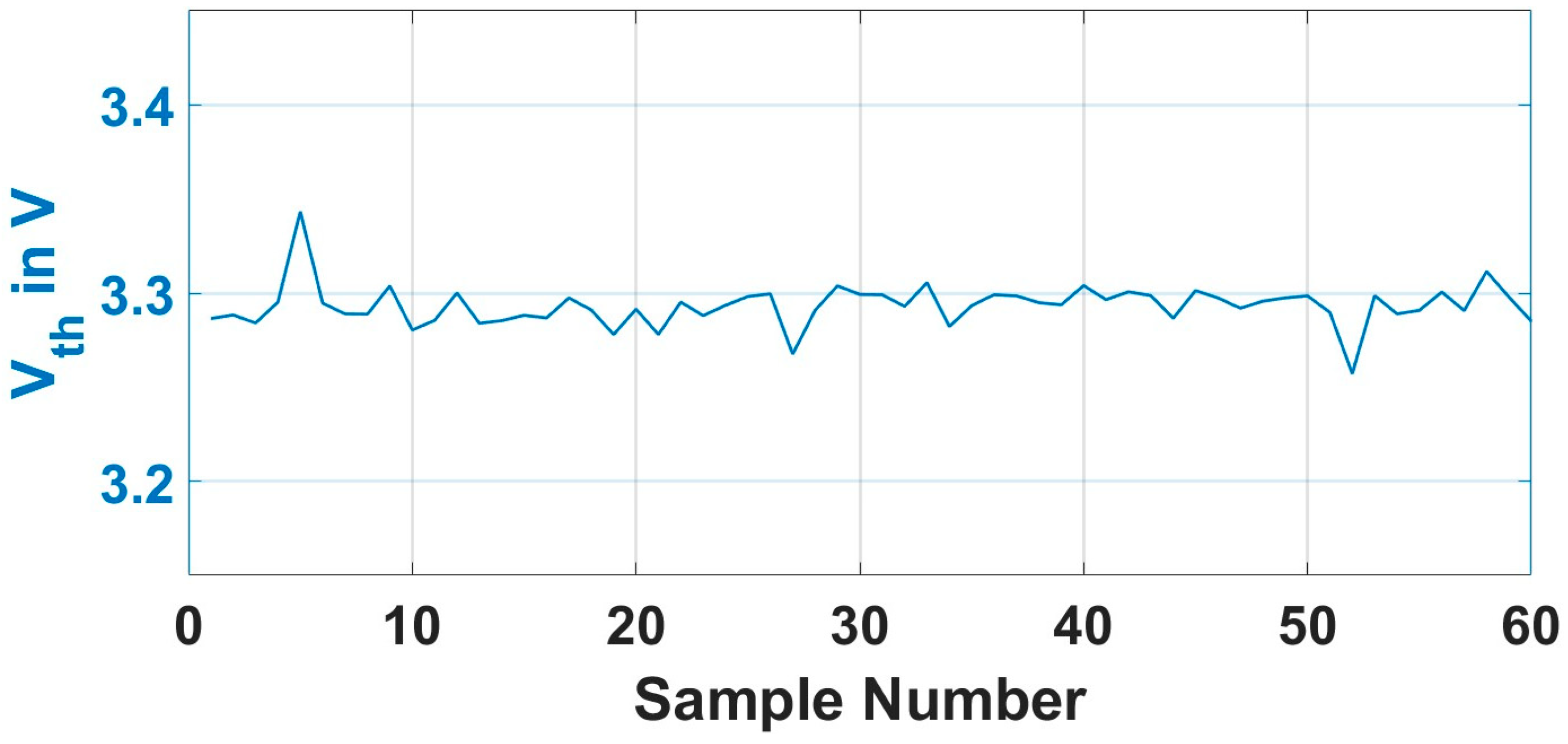

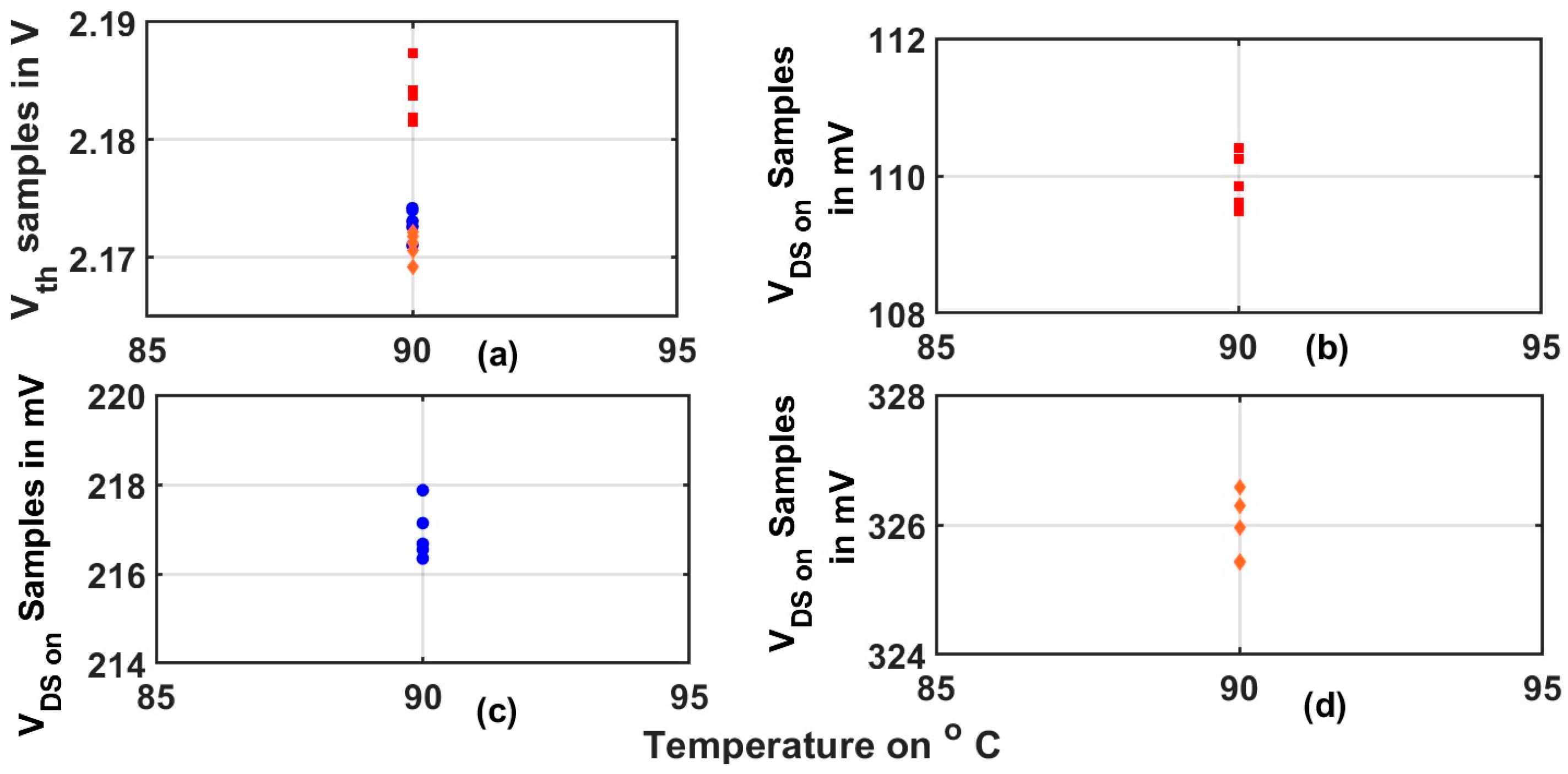

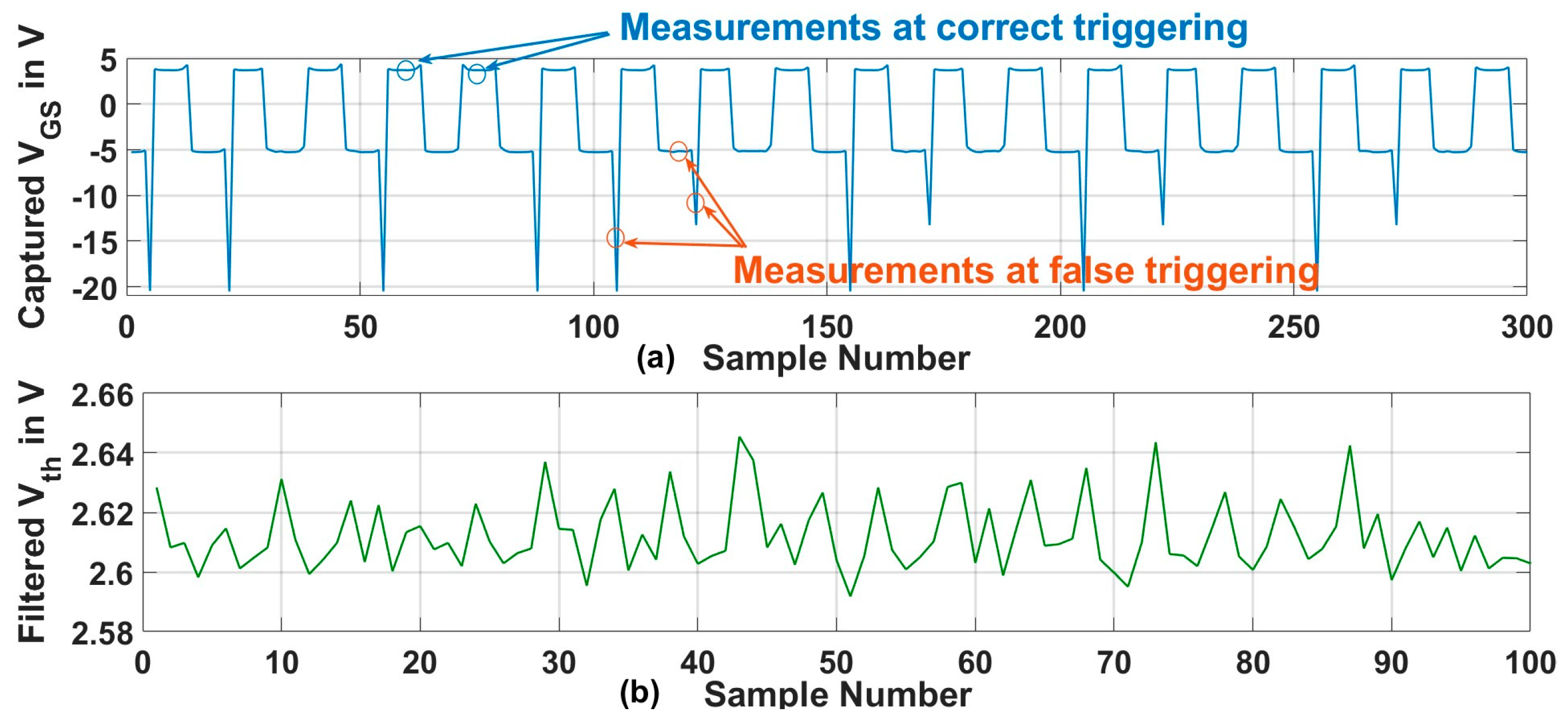

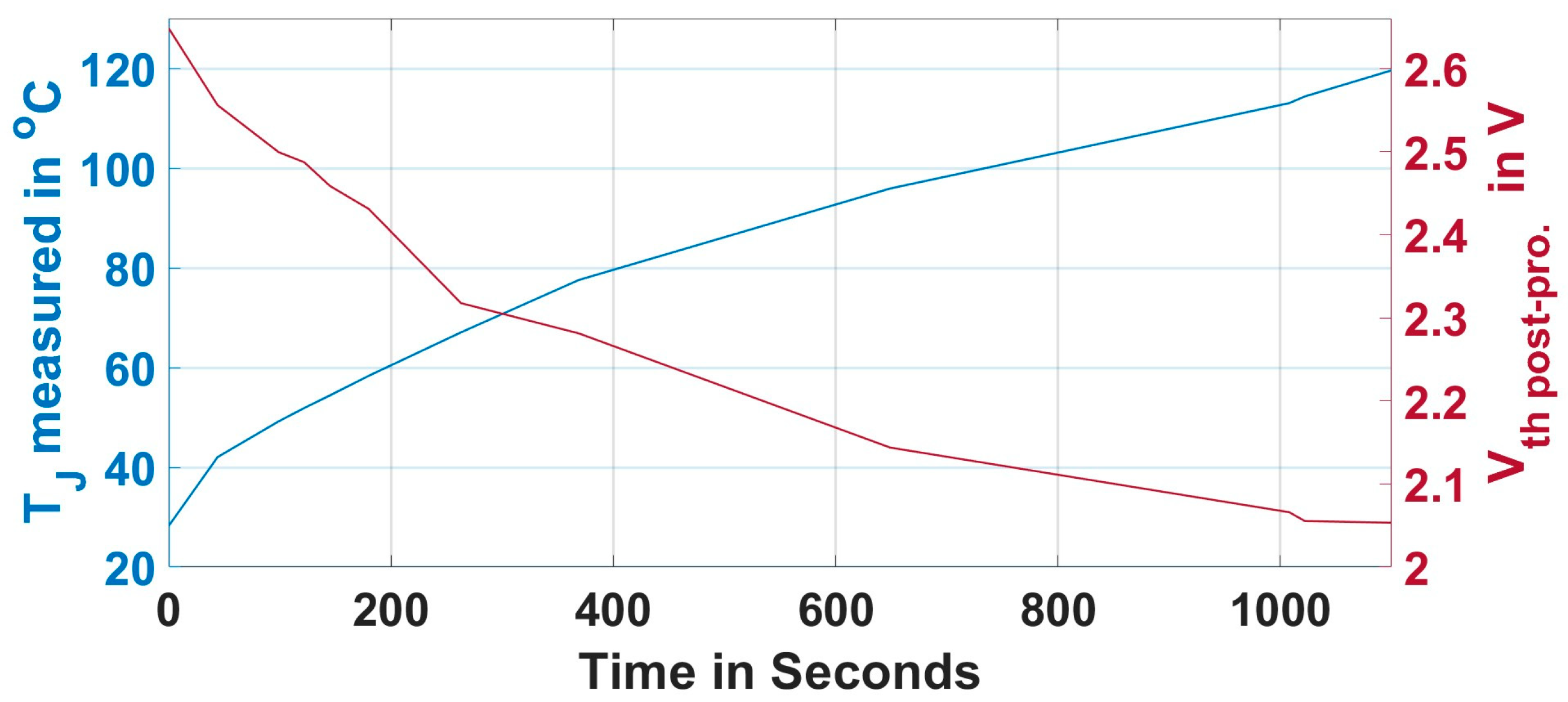

5.1. On-Line Tj Estimation Based on the Vth Measurements

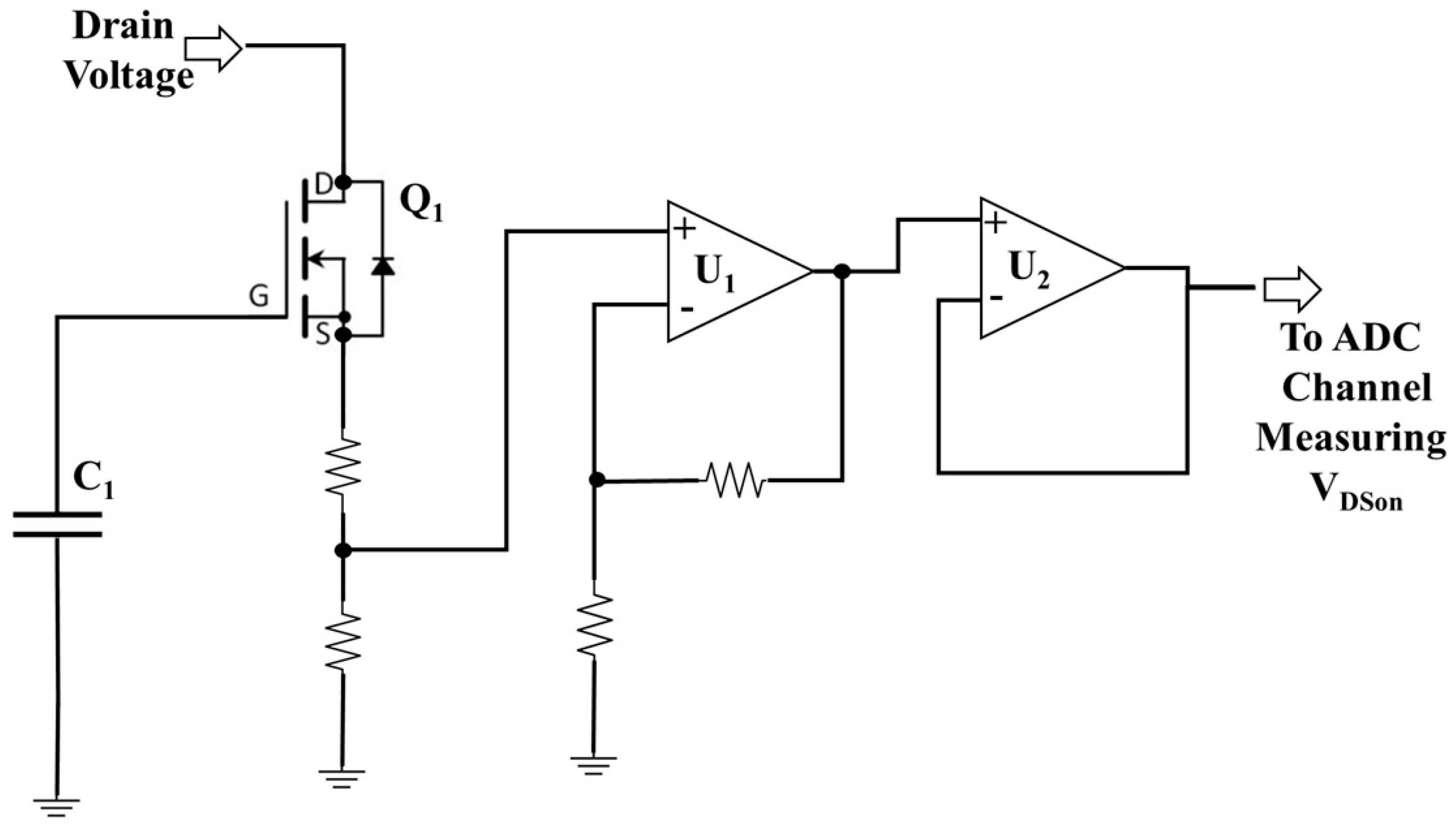

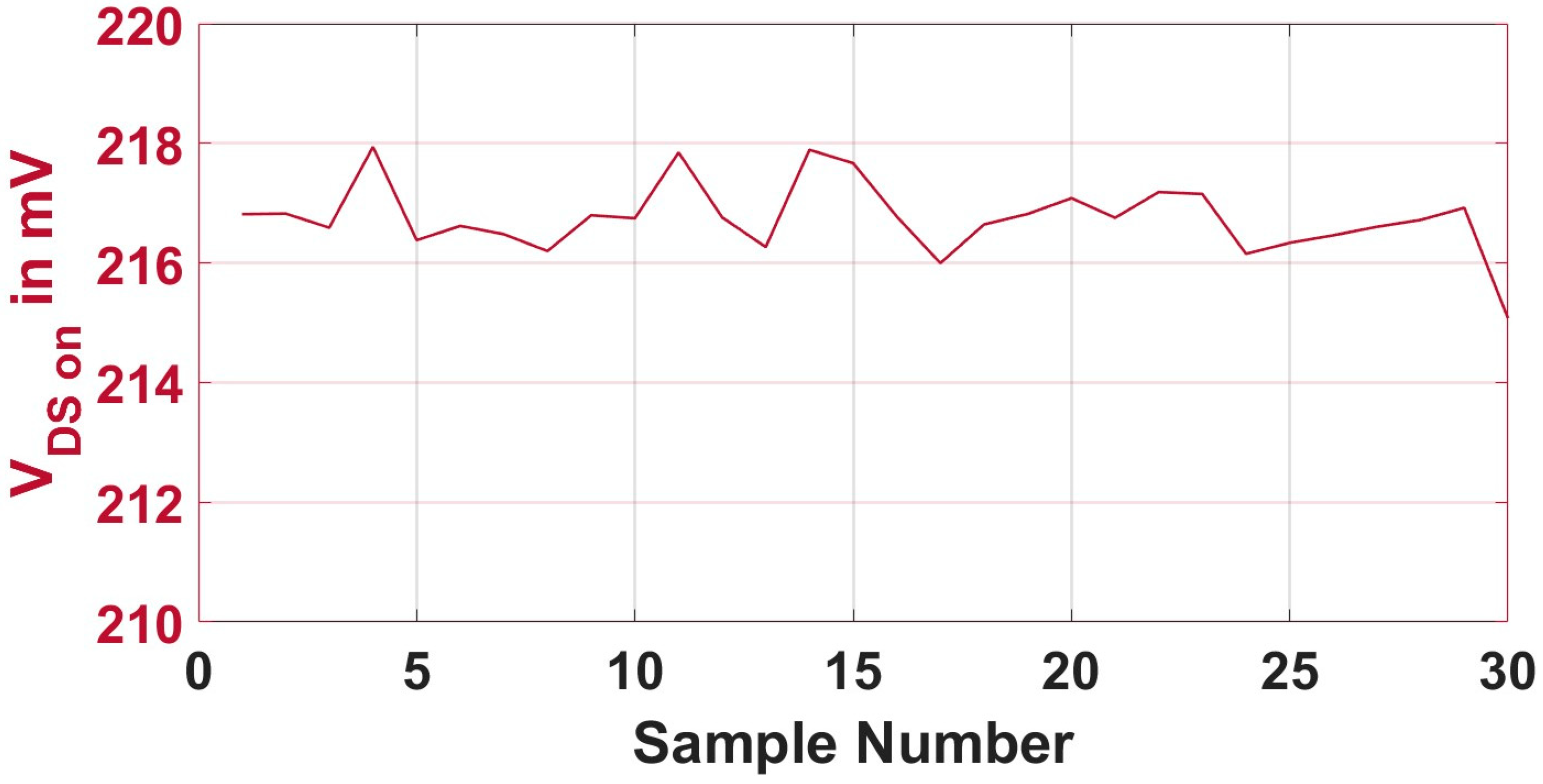

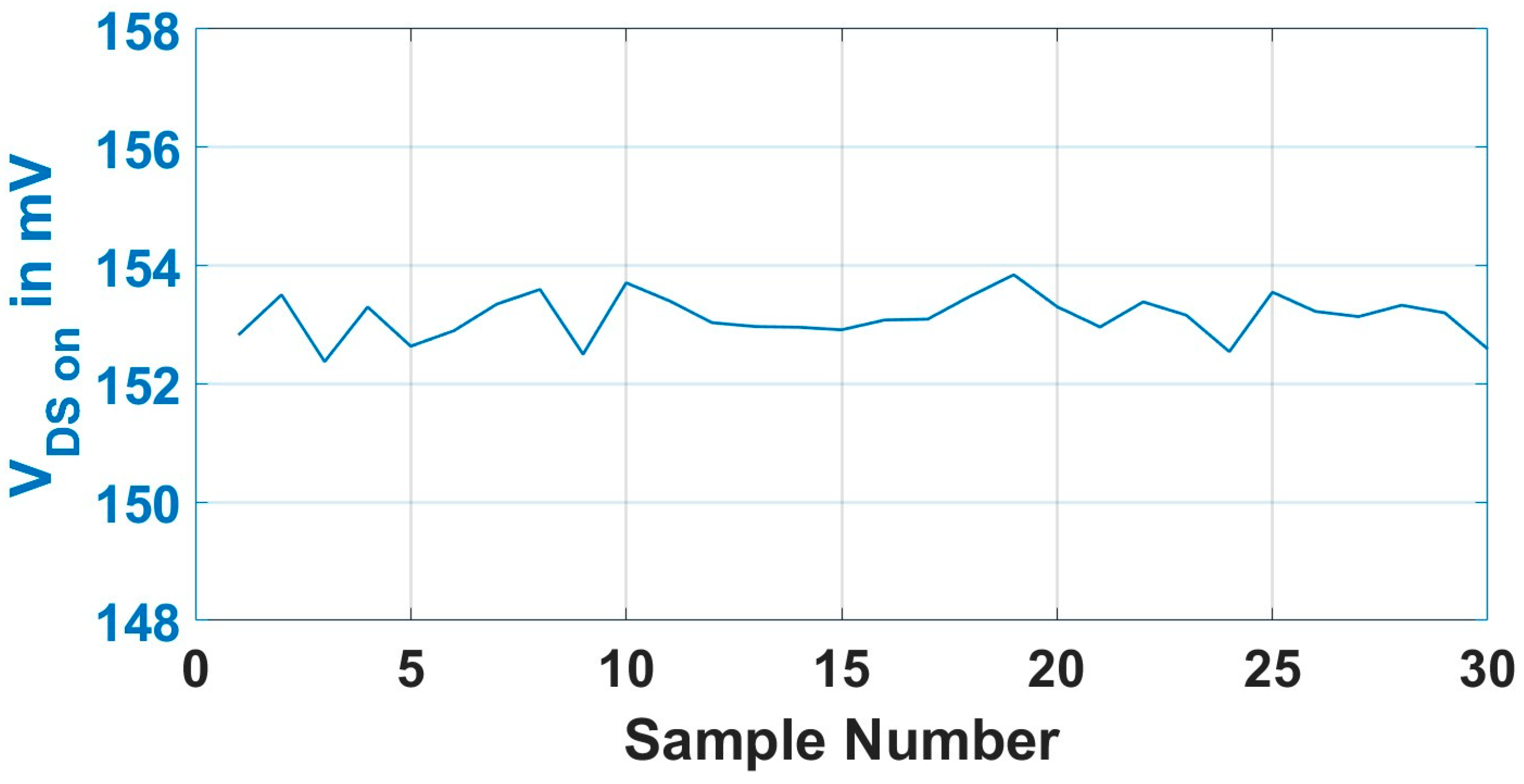

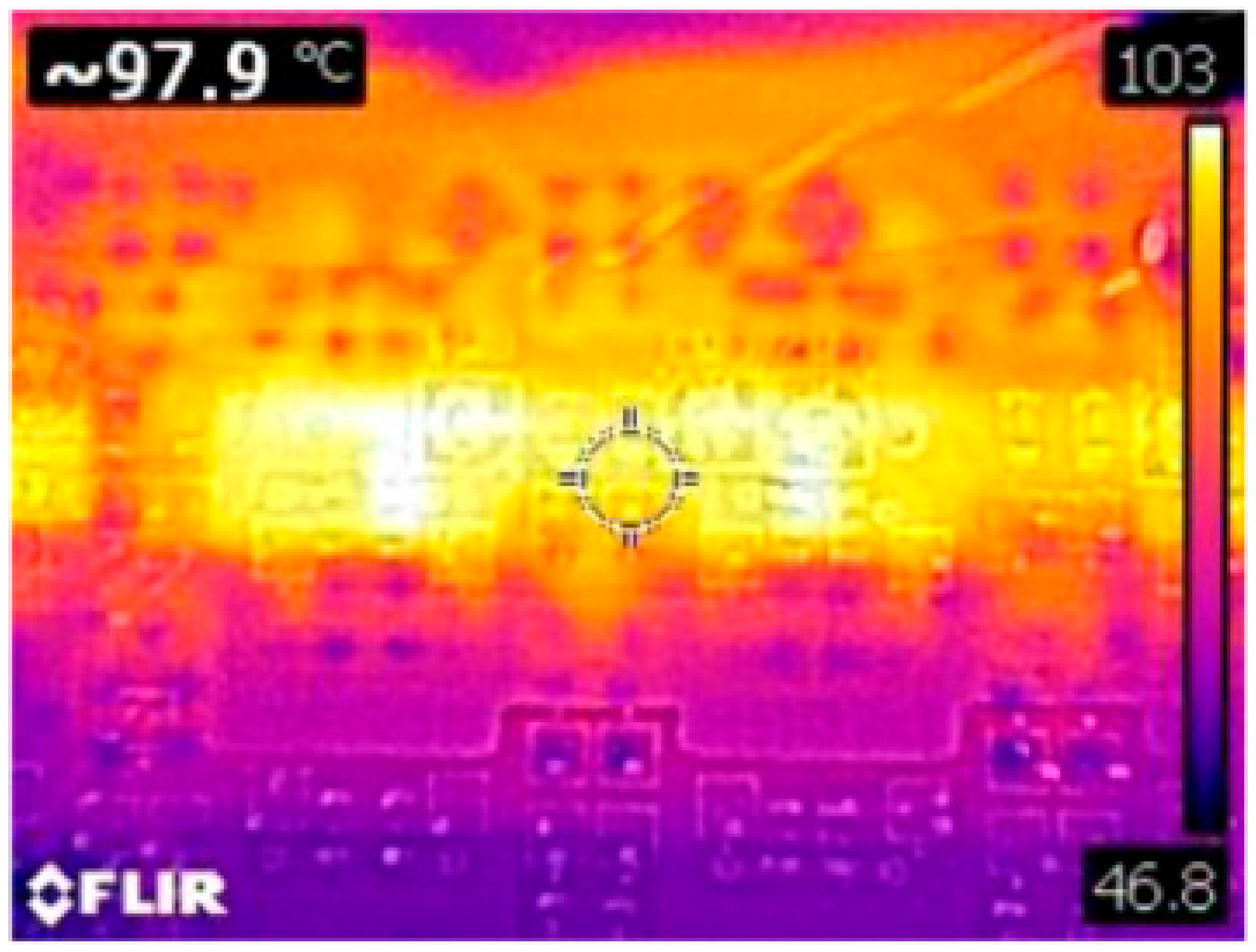

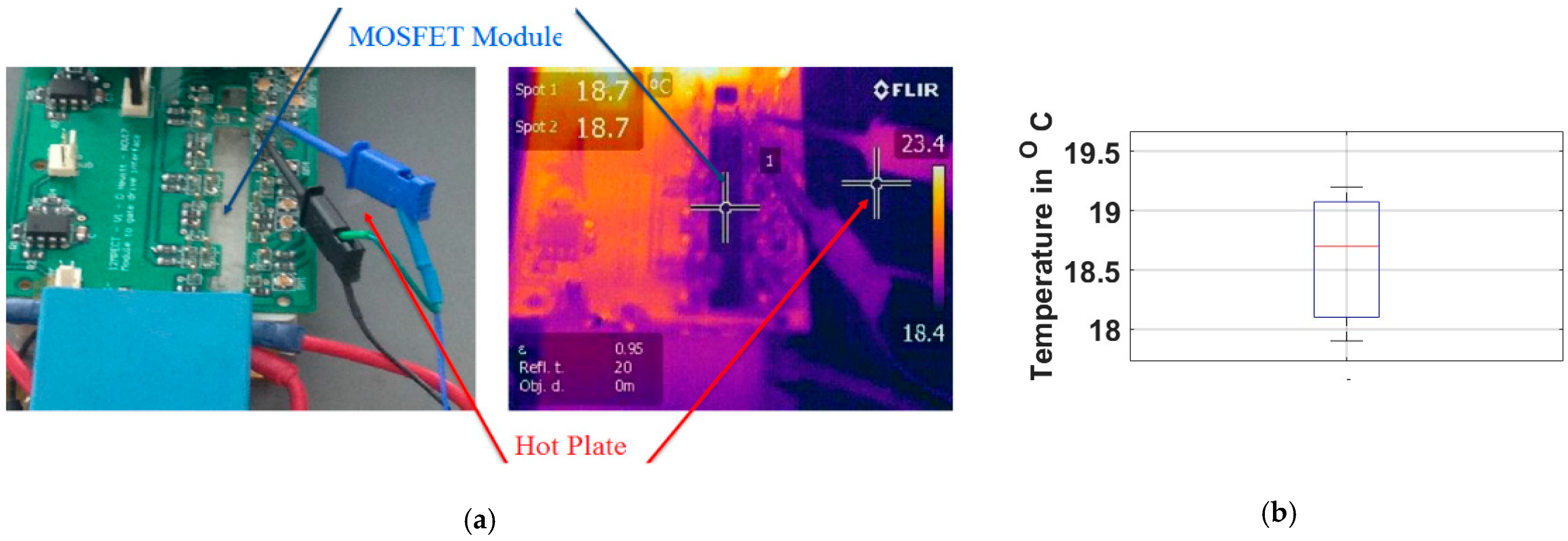

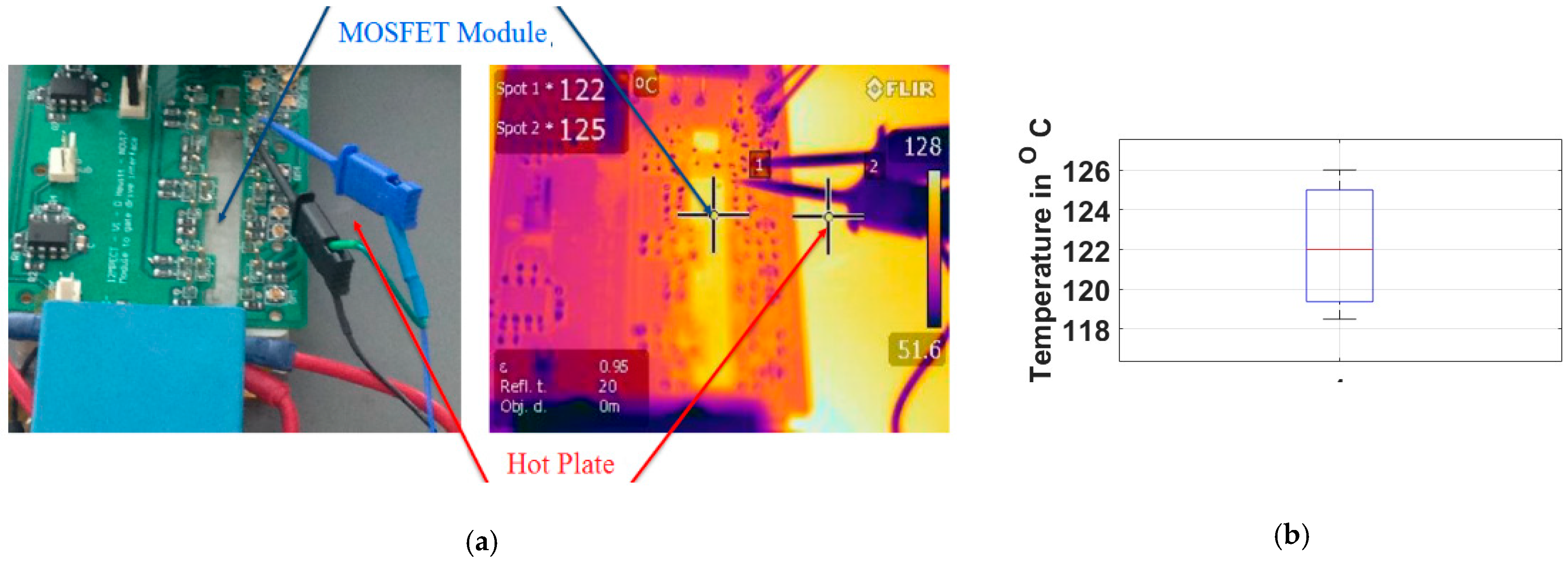

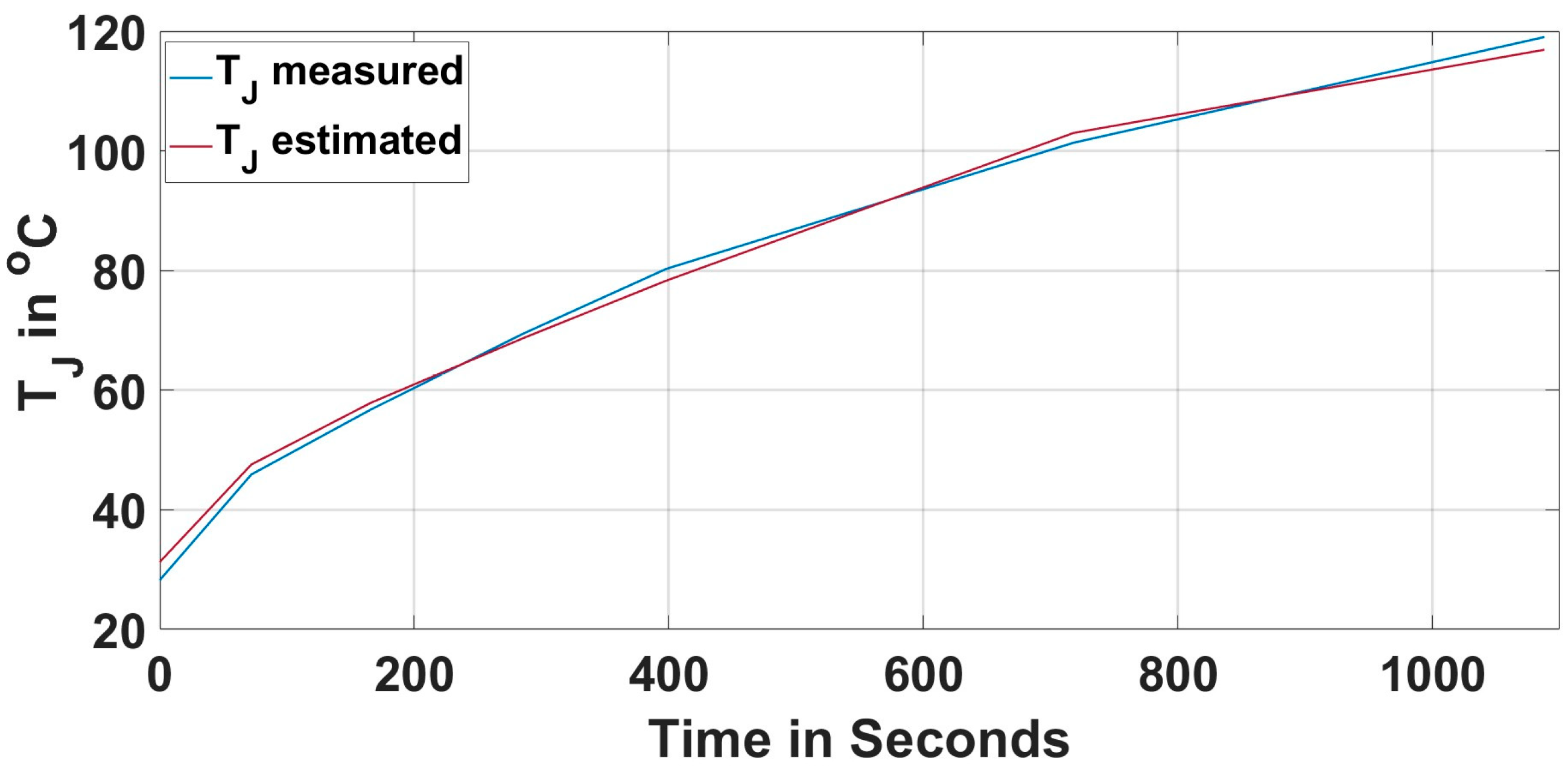

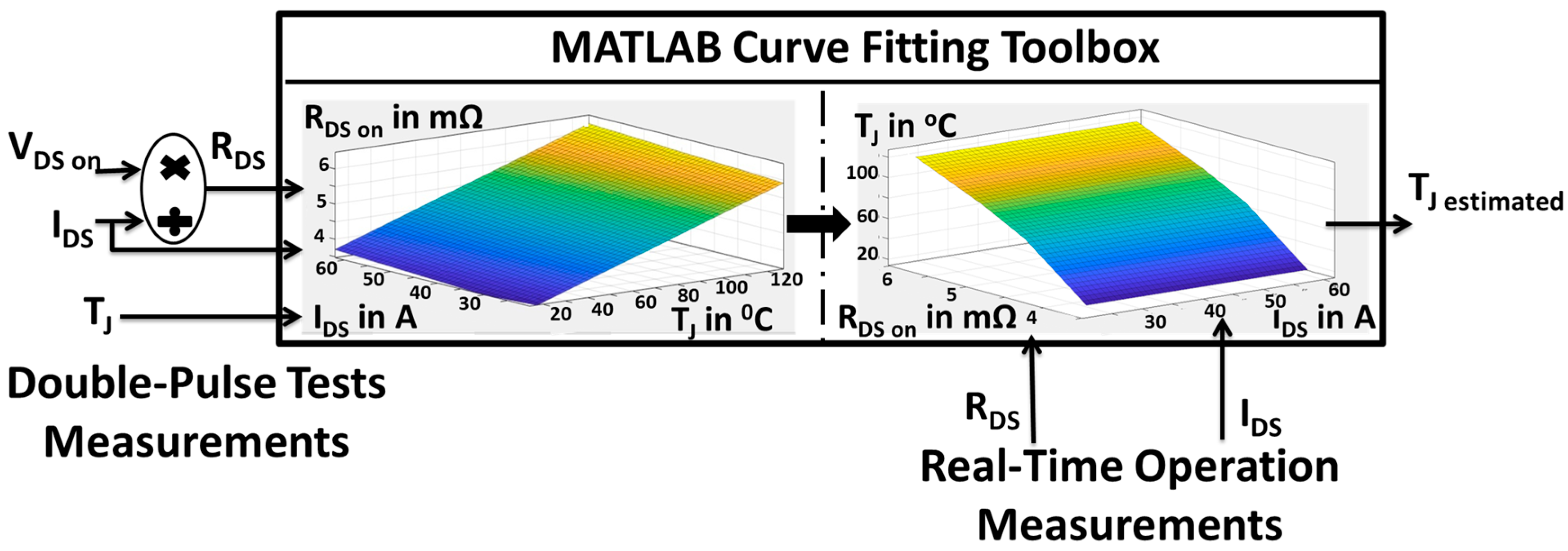

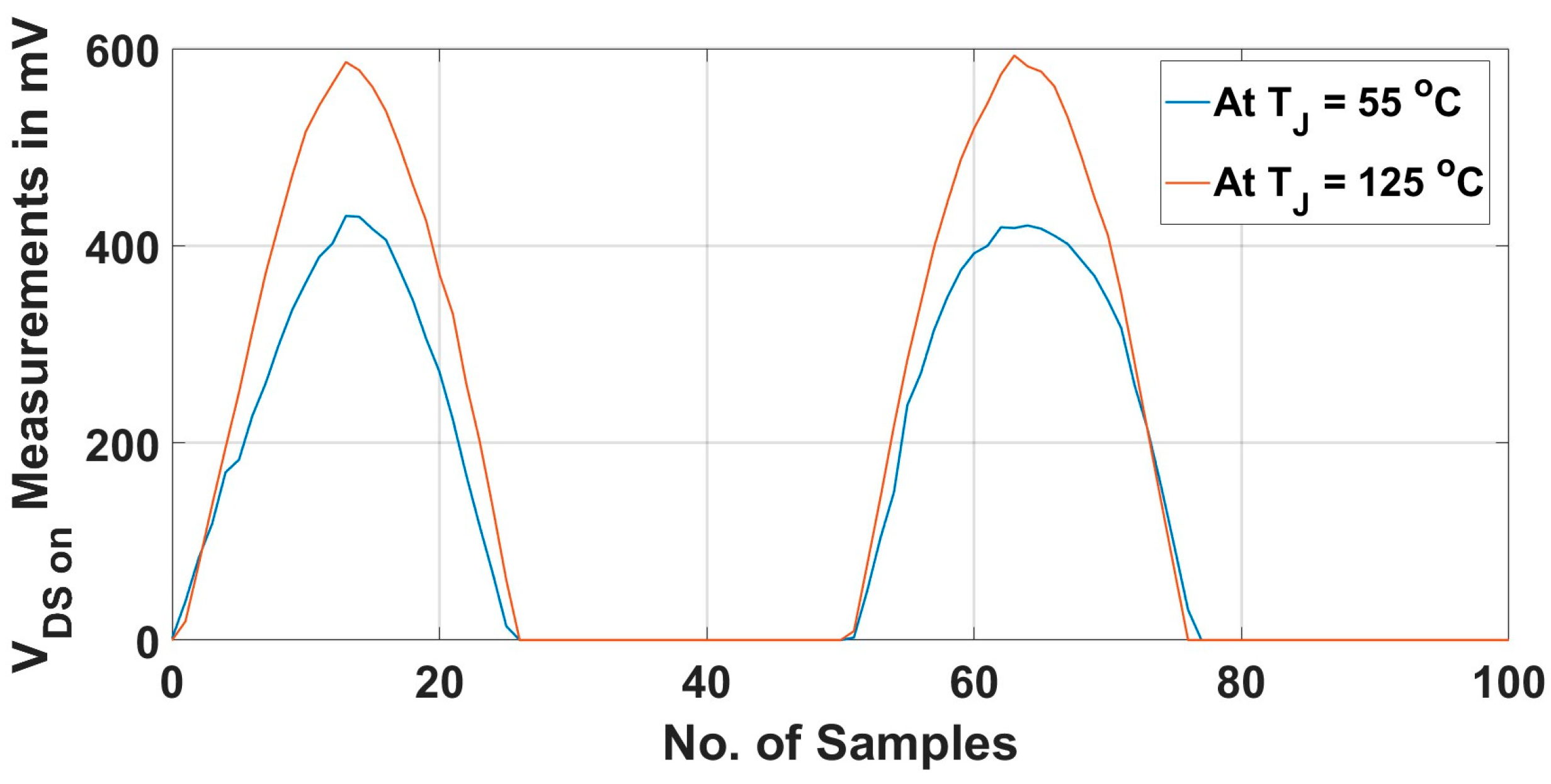

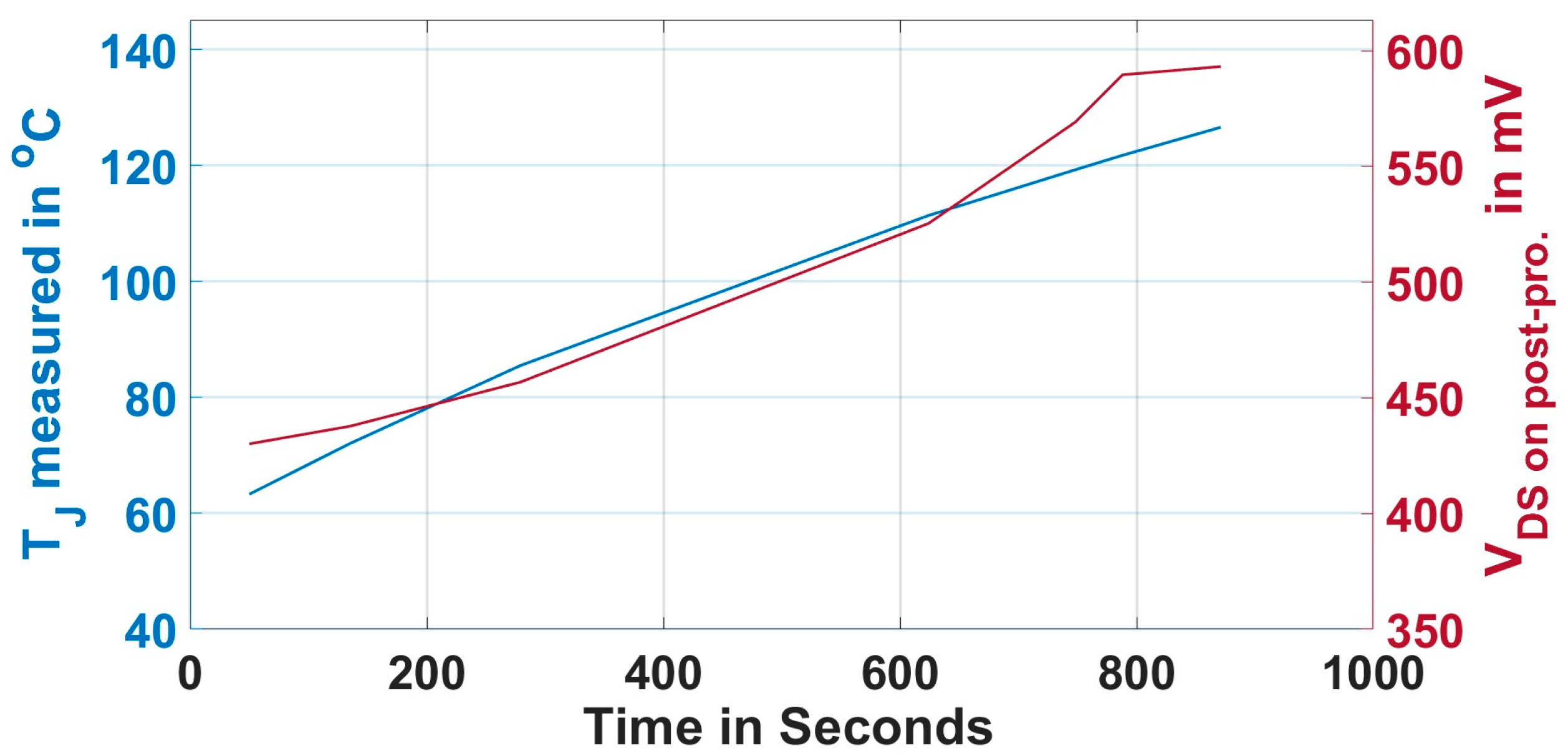

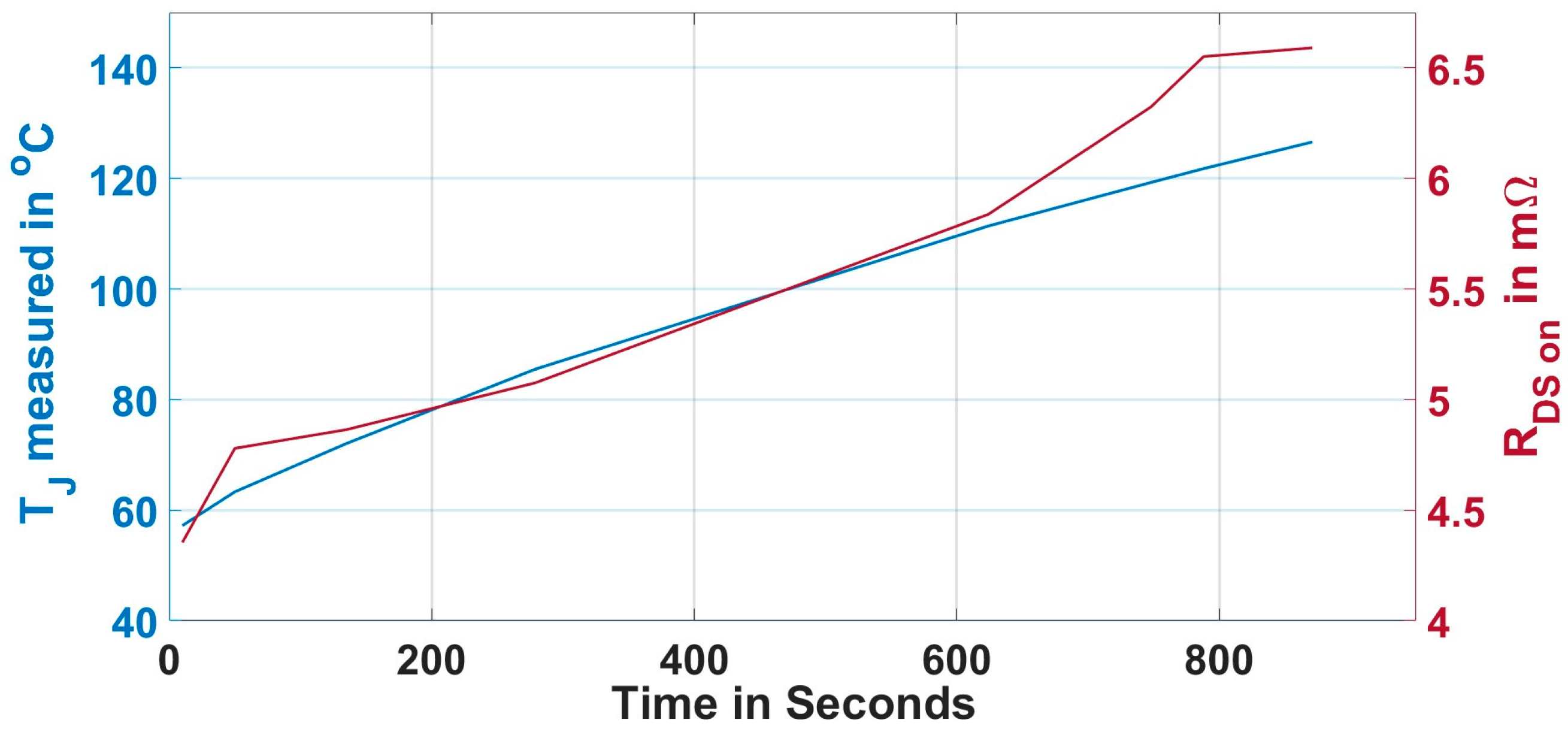

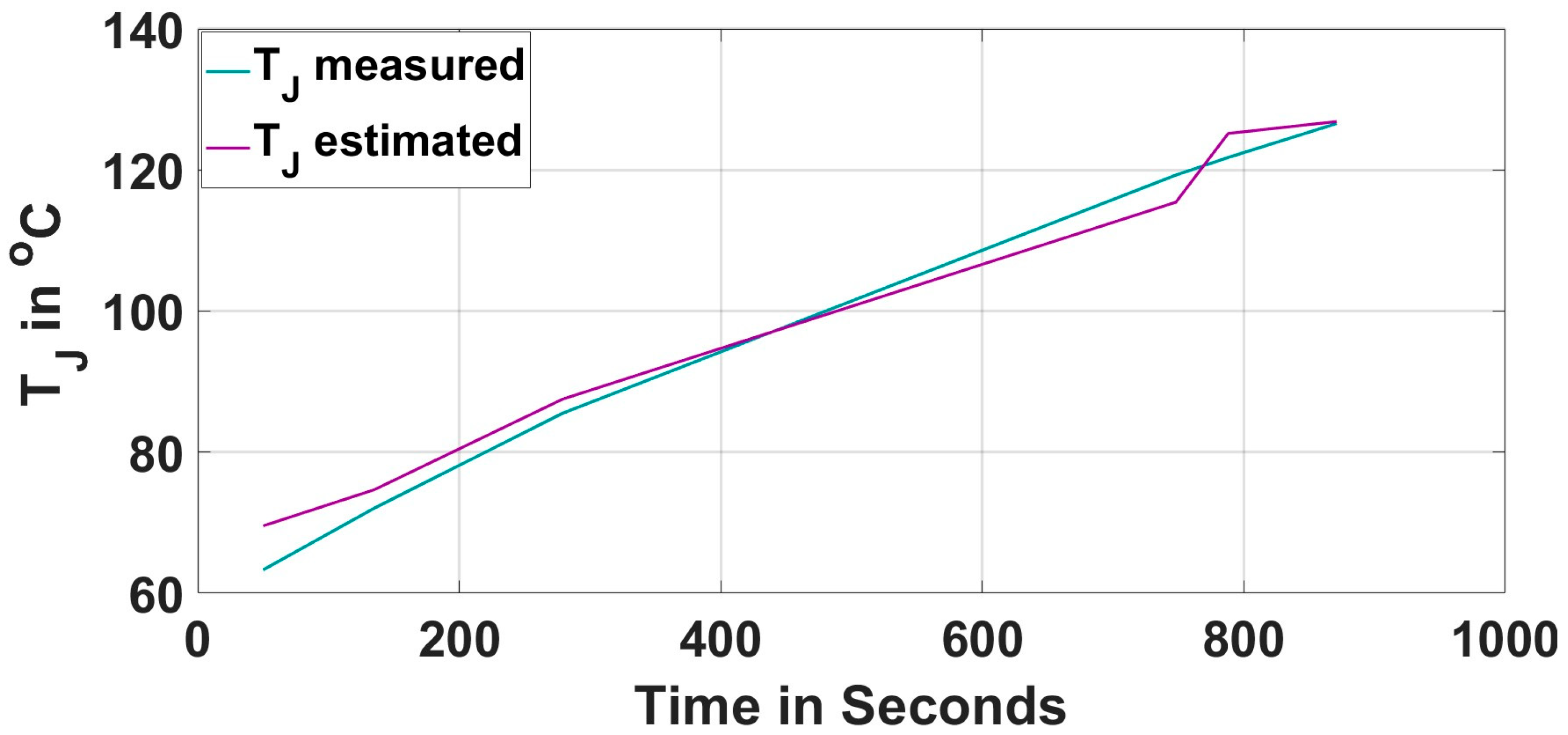

5.2. On-Line Tj Estimation Based on the VDSon Measurements

5.3. Comparisons Between the TSEPs Under Study

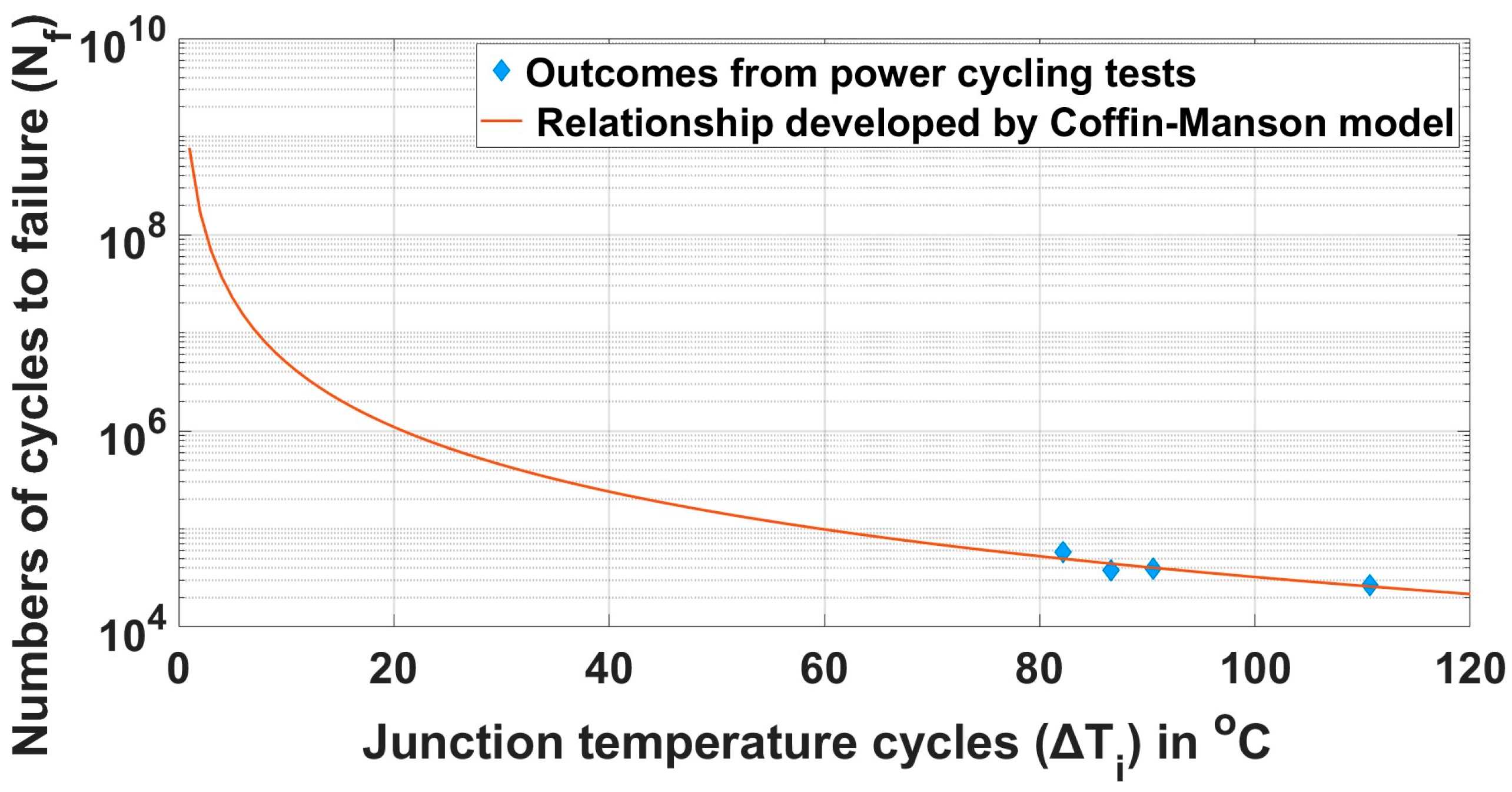

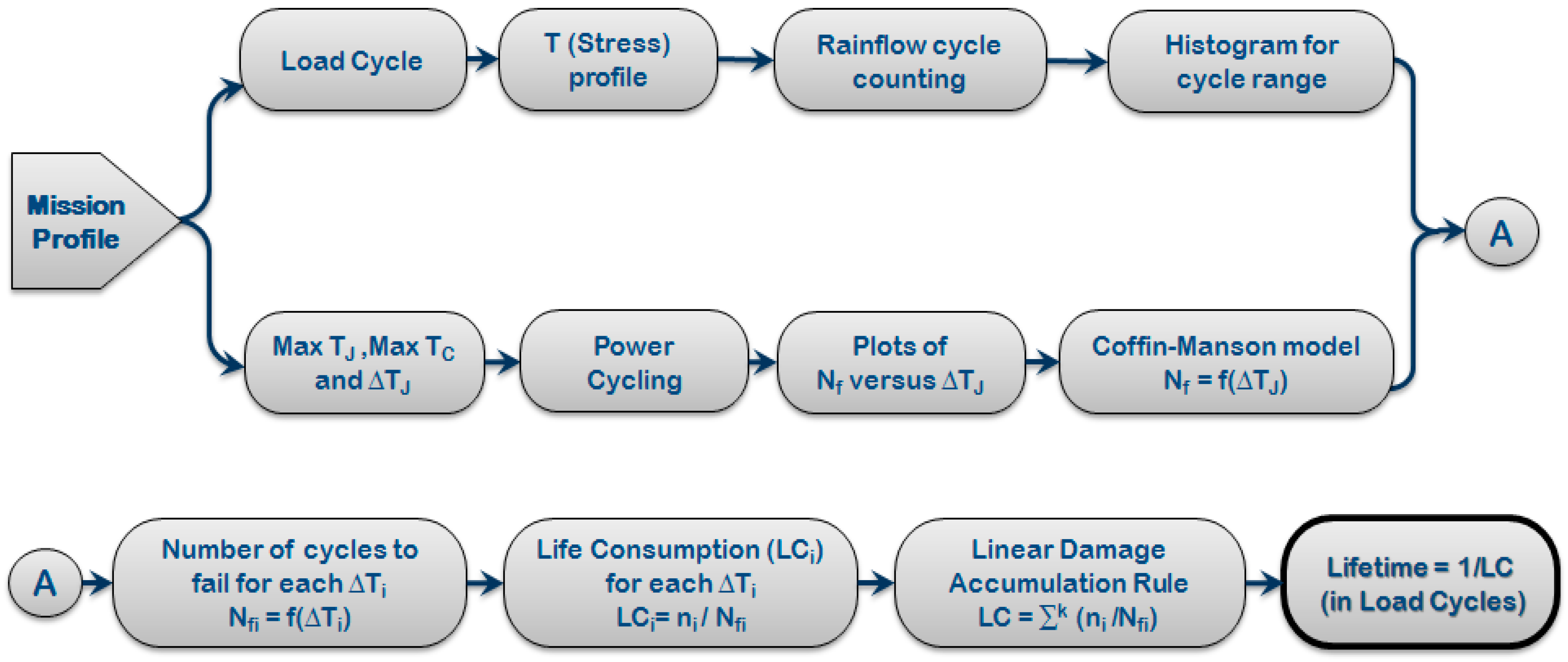

6. Reliability Modelling and Lifetime Prediction

7. Influence of the Aging of the SIC MOSFETS on the Studied TSEPs

8. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Neeb, C.; Boettcher, L.; Conrad, M.; Doncker, R.W.D. Innovative and reliable power modules: A future trend and evolution of technologies. IEEE Ind. Electron. Mag. 2014, 8, 6–16. [Google Scholar] [CrossRef]

- O’Donnell, S.; Debauche, J.L.; Wheeler, P.; Castellazzi, A. Silicon carbide MOSFETs in more electric aircraft power converters: The performance and reliability benefits over silicon IGBTs for a specified flight mission profile. In Proceedings of the EPE’16 ECCE Europe, Karlsruhe, Germany, 5–9 September 2016; pp. 1–10. [Google Scholar]

- Oh, H.; Han, B.; McCluskey, P.; Han, C.; Youn, B.D. Physics-of-failure, condition monitoring, and prognostics of insulated gate bipolar transistor modules: A review. IEEE Trans. Power Electron. 2015, 30, 2413–2426. [Google Scholar] [CrossRef]

- Wang, H.; Liserre, M.; Blaabjerg, F. Toward reliable power electronics. IEEE Ind. Electron. Mag. 2013, 7, 17–26. [Google Scholar] [CrossRef]

- Ciappa, M. Selected failure mechanisms of modern power modules. Microelectron. Rel. 2002, 42, 653–667. [Google Scholar] [CrossRef]

- Avenas, Y.; Dupont, L.; Baker, N.; Zara, H.; Barruel, F. Condition monitoring, a decade of proposed techniques. IEEE Ind. Electron. Mag. 2015, 9, 22–36. [Google Scholar] [CrossRef]

- Xiong, Y.; Cheng, X.; Shen, Z.J.; Mi, C.; Wu, H.; Garg, V.K. Prognostic and warning system for power-electronic modules in electric, hybrid electric, and fuel-cell vehicles. IEEE Trans. Ind. Electron. 2008, 55, 2268–2276. [Google Scholar] [CrossRef]

- Yang, S.; Xiang, D.; Bryant, A.; Mawby, P.; Ran, L.; Tavner, P. Condition monitoring for device reliability in power electronic converters: A review. IEEE Trans. Power Electron. 2010, 25, 2734–2752. [Google Scholar] [CrossRef]

- Avenas, Y.; Dupont, L.; Khatir, Z. Temperature measurement of power semiconductor devices by thermo-sensitive electrical parameters—A review. IEEE Trans. Power Electron. 2012, 27, 3081–3092. [Google Scholar] [CrossRef]

- Blackburn, D.-L. Temperature measurements of semiconductor devices—A review. In Proceedings of the 20th Annual Semiconductor Thermal Measurement and Management Symposium (SEMI-THERM), San Jose, CA, USA, 11 March 2004; pp. 70–80. [Google Scholar]

- Li, C.; Luo, H.; Li, W.; Li, C.; Yang, H.; He, X. Online junction temperature extraction of sic power mosfets with temperature sensitive optic parameter (TSOP) approach. IEEE Trans. Power Electron. 2019, 34, 10143–10152. [Google Scholar] [CrossRef]

- Furbock, C.; Thalhammer, R.; Litzenberger, M.; Seliger, N.; Pogany, D.; Gornik, E.; Wachutka, G. A differential backside laserprobing technique for the investigation of the lateral temperature distribution in power devices. In Proceedings of the International Symposium on Power Semiconductor Devices and ICs (ISPSD), Toronto, ON, Canada, 26–28 May 1999; pp. 193–196. [Google Scholar]

- Werber, D.; Wachutka, G. Interpretation of laser absorption measurements on 4 H-SiC bipolar diodes by numerical simulation. In Proceedings of the International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Hakone, Japan, 9–11 September 2008; pp. 89–92. [Google Scholar]

- Zarebski, J.; Gorecki, K. The electrothermal large-signal model of powerMOS transistors for SPICE. IEEE Trans. Power Electron. 2010, 25, 1265–1274. [Google Scholar] [CrossRef]

- Avenas, Y.; Dupont, L. Comparison of junction temperature evaluations in a power IGBTs module using an IR camera and three thermosensitive electrical parameters. In Proceedings of the 2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 5–9 February 2012. [Google Scholar]

- Brekel, W.; Duetemeyer, T.; Schilling, O. Time resolved in situ Tvj measurements of 6.5 kV IGBTs during inverter operation. In Proceedings of the Power Conversion Intelligent Motion Conference (PCIM Europe), Nuremberg, Germany, 12–14 May 2009; pp. 806–813. [Google Scholar]

- Chen, H.; Ji, B.; Pickert, V.; Cao, W. Real-time temperature estimation for power MOSFETs considering thermal aging effects. IEEE Trans. Device Mater. Rel. 2014, 14, 220–228. [Google Scholar] [CrossRef]

- Ccoa, J.A.B.; Strauss, B.; Mitic, G.; Lindemann, A. Investigation of temperature sensitive electrical parameters for power semiconductors (IGBT) in real-time applications. In Proceedings of the Power Conversion Intelligent Motion Conference (PCIM Europe), Nuremberg, Germany, 20–22 May 2014; pp. 1–9. [Google Scholar]

- Koenig, A.; Plum, T.; Fidler, P.; Doncker, R.W.D. On-line junction temperature measurement of CoolMOS devices. In Proceedings of the 2007 7th International Conference on Power Electronics and Drive Systems (PEDS), Bangkok, Thailand, 27–30 November 2007; pp. 90–95. [Google Scholar]

- Bęczkowski, S.; Ghimre, P.; Vega, A.R.D.; Munk-Nielsen, S.; Rannestad, B.; Thogersen, P. Online Vce measurement method for wearout monitoring of high power IGBT modules. In Proceedings of the 2013 15th European Conference on Power Electronics and Applications, Lille, France, 2–6 September 2013; pp. 1–7. [Google Scholar]

- Perpina, X.; Serviere, J.F.; Saiz, J.; Barlini, D.; Mermet-Guyennet, M.; Millan, J. Temperature measurement on series resistance and devices in power packs based on on-state voltage drop monitoring at high current. Microelectron. Rel. 2006, 46, 1834–1839. [Google Scholar] [CrossRef]

- Baker, N.; Munk-Nielsen, S.; Iannuzzo, F. Online junction temperature measurement via internal gate resistance during turn-on. In Proceedings of the 2014 16th European Conference on Power Electronics and Applications, Lappeenranta, Finland, 26–28 August 2014; pp. 1–10. [Google Scholar] [CrossRef]

- Baker, N.; Munk-Nielsen, S.; Iannuzzo, F.; Liserre, M. IGBT junction temperature measurement via peak gate current. IEEE Trans. Power Electron. 2016, 31, 3784–3793. [Google Scholar]

- Griffo, A.; Wang, J.; Colombage, K.; Kamel, T. Real-time measurement of temperature sensitive electrical parameters in sic power MOSFETs. IEEE Trans. Ind. Electron. 2018, 65, 2663–2671. [Google Scholar] [CrossRef]

- Jiang, X.; Jiang, X.; Wang, J.; Yu, H.; Chen, J.; Zeng, Z.; Yang, X.; Shen, Z.J. Online Junction Temperature Measurement for SiC MOSFET Based on Dynamic Threshold Voltage Extraction. IEEE Trans. Power Electron. 2021, 36, 3757–3768. [Google Scholar] [CrossRef]

- Stella, F.; Pellegrino, G.; Armando, E.; Daprà, D. Online junction temperature estimation of SIC power MOSFTES through on-state voltage mapping. IEEE Trans. Ind. Appl. 2018, 54, 3453–3462. [Google Scholar] [CrossRef]

- Wang, X.; Zou, M.; Gong, J.; Wang, Y.; Zeng, Z. Junction Temperature Monitoring of GaN HEMT by Using On-Resistance with Voltage Clamp and Current Shunt. In Proceedings of the 2025 IEEE Applied Power Electronics Conference and Exposition (APEC), Atlanta, GA, USA, 16–20 March 2025; pp. 219–224. [Google Scholar]

- Niu, H.; Lorenz, R.D. Real-time junction temperature sensing for silicon carbide MOSFET with different gate drive topologies and different operating conditions. IEEE Trans. Power Electron. 2018, 33, 3424–3440. [Google Scholar] [CrossRef]

- Yang, F.; Pu, S.; Xu, C.; Akin, B. Turn-on delay based real-time junction temperature measurement for SiC MOSFETs with aging compensation. IEEE Trans. Power Electron. 2021, 36, 1280–1294. [Google Scholar] [CrossRef]

- Peftitsis, D.; Baburske, R.; Rabkowski, J.; Lutz, J.; Tolstoy, G.; Nee, H.-P. Challenges regarding parallel connection of SiC JFETS. IEEE Trans. Power Eletron. 2013, 28, 4526. [Google Scholar] [CrossRef]

- Hu, J.; Alatise, O.; González, J.A.O.; Bonyadi, R.; Ran, L.; Mawby, P.A. The effect of electrothermal nonuniformities on parallel connected SIC power devices under unclamped and clamped inductive switching. IEEE Trans. Power Electron. 2016, 31, 4526–4535. [Google Scholar] [CrossRef]

- Tiwari, S.; Rabiei, A.; Shrestha, P.; Midtgård, O.-M.; Undeland, T.M.; Lund, R. Design considerations and laboratory testing of power circuits for parallel operation of silicon carbide MOSFETs. In Proceedings of the 2015 (EPE’15 ECCE-Europe), Geneva, Switzerland, 8–10 September 2015; pp. 1–10. [Google Scholar]

- Sadik, D.; Colmenares, J.; Peftitsis, D.; Lim, J.; Rabkowski, J.; Nee, H. Experimental investigations of static and transient current sharing of parallel-connected silicon carbide MOSFETs. In Proceedings of the 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 2–6 September 2013; pp. 1–10. [Google Scholar]

- Aichinger, T.; Rescher, G.; Pobegen, G. Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs. Microelectron. Reliab. 2018, 80, 68–78. [Google Scholar] [CrossRef]

- Peters, D.; Aichinger, T.; Basler, T.; Rescher, G.; Puschkarsky, K.; Reisinger, H. Investigation of threshold voltage stability of SiC MOSFETs. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 40–43. [Google Scholar]

- Jooq, M.K.Q.; Miralaei, M.; Ramezani, A. Post-layout simulation of an ultra-low-power OTA using DTMOS input differential pair. Int. J. Electron. Lett. 2017, 6, 168–180. [Google Scholar] [CrossRef]

- Gonzalez, J.A.O.; Alatise, O. A Novel non-intrusive technique for BTI characterization in SiC MOSFETS. IEEE Trans. Power Electron. 2019, 34, 5737–5747. [Google Scholar] [CrossRef]

- Luo, H.; Chen, Y.; Sun, P.; Li, W.; He, X. Junction temperature extraction approach with turn-off delay time for high-voltage high-power IGBT modules. IEEE Trans. Power Electron. 2016, 31, 5122–5132. [Google Scholar] [CrossRef]

- Dodge, J. Eliminating Parasitic Oscillation Between Parallel MOSFETs; Advanced Power Technology Application Note APT-0402; Advanced Power Technology: Lafayette, IN, USA, 2004. [Google Scholar]

- Joffe, E.B.; Lock, K.S. Grounds for Grounding: A Circuit to System Handbook; Wiley-IEEE: Hoboken, NJ, USA, 2010; Chapter 9. [Google Scholar]

- Wei, R.; Song, S.; Yang, K.; Cui, Y.; Peng, Y.; Chen, X.; Hu, X.; Xu, X. Thermal conductivity of 4H-SiC single crystals. J. Appl. Phys. 2013, 113, 053503. [Google Scholar] [CrossRef]

- Chen, M.; Wang, H.; Pan, D.; Wang, X.; Blaabjerg, F. Thermal characterization of silicon carbide MOSFET module suitable for high-temperature computationally efficient thermal-profile prediction. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 3947–3958. [Google Scholar] [CrossRef]

- Ordonez-Miranda, J.; Hermens, M.; Nikitin, I.; Kouznetsova, V.G.; van der Sluis, O.; Ras, M.A.; Reparaz, J.; Wagner, M.; Sledzinska, M.; Gomis-Bresco, J.; et al. Measurement and modeling of the effective thermal conductivity of sintered silver pastes. Int. J. Therm. Sci. 2016, 108, 185–194. [Google Scholar] [CrossRef]

- CREE. Silicon Carbide Power MOSFET C2MTM MOSFET Technology N-Channel Enhancement Mode C2M0025120D Datasheet. Rev. B, October 2015. Available online: https://docs.rs-online.com/3ef6/0900766b8149fd3d.pdf (accessed on 1 July 2025).

- Coffin, L.F., Jr. A study of the effects of cyclic thermal stresses on a ductile metal. Trans. Am. Soc. Mech. Eng. 1954, 76, 931–949. [Google Scholar] [CrossRef]

- Musallam, M.; Yin, C.; Bailey, C.; Johnson, M. Mission profile-based reliability design and real-time life consumption estimation in power electronics. IEEE Trans. Power Electron. 2015, 30, 2601–2613. [Google Scholar] [CrossRef]

- Ni, Z.; Lyu, X.; Yadav, O.P.; Singh, B.N.; Zheng, S.; Cao, D. Overview of real-time lifetime prediction and extension for SiC power converters. IEEE Trans. Power Electron. 2020, 35, 7765–7794. [Google Scholar] [CrossRef]

- Ugur, E.; Yang, F.; Pu, S.; Zhao, S.; Akin, B. Degradation assessment and precursor identification for SiC MOSFETs under high temp cycling. IEEE Trans. Ind. Appl. 2019, 55, 2858–2867. [Google Scholar] [CrossRef]

- Choi, U.; Blaabjerg, F.; Jørgensen, S. Power cycling test methods for reliability assessment of power device modules in respect to temperature stress. IEEE Trans. Power Electron. 2017, 33, 2531–2551. [Google Scholar] [CrossRef]

| Approach | Comments | Method | Reference | |

|---|---|---|---|---|

| Optical | Requires the chip to be optically connected to the detection system and therefore the protective dielectric gel has to be removed | Electroluminescence of MOSFET body diode | [11] | |

| Laser deflection | [12,13] | |||

| Infrared radiation | [14,15] | |||

| Physical contact | Requires significant alterations to module packaging and dielectric gel to place the device as close as possible to the chip | Thermo-sensitive devices such as thermistors or thermocouples | [16] | |

| TSEP | Provides a more practical solution for temperature monitoring since they rely on the thermal dependence of the electrical properties of the semiconductor devices to determine the Tj without modification to the module itself | Threshold voltage (Vth) |

| [17,18] |

| On-state Voltage (VDSon) |

| [19,20,21] | ||

| Internal gate resistance (Rg) |

| [22,23] | ||

| Paper | Features | Drawbacks |

|---|---|---|

| [24] | Quantifies the characteristics of some TSEP including Vth, VDSon, the turn-on transient characteristic (di/dt) | The quantification procedures took place only during the double-pulse test process and have not been verified in real-world operation scenarios |

| [25] | On-line junction temperature measurement for SiC MOSFET based on Vth extraction | The proposed Vth measurement is experimentally evaluated only through the double-pulse tests, not during real-world operation scenarios as well |

| [26] | Provides on-line junction temperature estimation using VDSon | It required a thermistor embedded in the module to measure the DBC temperature along with a shunt resistor in series with the switch to measure its current |

| [27] | Junction temperature monitoring using on-resistance with voltage clamp and current shunt | It required high bandwidth shunt approach integrated in the PCB board to detect the drain current |

| [28] | Utilizes the gate drive current (ig) during turn-on transients to estimate the Tj | The proposed approaches have high sensing offset 9–12 °C for Tj. In addition, they cannot directly regulate ig during the turn-on transient |

| [29] | Real-time junction temperature measurement for SiC MOSFETs using turn-on delay approach | It required sophisticated adjustable gate resistance circuit along with high resolution capture device to ensure proper results |

| Components | Description/Values |

|---|---|

| MOSFET module (M1) | SiC MOSFET Module under study |

| MOSFET module (M2 and M3) | CREE CAS300M12BM2 |

| DC Link Capacitor (C1) | 600 µF Film capacitor |

| Module mounted Capacitors (C2, C3, C4) | 2.2 µF Polypropylene |

| Load Inductor (L) | 3 Phase 320 µH Inductor |

| Current sensors | LEM LF 205-S |

| Gate Driver Boards | Prodrive PT62SCMD12 |

| Vth | VDSon | |

|---|---|---|

| Requirements |

|

|

| Dependents | Temperature | Temperature and IDS current |

| Performance |

|

|

| Estimated error | Maximum divergence of 2~3 °C between the estimated and the measured Tj | Maximum divergence of 5~6 °C between the estimated and the measured Tj |

| ∆Ti | 5.2 | 22 | 55.6 | 80.8 |

| ni | 3 | 1 | 2.5 | 0.5 |

| Nfi | 2.08 × 107 | 8.88 × 105 | 1.17 × 105 | 5.16 × 104 |

| LCi | 1.44 × 10−7 | 1.13 × 10−6 | 2.14 × 10−5 | 9.70 × 10−6 |

| LCtotal | 3.2373 × 10−5 | |||

| Lifetime | 30,890 (load cycles) ≈ 70,275 h | |||

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kamel, T.; Olagunju, O.; Johnson, T. Real-Time Temperature Estimation of the Machine Drive SiC Modules Consisting of Parallel Chips per Switch for Reliability Modelling and Lifetime Prediction. Machines 2025, 13, 689. https://doi.org/10.3390/machines13080689

Kamel T, Olagunju O, Johnson T. Real-Time Temperature Estimation of the Machine Drive SiC Modules Consisting of Parallel Chips per Switch for Reliability Modelling and Lifetime Prediction. Machines. 2025; 13(8):689. https://doi.org/10.3390/machines13080689

Chicago/Turabian StyleKamel, Tamer, Olamide Olagunju, and Temitope Johnson. 2025. "Real-Time Temperature Estimation of the Machine Drive SiC Modules Consisting of Parallel Chips per Switch for Reliability Modelling and Lifetime Prediction" Machines 13, no. 8: 689. https://doi.org/10.3390/machines13080689

APA StyleKamel, T., Olagunju, O., & Johnson, T. (2025). Real-Time Temperature Estimation of the Machine Drive SiC Modules Consisting of Parallel Chips per Switch for Reliability Modelling and Lifetime Prediction. Machines, 13(8), 689. https://doi.org/10.3390/machines13080689