1. Introduction

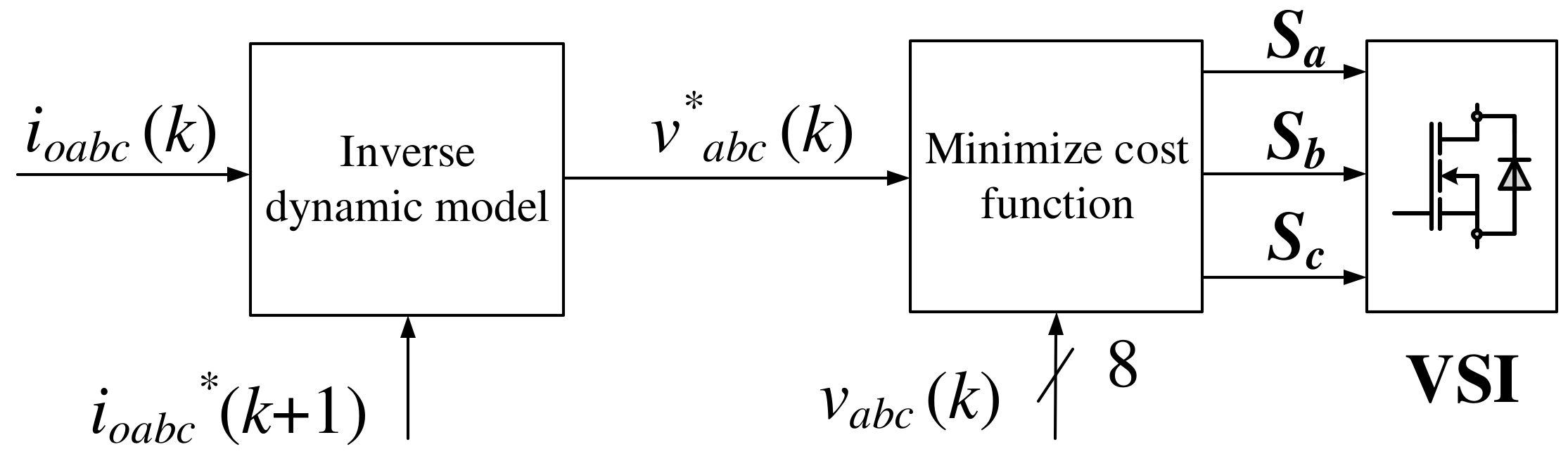

The increasing number of power electronics applications in industry, consumer electronics, and transportation leads to an increasing importance of power converters for power systems. Due to the simplicity of their structure and their ability to handle the voltage by keeping the system stable, two-level three-phase dc/ac voltage source inverters (VSIs) are now extensively used in motor drives, active filters, unified power flow controllers in power systems, and uninterrupted power supplies to generate controllable frequency and ac voltage magnitudes [

1,

2,

3,

4]. The lifespan of a power converter is mainly based on the lifespan of power switches. Hence, it requires improving the lifespan of power switches to prolong the lifespan of a converter. The main reason for aging states or failure in power switches and capacitors is thermal stress [

5,

6]. It is widely recognized that thermal stress is a crucial factor in determining the lifespan of power devices. Thus, increasing a converter’s lifespan by relieving stressed power switches, which suffer excessive thermal stress, is necessary.

The most commonly used method to lower the junction temperature of power devices is switching frequency control [

7]. The switching frequency is a loss-dependent variable that mainly affects the switching losses of power semiconductor devices. Thus, the switching frequency is usually used to adjust a converter’s junction temperature [

7]. In [

8,

9], for a two-level inverter used in an adjustable speed drive application, switching frequency reduction techniques based on junction temperature change have been presented. However, this will introduce a lot of calculations and depend on the parameter accuracy. The discontinuous pulse-width modulation (DPWM) [

10,

11,

12] is a widely used technique that works by clamping the converter’s output reference voltage to the upper rail or lower rail of a dc link during a defined period of time to prevent the corresponding power device from switching. Thus, the switching loss is reduced. The consequent mean value of junction temperature and its variance are also decreased as a result of the decreased power device loss during the clamping period. However, because of the switching loss reduction in both three-phase legs, the output current performance of the VSI is decreased with a higher total harmonic distortion (THD). The model predictive control (MPC) method, referred to as a class of digital control algorithms, uses the model of the system to predict the future behavior of a converter and thus select the optimal switching state to precisely operate the converter [

13,

14,

15,

16]. In [

17], a cost function is added through a linear low-pass filter to lower the power loss under the MPC strategy implementation. By excluding switching states that are predicted to have greater power losses, this filter helps reduce thermal stress. Nonlinear constraints, however, might have an impact on how accurate the linear filter is. Nonlinear restrictions could lead to the filter being mistaken and have a substantial impact on how the MPC problem is formulated. The author in [

18] introduces a predictive control technique based on preselecting the switching states to evenly distribute the power loss in three-phase legs as well as decrease the switching loss. The capability of MPC to simultaneously control multiple targets is one of its advantages. Along with other control objectives, like output currents, voltage, etc., an additional cost function is added to the traditional MPC method to decrease the number of switching transitions or the junction temperature of switching devices [

19,

20]. However, it can be difficult to adjust the weighting factor for every control objective in the cost function. Additionally, the output performance of the converter might be decreased due to the existence of multiple control objectives in a cost function.

It can be seen that previous studies mainly focused on uniformly reducing the switching loss of an entire converter without considering the different aging states among phase legs. In three-phase VSIs, the different aging states and predicted lifespans for each phase leg might be caused by unequal operating stress, switch failure, or switch replacement in the past. Furthermore, their manufacturing processes are considered a potential cause of the failure of semiconductor devices. Therefore, increasing a converter’s lifespan by relieving the most stressed phase leg or the leg that has aged the most, which suffers excessive thermal stress due to aging, is crucial. Hence, several per-phase techniques, which aim at reducing the thermal stress of the leg that has aged the most, are proposed. The strategy in [

21] alters the switching strategy to reduce the loss of a particular power switch in a three-level neutral-point-clamped converter by using redundant switching states. In [

22], the author proposed a PWM method using a hybrid offset voltage injection to decrease the switching loss in the most aged leg. However, due to using direct output currents as a condition to detect the clamping regions, this method is mainly effective under a unity-power-factor load. Meanwhile, the author in [

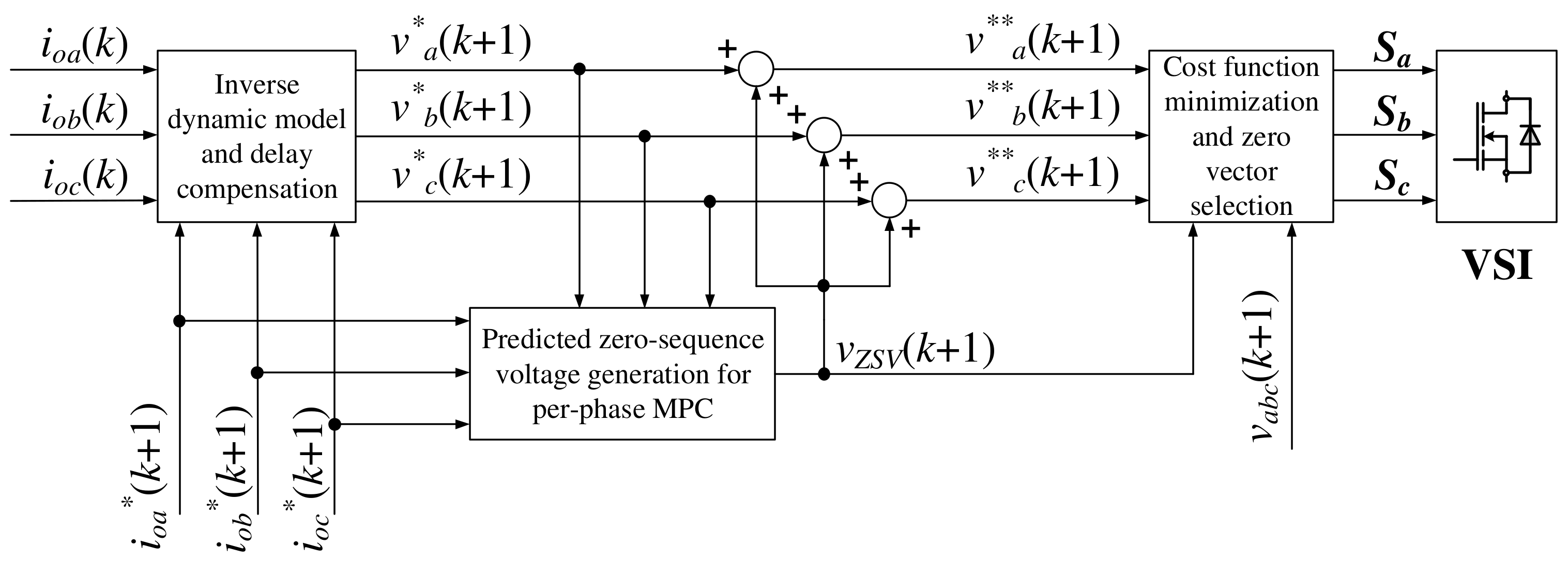

23] modified the DPWM1 technique to lower the switching loss in a particular phase leg of a voltage source rectifier. Regarding the MPC techniques, which will be evaluated in this study, the first considered technique is per-phase MPC with an offset voltage injection method, termed per-phase MPC1 [

24]. Unlike conventional MPC, the per-phase MPC1 technique employs modified predicted reference voltages to control the phase currents and reduce the switching loss in a specific phase leg. It achieves this by generating a predicted zero-sequence voltage (

ZSV) and introducing it to the predicted reference voltage of the targeted phase leg, effectively limiting that phase leg’s operation by clamping it to the upper or lower rails of a dc link. These clamping periods make the considered aged leg keep its switching state for a period of time. Per-phase MPC1 can generate a maximum clamping period of

in both the upper and lower rails of the dc link for the targeted aged leg. Regarding the remaining per-phase MPC method, a per-phase MPC technique with the preselection of a switching state [

25], termed per-phase MPC2, will be discussed. The approach of preselecting the switching state defines the clamping period of the leg that has aged the most and the related switching states from the available voltage vectors of the VSI based on the predicted reference voltages. By choosing the optimal switching state among the preselected voltage vectors by evaluating a predefined cost function, the switching frequency and power loss in the leg that has aged the most are lowered. The lifespan of the leg that has aged the most will rise due to a reduction in thermal stress, which will also increase the lifespan of the VSI. As for the per-phase MPC techniques, they require determining the leg that has aged the most. The diagnosis methods require an aging indicator to identify the current aging status of the power semiconductor devices. Aging indicator identification on power semiconductor devices has been carried out by performing accelerated aging experiments with the monitoring of selected parameters. Accelerated aging tests allow the effects of failure mechanisms to be analyzed and aging indicators to be identified. Various electrical aging indicators for IGBTs have been investigated and proposed in the literature, such as changes in the collector–emitter on-state voltage,

[

26,

27], the threshold voltage,

[

28,

29], and the temperature [

30,

31,

32]. However, the diagnosis method is outside of the scope of this study, so a detailed description is not included.

The objective of this paper is to discuss, evaluate, and compare the features and performance of VSIs controlled by two per-phase MPC schemes. Fundamental principles, operation concepts, and performance outcomes are employed to establish a comparison between two per-phase MPC approaches. From this comparison and evaluation, the better technique will be determined in terms of reducing the switching loss of a specific phase leg in a VSI to extend the corresponding lifespan. Additionally, the two per-phase MPC methods are compared by employing them in various settings in terms of the sampling frequency, output power, load condition, and parameter uncertainty. This helps tailor the selection of per-phase MPC methods based on the unique requirements and constraints of a particular situation or problem. These methods are conducted in both a simulation and an experiment to obtain comparable results. This study is structured as follows. The control concepts of the two per-phase MPC methods are reviewed after an overview of two-level three-phase VSIs. Then, the simulation and experiment outcomes are discussed for a comparison between the per-phase MPC1 and per-phase MPC2 approaches.

3. Performance Comparison

In this section, a performance comparison between the two per-phase MPC techniques is carried out in both a simulation and an experiment using the parameters listed in

Table 1. Furthermore, in both the control schemes, phase

is considered the leg that has aged the most.

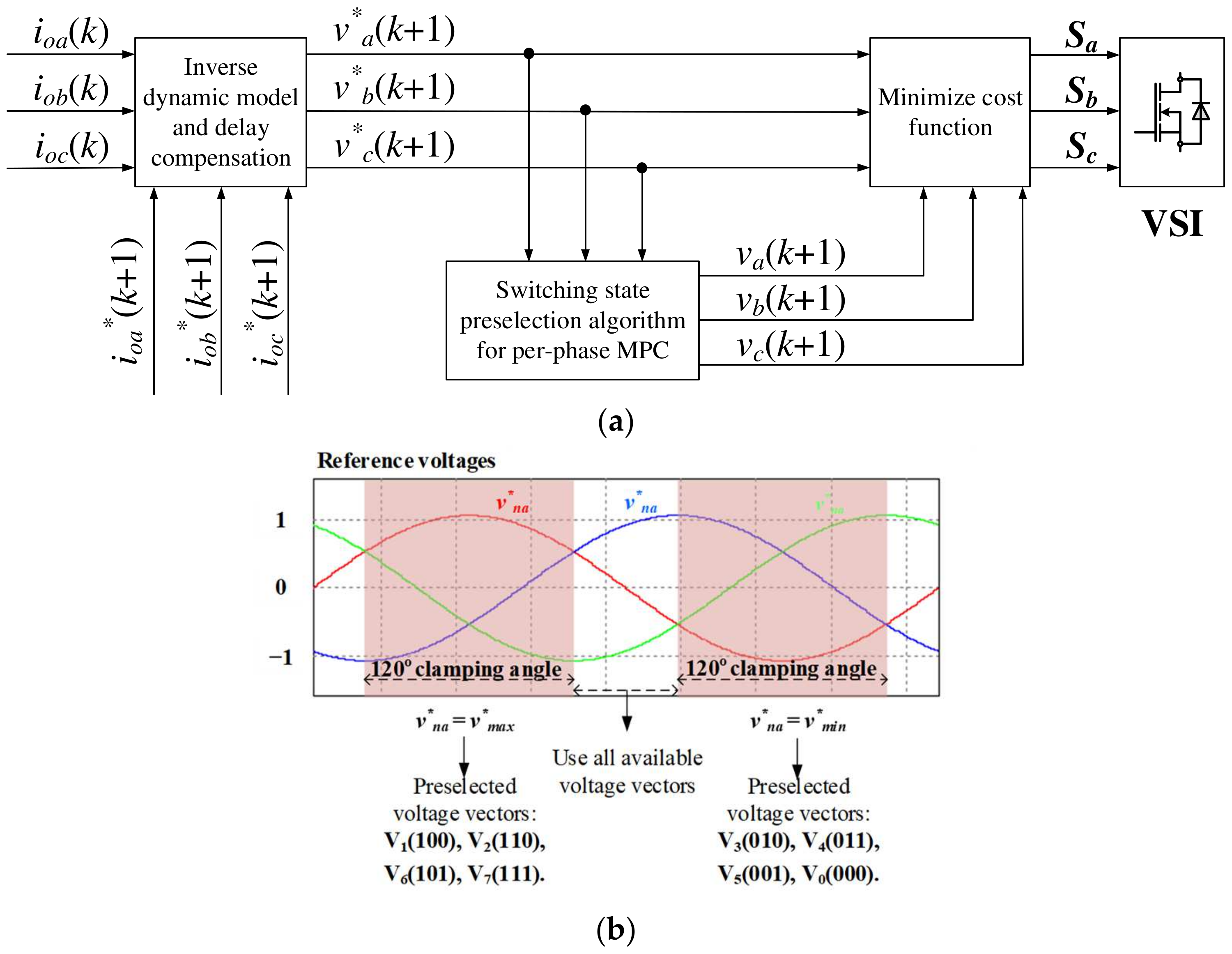

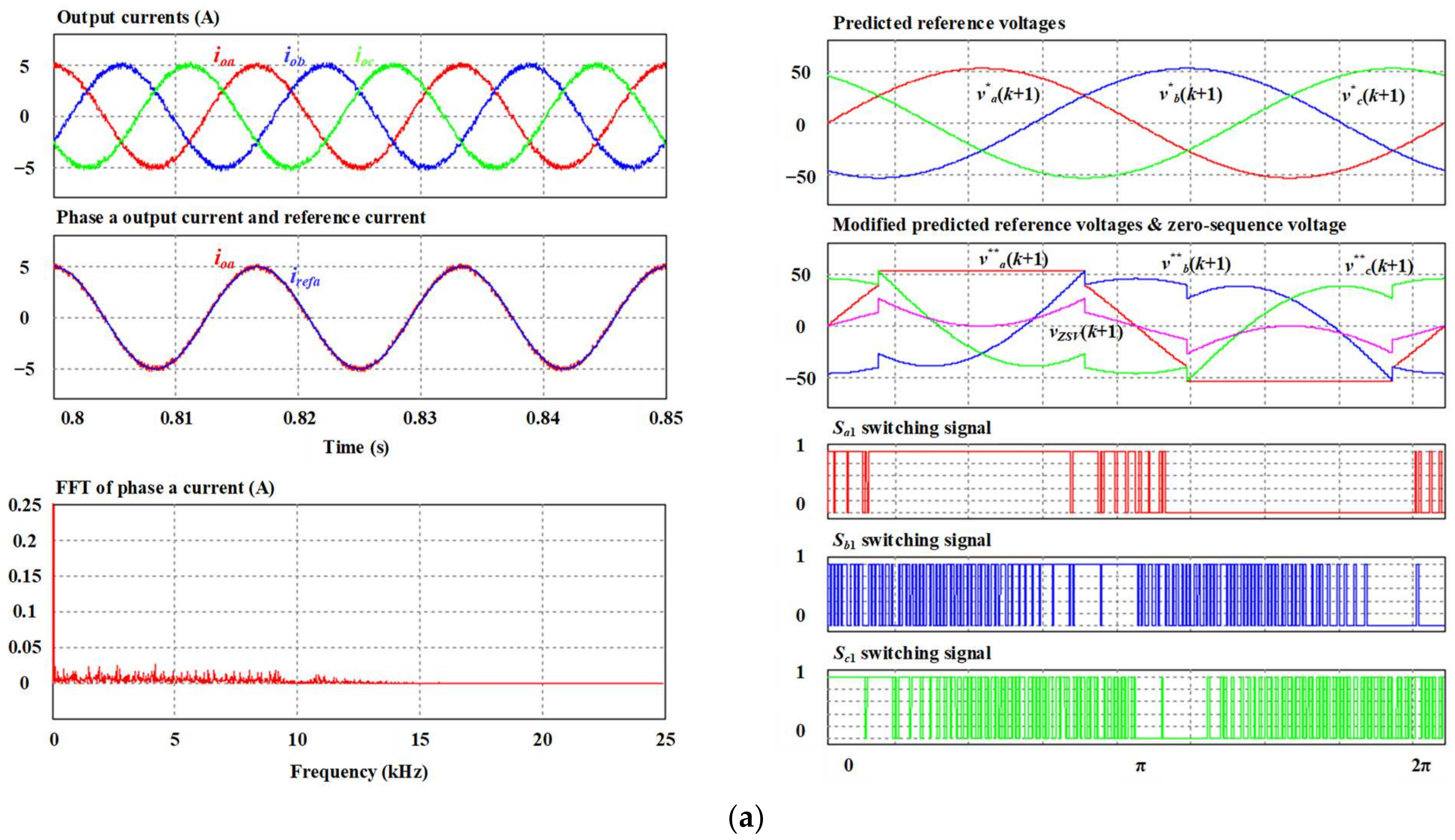

Figure 6 presents the steady-state results of the output current, fast Fourier transform (FFT) of phase

current, and switching signals acquired by the per-phase MPC1, per-phase MPC2, and space vector PWM (SVPWM) approaches. Since the regular MPC method chooses the optimal switching that minimizes a cost function, no commutations are forced every sample period. In fact, one switching state can be the optimal selection for two or more sample periods. This leads to a variable switching frequency. The average switching frequency per power device,

will be defined as the average value of the switching frequencies of the six controlled power semiconductor devices in the VSI circuit. Thus,

where

is the switching frequency during a time interval of the power semiconductor device number

of phase

. For a fair comparison, the carrier frequency,

and the sampling frequency,

are set to achieve a similar average switching frequency in both the per-phase MPC and SVPWM methods.

The output currents obtained using the three control methods have a sinusoidal waveform and an accurate phase and magnitude. The phase

output current,

, acquired by the three approaches show a small difference from the reference current,

. However, it can be noticed that the current quality and ripple content (or THD) are different among the control schemes because the per-phase MPCs are the nonconstant switching frequency control method. The FFT of the phase

output current has a wide range of frequencies. The FFT of the phase

output current is uniformly distributed across the frequency spectrum, reducing the individual harmonic component amplitudes. The FFT of the phase

output current obtained using the SVPWM method presents characteristic sidebands near the carrier frequency,

, as shown in

Figure 6c. Hence, the peak amplitude of the spectral content of the per-phase MPC methods is evidently lower than that of the SVPWM method.

On the right-hand side of

Figure 6a, the waveforms of the predicted reference voltage, the modified predicted reference voltages, the predicted

ZSV, and the switching signal in one fundamental period obtained using the per-phase MPC1 method are presented. As can be observed, the modified predicted reference voltage of phase

consists of two clamping periods of

at the positive and negative dc-link rails. This results in the power semiconductor device,

keeping its switching state for a two-thirds fundamental cycle. Meanwhile, the generated predicted

ZSV, which is injected into the sinusoidal reference voltages, does not generate the clamping periods in phases

and

. Regarding these waveforms obtained through the per-phase MPC2 scheme in

Figure 6b, the power semiconductor device

’s switching state contains a clamping period, which corresponds to the cases where the phase

reference voltage is determined as

or

. Meanwhile, the SVPWM has a continuous switching pattern in both three-phase legs, as shown in

Figure 6c.

In terms of dynamic performance,

Figure 7 illustrates the transient-state output current waveforms acquired by the per-phase MPC1, per-phase MPC2, and SVPWM approaches. The magnitude of the reference current is increased from

to

to induce a transient state. This allows for an assessment of the dynamic behavior of the output current. In

Figure 7, both the per-phase MPC schemes have excellent dynamic performance. The waveforms in

Figure 7a,b show that the system is highly stable since the current quickly follows the new reference value without any overshoot.

Figure 7c shows the output currents in response to the current step using SVPWM. The plot of the phase

output current and its reference indicate a lower dynamic performance compared to the two per-phase MPC approaches. To increase the dynamic performance of the PWM method, decoupling terms can be added to the PI controllers, or the PI gains can be increased. It should be noted that the increase in PI gains might lead to uncontrolled oscillation about the set point and instability in the system.

Parameter uncertainty can degrade the control system’s performance and even affect the system’s stability. In the MPC technique, the prediction model critically relies on having accurate load parameters.

Figure 8 shows the behavior of the output currents and switching state under a load inductance mismatch obtained with only the per-phase MPC1 and per-phase MPC2 methods. The same condition is applied to the load inductance as in the parameter mismatch of the dc-link voltage. In the first part of the waveforms, the equivalent inductance is half of the actual inductance; the middle shows that the equivalent inductance is correct; and the last shows that the equivalent inductance is 1.5 times higher than the actual one. The same condition is tested for the load resistance in

Figure 9. It can be seen from

Figure 9a,b that the output currents obtained from the two approaches are properly controlled with a sinusoidal form and an accurate magnitude. However, the current ripples obtained by per-phase MPC1 are slightly higher than those of per-phase MPC2. Additionally, the switching frequency decrease capability under per-phase MPC1 is decreased when the equivalent load inductance is higher than the actual load inductance. In terms of the parameter mismatch of the load resistance, both per-phase MPC1 and per-phase MPC2 properly control the output currents with negligible ripples. The switching frequency decrease capability is not degraded. Therefore, it can be concluded that per-phase MPC1 is affected by the parameter mismatch of the load more than per-phase MPC2.

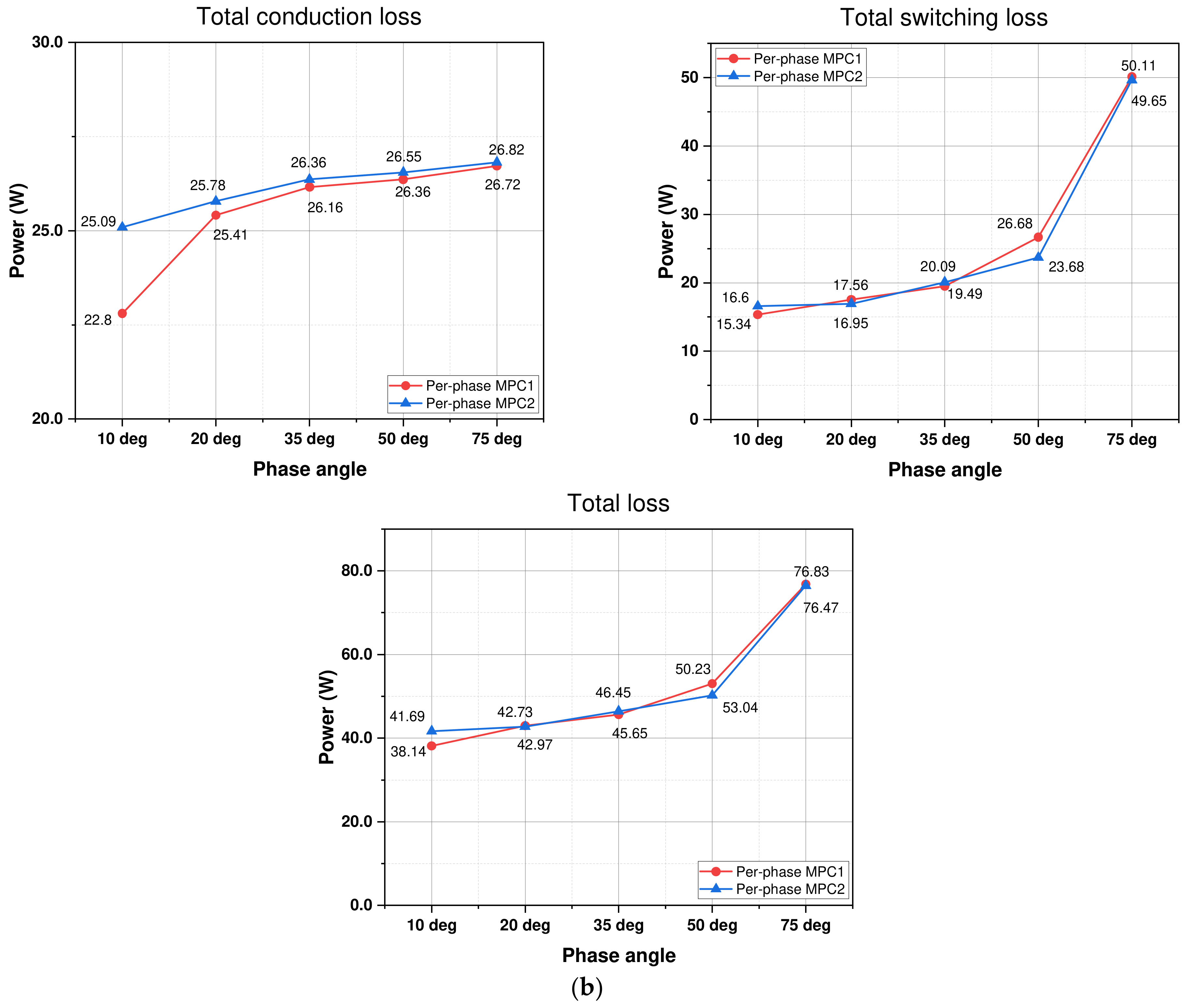

The values calculated from the simulation results are shown to comprehensively evaluate the output performance acquired using the per-phase MPC1, per-phase MPC2, and SVPWM methods.

Figure 10a–d present a performance comparison among the per-phase MPC1, per-phase MPC2, and SVPWM methods, including the THD value of the output current, switching frequency, and loss. The power loss of the semiconductor devices is calculated using the Thermal Module in the PSIM program with the actual device’s parameter from the IGBT datasheet.

Figure 10a presents an output phase current THD comparison between the three approaches. The THD value of the phase

current obtained through per-phase MPC2 is smaller than that obtained using the per-phase MPC1 method. However, due to the fact that the output current THD in phase

and phase

obtained through per-phase MPC2 is significantly high, the average THD obtained through per-phase MPC2 will still be similar to that obtained using the per-phase MPC1 method. Meanwhile, the output current THD in both three-phase legs obtained through SVPWM is the same and smaller than that obtained using the two per-phase MPC approaches. This is explained by the use of a PWM modulator, which is capable of shifting the main switching harmonics into a high-frequency region (around multiples of the switching frequency), and this leads to lower current harmonics. As shown in

Figure 10b, the three control schemes have a similar average switching frequency at about 4.1 kHz. Per-phase MPC2 lowers the switching frequency in phase

most, with a 22% lower frequency than for per-phase MPC1. However, the switching frequency in the remaining phases is significantly high. Meanwhile, the SVPWM has a constant switching frequency in both the three-phase legs.

Regarding the power loss performance comparison, thanks to the significant reduction in the switching frequency in phase

, the corresponding switching losses of phase

are relatively low. As shown in

Figure 10c, the phase

switching loss obtained through per-phase MPC2 is the lowest among the three control schemes, as it is about 33% lower than that of per-phase MPC1 and 75% lower than that of SVPWM. Although the phase

switching loss is decreased in the per-phase MPC methods, the switching losses in the two remaining phase legs increase. This leads to the total switching loss and total loss obtained by the two per-phase MPC methods and the SVPWM schemes being similar, as shown in

Figure 10d. The total loss attained through per-phase MPC2 is marginally lower than for the per-phase MPC1 and SVPWM approaches.

In order to further clarify the performance of the per-phase MPC approaches, a comparison among the two per-phase MPC methods is implemented under different circumstances, including a variety of sampling frequencies, output powers, and load angles.

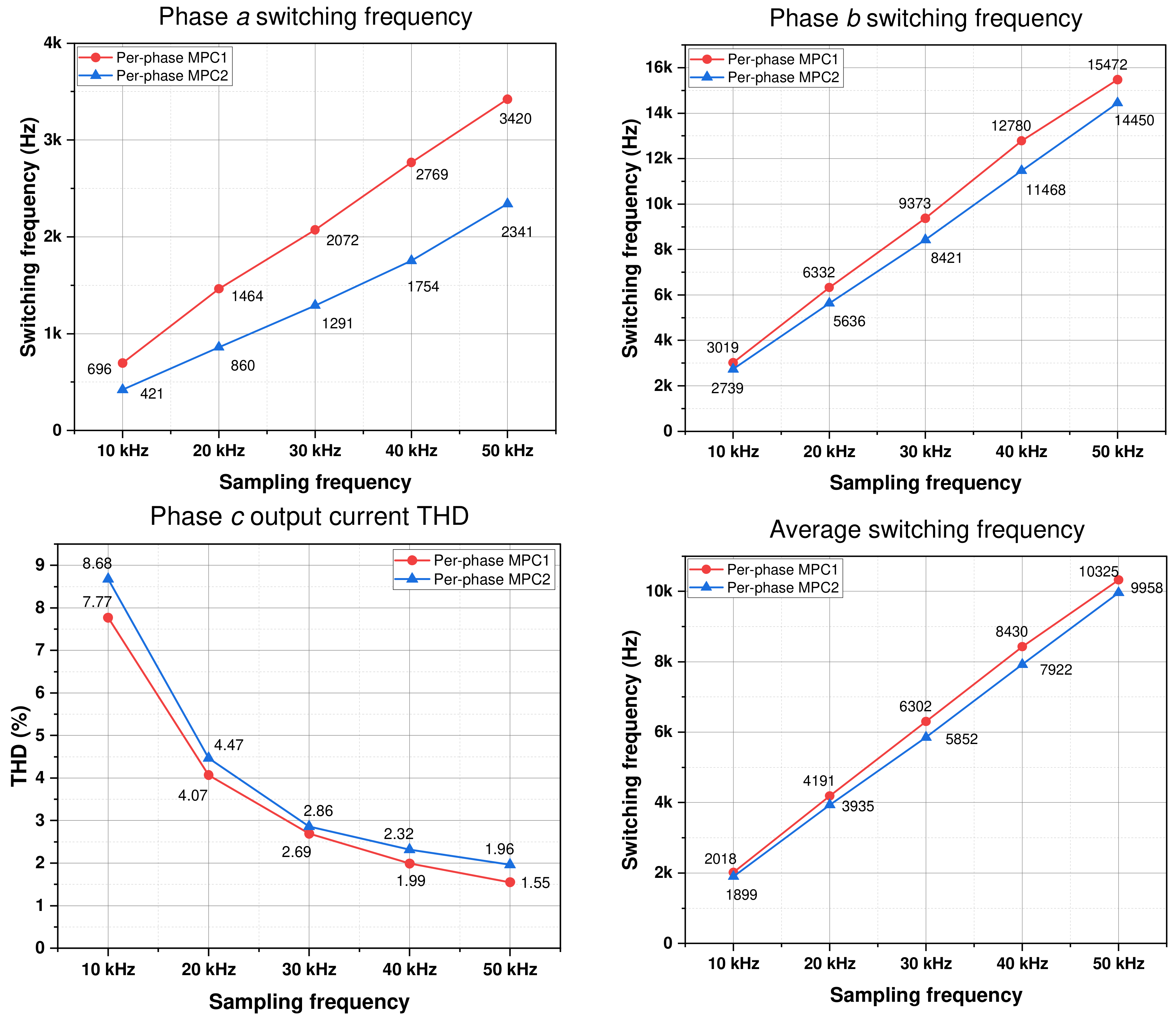

Figure 11 shows the phase and average output current THD under different sampling frequency conditions obtained by the two per-phase MPC approaches. The THD values of the output currents obtained by the two per-phase MPC techniques decrease as the sampling frequency increases. The average output current THD of per-phase MPC1 is slightly lower than that of per-phase MPC2.

In

Figure 12, the average frequency of per-phase MPC1 is slightly higher than that of per-phase MPC2 by about 7%. Under different sampling frequencies, per-phase MPC2 decreases the switching frequency of phase

the most. The switching frequency of phase

obtained through per-phase MPC2 is lower than that of per-phase MPC1 by about 35%.

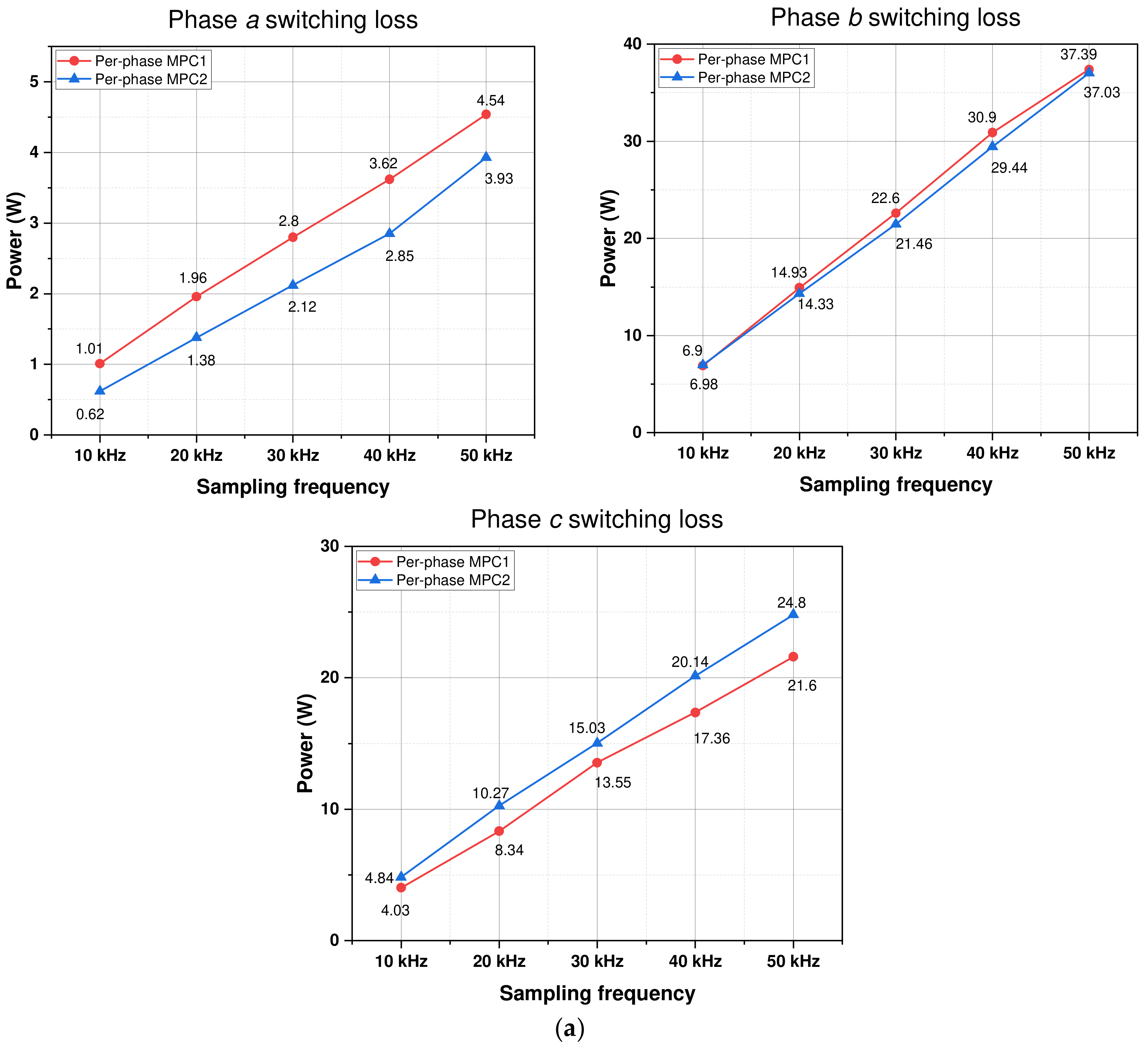

Regarding the conduction loss acquired through the two MPC approaches, the difference in the conduction loss between the two techniques under different sampling frequency conditions is small. The phase

switching loss acquired through per-phase MPC2 is the lowest, as shown in

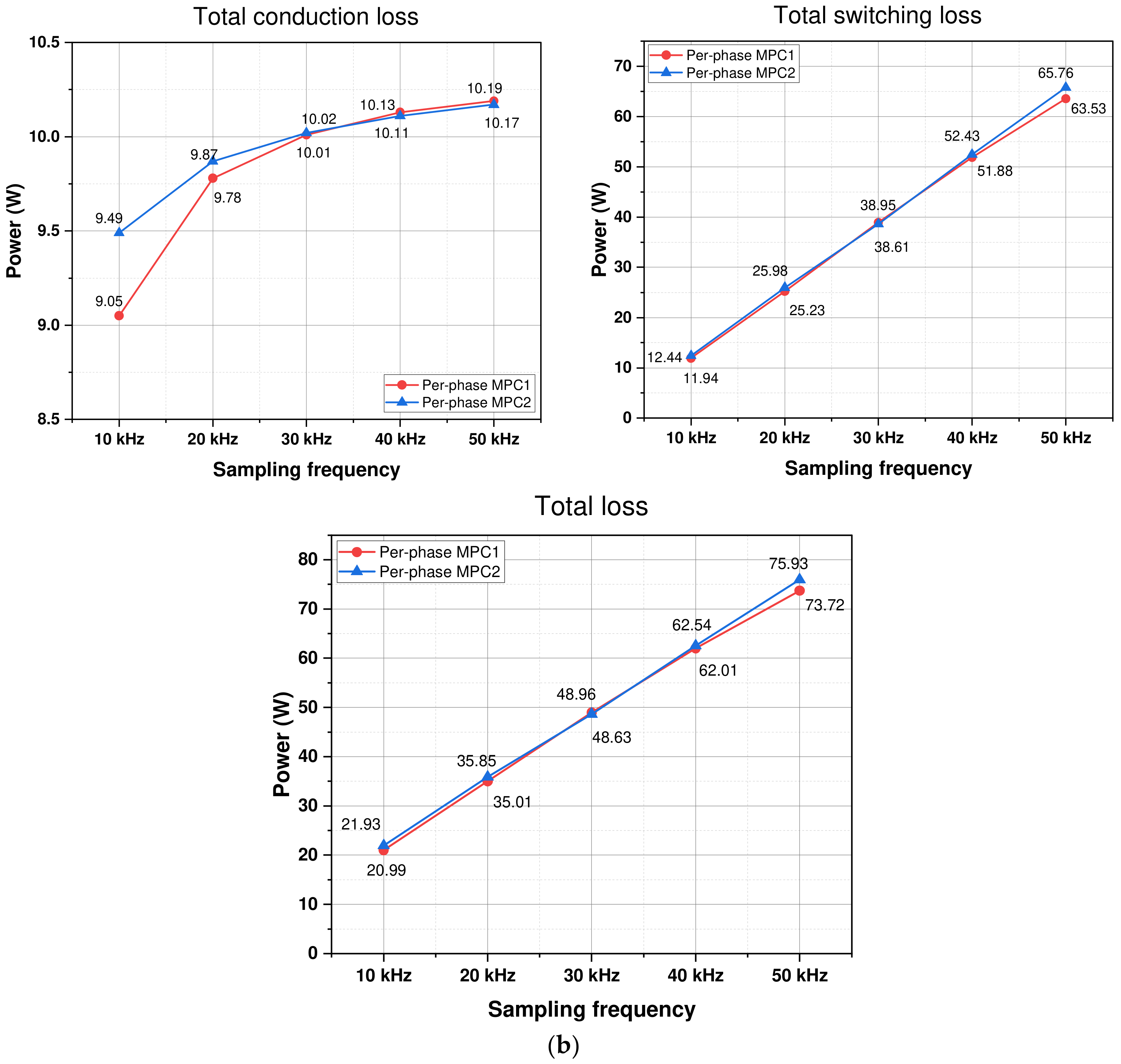

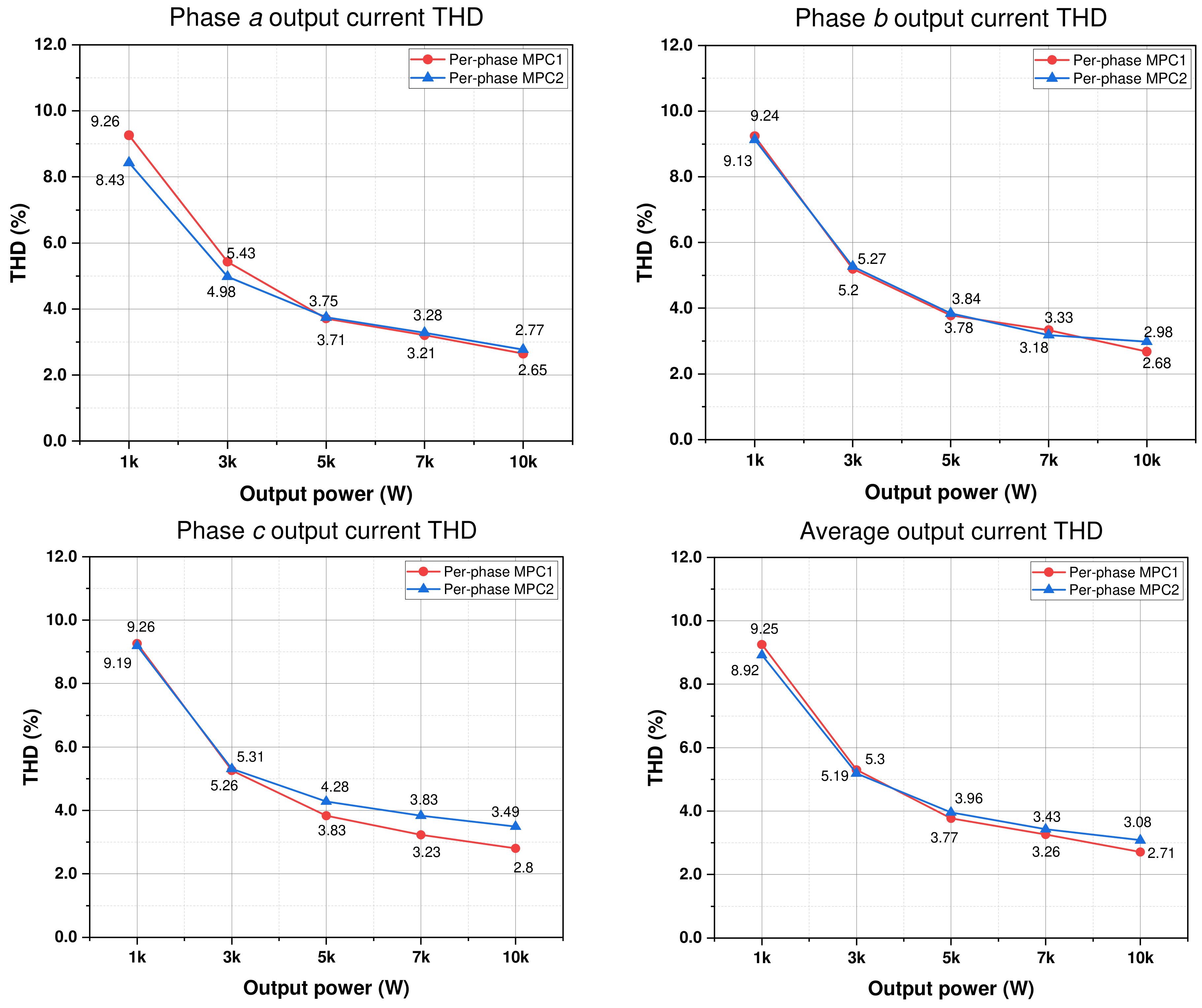

Figure 13a. This switching loss is lower than that of per-phase MPC1 by about 20–30%. However, because the switching losses in the remaining phase legs increase, the two per-phase MPC methods have a similar total loss.

Figure 14 shows the phase and average output current THD under different output power conditions obtained through the two per-phase approaches. The THD value of the output current obtained through the two schemes decreases when the output power increases. The per-phase MPC2 method has the highest output current THD when the output power is large. The average output current THD of per-phase MPC1 is slightly lower than that of per-phase MPC2.

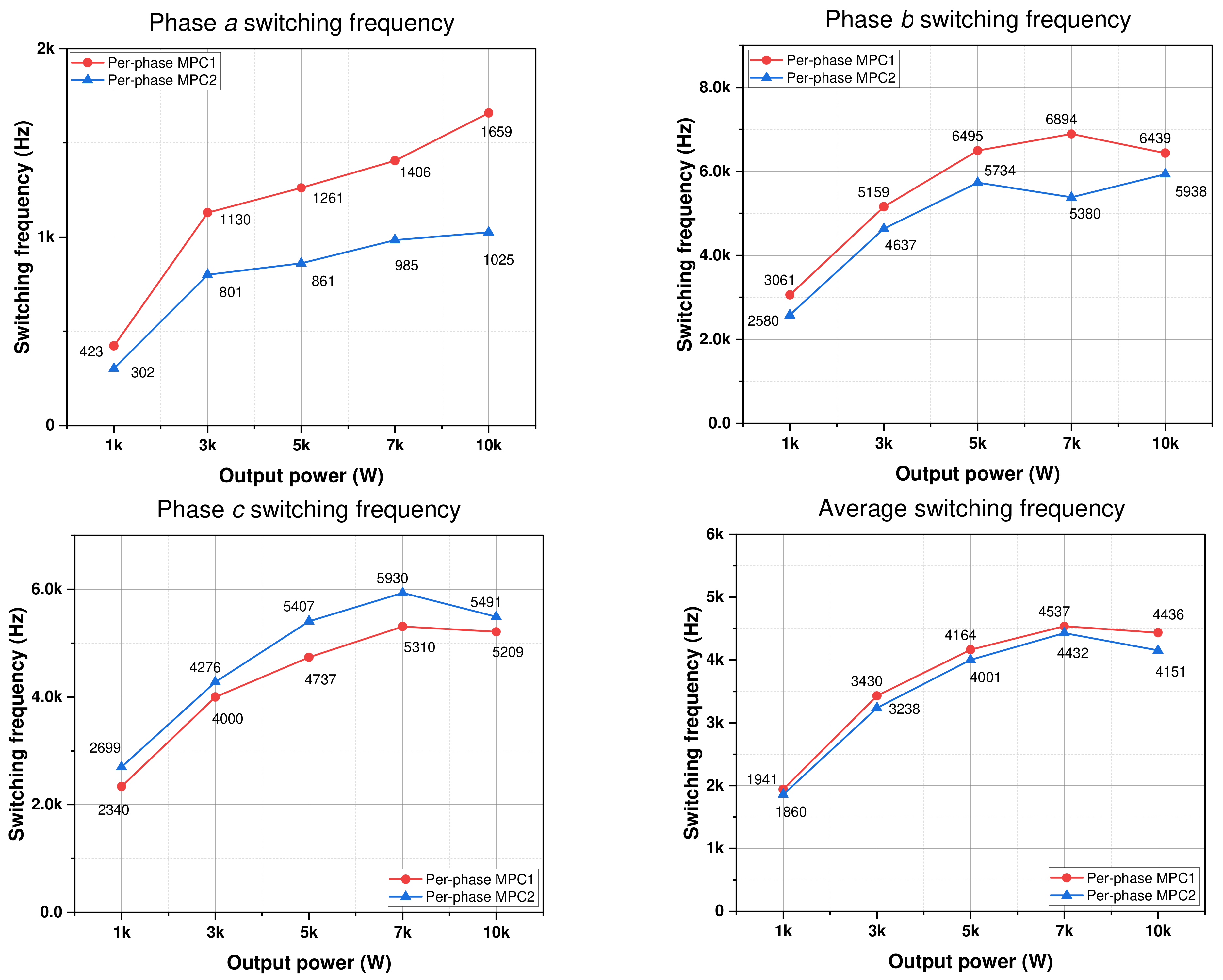

In

Figure 15, the average switching frequencies of the two per-phase control schemes are similar, with a small difference when the output power varies. The switching frequency of phase

is reduced the most by per-phase MPC2. The switching frequency obtained through per-phase MPC2 is lower than that of per-phase MPC1 by about 30%.

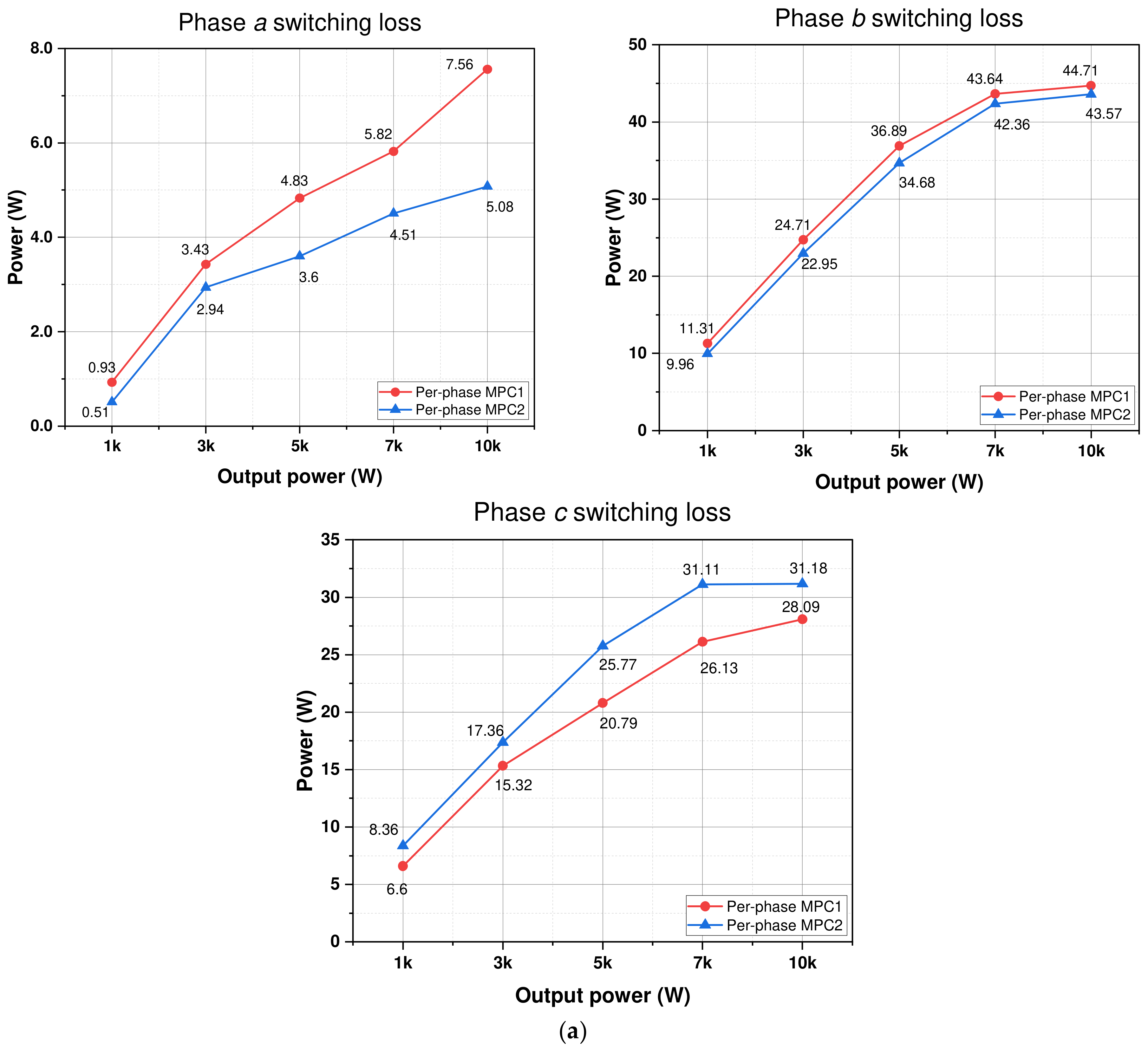

Regarding the conduction loss acquired through the two approaches, the difference in the conduction loss between the two techniques under various output powers is small. The switching loss of phase

acquired with per-phase MPC2 is the lowest. This switching loss is lower than that of per-phase MPC1 by about 20–35%, as shown in

Figure 16a. However, because the switching losses in remaining phase legs increase, the two per-phase MPC methods have similar total losses.

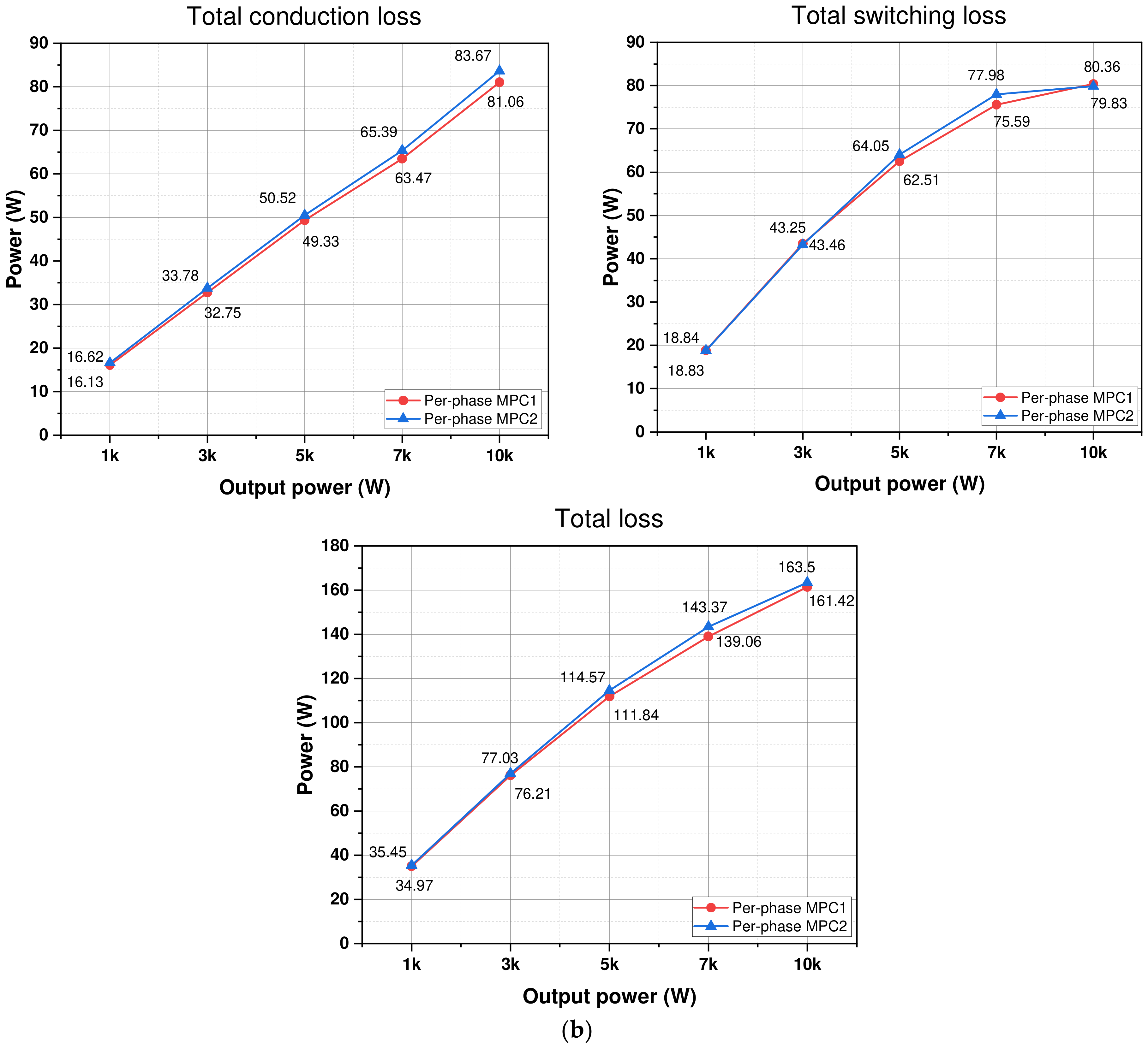

Figure 17 shows the phase and average output current THD under different load conditions obtained using the two per-phase approaches. The THD value of the output currents acquired with the two per-phase MPC approaches decreases when the phase load angle rises. Under different load conditions, the average THD of the output current attained with per-phase MPC1 and per-phase MPC2 are similar.

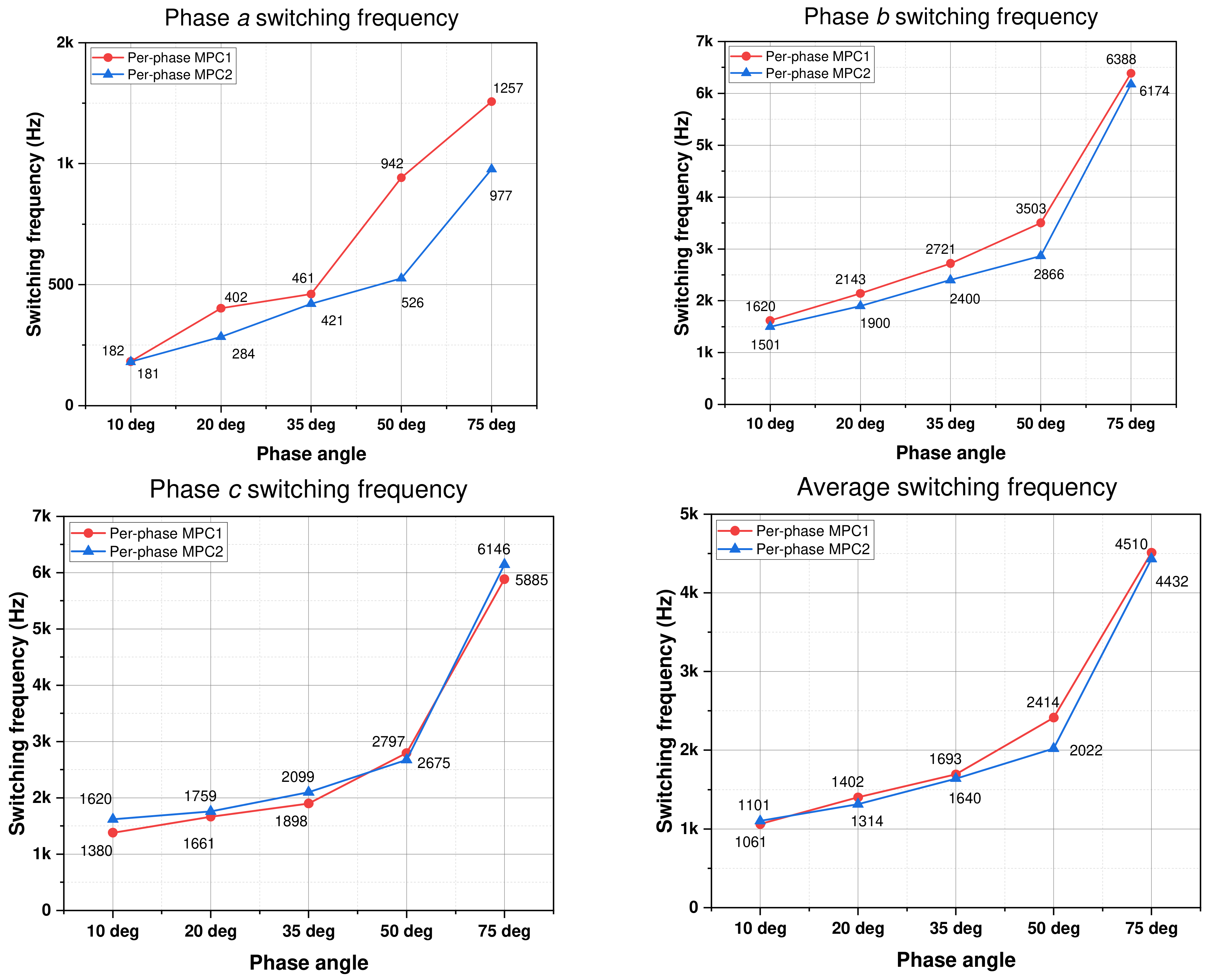

In

Figure 18, the difference in the average switching frequency between the two control schemes is negligible under different load conditions. Under different load conditions, the switching frequency of phase

is decreased the most by per-phase MPC2. The switching frequency obtained with the per-phase MPC2 method is lower than that of per-phase MPC1 by about 30%.

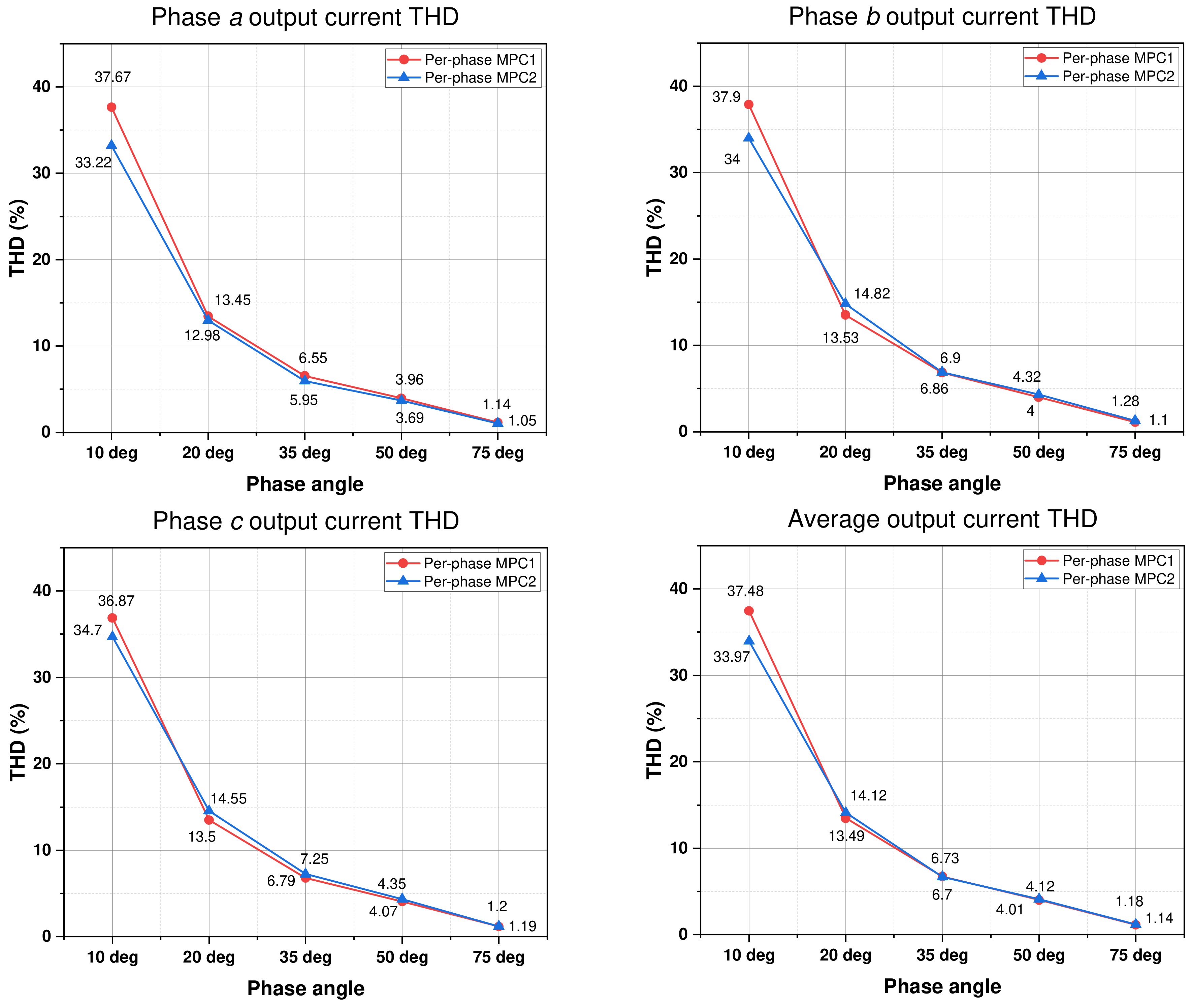

A comparison of the power loss between the per-phase techniques under a variety of load conditions is depicted in

Figure 19. Regarding the conduction loss acquired through the two per-phase MPC approaches, the difference in the conduction loss between the two techniques under different load conditions is small. The switching loss of phase

acquired with per-phase MPC2 is the lowest. This is lower than the switching loss of per-phase MPC1 by about 20–30%. However, due to the switching losses in the remaining phase legs increasing, the two per-phase MPC methods have similar total losses.

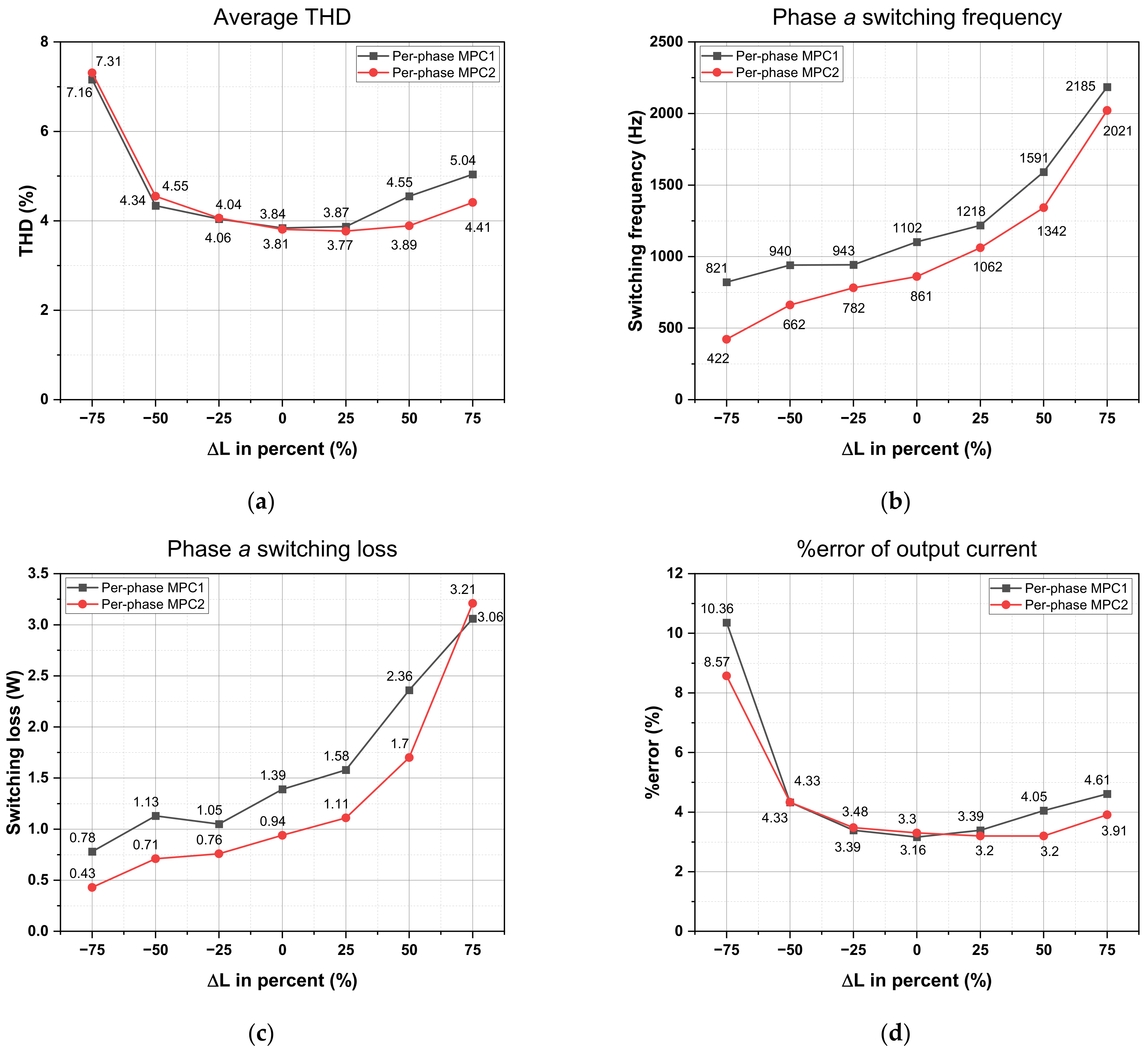

Figure 20 displays the performance of the per-phase MPC1 and per-phase MPC2 methods when there exists a parameter mismatch in the load inductance. This performance evaluation includes several aspects, such as the average THD value, the switching frequency and switching loss in phase

, and the %error of the output current. In

Figure 20, the vertical axis in the line charts illustrates the variance between the model parameter and the real value of load inductance. As observed in

Figure 20a, the average output current THD obtained using the per-phase MPC1 and MPC2 methods varies slightly with a 25% load inductance variance. When the load inductance variance is 50%, the average THD of the output current increases. In particular, the average THD attained using the per-phase MPC1 and MPC2 methods significantly rises as the real value of the load inductance is 75% larger than the value of the model parameter.

Figure 20b,c illustrate that the capability of the per-phase MPC methods to reduce the switching frequency diminishes when the model parameter of the inductance exceeds its actual value. When the model parameter inductance is 75% smaller than the real inductance, there is a notable increase in the %error of the output current. This increase is substantial, reaching about 3.3 times for per-phase MPC1 and about 2.6 times for per-phase MPC2 compared to the normal condition. In comparison between the per-phase MPC1 and per-phase MPC2 methods, the MPC1 method is affected by a load inductance mismatch more than the MPC2 method.

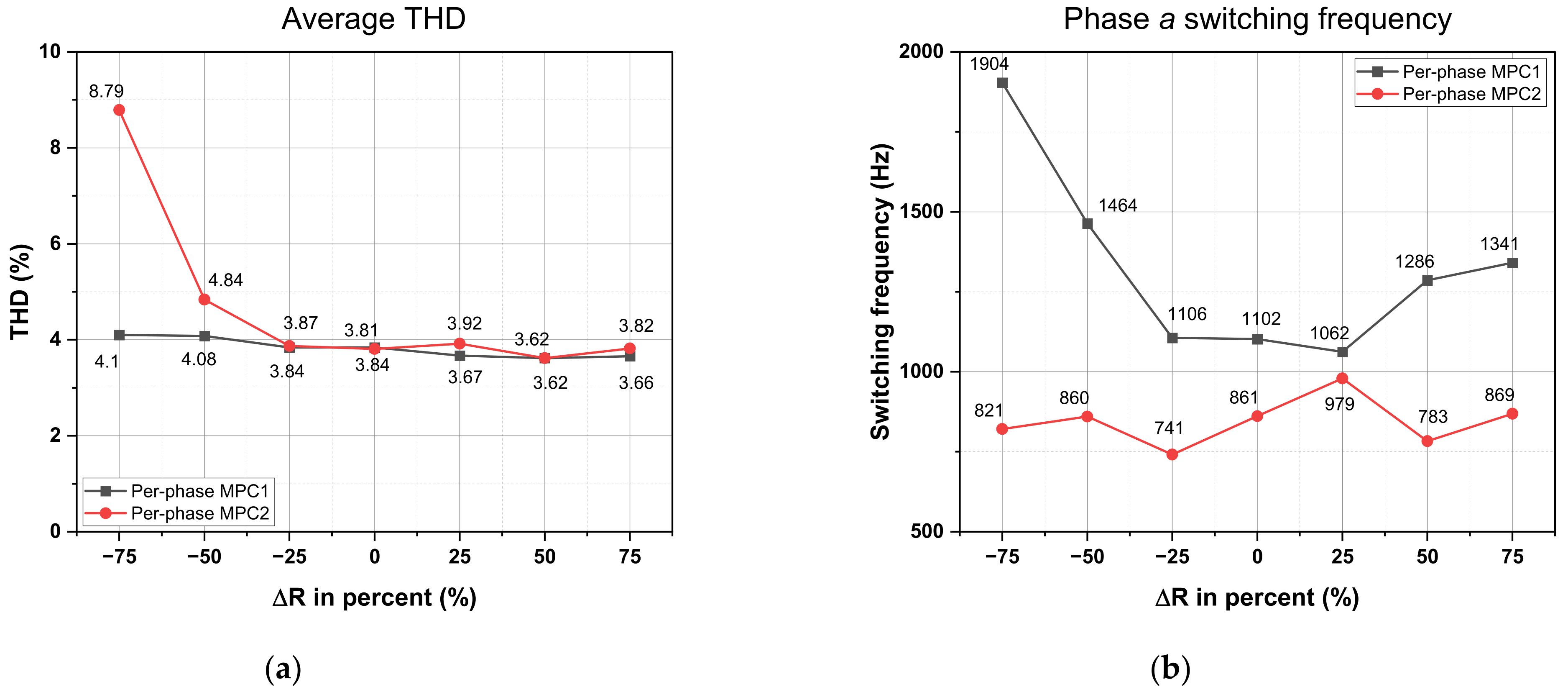

Similar to the parameter mismatch of the load inductance,

Figure 21 displays the performance of the per-phase MPC1 and per-phase MPC2 methods when there is a parameter mismatch in the load resistance with similar aspects.

Figure 21a illustrates that the average output current THD obtained using the two per-phase methods slightly varies with a 50% smaller and 75% larger load resistance variance. When the model parameter resistance is 75% smaller than the real one, the average THD of the output current obtained with per-phase MPC2 increases significantly. Regarding the methods’ capability to reduce the switching frequency, per-phase MPC2 performs well even when the variation between the model parameter value of the load resistance and the real value is 75%. Meanwhile, the capability to reduce the switching frequency of per-phase MPC2 is lowered when the variation between the model parameter value of the load resistance and the real value is 55%. Especially when the model parameter resistance is 75% smaller than the real resistance, the phase

switching frequency obtained through per-phase MPC1 significantly increases.

Figure 21c depicts a phase

switching loss comparison between the two per-phase MPC approaches. The phase

switching loss obtained with the two per-phase MPC methods significantly increases when the model parameter resistance is 50% and 75% smaller than the actual resistance. As observed in

Figure 21d, per-phase MPC1 only can maintain the output current error with a 25% load resistance variance. When the difference between the model parameter resistance and the actual one is higher than 50%, the %error of the output current acquired with per-phase MPC1 rises notably. Meanwhile, per-phase MPC2 can maintain the output current error even with a 50% load resistance variance. In comparison between the per-phase MPC and per-phase MPC2 methods, the MPC1 method is affected by the load resistance mismatch more than the MPC2 method.

To comprehensively compare the performance of the per-phase MPC1 and per-phase MPC2 methods, two control schemes are conducted in the experiment. The per-phase MPC schemes are validated using a laboratory-scaled two-level three-phase VSI system. The structure of the two-level three-phase VSI system is presented in

Figure 22. Meanwhile, the system parameters are similar to the simulation, as listed in

Table 1. A Texas Instruments digital signal processor (DSP) TMS320F28335 is employed for implementing both of the per-phase MPC methods.

Figure 23 presents the experiment results of the output current waveforms, the FFT of phase

current, and the switching signals at steady-state acquired by the per-phase MPC1 and per-phase MPC2 schemes. The output currents acquired with the two control methods have a sinusoidal form and an accurate phase and magnitude. In the per-phase MPC schemes, the FFT of the phase

output current has a wide range of frequencies. The FFT of the phase

output current is uniformly distributed across the frequency spectrum, reducing the individual harmonic component amplitudes.

On the right-hand side of

Figure 23a, the waveforms of the phase

modified predicted reference voltages, predicted

ZSV, and switching signal in one fundamental period obtained using the per-phase MPC1 method are presented. The modified predicted reference voltage of phase

consists of two clamping periods of

at positive and negative dc-link rails. This results in the power semiconductor device,

keeping its switching state for two-thirds of a fundamental cycle. In terms of per-phase MPC2, in

Figure 23b, the power semiconductor device

’s switching state contains a clamping period, which relates to the cases where the phase

reference voltage is determined as

or

as in experimental results shown in

Figure 23b.

In terms of dynamic performance,

Figure 24 illustrates the transient-state output current waveforms acquired by the per-phase MPC1 and per-phase MPC2 approaches. The magnitude of the reference current is increased from

to

to induce a transient state. This allows for an assessment of the dynamic behavior of the output current. In

Figure 24, both the two per-phase MPC schemes have excellent dynamic performance. The waveforms of

Figure 24a,b show that the system is highly stable since the current quickly follows the new reference value without any overshoot.

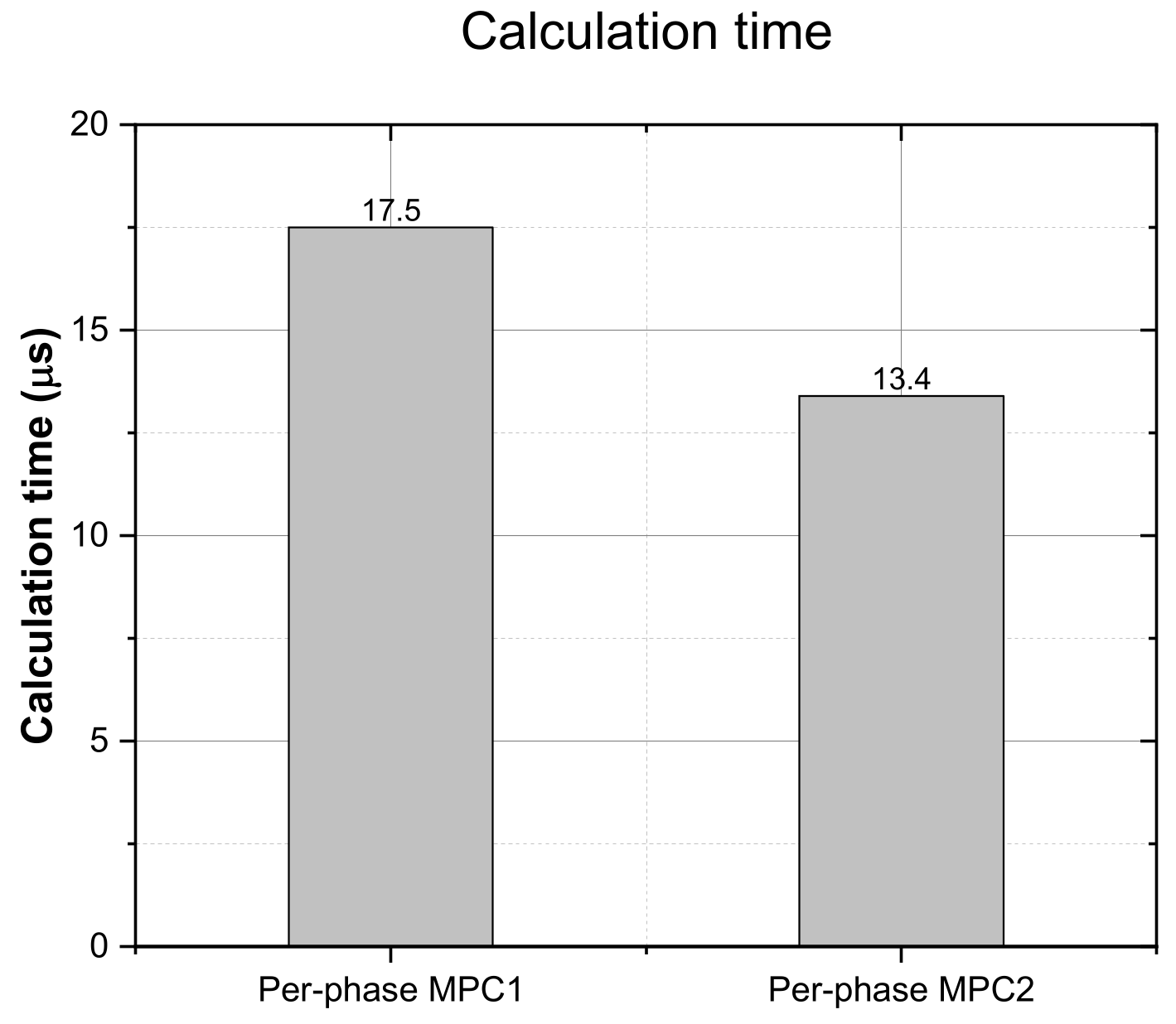

In the experiment implementation, the two per-phase techniques take different calculation times to execute the algorithm. The execution time for each of the algorithms was computed by measuring the elapsed time in the experimental setup, and the results are shown in

Figure 25. It can be seen that per-phase MPC1 has the highest calculation time at 17.5 μs. This is because of the calculation time for all seven switching states and the zero-voltage vector selection of the considered per-phase MPC1 technique. Meanwhile, during the clamping period, the per-phase MPC2 method only needs to evaluate four switching states. Thus, its calculation time is lower than that of per-phase MPC1.

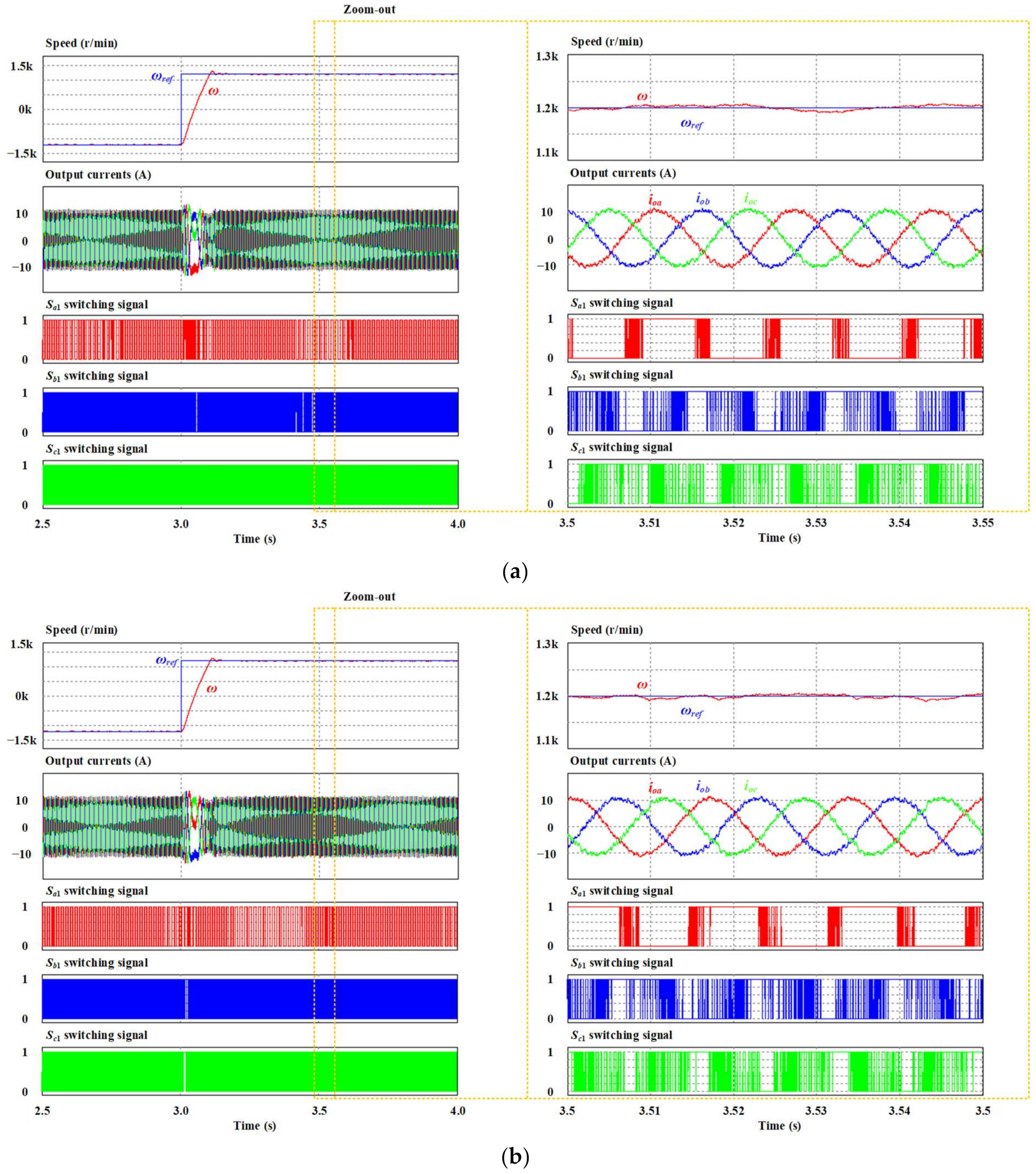

In addition to static load conditions, the simulation results obtained through two per-phase MPC for a VSI-fed three-phase induction motor are depicted in

Figure 26. Here, phase

was still assumed to be the leg that has aged the most. In the simulation, the speed range control was evaluated while varying the rotor speed from −1200 r/min to 1200 r/min. The waveforms of the motor speed, output currents, and switching patterns are depicted in

Figure 26. As can be seen in both

Figure 26a,b, the motor speed correctly tracked the corresponding reference for both the two per-phase MPC methods. Meanwhile, the output currents have the correct sinusoidal form and magnitude. In terms of switching patterns, it can be observed that the phase

switching patterns obtained using the two per-phase MPC methods contain clamping regions as expected. This verifies the correctness of the two per-phase MPC methods used against the dynamic load (a three-phase induction motor).

Table 2 provides an overview of comparative findings derived from the simulations and experimental outcomes for the two per-phase MPC methods. Regarding output performance, the per-phase MPC1 method provides a lower output current THD than the per-phase MPC2 method. The two per-phase MPC techniques are good at lowering the switch loss in a specific leg. Among them, per-phase MPC2 reduces the switching frequency and switching loss in a specific phase the most, by about 20–30% lower than per-phase MPC1. In terms of dynamic response, the two per-phase MPC methods have superior performance. It is determined that the two per-phase MPC methods have differences in their parameter sensitivity. The load mismatches have a small effect on the performance of the per-phase MPC2 method but a great effect on the per-phase MPC1 method. Due to the per-phase MPC1 method having to calculate all the switching state cases of the VSI for the considered cost function, the corresponding calculation time is higher than that of the per-phase MPC2 method by about 30%. Additionally, another drawback of the two per-phase MPC approaches is that the switching loss in the two remaining phases increases notably, though both per-phase MPC approaches can significantly reduce the switching loss in specific phase legs.