The Development and Progress of Multi-Physics Simulation Design for TSV-Based 3D Integrated System

Abstract

:1. Introduction

2. Electrical Simulation Design of TSV in 3D Integrated System

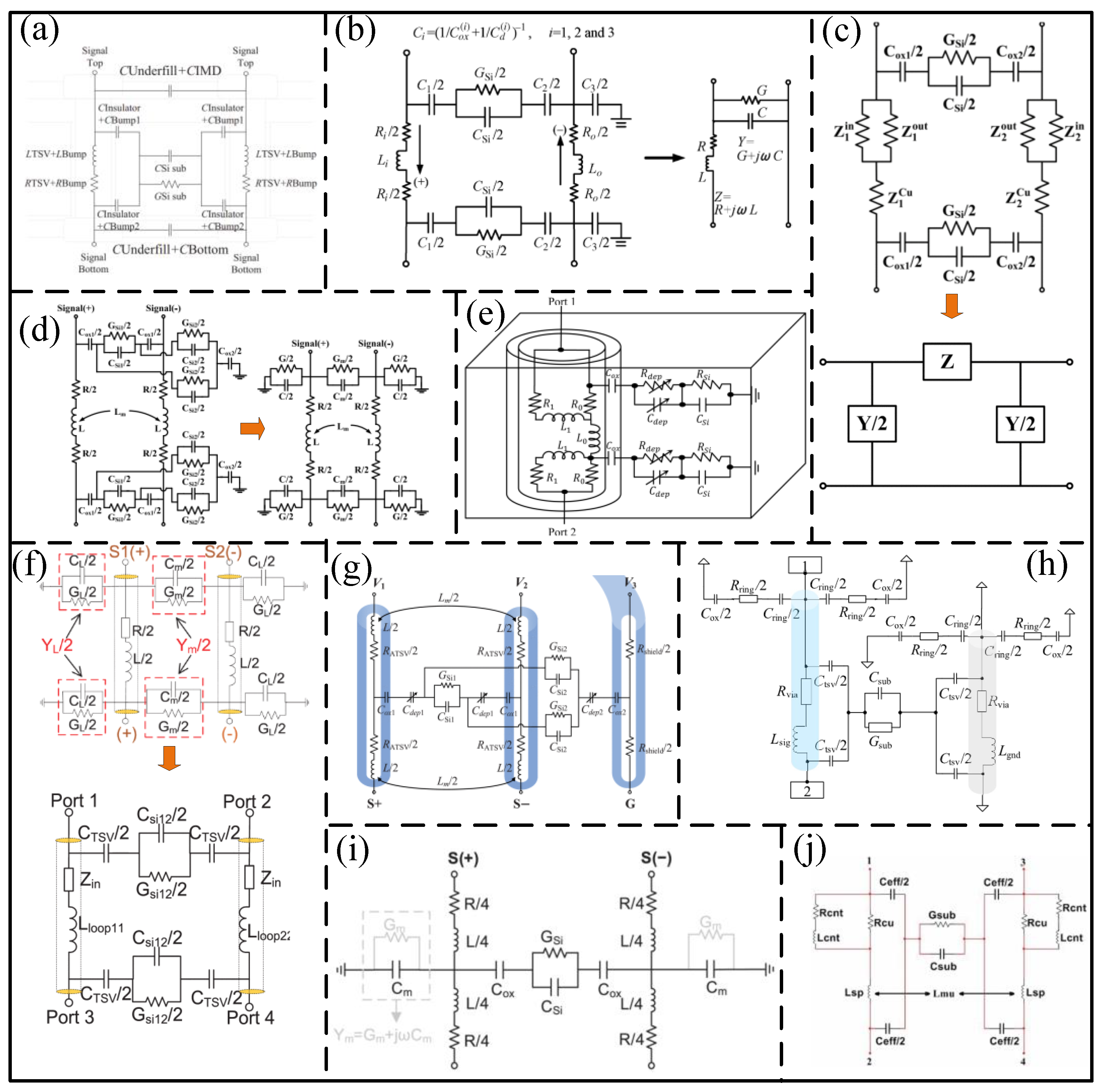

2.1. Lumped Parameter Model-Based Design

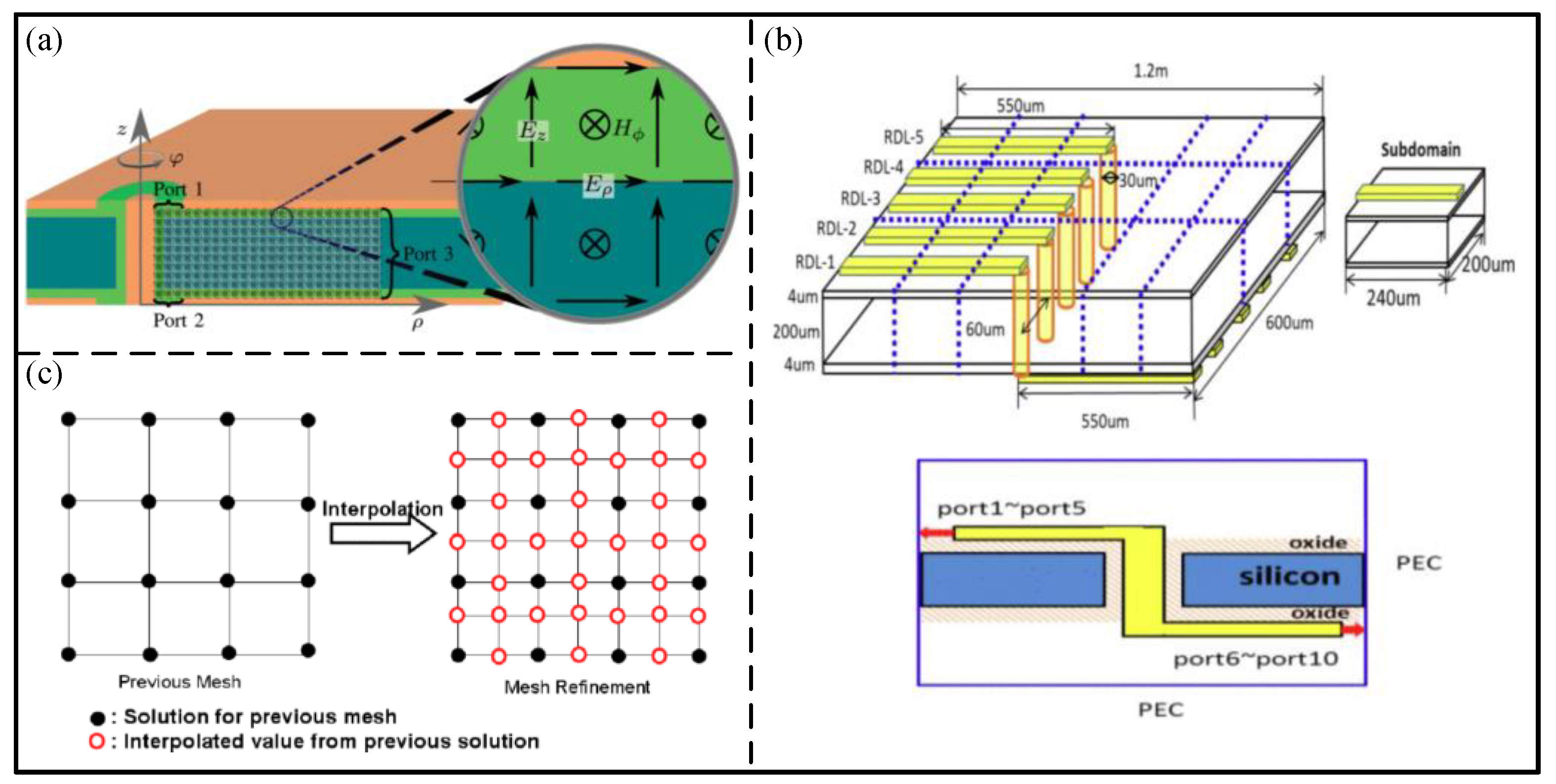

2.2. Numerical Computation Model-Based Design

3. Thermal Simulation Design of TSV in 3D Integrated System

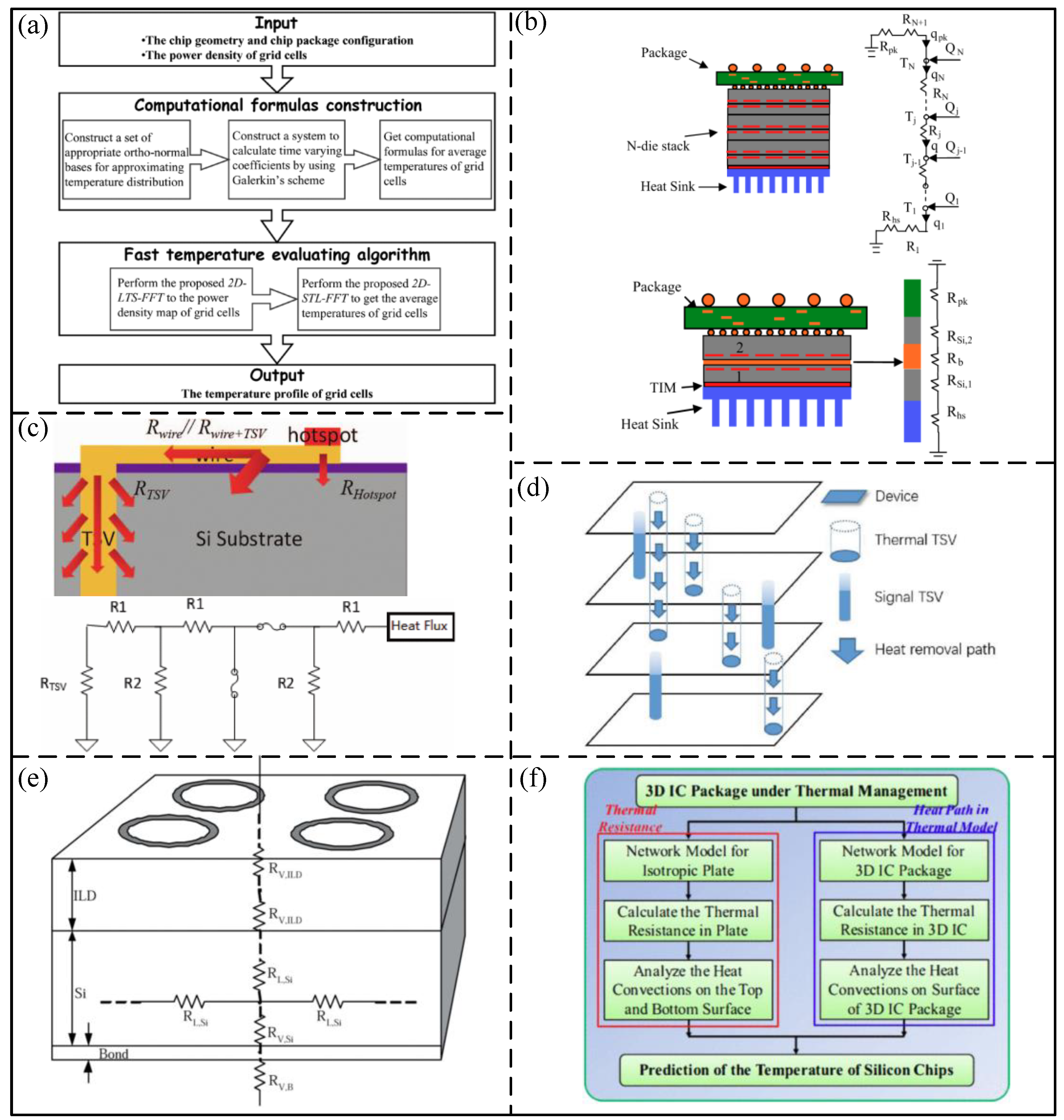

3.1. Analytical Model-Based Design

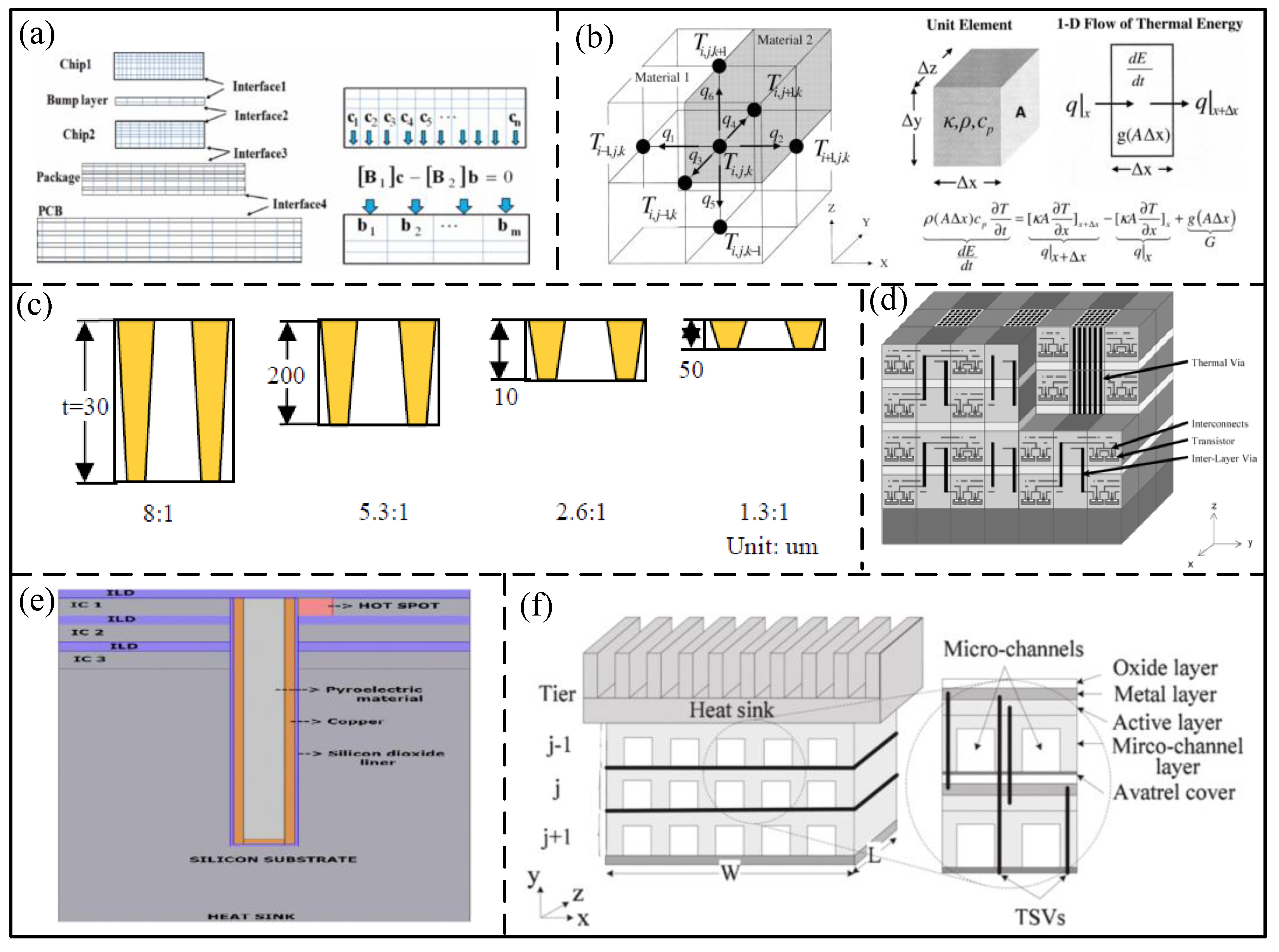

3.2. Numerical Computation Model-Based Design

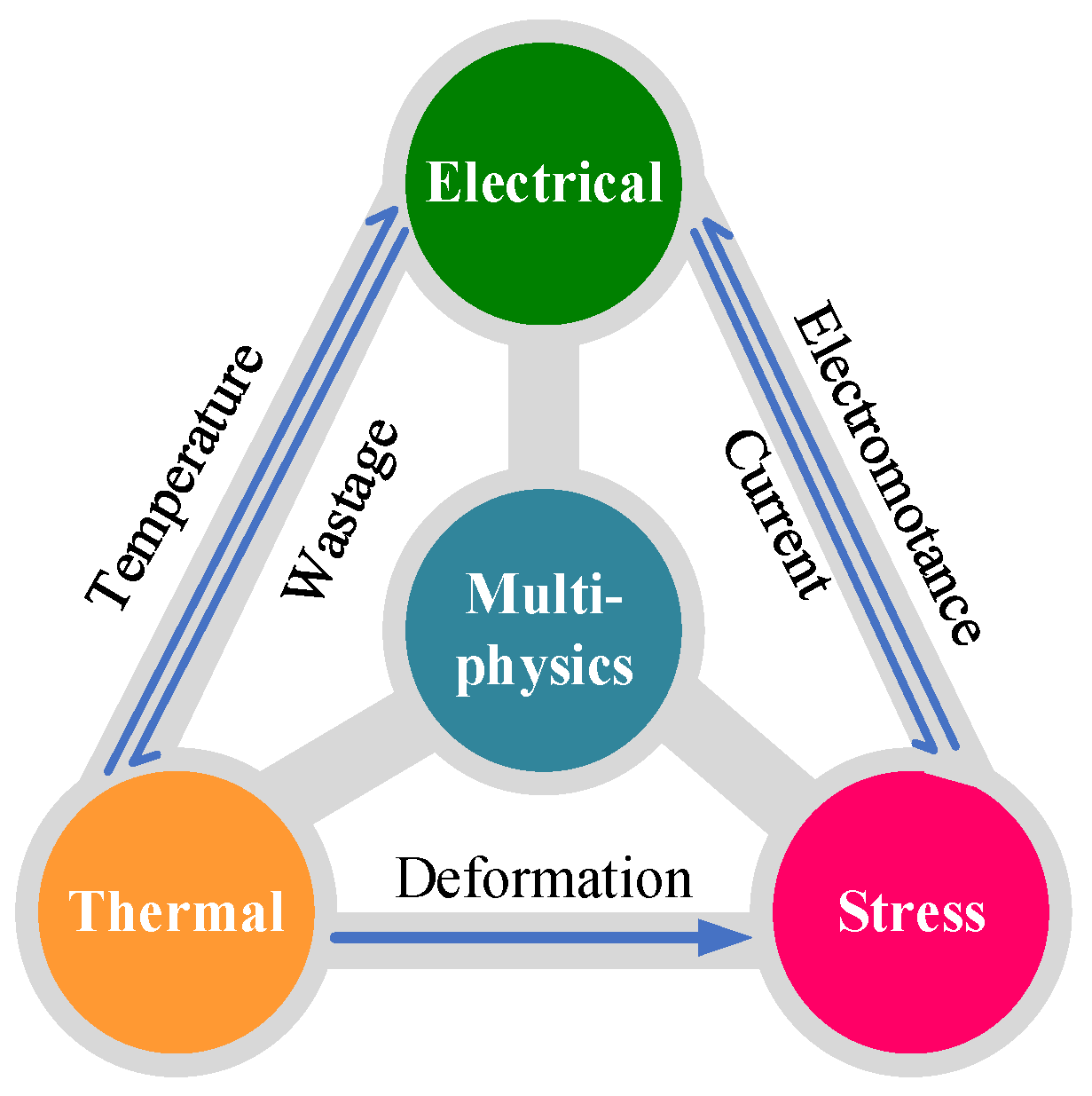

4. Multi-Physics Co-Simulation Design of TSV in 3D Integrated System

4.1. Thermal Stress Coupling Simulation Design

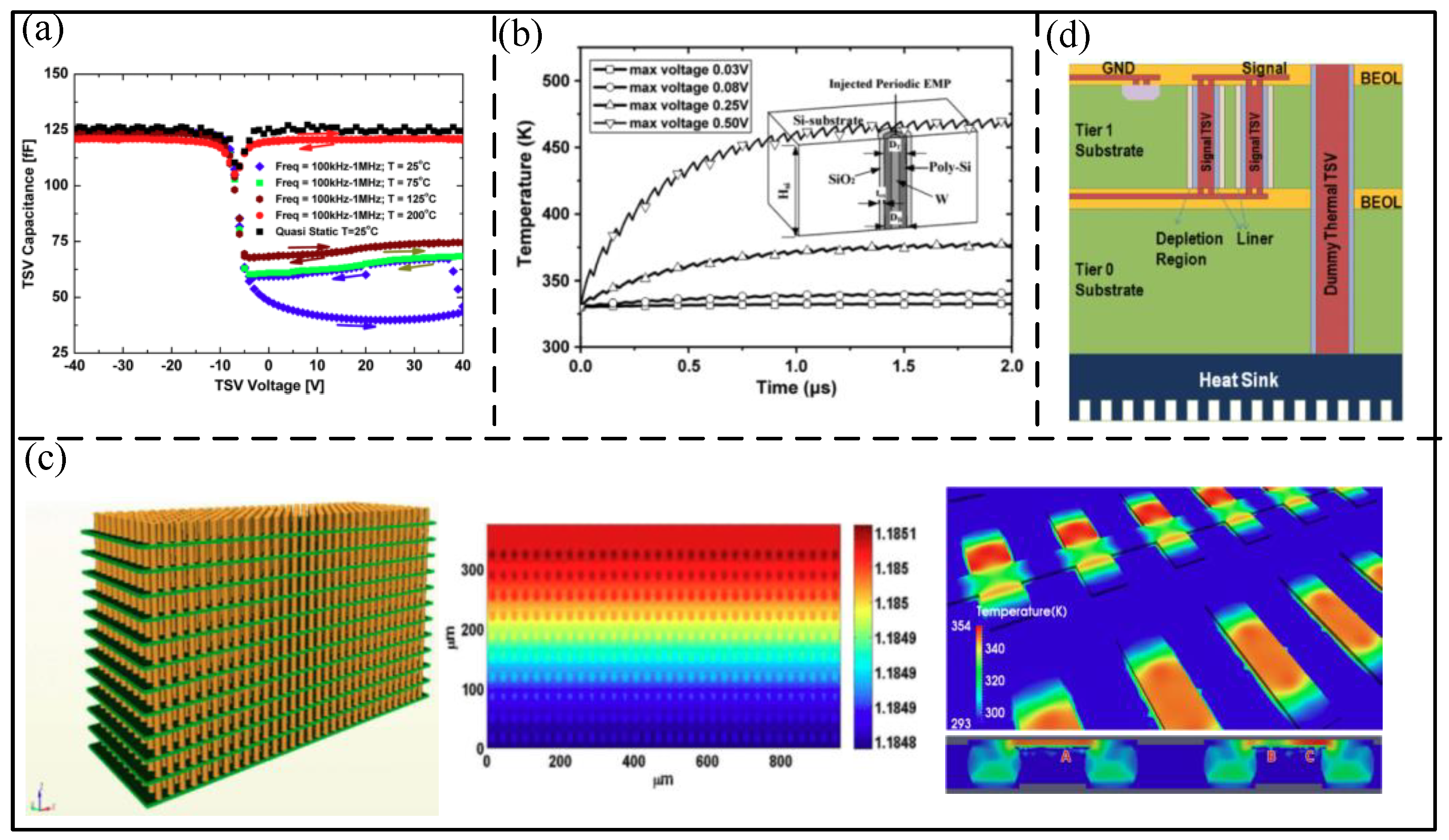

4.2. Electro-Thermal Coupling Simulation Design

5. Conclusions

- (1)

- Advanced integrated microsystems. The 3D integrated technology of imaging sensing is based on the route of imaging sensing chip and CMOS chip integration, using high-density TSV or inter-chip bonding technology, which lays a technical foundation for the development of computational and intelligent imaging in the future. The RF 3D integrated system has been widely applied in aerospace, aviation, ships, weapons, information technology, biology, medicine, industrial control, consumer electronics, etc. In addition, the Chiplet-based 3D integration technologies will be widely used in high-performance computing systems, high-reliability MEMS systems, mass memory systems, etc.

- (2)

- Crossed and reconfigurable architecture design technology. The 3D heterogeneous integration of the microsystem is focused on system-level packaging, and the crossed design from system to package is also required. In addition, the cost and lifetime of 3D wiring, multi-domain and multi-tools interactions are need to addressed for high-reliability 3D integrated microsystems. The reconfigurable technology can effectively improve the utilization efficiency of Chips and then improve the utilization range of 3D integrated microsystems. With the product development cycles continuing to shorten, collaborative design across multiple disciplines and domains such as circuit, structure, process and thermal design is required to achieve the 3D heterogeneous integrated microsystems.

- (3)

- Standardized and intelligent design technology. Standardized and intelligence are the design direction of 3D integrated microsystems. The standardized interconnection protocols can achieve the normalization and modularization of circuits in 3D integrated microsystems. In addition, intelligence refers to the application of the system to more scenarios and environments so that the degree of autonomy of the system is greatly enhanced. The application field of the system is significantly expanded, and the continuous innovation of the platform is promoted. Moreover, the intelligent optimization method can be used to improve the design efficiency of a 3D integrated system.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Beyne, E. The rise of the 3rd dimension for system integration. In Proceedings of the 2006 International Interconnect Technology Conference, Burlingame, CA, USA, 5–7 June 2006. [Google Scholar]

- Cheramy, S.; Charbonnier, J.; Henry, D.; Astier, A.; Chausse, P.; Neyret, M.; Brunet-Manquat, C.; Verrun, S.; Sillon, N.; Bonnot, L.; et al. 3D integration process flow for set-top box application: Description of technology and electrical results. In Proceedings of the 2009 European Microelectronics and Packaging Conference, Rimini, Italy, 15–18 June 2009. [Google Scholar]

- Vivet, P.; Guthmuller, E.; Thonnart, Y.; Pillonnet, G.; Moritz, G.; Miro-Panadès, I.; Fuguet, C.; Durupt, J.; Bernard, C.; Varreau, D.; et al. 2.3 A 220GOPS 96-Core Processor with 6 Chiplets 3D-Stacked on an Active Interposer Offering 0.6ns/mm Latency, 3Tb/s/mm2 Inter-Chiplet Interconnects and 156mW/mm2@ 82%-Peak-Efficiency DC-DC Converters. In Proceedings of the 2020 IEEE International Solid- State Circuits Conference-(ISSCC), San Francisco, CA, USA, 16–20 February 2020. [Google Scholar]

- Pawlowski, J.T. Hybrid memory cube (HMC). In Proceedings of the 2011 IEEE Hot Chips 23 Symposium (HCS), Stanford, CA, USA, 17–19 August 2011. [Google Scholar]

- Erofeev, E.; Arykov, V.; Stepanenko, M.; Voevodin, A.; Kogai, A.; Kurikalov, V. 28 GHz Single-Chip Transmit RF Front-End MMIC for Multichannel 5G Wireless Communications. Symmetry 2020, 12, 1167. [Google Scholar] [CrossRef]

- Shim, W.; Yu, S. Technological Design of 3D NAND-Based Compute-in-Memory Architecture for GB-Scale Deep Neural Network. IEEE Electron Device Lett. 2021, 42, 160–163. [Google Scholar] [CrossRef]

- Topol, A.W.; La Tulipe, D.C.; Shi, L.; Frank, D.J.; Bernstein, K.; Steen, S.E.; Kumar, A.; Singco, G.U.; Young, A.M.; Guarini, K.W.; et al. Three-dimensional integrated circuits. IBM J. Res. Dev. 2006, 50, 491–506. [Google Scholar] [CrossRef]

- Dang, B.; Wright, S.L.; Andry, P.S.; Sprogis, E.J.; Tsang, C.K.; Interrante, M.J.; Webb, B.C.; Polastre, R.J.; Horton, R.R.; Patel, C.S.; et al. 3D chip stacking with C4 technology. IBM J. Res. Dev. 2008, 52, 599–609. [Google Scholar] [CrossRef]

- Deguchi, J.; Sugimura, T.; Nakatani, Y.; Fukushima, T.; Koyanagi, M. Quantitative Derivation and Evaluation of Wire Length Distribution in Three-Dimensional Integrated Circuits Using Simulated Quenching. Jpn. J. Appl. Phys. 2006, 45, 3260. [Google Scholar] [CrossRef]

- Qian, L.; Qian, K.; He, X.; Chu, Z.; Ye, Y.; Shi, G.; Xia, Y. Through-Silicon Via-Based Capacitor and Its Application in LDO Regulator Design. IEEE Trans. Very Large Scale Integr. Syst. 2019, 27, 1947–1951. [Google Scholar] [CrossRef]

- Qian, L.; Xia, Y.; He, X.; Qian, K.; Wang, J. Electrical Modeling and Characterization of Silicon-Core Coaxial Through-Silicon Vias in 3-D Integration. IEEE Trans. Compon. Packag. Manuf. Technol. 2018, 8, 1336–1343. [Google Scholar] [CrossRef]

- Qu, C.; Ding, R.; Liu, X.; Zhu, Z. Modeling and Optimization of Multiground TSVs for Signals Shield in 3-D ICs. IEEE Trans. Electromagn. Compat. 2017, 59, 461–467. [Google Scholar] [CrossRef]

- Savidis, I.; Alam, S.M.; Jain, A.; Pozder, S.; Jones, R.E.; Chatterjee, R. Electrical modeling and characterization of through-silicon vias (TSVs) for 3-D integrated circuits. Microelectron. J. 2010, 41, 9–16. [Google Scholar] [CrossRef]

- Hu, J.; Wang, L.; Jin, L.; JiangNan, H.Z. Electrical modeling and characterization of through silicon vias (TSV). In Proceedings of the 2012 International Conference on Microwave and Millimeter Wave Technology (ICMMT), Shenzhen, China, 5–8 May 2012. [Google Scholar]

- Bandyopadhyay, T.; Han, K.J.; Chung, D.; Chatterjee, R.; Swaminathan, M.; Tummala, R. Rigorous Electrical Modeling of Through Silicon Vias (TSVs) With MOS Capacitance Effects. IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 893–903. [Google Scholar] [CrossRef]

- Xu, C.; Li, H.; Suaya, R.; Banerjee, K. Compact AC Modeling and Performance Analysis of Through-Silicon Vias in 3-D ICs. IEEE Trans. Electron Devices 2010, 57, 3405–3417. [Google Scholar] [CrossRef]

- Xu, Z.; Lu, J.Q. Three-Dimensional Coaxial Through-Silicon-Via (TSV) Design. IEEE Electron Device Lett. 2012, 33, 1441–1443. [Google Scholar] [CrossRef]

- Zhao, W.S.; Yin, W.Y.; Wang, X.P.; Xu, X.L. Frequency- and Temperature-Dependent Modeling of Coaxial Through-Silicon Vias for 3-D ICs. IEEE Trans. Electron Devices 2011, 58, 3358–3368. [Google Scholar] [CrossRef]

- Lu, Q.; Zhu, Z.; Liu, Y.; Liu, X.; Yin, X. Wideband Electromagnetic Modeling of Coaxial-Annular Through-Silicon Vias. IEEE Trans. Electromagn. Compat. 2018, 60, 1915–1922. [Google Scholar] [CrossRef]

- Liang, Y.; Li, Y. Closed-Form Expressions for the Resistance and the Inductance of Different Profiles of Through-Silicon Vias. IEEE Electron Device Lett. 2011, 32, 393–395. [Google Scholar] [CrossRef]

- Lu, Q.; Zhu, Z.; Yang, Y.; Ding, R. Electrical Modeling and Characterization of Shield Differential Through-Silicon Vias. IEEE Trans. Electron Devices 2015, 62, 1544–1552. [Google Scholar]

- Salah, K.; Ragai, H.; Ismail, Y.; Rouby, A.E. Equivalent lumped element models for various n-port Through Silicon Vias networks. In Proceedings of the 16th Asia and South Pacific Design Automation Conference (ASP-DAC 2011), Yokohama, Japan, 25–28 January 2011. [Google Scholar]

- Qu, C.; Ding, R.; Zhu, Z. High-Frequency Electrical Modeling and Characterization of Differential TSVs for 3-D Integration Applications. IEEE Microw. Wirel. Compon. Lett. 2017, 27, 721–723. [Google Scholar] [CrossRef]

- Fu, K.; Zhao, W.S.; Wang, G.; Swaminathan, M. Modeling and Performance Analysis of Shielded Differential Annular Through-Silicon Via (SD-ATSV) for 3-D ICs. IEEE Access 2018, 6, 33238–33250. [Google Scholar] [CrossRef]

- Su, J.; Zhang, W.; Yao, C. Partial Coaxial Through-Silicon via for Suppressing the Substrate Noise in 3-Dimensional Integrated Circuit. IEEE Access 2019, 7, 98803–98810. [Google Scholar] [CrossRef]

- Hu, Q.H.; Zhao, W.S.; Fu, K.; Wang, G. Modeling and Characterization of Differential Multibit Carbon-Nanotube Through-Silicon Vias. IEEE Trans. Compon. Packag. Manuf. Technol. 2020, 10, 534–537. [Google Scholar] [CrossRef]

- Rao, M. Electrical Modeling and Characterization of Copper/Carbon Nanotubes in Tapered through Silicon Vias. In Proceedings of the 2017 30th International Conference on VLSI Design and 2017 16th International Conference on Embedded Systems (VLSID), Hyderabad, India, 7–11 January 2017. [Google Scholar]

- Liu, X.; Zhu, Z.; Yang, Y.; Ding, R. Parasitic Inductance of Non-Uniform Through-Silicon Vias (TSVs) for Microwave Applications. IEEE Microw. Wirel. Compon. Lett. 2015, 25, 424–426. [Google Scholar] [CrossRef]

- Alam, S.M.; Jones, R.E.; Rauf, S.; Chatterjee, R. Inter-Strata Connection Characteristics and Signal Transmission in Three-Dimensional (3D) Integration Technology. In Proceedings of the 8th International Symposium on Quality Electronic Design (ISQED’07), San Jose, CA, USA, 26–28 March 2007. [Google Scholar]

- Weerasekera, R.; Grange, M.; Pamunuwa, D.; Tenhunen, H.; Zheng, L.R. Compact modelling of Through-Silicon Vias (TSVs) in three-dimensional (3-D) integrated circuits. In Proceedings of the 2009 IEEE International Conference on 3D System Integration, San Francisco, CA, USA, 28–30 September 2009. [Google Scholar]

- Katti, G.; Stucchi, M.; De Meyer, K.; Dehaene, W. Electrical Modeling and Characterization of Through Silicon via for Three-Dimensional ICs. IEEE Trans. Electron Devices 2010, 57, 256–262. [Google Scholar] [CrossRef]

- Jueping, C.; Peng, J.; Lei, Y.; Yue, H.; Zan, L. Through-silicon via (TSV) capacitance modeling for 3D NoC energy consumption estimation. In Proceedings of the 2010 10th IEEE International Conference on Solid-State and Integrated Circuit Technology, Shanghai, China, 1–4 November 2010. [Google Scholar]

- Kim, J.; Pak, J.; Cho, J.; Song, E.; Cho, J.; Kim, H.; Song, T.; Lee, J.; Lee, H.; Park, K.; et al. High-Frequency Scalable Electrical Model and Analysis of a Through Silicon Via (TSV). IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 181–195. [Google Scholar]

- Savidis, I.; Friedman, E.G. Closed-Form Expressions of 3-D Via Resistance, Inductance, and Capacitance. IEEE Trans. Electron Devices 2009, 56, 1873–1881. [Google Scholar] [CrossRef]

- Nicollian, E.H.; Brews, J.R. MOS (Metal Oxide Semiconductor) Physics and Technology; John Wiley & Sons: Somerset, NJ, USA, 2002; p. 928. [Google Scholar]

- Liao, H.Y.; Chiou, H.K. RF Model and Verification of Through-Silicon Vias in Fully Integrated SiGe Power Amplifier. IEEE Electron Device Lett. 2011, 32, 809–811. [Google Scholar] [CrossRef]

- Kim, J.; Pak, J.; Cho, J.; Lee, J.; Lee, H.; Park, K.; Kim, J. Modeling and analysis of differential signal Through Silicon Via (TSV) in 3D IC. In Proceedings of the 2010 IEEE CPMT Symposium Japan, Tokyo, Japan, 24–26 August 2010. [Google Scholar]

- Dahl, D.; Duan, X.; Ndip, I.; Lang, K.D.; Schuster, C. Efficient Computation of Localized Fields for Through Silicon Via Modeling Up to 500 GHz. IEEE Trans. Compon. Packag. Manuf. Technol. 2015, 5, 1793–1801. [Google Scholar] [CrossRef]

- Xie, B.; Swaminathan, M. FDFD Modeling of Signal Paths With TSVs in Silicon Interposer. IEEE Trans. Compon. Packag. Manuf. Technol. 2014, 4, 708–717. [Google Scholar] [CrossRef]

- Huang, C.; Liu, S.; Zhu, J.; Tang, W.; Zhuang, W. A novel modeling of TSV MOS capacitance by finite difference method. In Proceedings of the 2014 15th International Conference on Electronic Packaging Technology, Chengdu, China, 12–15 August 2014. [Google Scholar]

- Han, K.J.; Swaminathan, M.; Bandyopadhyay, T. Electromagnetic Modeling of Through-Silicon Via (TSV) Interconnections Using Cylindrical Modal Basis Functions. IEEE Trans. Adv. Packag. 2010, 33, 804–817. [Google Scholar] [CrossRef]

- Xie, J.; Swaminathan, M. DC IR drop solver for large scale 3D power delivery networks. In Proceedings of the 19th Topical Meeting on Electrical Performance of Electronic Packaging and Systems, Austin, TX, USA, 25–27 October 2010. [Google Scholar]

- Xu, Y.; Yu, W.; Chen, Q.; Jiang, L.; Wong, N. Efficient variation-aware EM-semiconductor coupled solver for the TSV structures in 3D IC. In Proceedings of the 2012 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 12–16 March 2012. [Google Scholar]

- Jain, P.; Zhou, P.; Kim, C.H.; Sapatnekar, S.S. Thermal and Power Delivery Challenges in 3D ICs. In Three Dimensional Integrated Circuit Design; Xie, Y., Cong, J., Sapatnekar, S., Eds.; Integrated Circuits and Systems; Springer: Boston, MA, USA, 2010. [Google Scholar]

- Kashfi, F.; Draper, J. Thermal sensor design for 3D ICs. In Proceedings of the 2012 IEEE 55th International Midwest Symposium on Circuits and Systems (MWSCAS), Boise, ID, USA, 5–8 August 2012. [Google Scholar]

- Choday, S.H.; Lu, C.; Raghunathan, V.; Roy, K. On-chip energy harvesting using thin-film thermoelectric materials. In Proceedings of the 29th IEEE Semiconductor Thermal Measurement and Management Symposium, San Jose, CA, USA, 17–21 March 2013. [Google Scholar]

- Bandyopadhyay, S.; Chandrakasan, A.P. Platform architecture for solar, thermal and vibration energy combining with MPPT and single inductor. In Proceedings of the 2011 Symposium on VLSI Circuits—Digest of Technical Papers, Kyoto, Japan, 15–17 June 2011. [Google Scholar]

- Zhan, Y.; Sapatnekar, S.S. High-Efficiency Green Function-Based Thermal Simulation Algorithms. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2007, 26, 1661–1675. [Google Scholar] [CrossRef]

- Huang, P.Y.; Lee, Y.M. Full-Chip Thermal Analysis for the Early Design Stage via Generalized Integral Transforms. IEEE Trans. Very Large Scale Integr. Syst. 2009, 17, 613–626. [Google Scholar] [CrossRef]

- Jain, A.; Jones, R.E. Chatterjee, S. Pozder. Analytical and Numerical Modeling of the Thermal Performance of Three-Dimensional Integrated Circuits. IEEE Trans. Compon. Packag. Technol. 2010, 33, 56–63. [Google Scholar] [CrossRef]

- Pi, Y.; Wang, W.; Jin, Y. An accurate calculation method on thermal effectiveness of TSV and wire. In Proceedings of the 2016 IEEE 18th Electronics Packaging Technology Conference (EPTC), Singapore, 30 November–3 December 2016. [Google Scholar]

- Zhao, Y.; Hao, C.; Yoshimura, T. Thermal and Wirelength Optimization With TSV Assignment for 3-D-IC. IEEE Trans. Electron Devices 2019, 66, 625–632. [Google Scholar] [CrossRef]

- Ayala, J.L.; Sridhar, A.; Cuesta, D. Thermal modeling and analysis of 3D multi-processor chips. Integration 2010, 43, 327–341. [Google Scholar] [CrossRef]

- Liu, Z.; Swarup, S.; Tan, S.X.D.; Chen, H.B.; Wang, H. Compact Lateral Thermal Resistance Model of TSVs for Fast Finite-Difference Based Thermal Analysis of 3-D Stacked ICs. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2014, 33, 1490–1502. [Google Scholar] [CrossRef]

- Lan, J.-S.; Wu, M.-L. An analytical model for thermal failure analysis of 3D IC packaging. In Proceedings of the 2014 15th International Conference on Thermal, Mechanical and Mulit-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE), Ghent, Belgium, 7–9 April 2014. [Google Scholar]

- Zhu, J.; Liu, Y.; Zhuang, W.; Tang, W. Fast thermal analysis of TSV-based 3D-ICs by GMRES with symmetric successive over-relaxation (SSOR) preconditioning. In Proceedings of the 2015 IEEE Electrical Design of Advanced Packaging and Systems Symposium (EDAPS), Seoul, Republic of Korea, 14–16 December 2015. [Google Scholar]

- Kuo, W.S.; Wang, M.; Chen, E.; Lai, J.Y.; Wang, Y.P. Thermal Investigations of 3D FCBGA Packages with TSV Technology. In Proceedings of the 2008 3rd International Microsystems, Packaging, Assembly & Circuits Technology Conference, Taipei, Taiwan, 22–24 October 2008. [Google Scholar]

- Xie, J.; Swaminathan, M. 3D transient thermal solver using non-conformal domain decomposition approach. In Proceedings of the 2012 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), San Jose, CA, USA, 5–8 November 2012. [Google Scholar]

- Wang, T.-Y.; Chen, C.C.-P. 3-D Thermal-ADI: A linear-time chip level transient thermal simulator. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2002, 21, 1434–1445. [Google Scholar] [CrossRef]

- Wang, T.-Y.; Chen, C.C.P. Thermal-ADI—A linear-time chip-level dynamic thermal-simulation algorithm based on alternating-direction-implicit (ADI) method. IEEE Trans. Very Large Scale Integr. Syst. 2003, 11, 691–700. [Google Scholar] [CrossRef]

- Fu, J.; Hou, L.; Wang, J.; Lu, B.; Zhao, W.; Yang, Y. A novel thermal-aware structure of TSV cluster. In Proceedings of the 2015 28th IEEE International System-on-Chip Conference (SOCC), Beijing, China, 8–11 September 2015. [Google Scholar]

- Hoe, Y.Y.G.; Yue, T.G.; Damaruganath, P.; Chong, C.T.; Lau, J.H.; Xiaowu, Z.; Vaidyanathan, K. Effect of TSV interposer on the thermal performance of FCBGA package. In Proceedings of the 2009 11th Electronics Packaging Technology Conference, Singapore, 9–11 December 2009. [Google Scholar]

- Todri, A.; Kundu, S.; Girard, P.; Bosio, A.; Dilillo, L.; Virazel, A. A Study of Tapered 3-D TSVs for Power and Thermal Integrity. IEEE Trans. Very Large Scale Integr. Syst. 2013, 21, 306–319. [Google Scholar] [CrossRef]

- Chiang, T.-Y.; Banerjee, K.; Saraswat, K.C. Effect of via separation and low-k dielectric materials on the thermal characteristics of Cu interconnects. In Proceedings of the International Electron Devices Meeting 2000. Technical Digest. IEDM (Cat. No.00CH37138), San Francisco, CA, USA, 10–13 December 2000. [Google Scholar]

- Goplen, B.; Sapatnekar, S.S. Placement of thermal vias in 3-D ICs using various thermal objectives. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2006, 25, 692–709. [Google Scholar] [CrossRef]

- Singh, S.G.; Tan, C.S. Thermal mitigation using thermal through silicon via (TTSV) in 3-D ICs. In Proceedings of the 2009 4th International Microsystems, Packaging, Assembly and Circuits Technology Conference, Taipei, Taiwan, 21–23 October 2009. [Google Scholar]

- Wang, X.; Yang, Y.; Chen, D.; Li, D. A High-efficiency Design Method of TSV Array for Thermal Management of 3D Integrated System. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2022; early access. [Google Scholar] [CrossRef]

- Gagan, G.C.; Singh, S.G.; Dutta, A. Optimized ttsv structure for heat mitigation and energy harvesting. In Proceedings of the 2014 12th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Guilin, China, 28–31 October 2014. [Google Scholar]

- Singh, S.; Panigrahi, A.K.; Singh, O.K.; Singh, S.G. Analysis of graphene and CNT based finned TTSV and spreaders for thermal management in 3D IC. In Proceedings of the 2016 IEEE International 3D Systems Integration Conference (3DIC), San Francisco, CA, USA, 8–11 November 2016. [Google Scholar]

- Shi, B.; Srivastava, A.; Bar-Cohen, A. Hybrid 3D-IC Cooling System Using Micro-fluidic Cooling and Thermal TSVs. In Proceedings of the 2012 IEEE Computer Society Annual Symposium on VLSI, Amherst, MA, USA, 19–21 August 2012. [Google Scholar]

- Jan, S.-R.; Chou, T.-P.; Yeh, C.-Y.; Liu, C.W.; Goldstein, R.V.; Gorodtsov, V.A.; Shushpannikov, P.S. A Compact Analytic Model of the Strain Field Induced by Through Silicon Vias. IEEE Trans. Electron Devices 2012, 59, 777–782. [Google Scholar] [CrossRef]

- Lu, K.H.; Ryu, S.-K.; Zhao, Q.; Zhang, X.; Im, J.; Huang, R.; Ho, P.S. Thermal stress induced delamination of through silicon vias in 3-D interconnects. In Proceedings of the 2010 Proceedings 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010. [Google Scholar]

- Wang, F.; Zhu, Z.; Yang, Y.; Liu, X.; Ding, R. Analytical models for the thermal strain and stress induced by annular through-silicon-via (TSV). IEICE Electron. Express 2013, 10, 20130666. [Google Scholar] [CrossRef]

- Lu, K.H.; Zhang, X.; Ryu, S.K.; Im, J.; Huang, R.; Ho, P.S. Thermo-mechanical reliability of 3-D ICs containing through silicon vias. In Proceedings of the 2009 59th Electronic Components and Technology Conference, San Diego, CA, USA, 26–29 May 2009. [Google Scholar]

- Adamshick, S.; Coolbaugh, D.; Liehr, M. Feasibility of coaxial through silicon via 3D integration. Electron. Lett. 2013, 49, 1028–1030. [Google Scholar] [CrossRef]

- Wang, F.; Zhu, Z.; Yang, Y.; Yin, X.; Liu, X.; Ding, R. An Effective Approach of Reducing the Keep-Out-Zone Induced by Coaxial Through-Silicon-Via. IEEE Trans. Electron Devices 2014, 61, 2928–2934. [Google Scholar] [CrossRef]

- Feng, W.; Bui, T.T.; Watanabe, N.; Shimamoto, H.; Aoyagi, M.; Kikuchi, K. Fabrication and stress analysis of annular-trench-isolated TSV. Microelectron. Reliab. 2016, 63, 142–147. [Google Scholar] [CrossRef]

- Ryu, S.K.; Lu, K.H.; Zhang, X.; Im, J.H.; Ho, P.S.; Huang, R. Impact of Near-Surface Thermal Stresses on Interfacial Reliability of Through-Silicon Vias for 3-D Interconnects. IEEE Trans. Device Mater. Reliab. 2011, 11, 35–43. [Google Scholar] [CrossRef]

- Liu, X.; Thadesar, P.A.; Taylor, C.L.; Kunz, M.; Tamura, N.; Bakir, M.S.; Sitaraman, S.K. Experimental Stress Characterization and Numerical Simulation for Copper Pumping Analysis of Through-Silicon Vias. IEEE Trans. Compon. Packag. Manuf. Technol. 2016, 6, 993–999. [Google Scholar] [CrossRef]

- Dong, G.; Shi, T.; Zhao, Y.-B.; Yang, Y.-T. An analytical model of thermal mechanical stress induced by through silicon via. Chinese Phys. B 2015, 24, 5. [Google Scholar] [CrossRef]

- Dequivre, T.; Kolhatkar, G.; Youssef, A.; Le, X.T.; Brisard, G.M.; Ruediger, A.; Charlebois, S.A. Wet Metallization of High Aspect Ratio TSV Using Electrografted Polymer Insulator to Suppress Residual Stress in Silicon. IEEE Trans. Device Mater. Reliab. 2017, 17, 514–521. [Google Scholar] [CrossRef]

- Heryanto, A.; Putra, W.N.; Trigg, A.D.; Gao, S.; Kwon, W.; Che, F.; Ang, X.; Wei, J.; Made, R.; Gan, C.; et al. Effect of Copper TSV Annealing on Via Protrusion for TSV Wafer Fabrication. J. Electron. Mater. 2012, 41, 2533–2542. [Google Scholar] [CrossRef]

- Su, F.; Lan, T.; Pan, X. Stress evaluation of Through-Silicon Vias using micro-infrared photoelasticity and finite element analysis. Opt. Lasers Eng. 2015, 74, 87–93. [Google Scholar] [CrossRef]

- Kim, J.H.; Han, S.M.J.; Yoo, W.S. Multiwavelength Raman characterization of silicon stress near through-silicon vias and its inline monitoring applications. J. Micro/Nanolithography MEMS MOEMS 2014, 13, 011205. [Google Scholar]

- Zhao, X.; Ma, L.; Wang, Y.; Guo, F. Effect of Thermal Mechanical Behaviors of Cu on Stress Distribution in Cu-Filled Through-Silicon Vias Under Heat Treatment. J. Electron. Mater. 2018, 47, 142–147. [Google Scholar] [CrossRef]

- Zhang, C.; Li, L. Characterization and Design of Through-Silicon Via Arrays in Three-Dimensional ICs Based on Thermomechanical Modeling. IEEE Trans. Electron Devices 2011, 58, 279–287. [Google Scholar] [CrossRef]

- Wang, X.P.; Zhao, W.; Yin, W.Y. Electrothermal modelling of through silicon via (TSV) interconnects. In Proceedings of the 2010 IEEE Electrical Design of Advanced Package & Systems Symposium, Singapore, 7–9 December 2010. [Google Scholar]

- Zhao, W.S.; Wang, X.P.; Xu, X.L.; Yin, W.Y. Electrothermal modeling of coaxial through silicon via (TSV) for three-dimensional ICs. In Proceedings of the 2010 IEEE Electrical Design of Advanced Package & Systems Symposium, Singapore, 7–9 December 2010. [Google Scholar]

- Katti, G.; Stucchi, M.; Velenis, D.; Soree, B.; De Meyer, K.; Dehaene, W. Temperature-Dependent Modeling and Characterization of Through-Silicon Via Capacitance. IEEE Electron Device Lett. 2011, 32, 563–565. [Google Scholar] [CrossRef]

- Wang, X.P.; Yin, W.Y.; He, S. Multiphysics Characterization of Transient Electrothermomechanical Responses of Through-Silicon Vias Applied With a Periodic Voltage Pulse. IEEE Trans. Electron Devices 2010, 57, 1382–1389. [Google Scholar] [CrossRef]

- Lu, T.; Jin, J.M. Electrical-Thermal Co-Simulation for DC IR-Drop Analysis of Large-Scale Power Delivery. IEEE Trans. Compon. Packag. Manuf. Technol. 2014, 4, 323–331. [Google Scholar] [CrossRef]

- Lu, T.; Jin, J.M. Thermal-Aware High-Frequency Characterization of Large-Scale Through-Silicon-Via Structures. IEEE Trans. Compon. Packag. Manuf. Technol. 2014, 4, 1015–1025. [Google Scholar] [CrossRef]

- Lu, T.; Jin, J.M. Transient Electrical-Thermal Analysis of 3-D Power Distribution Network With FETI-Enabled Parallel Computing. IEEE Trans. Compon. Packag. Manuf. Technol. 2014, 4, 1684–1695. [Google Scholar]

- Sai, M.P.D.; Yu, H.; Shang, Y.; Tan, C.S.; Lim, S.K. Reliable 3-D Clock-Tree Synthesis Considering Nonlinear Capacitive TSV Model With Electrical–Thermal–Mechanical Coupling. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2013, 32, 1734–1747. [Google Scholar] [CrossRef]

- Jiang, L.; Xu, C.; Rubin, B.J.; Weger, A.J.; Deutsch, A.; Smith, H.; Caron, A.; Banerjee, K. A Thermal Simulation Process Based on Electrical Modeling for Complex Interconnect, Packaging, and 3DI Structures. IEEE Trans. Adv. Packag. 2010, 33, 777–786. [Google Scholar] [CrossRef]

| Ref. | Maximum Errors | |||

|---|---|---|---|---|

| R | L | G | C | |

| Savidis et al. [13] | 8% | 8% | 8% | 8% |

| Lu et al. [19] | 6.5% | 1.7% | 5.5% | 1.8% |

| Liang et al. [20] | 2% | 5% | - | - |

| Salah et al. [22] | 6% | 6% | - | 6% |

| Liu et al. [28] | - | 8% | - | - |

| Weerasekera et al. [30] | 2% | 3% | - | 6% |

| Katti et al. [31] | - | - | - | 3.52% |

| Cai et al. [32] | - | - | - | 10.1% |

| Closed-Form Expressions | Reference |

| [32] | |

| [20] | |

| [33] | |

| [20] | |

| [31] | |

| [34] | |

| [20] | |

| [30] | |

| [34] | |

| [20] | |

| [35] | |

| [36] | |

| [30] | |

| [22] | |

| [31] | |

| [22] | |

| [37] | |

| [37] | |

| [37] |

| Models | Advantages | Limitations |

|---|---|---|

| Analytical model | Simple and easy; Low computational complexity; High computing efficiency. | Limited parameters for analysis; Low precision. |

| FDM | Theoretical perfection; Applicable to various accuracies; Easy to compute in parallel. | Complicated dealing with irregular areas; Poor adaptability to grids. |

| FEM | High precision; Multiple parameters for analysis; Easier to handle irregular areas; Easy to compute boundaries; Good adaptability to grids. | Low computing efficiency; High computational complexity; High computational memory consumption. |

| FVM | Good conservativeness; Good adaptability to grids. | Complicated computing boundary; High computational memory consumption; Low simulation efficiency. |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, X.; Chen, D.; Li, D.; Kou, C.; Yang, Y. The Development and Progress of Multi-Physics Simulation Design for TSV-Based 3D Integrated System. Symmetry 2023, 15, 418. https://doi.org/10.3390/sym15020418

Wang X, Chen D, Li D, Kou C, Yang Y. The Development and Progress of Multi-Physics Simulation Design for TSV-Based 3D Integrated System. Symmetry. 2023; 15(2):418. https://doi.org/10.3390/sym15020418

Chicago/Turabian StyleWang, Xianglong, Dongdong Chen, Di Li, Chen Kou, and Yintang Yang. 2023. "The Development and Progress of Multi-Physics Simulation Design for TSV-Based 3D Integrated System" Symmetry 15, no. 2: 418. https://doi.org/10.3390/sym15020418

APA StyleWang, X., Chen, D., Li, D., Kou, C., & Yang, Y. (2023). The Development and Progress of Multi-Physics Simulation Design for TSV-Based 3D Integrated System. Symmetry, 15(2), 418. https://doi.org/10.3390/sym15020418