Experimental Investigation on the Electrical Properties of DPPT-TT Polymer Field-Effect Transistors Featuring Stair Gate Dielectric

Abstract

1. Introduction

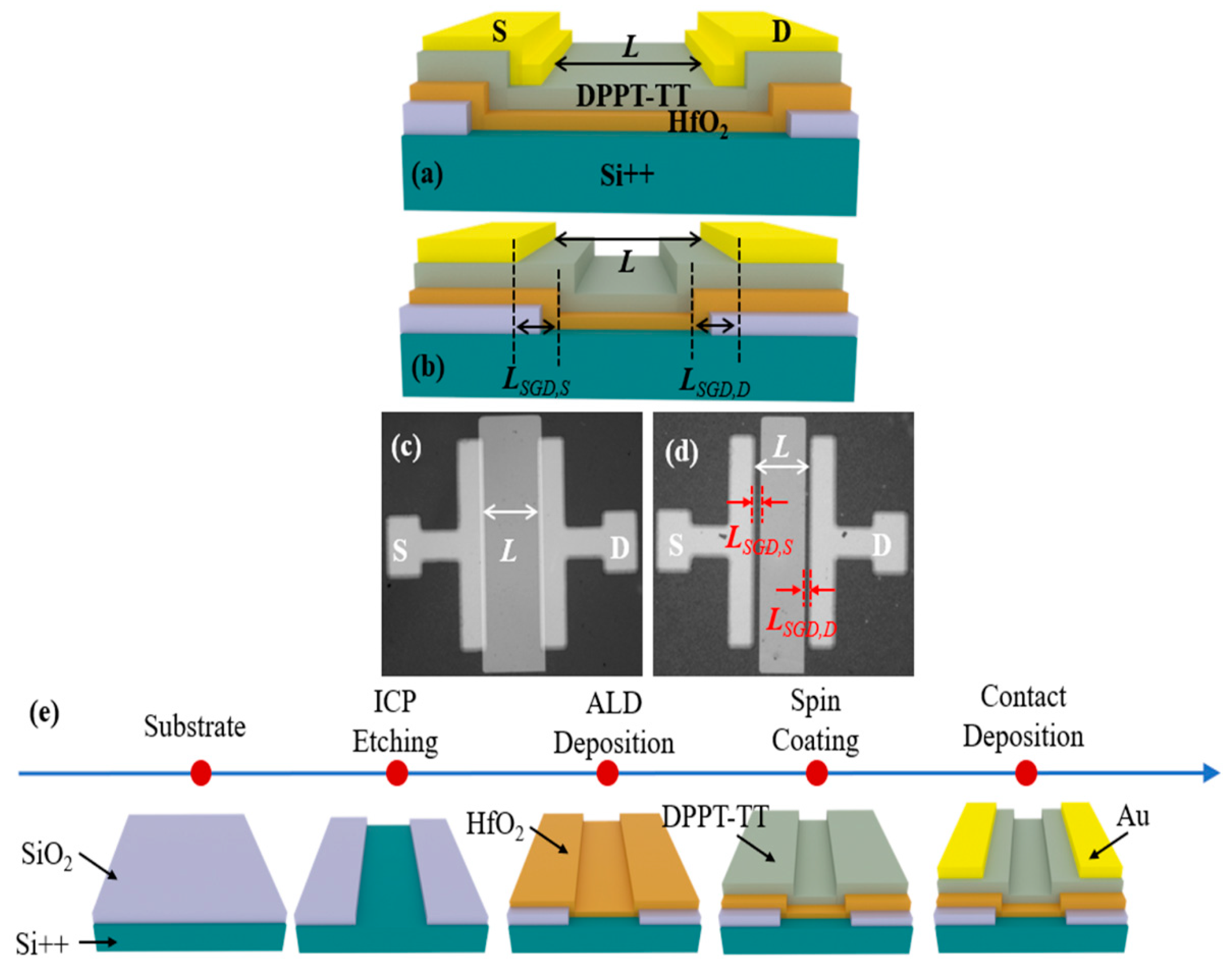

2. Experimental Section

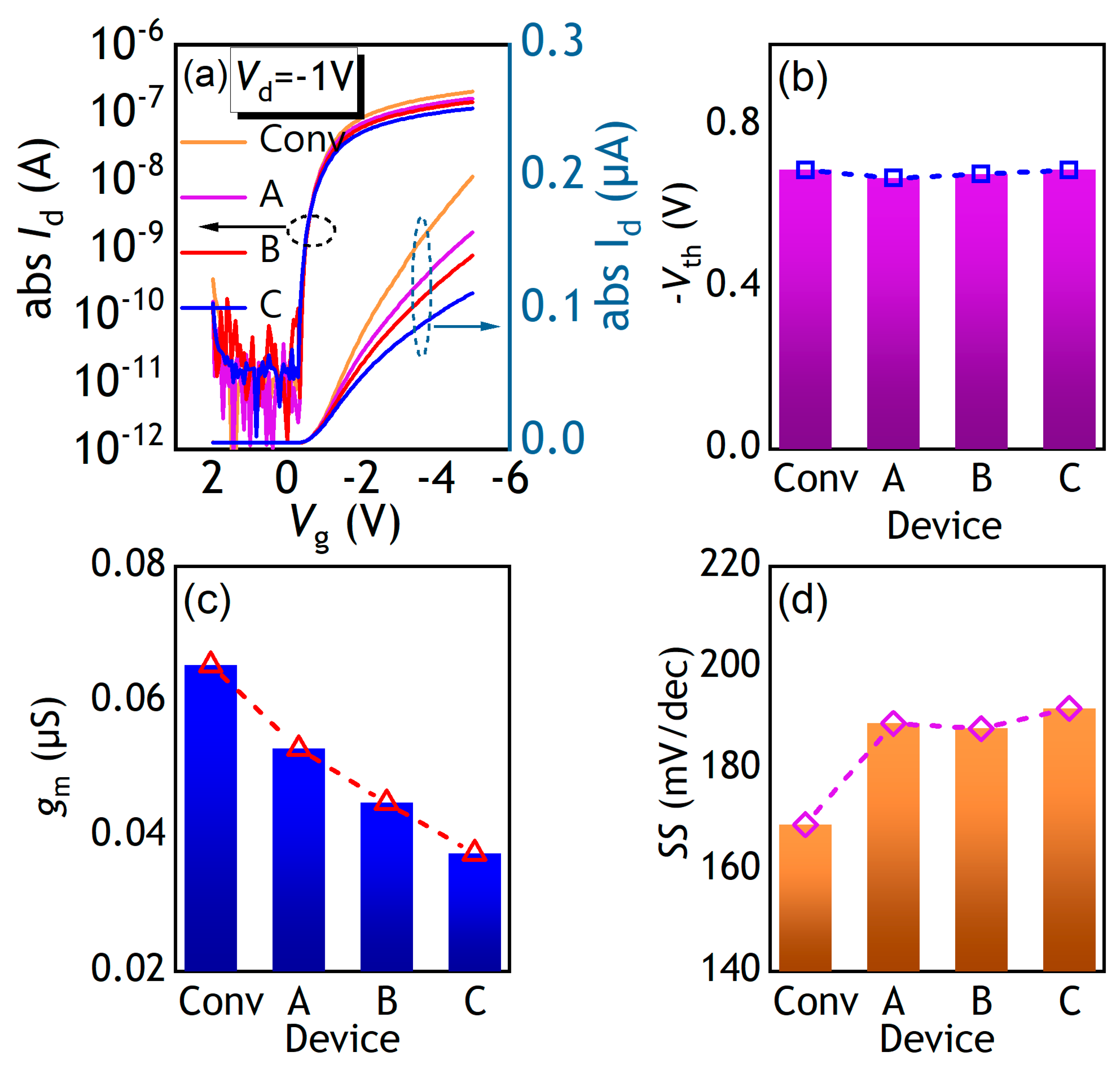

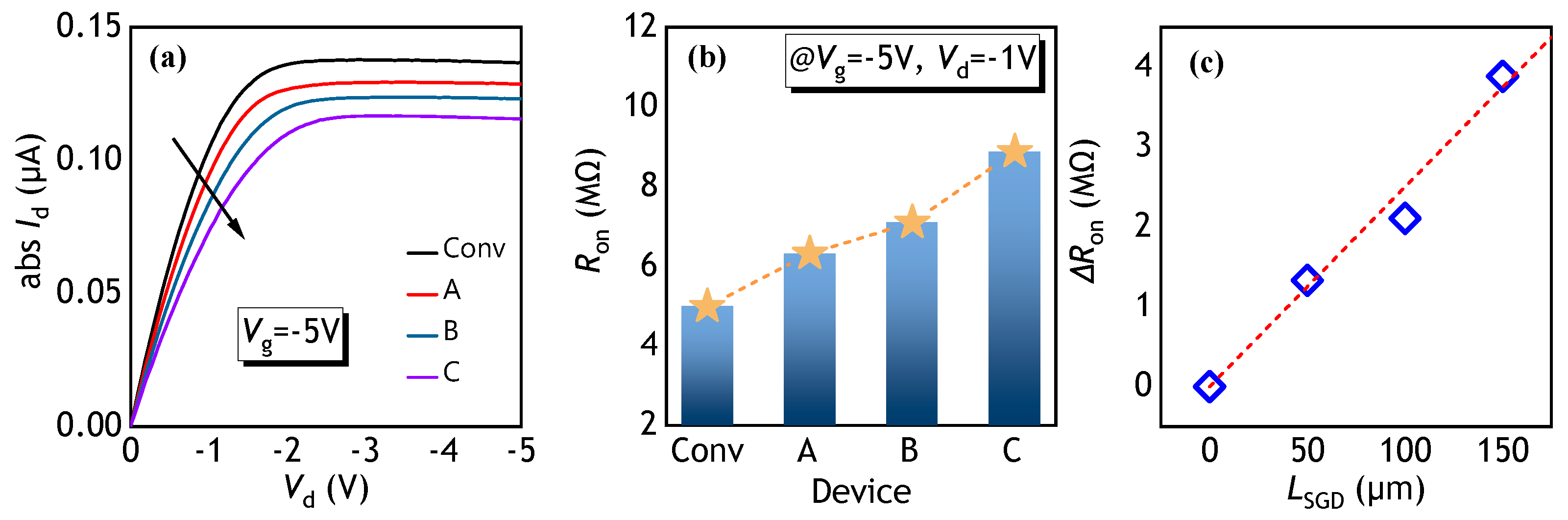

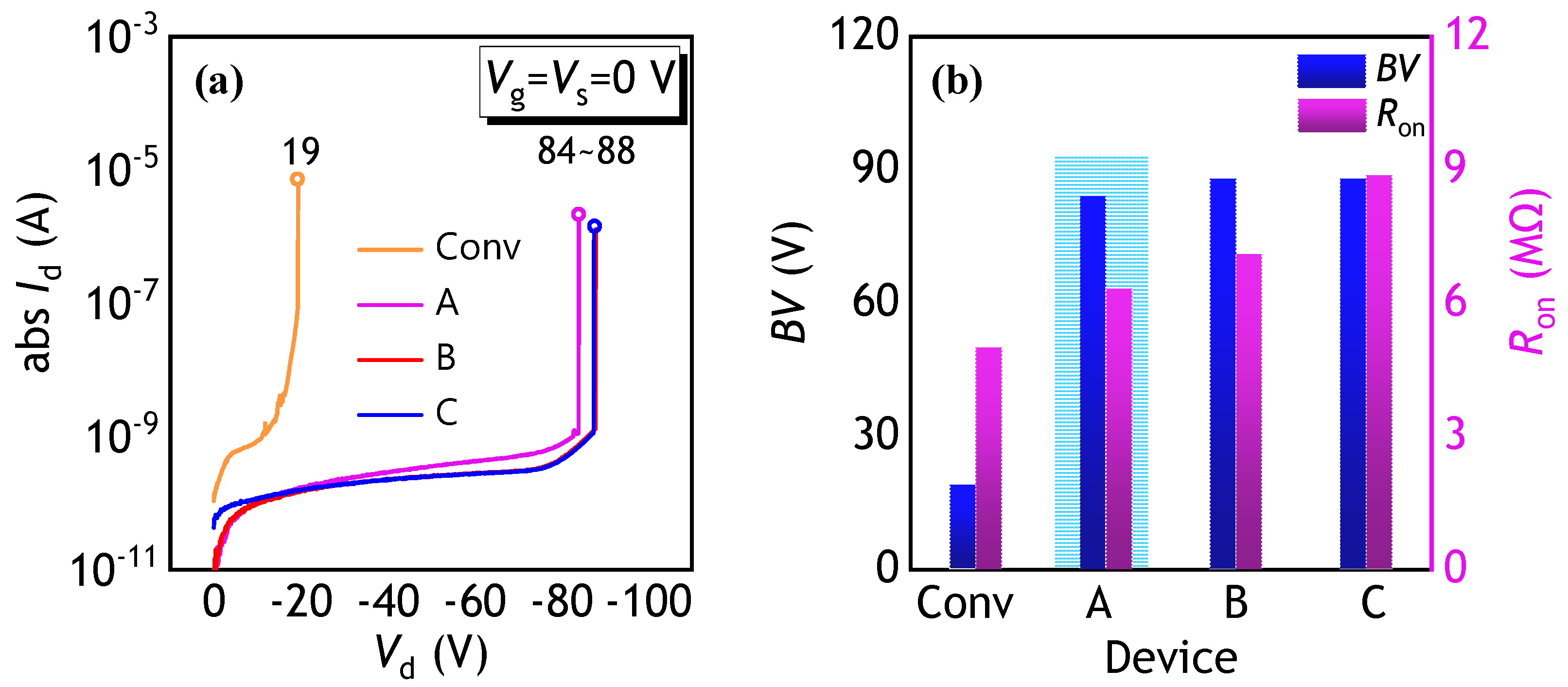

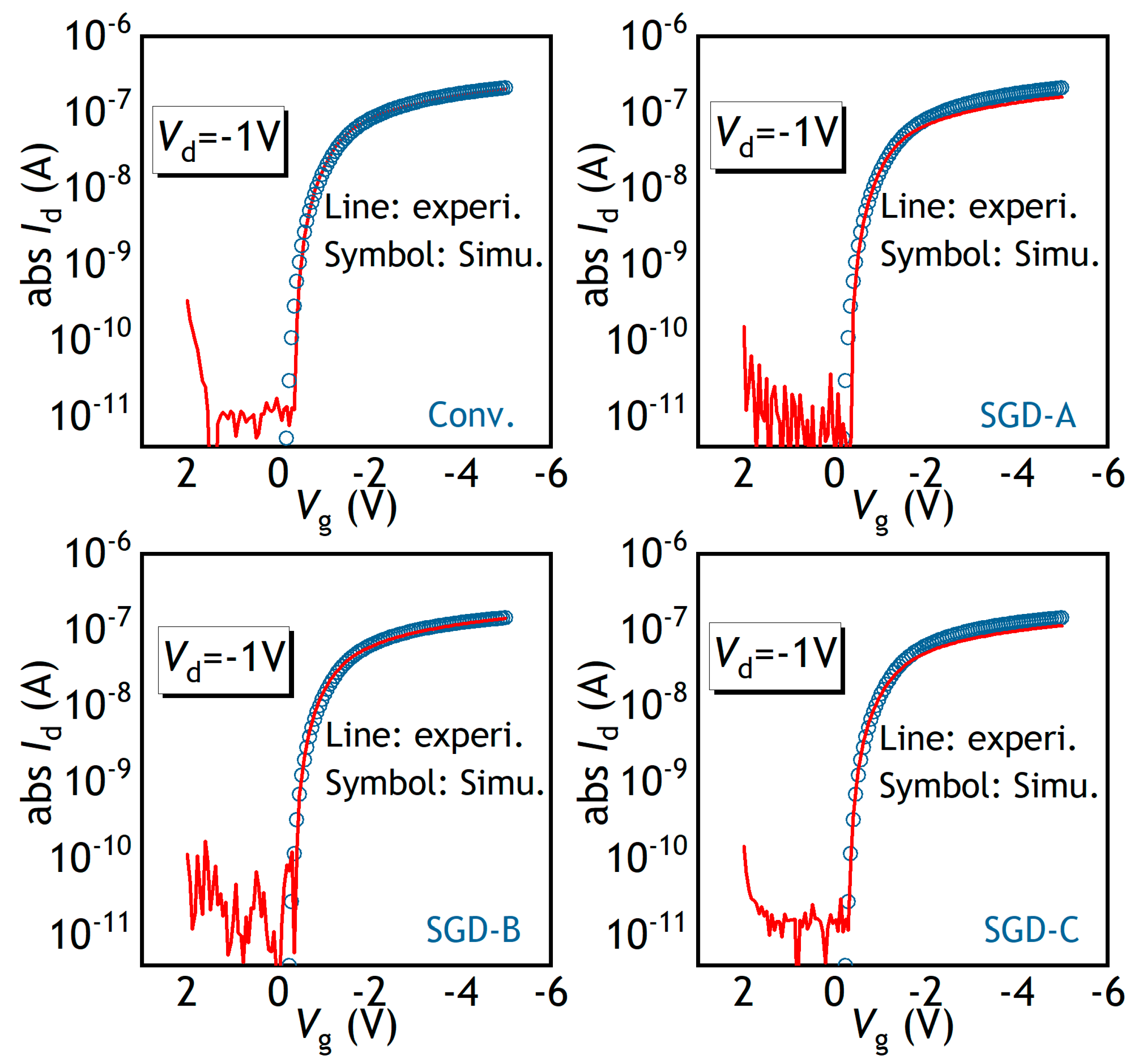

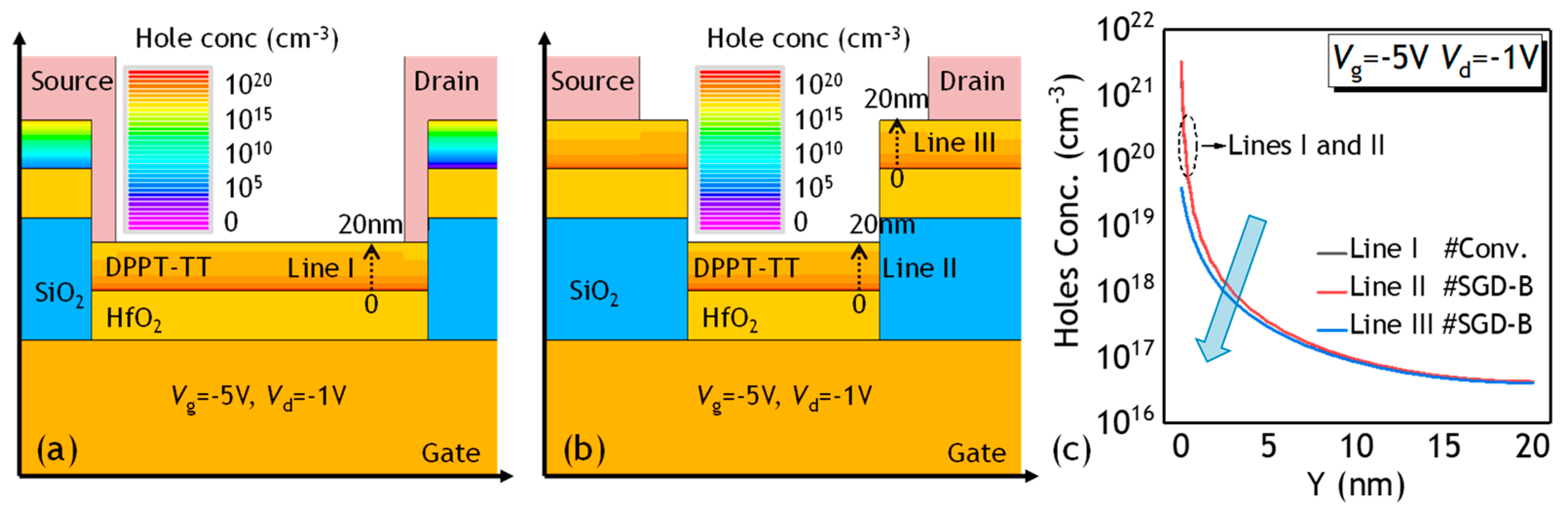

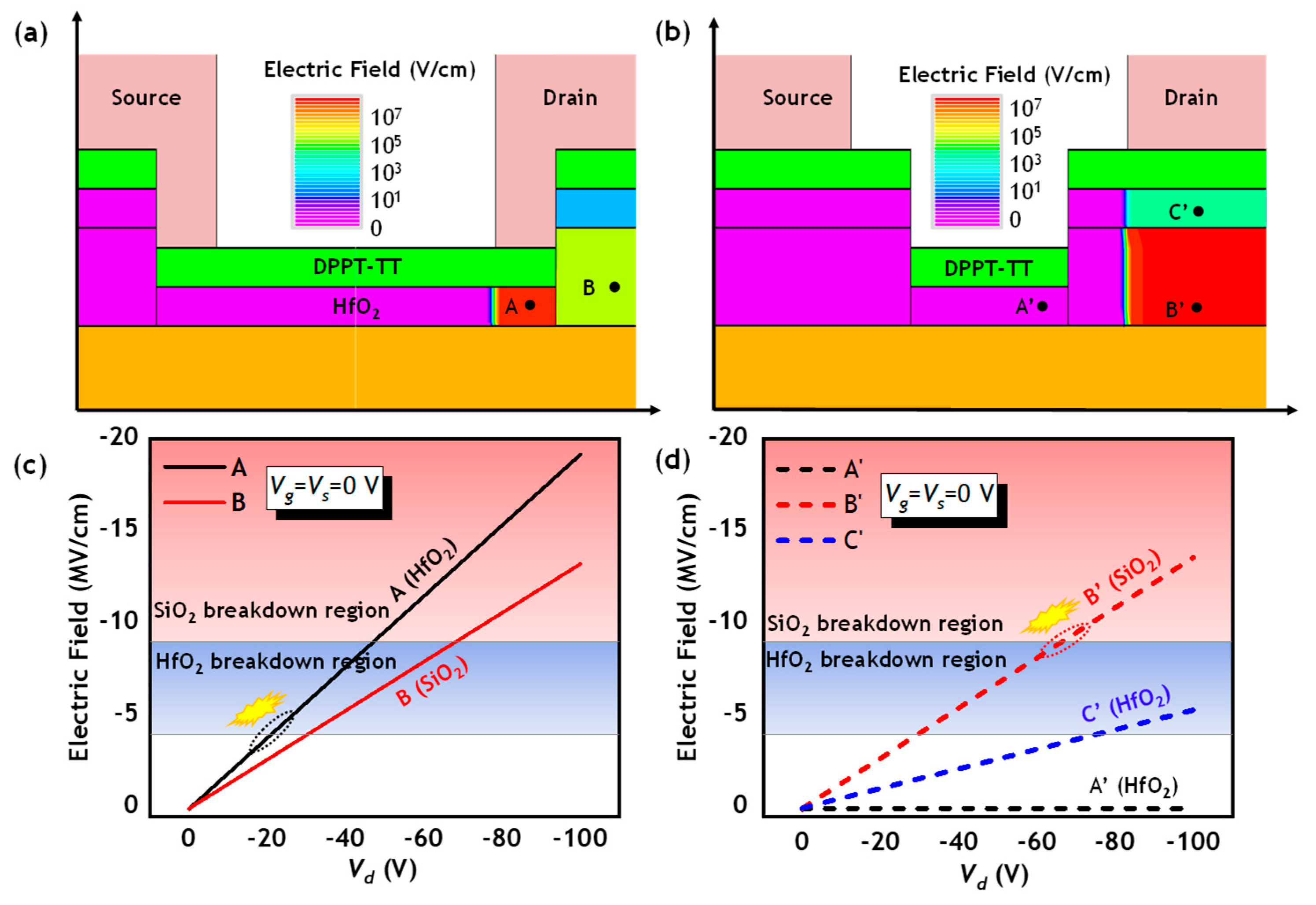

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Harikesh, P.C.; Yang, C.-Y.; Tu, D.; Gerasimov, J.Y.; Dar, A.M.; Armada-Moreira, A.; Massetti, M.; Kroon, R.; Bliman, D.; Olsson, R.; et al. Organic electrochemical neurons and synapses with ion mediated spiking. Nat. Commun. 2022, 13, 901. [Google Scholar] [CrossRef] [PubMed]

- Su, Y.; Geng, D.; Chen, Q.; Ji, H.; Li, M.; Shang, G.; Liu, L.; Duan, X.; Chuai, X.; Huang, S.; et al. Novel TFT-Based emission driver in high performance AMOLED display applications. Org. Electron. 2021, 93, 106160. [Google Scholar] [CrossRef]

- Petritz, A.; Karner-Petritz, E.; Uemura, T.; Schäffner, P.; Araki, T.; Stadlober, B.; Sekitani, T. Imperceptible energy harvesting device and biomedical sensor based on ultraflexible ferroelectric transducers and organic diodes. Nat. Commun. 2021, 12, 2399. [Google Scholar] [CrossRef] [PubMed]

- Wu, Z.; Yin, H.; Li, G.; Ji, Z. Recent progress in semitransparent organic solar cells. Org. Electron. 2024, 129, 107060. [Google Scholar] [CrossRef]

- Shiwaku, R.; Matsui, H.; Nagamine, K.; Uematsu, M.; Mano, T.; Maruyama, Y.; Nomura, A.; Tsuchiya, K.; Hayasaka, K.; Takeda, Y.; et al. A Printed Organic Circuit System for Wearable Amperometric Electrochemical Sensors. Sci. Rep. 2018, 8, 6368. [Google Scholar] [CrossRef] [PubMed]

- Wu, W.; Geng, D.; Chen, C.; Chuai, X.; Li, S.; Lu, N.; Li, L. High-speed, low-voltage, small-pitch and robust OTFT-based integrated gate driver for active-matrix displays. Org. Electron. 2024, 124, 106939. [Google Scholar] [CrossRef]

- Li, M.; Zheng, J.; Wang, X.; Yu, R.; Wang, Y.; Qiu, Y.; Cheng, X.; Wang, G.; Chen, G.; Xie, K.; et al. Light-responsive self-strained organic semiconductor for large flexible OFET sensing array. Nat. Commun. 2022, 13, 4912. [Google Scholar] [CrossRef] [PubMed]

- Chen, X.; Wang, Z.; Qi, J.; Hu, Y.; Huang, Y.; Sun, S.; Sun, Y.; Gong, W.; Luo, L.; Zhang, L.; et al. Balancing the film strain of organic semiconductors for ultrastable organic transistors with a five-year lifetime. Nat. Commun. 2022, 13, 1480. [Google Scholar] [CrossRef] [PubMed]

- Bharti, D.; Raghuwanshi, V.; Varun, I.; Mahato, A.K.; Tiwari, S.P. High Performance and Electro-Mechanical Stability in Small Molecule: Polymer Blend Flexible Organic Field-Effect Transistors. IEEE Electron. Device Lett. 2016, 37, 1215–1218. [Google Scholar] [CrossRef]

- Knopfmacher, O.; Hammock, M.L.; Appleton, A.L.; Schwartz, G.; Mei, J.; Lei, T.; Pei, J.; Bao, Z. Highly stable organic polymer field-effect transistor sensor for selective detection in the marine environment. Nat. Commun. 2014, 5, 2954. [Google Scholar] [CrossRef] [PubMed]

- Bilgaiyan, A.; Cho, S.-I.; Abiko, M.; Watanabe, K.; Mizukami, M. Flexible, high mobility short-channel organic thin film transistors and logic circuits based on 4H–21DNTT. Sci. Rep. 2021, 11, 11710. [Google Scholar] [CrossRef] [PubMed]

- Luo, Z.; Peng, B.; Zeng, J.; Yu, Z.; Zhao, Y.; Xie, J.; Lan, R.; Ma, Z.; Pan, L.; Cao, K.; et al. Sub-thermionic, ultra-high-gain organic transistors and circuits. Nat. Commun. 2021, 12, 1928. [Google Scholar] [CrossRef] [PubMed]

- Ogier, S.D.; Matsui, H.; Feng, L.; Simms, M.; Mashayekhi, M.; Carrabina, J.; Terés, L.; Tokito, S. Uniform, high performance, solution processed organic thin-film transistors integrated in 1 MHz frequency ring oscillators. Org. Electron. 2018, 54, 40–47. [Google Scholar] [CrossRef]

- Kjellander, B.K.C.; Smaal, W.T.T.; Myny, K.; Genoe, J.; Dehaene, W.; Heremans, P.; Gelinck, G.H. Optimized circuit design for flexible 8-bit RFID transponders with active layer of ink-jet printed small molecule semiconductors. Org. Electron. 2013, 14, 768–774. [Google Scholar] [CrossRef]

- Ran, W.; Ren, Z.; Wang, P.; Yan, Y.; Zhao, K.; Li, L.; Li, Z.; Wang, L.; Yang, J.; Wei, Z.; et al. Integrated polarization-sensitive amplification system for digital information transmission. Nat. Commun. 2021, 12, 6476. [Google Scholar] [CrossRef] [PubMed]

- Romanuik, S.F.; Rout, B.; Girard-Lauriault, P.-L.; Bhadra, S. Resolving Unusual Gate Current and Dielectric Breakdown of Solution Processed Carbon Nanotube Thin Film Transistor. In Proceedings of the 2022 IEEE International Symposium on Circuits and Systems (ISCAS), Austin, TX, USA, 27 May–1 June 2022; pp. 2008–2011. [Google Scholar]

- Zhang, J.; Zhou, J.; Wang, Y.; Li, M.; Du, L.; Chen, J.; Zhang, M.; Yao, J.; Zhang, G.; Sun, H.; et al. A 2.2kV Organic Semiconductor- Based Lateral Power Device. IEEE Electron. Device Lett. 2022, 43, 276–279. [Google Scholar] [CrossRef]

- Huseynova, G.; Xu, Y.; Nketia Yawson, B.; Shin, E.-Y.; Lee, M.J.; Noh, Y.-Y. P-type doped ambipolar polymer transistors by direct charge transfer from a cationic organic dye Pyronin B ferric chloride. Org. Electron. 2016, 39, 229–235. [Google Scholar] [CrossRef]

- Lüssem, B.; Keum, C.-M.; Kasemann, D.; Naab, B.; Bao, Z.; Leo, K. Doped Organic Transistors. Chem. Rev. 2016, 116, 13714–13751. [Google Scholar] [CrossRef] [PubMed]

- Jang, J.; Song, Y.; Yoo, D.; Kim, T.-Y.; Jung, S.-H.; Hong, S.; Lee, J.-K.; Lee, T. Micro-scale twistable organic field effect transistors and complementary inverters fabricated by orthogonal photolithography on flexible polyimide substrate. Org. Electron. 2014, 15, 2822–2829. [Google Scholar] [CrossRef]

- Lee, S.; Nathan, A. Conduction Threshold in Accumulation-Mode InGaZnO Thin Film Transistors. Sci. Rep. 2016, 6, 22567. [Google Scholar] [CrossRef] [PubMed]

- Silvaco International. Atlas User’s Manual; Silvaco International: Santa Clara, CA, USA, 2019; pp. 1–1797. [Google Scholar]

| Device | Conv | A | B | C |

|---|---|---|---|---|

| tHfO2 (nm) | 20 | 20 | 20 | 20 |

| tSiO2 (nm) | / | 50 | 50 | 50 |

| LSGD (μm) | / | 50 | 100 | 150 |

| Energy band gap (eV) | 1.26 |

| Electron affinity (eV) | 4.07 |

| Effective density of states (HOMO) (cm−3) | 1.0 × 1021 |

| Effective density of states (LUMO) (cm−3) | 1.0 × 1021 |

| Permittivity of HfO2 | 21 |

| Permittivity of SiO2 | 3.9 |

| Work function of contacts (eV) | 5.1 |

| NTD (cm−3eV−1) | WTD (eV) | NGD (cm−3eV−1) | WGD (eV) | EGD (eV) |

|---|---|---|---|---|

| 1.0 × 1018 | 0.1 | 1.0 × 1016 | 0.1 | 0.4 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhu, H.; Qian, Y.; Yan, Y.; Chen, L.; Chen, Q.; Sun, H.; Xu, Y.; Yang, G. Experimental Investigation on the Electrical Properties of DPPT-TT Polymer Field-Effect Transistors Featuring Stair Gate Dielectric. Polymers 2025, 17, 289. https://doi.org/10.3390/polym17030289

Zhu H, Qian Y, Yan Y, Chen L, Chen Q, Sun H, Xu Y, Yang G. Experimental Investigation on the Electrical Properties of DPPT-TT Polymer Field-Effect Transistors Featuring Stair Gate Dielectric. Polymers. 2025; 17(3):289. https://doi.org/10.3390/polym17030289

Chicago/Turabian StyleZhu, Hong, Yi Qian, Yu Yan, Lijian Chen, Quanhua Chen, Huabin Sun, Yong Xu, and Guangan Yang. 2025. "Experimental Investigation on the Electrical Properties of DPPT-TT Polymer Field-Effect Transistors Featuring Stair Gate Dielectric" Polymers 17, no. 3: 289. https://doi.org/10.3390/polym17030289

APA StyleZhu, H., Qian, Y., Yan, Y., Chen, L., Chen, Q., Sun, H., Xu, Y., & Yang, G. (2025). Experimental Investigation on the Electrical Properties of DPPT-TT Polymer Field-Effect Transistors Featuring Stair Gate Dielectric. Polymers, 17(3), 289. https://doi.org/10.3390/polym17030289