Numerical Simulation of the Effect of APCVD Reactor Tilted Ceiling Height on Silicon Epitaxial Layer Thickness Uniformity

Abstract

1. Introduction

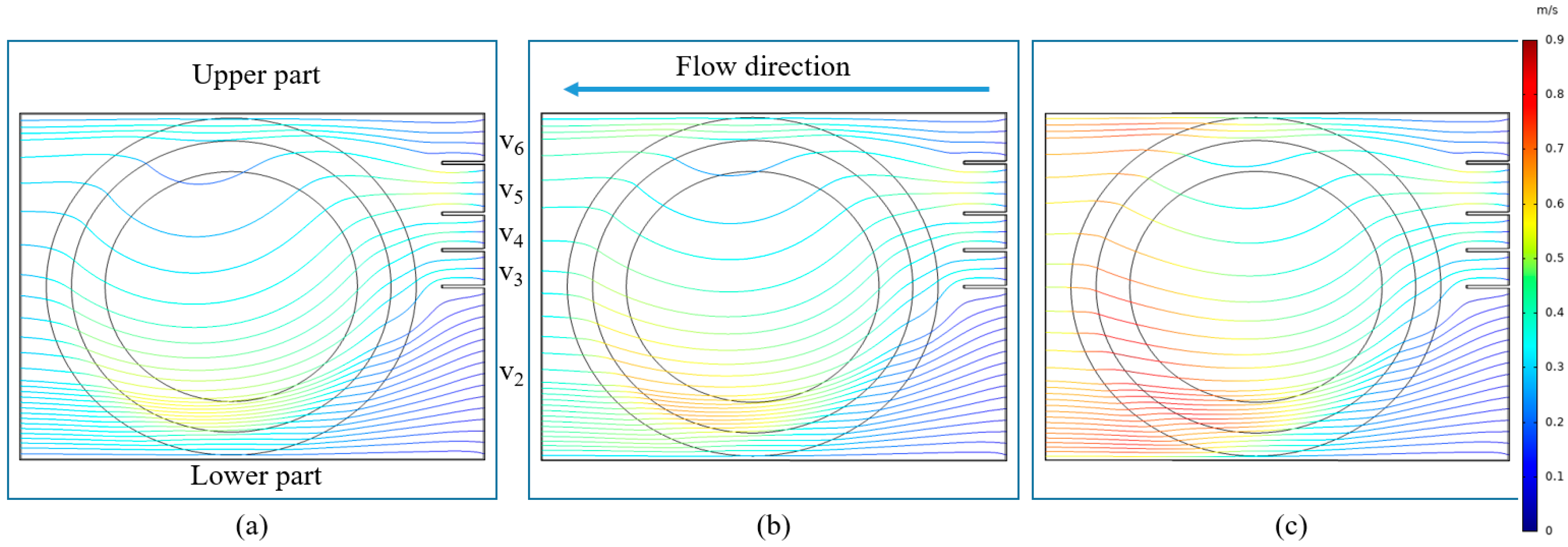

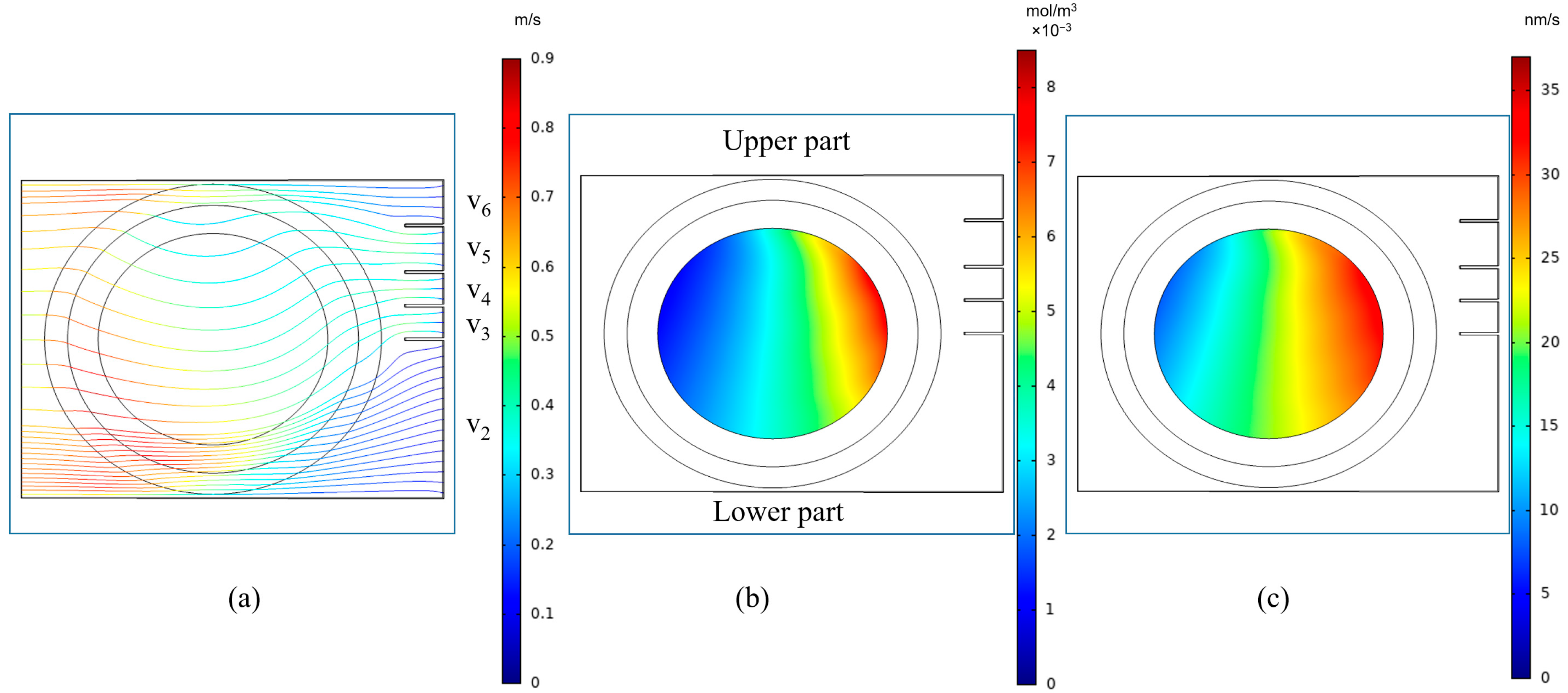

2. Physical System, Governing Equations, and Mathematical Formulation

2.1. Governing Equations

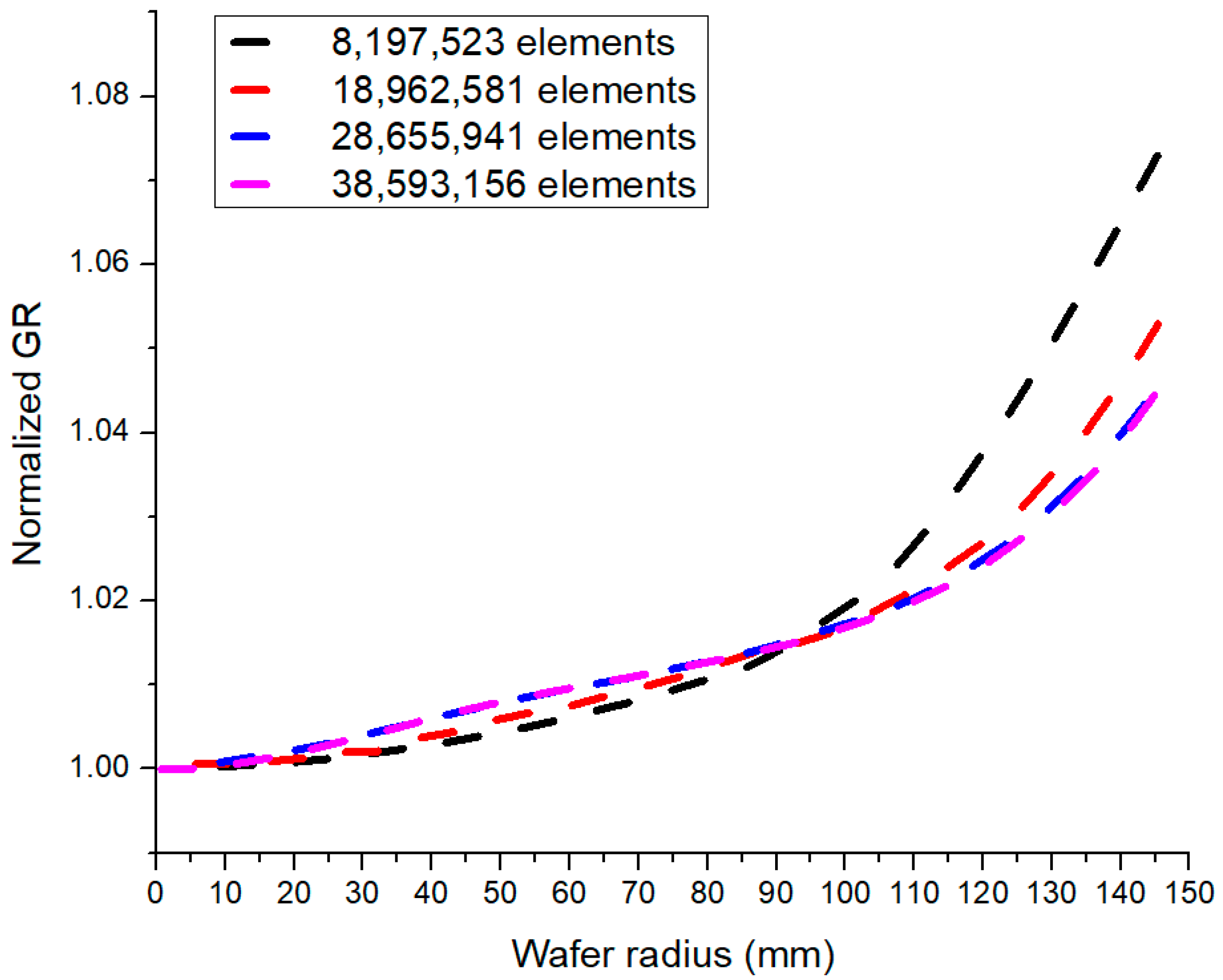

2.2. Numerical Procedure

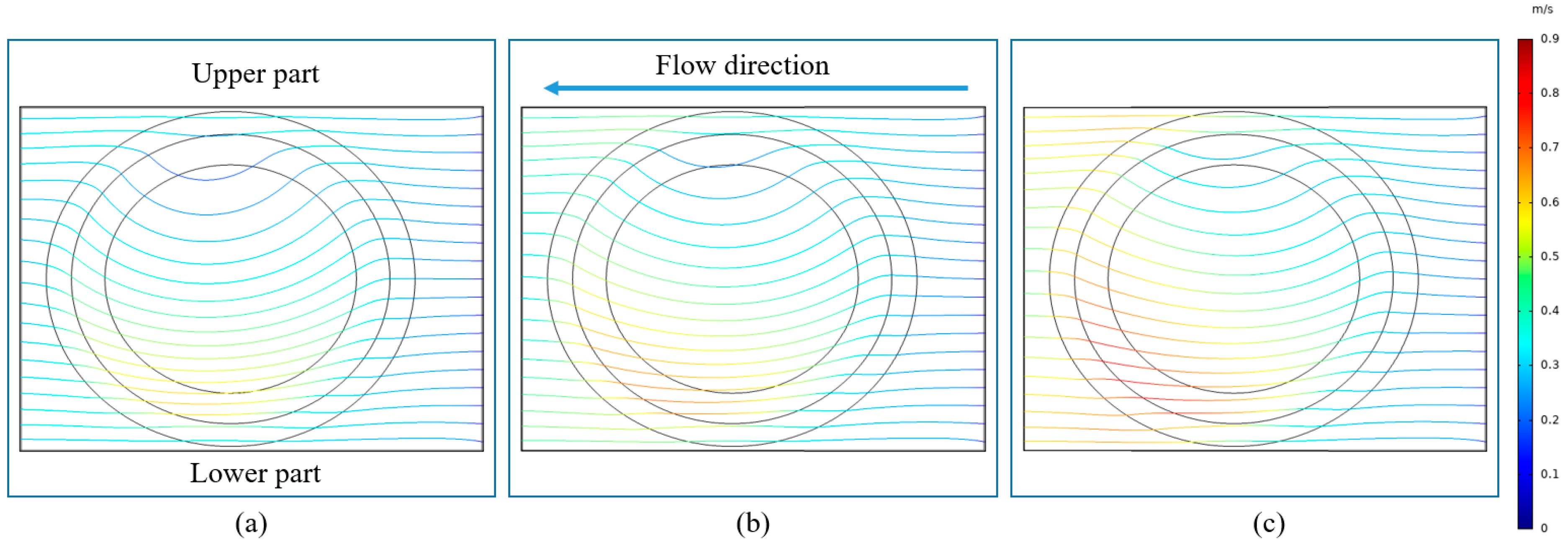

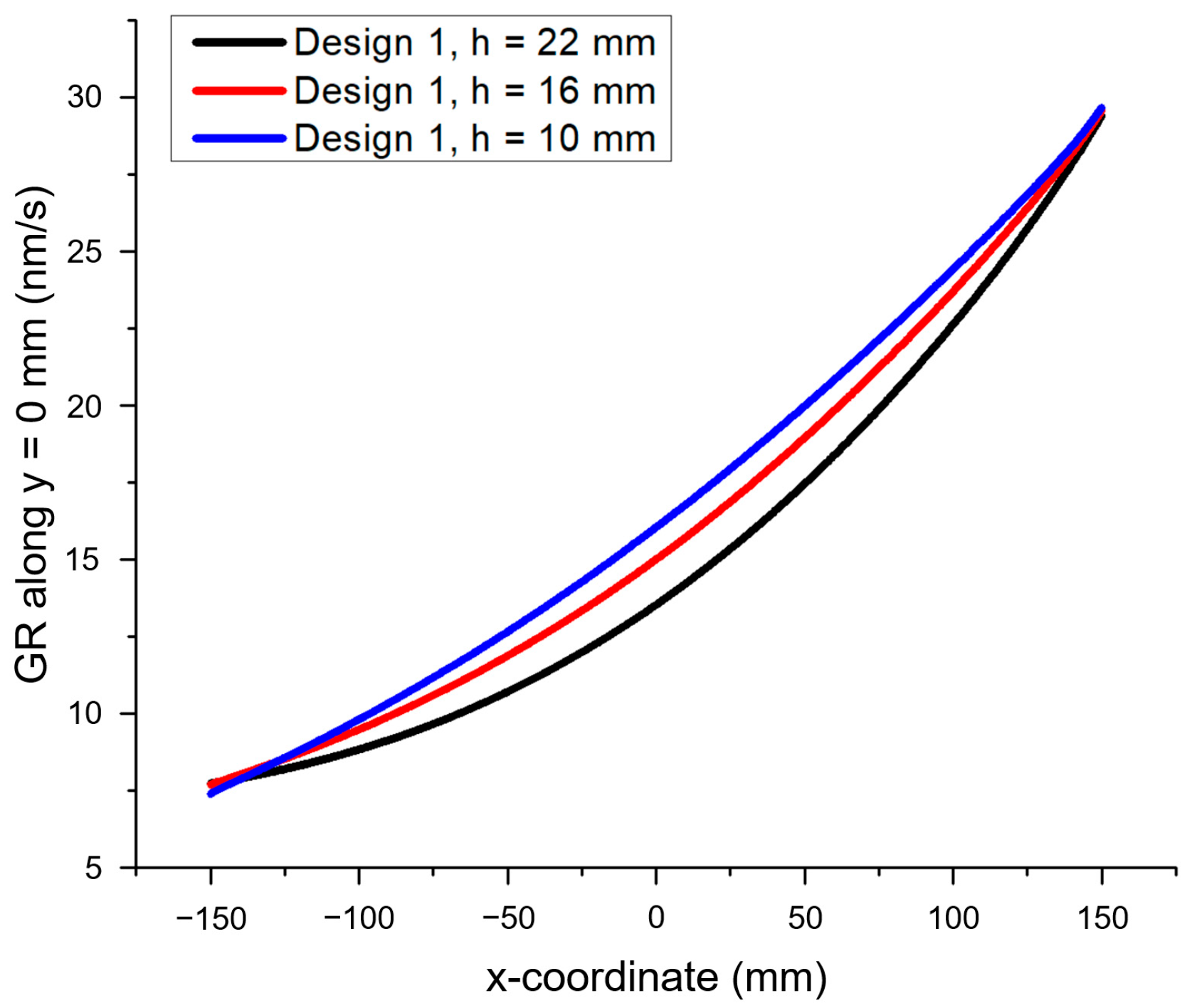

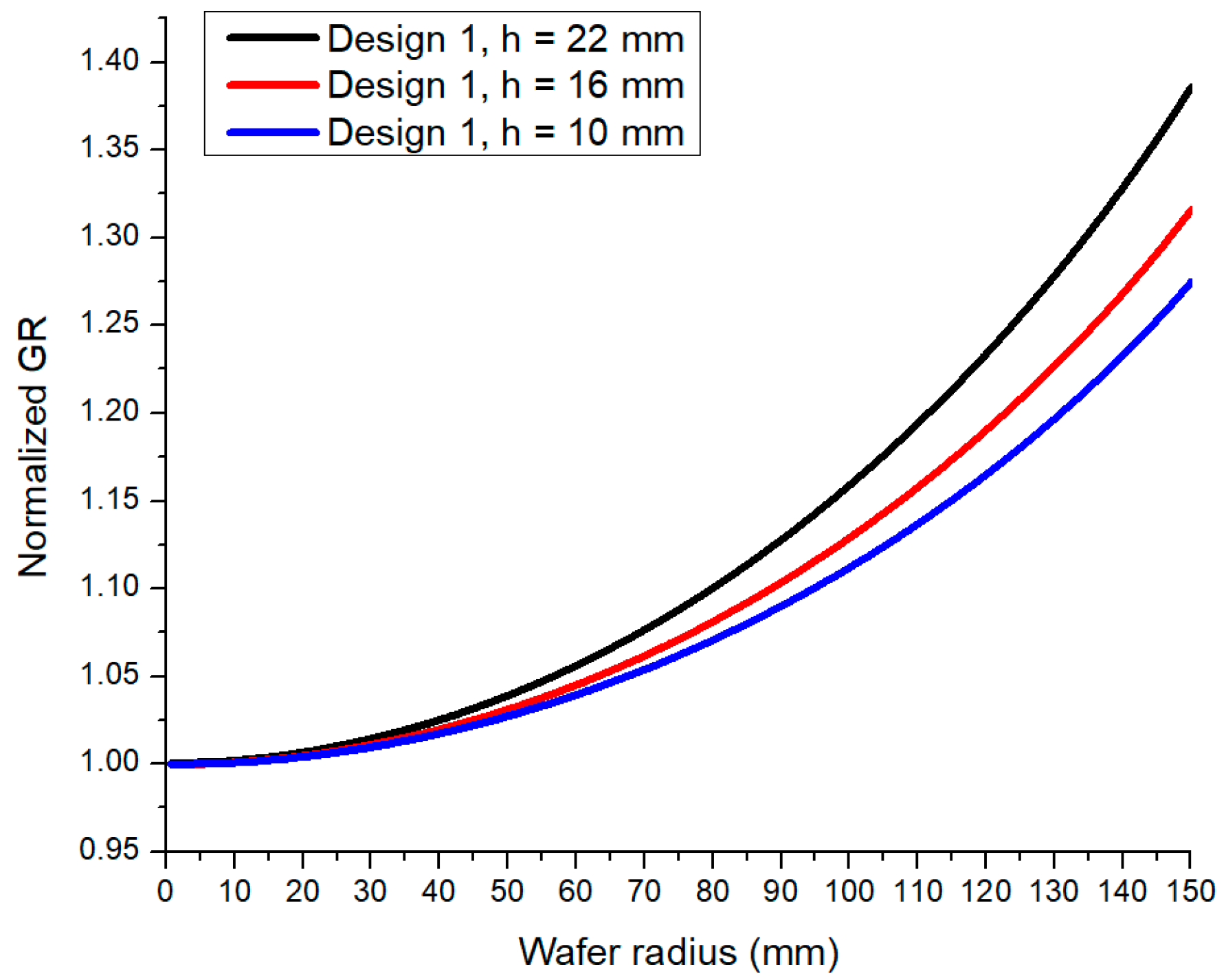

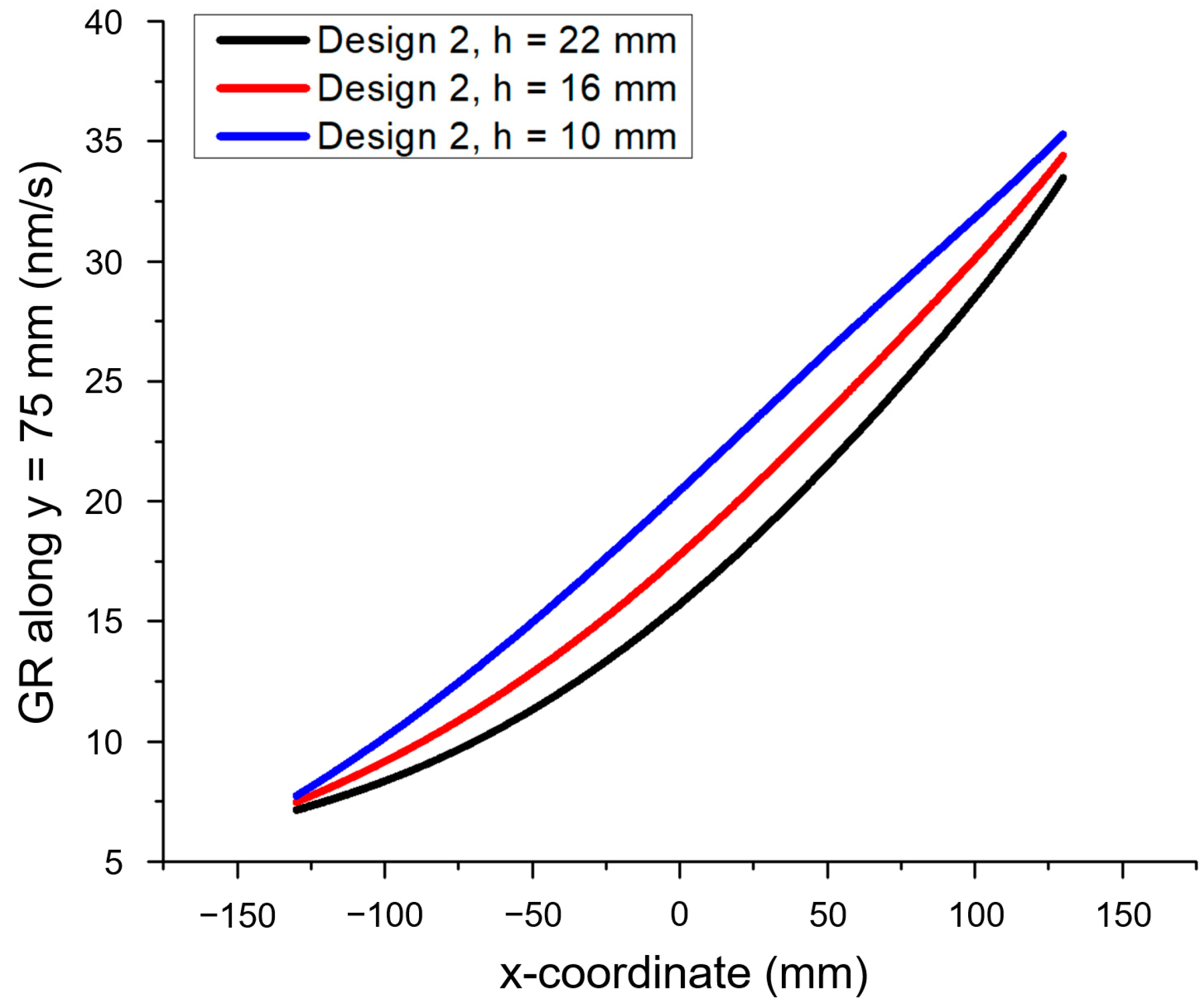

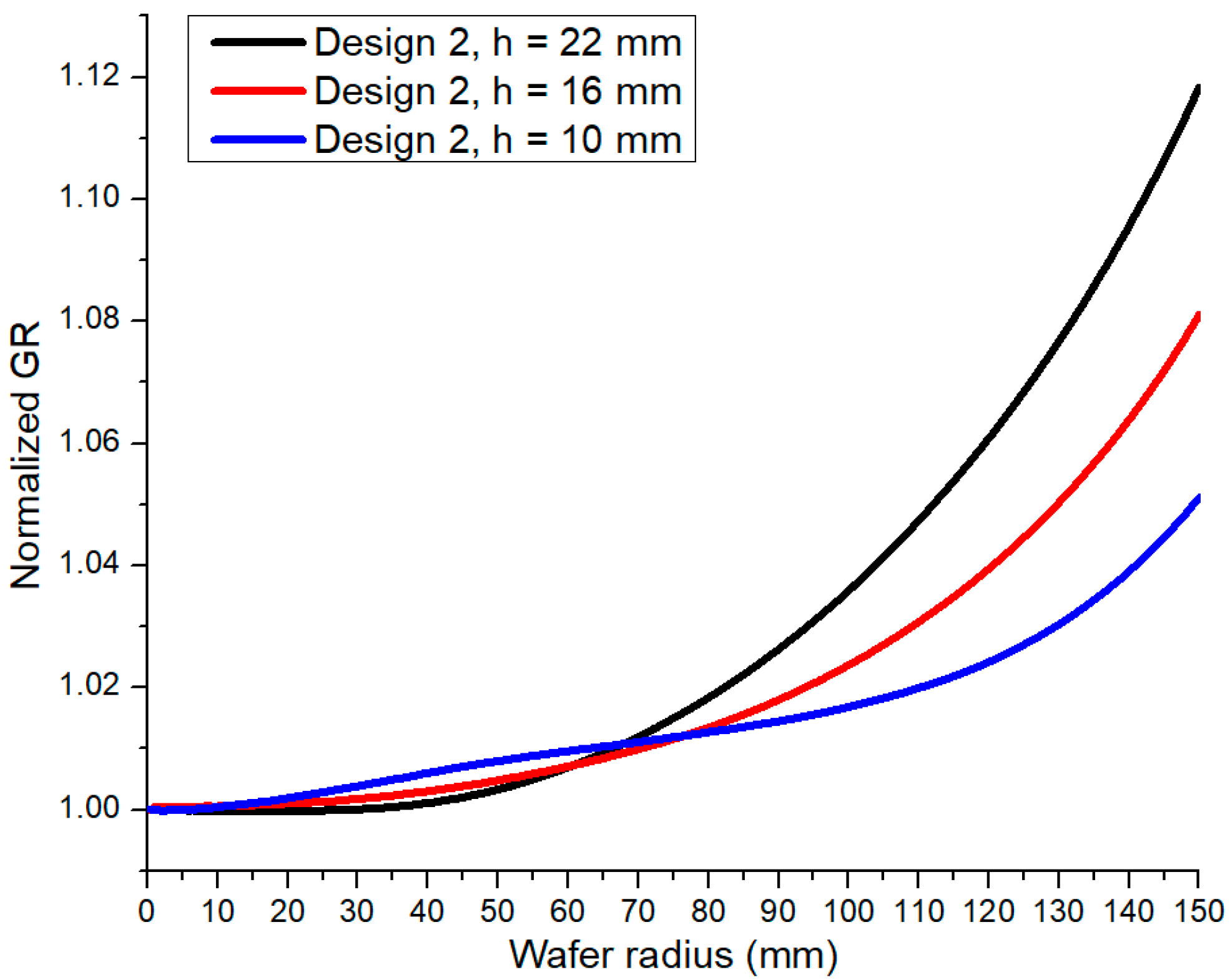

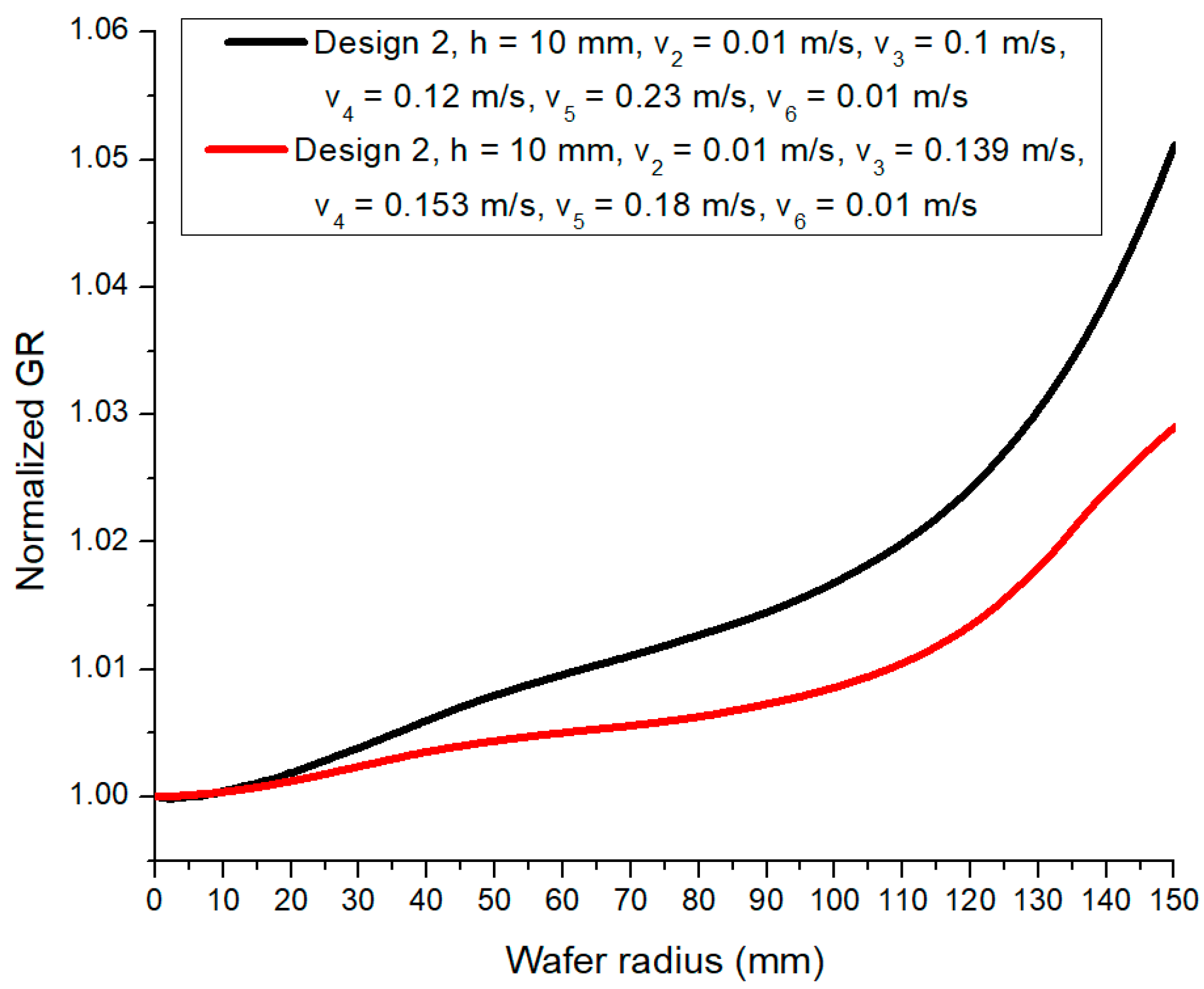

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kim, T.; Lee, J. Fabrication and characterization of silicon-on-insulator wafers. Micro Nano Syst. Lett. 2023, 11, 15. [Google Scholar] [CrossRef]

- Hossain, N.; Mahmud, M.Z.A.; Hossain, A.; Rahman, M.K.; Islam, M.S.; Tasnim, R.; Mobarak, M.H. Advances of materials science in MEMS applications: A review. Results Eng. 2024, 22, 102115. [Google Scholar] [CrossRef]

- Habuka, H.; Katayama, M.; Shimada, M.; Okuyama, K. Nonlinear increase in silicon epitaxial growth rate in a SiHCl3-H2 system under atmospheric pressure. J. Cryst. Growth 1997, 182, 352–362. [Google Scholar] [CrossRef]

- Habuka, H.; Fukaya, S.; Sawada, A.; Takeuchi, T.; Aihara, M. Flatness deterioration of silicon epitaxial film formed in a horizontal single-wafer epitaxial reactor II. Jpn. J. Appl. Phys. 2002, 41, 5692–5696. [Google Scholar] [CrossRef]

- Faller, F.R.; Hurrle, A. High-temperature CVD for crystalline-silicon thin-film solar cells. IEEE Trans. Electron Devices 1999, 46, 2048–2054. [Google Scholar] [CrossRef]

- Shimura, F. Semiconductor Silicon Crystal Technology, 1st ed.; Harcourt Brace Jovanovich: San Diego, CA, USA, 1989. [Google Scholar]

- Tilli, M.; Krockel, M.P.; Petzold, M.; Theuss, H.; Motooka, T.; Lindroos, V. Handbook of Silicon Based MEMS Materials and Technologies, 3rd ed.; Matthew Deans: London, UK, 2020. [Google Scholar]

- Li, C.; Li, C.; Jiang, H.; Chen, H.; Fang, H. Analysis of influencing factors on silicon epitaxial growth in horizontal single-wafer reactor through orthogonal test. Cryst. Res. Technol. 2024, 59, 2300237. [Google Scholar] [CrossRef]

- Ramadan, Z.; Im, I.T.; Park, C.W. Process optimization and modeling of the silicon growth in trichlorosilane-hydrogen gas mixture in a planetary CVD reactor. IEEE Trans. Semicond. Manuf. 2021, 34, 1–8. [Google Scholar] [CrossRef]

- Habuka, H.; Aoyama, Y.; Akiyama, S.; Otsuka, T.; Qu, W.F.; Shimada, M.; Okuayama, K. Chemical process of silicon epitaxial growth in a SiHCl3-H2 system. J. Cryst. Growth 1999, 207, 77–86. [Google Scholar] [CrossRef]

- Saito, A.; Miyazaki, K.; Matsui, M.; Habuka, H. In-situ observation of chemical vapor deposition using SiHCl3 nad BCl3 gases. Phys. Status Solidi 2015, 12, 953–957. [Google Scholar]

- Jeon, S.; Park, H.; Oh, H.J.; Kim, W.K. Computational modeling of a chemical vapor deposition reactor for epitaxial silicon formation. Sci. Adv. Mater. 2016, 8, 578–582. [Google Scholar] [CrossRef]

- Makino, S.; Inagaki, M.; Nakashima, K.; Kozawa, T.; Horinouchi, N. A simplified reaction reaction model and numerical analysis for Si depositon from SiHCl3-H2 system in vertical rotating disk reactors. J. Cryst. Growth 2016, 454, 156–163. [Google Scholar] [CrossRef]

- Miyazaki, K.; Saito, A.; Habuka, H. In situ measurement for evaluating temperature change related to silicon film formation in a SiHCl3-H2 system. ECS J. Solid State Sci. Technol. 2015, 5, 16–20. [Google Scholar] [CrossRef]

- Koosha, N.; Sabet, J.K.; Moosavian, M.A.; Amini, Y. Improvement of synthesized graphene structure through various solvent liquids at low temperatures by chemical vapor deposition method. Mater. Sci. Eng. B 2021, 274, 115458. [Google Scholar] [CrossRef]

- Saito, A.; Sakurai, A.; Habuka, H. Increase in silicon film deposition rate in SiHCl3-SiHx-H2 system. J. Cryst. Growth 2017, 468, 204–207. [Google Scholar] [CrossRef]

- Lundstrom, M.S.; Lam, M.A. Moore’s law: The journey ahead. Science 2022, 378, 722–723. [Google Scholar] [CrossRef]

- Jeong, J.; Lee, S.H.; Masuoka, S.A.; Min, S.; Lee, S.; Kim, S.; Myung, T.; Choi, B.; Sohn, C.W.; Kim, S.W.; et al. World’s first GAA 3nm foundry platform technology (SF3) with novel multi-bridge-channel-FET (MBCFETTM) Process. In Proceedings of the 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Kyoto, Japan, 11–16 June 2023; pp. 1–2. [Google Scholar]

- Kao, I.; Chung, C. Wafer Manufacturing: Shaping of Single Crystal Silicon Wafers, 1st ed.; Wiley: Hoboken, NJ, USA, 2021. [Google Scholar]

- Kunle, M.; Baumgartl, J.; Ackermann, T. Uniformity improvement for 200mm APCVD epitaxial Si film by retrofit of applied materials epi centura. In Proceedings of the SEMI Advanced Semiconductor Manufacturing Conference, Saratoga Springs, NY, USA, 19–21 May 2014; Volume 25, pp. 389–392. [Google Scholar]

- Levinson, H.J. High-NA EUV lithography: Current status and outlook for the future. Jpn. J. Appl. Phys. 2022, 61, SD0803-1–SD0803-18. [Google Scholar] [CrossRef]

- Irikura, K.; Muroi, M.; Yamada, A.; Matsuo, M.; Habuka, H.; Ishida, Y.; Ikeda, S.I.; Hara, S. Advantages of a slim vertical gas channel at high SiHCl3 concentrations for atmospheric pressure silicon epitaxial growth. Mater. Sci. Semicond. Process. 2018, 87, 13–18. [Google Scholar] [CrossRef]

- Lee, H.; Lee, J.; Kim, S.; Lee, C.; Han, S.; Kim, M.; Kwon, W.; Park, S.K.; Veeraraghavan, S.; Kim, J.; et al. Improvement of depth of focus control using wafer geometry. SPIE Adv. Lithogr. 2015, 9424, 942428-1–942428-6. [Google Scholar]

- Pacheco, J.M.; Gueorguiev, G.K.; Martins, J.L. First-principles study of the possibility of condensed phases of endohedral silicon cage clusters. Phys. Rev. B 2002, 66, 033401. [Google Scholar] [CrossRef]

- Gueorguiev, G.K.; Stafstrom, S.; Hultman, L. Nano-wire formation by self-assembly of silicon-metal cage-like molecules. Chem. Phys. Lett. 2008, 458, 170–174. [Google Scholar] [CrossRef]

- Sibanda, D.; Oyinbo, S.T.; Jen, T.C. A review of atomic layer deposion modelling and simulation methodologies: Density functional theory and molecular dynamics. Nanotechnol. Rev. 2022, 11, 1332–1363. [Google Scholar] [CrossRef]

- Tian, Y.; Yan, Z.; Jiang, L.; Liu, R.; Liu, B.; Shao, Y.; Yang, X.; Lu, M. Multiscale models of CVD process: Review and prospective. Materials 2024, 17, 5131. [Google Scholar] [CrossRef]

- Holstein, W.L. Design and modeling of chemical vapor deposition reactors. Prog. Cryst. Growth Charact. Mater. 1992, 24, 111–211. [Google Scholar] [CrossRef]

- Fischer, A.; Kissinger, G.; Ritter, G.; Akhmetov, V.; Kittler, M. Plastic deformation in 200 mm silicon wafers arising from mechanical loads in vertical-type and horizontal-type furnaces. Mater. Sci. Eng. B 2009, 159–160, 103–106. [Google Scholar] [CrossRef]

- Sivaram, S. Chemical Vapor Deposition: Thermal and Plasma Deposition of Electronic Materials; Van Nostrand Reinhold: New York, NY, USA, 1995. [Google Scholar]

- Hahn, P.O. The 300 mm silicon wafer—A cost and technology challenge. Microelectron. Eng. 2001, 56, 3–13. [Google Scholar] [CrossRef]

- Deng, B.; Liu, Z.; Peng, H. Toward mass production of CVD graphene films. Adv. Mater. 2018, 31, 1800996. [Google Scholar] [CrossRef]

- Rinaldi, A.M.; Crippa, D. Chapter 1 CVD teachnologies for silicon: A quick survey. Semicond. Semimet. 2001, 72, 1–50. [Google Scholar]

- Kommu, S.; Wilson, G.M.; Khomami, B. A theoretical/experimental study of silicon epitaxy in horizontal single-wafer chemical vapor deposition reactors. J. Electrochem. Soc. 2000, 147, 1538–1550. [Google Scholar] [CrossRef]

- Le, B.P.; Chen, J.C.; Hu, C.; Lin, W.J.; Tu, C.C.; Chen, L.C. Numerical analysis of the use of multiple inlet plates to improve the thickness uniformity of silicon epitaxial layers during atmospheric pressure chemical vapor deposition. Results Eng. 2024, 24, 103688. [Google Scholar] [CrossRef]

- Kommu, S.; Khomami, B. High-volume single-wafer reactors for silicon epitaxy. Ind. Eng. Chem. Res. 2002, 41, 732–743. [Google Scholar] [CrossRef]

- Salinger, A.G.; Pawlowski, R.P.; Shadid, J.N.; Waanders, B.G.V.B. Computational analysis and optimization of a chemical vapor deposition reactor with large-scale computing. Ind. Eng. Chem. Res. 2004, 43, 4612–4623. [Google Scholar] [CrossRef]

- Habuka, H. Flatness deterioration of Silicon epitaxxial film formed using horizontal single-wafer epitaxial reactor. Jpn. J. Appl. Phys. 2001, 40, 6041–6044. [Google Scholar] [CrossRef]

- Habuka, H.; Fukaya, S.I.; Sawada, A.; Takeuchi, T.; Aihara, M. Formation mechanism of local thickness profile of silicon epitaxial film. J. Cryst. Growth 2004, 266, 327–332. [Google Scholar] [CrossRef]

- Fang, M.; Xiong, Y.Y.; Yuan, X.Z.; Liu, Y.W. Numerical analysis of the chemical vapor deposition of polysilicon in a trichlorosilane and hydrogen system. Energy Procedia 2014, 61, 1987–1991. [Google Scholar] [CrossRef]

- Habuka, H.; Katayama, M.; Shimada, M.; Okuyama, K. Numerical evaluation of Silicon-thin film growth from SiHCl3-H2 gas mixture in a horizontal vapor deposition reactor. Jpn. J. Appl. Phys. 1994, 33, 1977–1985. [Google Scholar] [CrossRef]

- Angermeier, D.; Monna, R.; Slaoui, A.; Muller, J.C. Modeling and analysis of the Silicon epitaxial growth with SiHCl3 in a horizontal rapid thermal chemical vapor deposiiton reactor. J. Electrochem. Soc. 1997, 144, 3256–3261. [Google Scholar] [CrossRef]

- Garbrecht, O. Large Eddy Simulation of Three-Dimentional Mixed Convection on a Vertical Plate. Ph.D. Thesis, RWTH Aachen University, Aachen, Germany, 2017. [Google Scholar]

- Cheng, T.S.; Hsiao, M.C. Numerical investigations of geometric effects on flow and thermal fields in a horizontal CVD reactor. J. Cryst. Growth 2008, 310, 3097–3106. [Google Scholar] [CrossRef]

- Le, B.P.; Lin, W.J.; Chen, J.C.; Hu, C.; Tu, C.C.; Chen, L.C. Numerical and experimental investigation of the effect of side injectors on the deposition rate near the wafer edge during atmospheric pressure chemical vapor deposition. Mater. Sci. Semicond. Process. 2024, 172, 108085. [Google Scholar] [CrossRef]

- Habuka, H.; Nagoya, T.; Mayusumi, M.; Katayama, M.; Shimada, M.; Okuyama, K. Model on transport phenomena and epitaxial growth of silicon thin film in SiHCl3-H2 system under atmospheric pressure. J. Cryst. Growth 1996, 169, 61–72. [Google Scholar] [CrossRef]

- Lin, W.J.; Chen, J.C. A numerical study of the effect of pulse duration on preventing particle generation during the AlN pulsed MOCVD process. Mater. Sci. Semicond. Process. 2022, 148, 106816. [Google Scholar] [CrossRef]

- Lin, W.J.; Chen, J.C. Numerical Study of Growth Rate and Purge Time in the AlN Pulsed MOCVD Process. Crystals 2022, 12, 1101. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Le, B.-P.; Chen, J.-C.; Hu, C.; Lin, W.-J.; Tu, C.-C.; Chen, L.-C. Numerical Simulation of the Effect of APCVD Reactor Tilted Ceiling Height on Silicon Epitaxial Layer Thickness Uniformity. Crystals 2025, 15, 477. https://doi.org/10.3390/cryst15050477

Le B-P, Chen J-C, Hu C, Lin W-J, Tu C-C, Chen L-C. Numerical Simulation of the Effect of APCVD Reactor Tilted Ceiling Height on Silicon Epitaxial Layer Thickness Uniformity. Crystals. 2025; 15(5):477. https://doi.org/10.3390/cryst15050477

Chicago/Turabian StyleLe, Ba-Phuoc, Jyh-Chen Chen, Chieh Hu, Wei-Jie Lin, Chun-Chin Tu, and Liang-Chin Chen. 2025. "Numerical Simulation of the Effect of APCVD Reactor Tilted Ceiling Height on Silicon Epitaxial Layer Thickness Uniformity" Crystals 15, no. 5: 477. https://doi.org/10.3390/cryst15050477

APA StyleLe, B.-P., Chen, J.-C., Hu, C., Lin, W.-J., Tu, C.-C., & Chen, L.-C. (2025). Numerical Simulation of the Effect of APCVD Reactor Tilted Ceiling Height on Silicon Epitaxial Layer Thickness Uniformity. Crystals, 15(5), 477. https://doi.org/10.3390/cryst15050477